### 國立交通大學

### 電子工程學系 電子研究所碩士班

### 碩士論文

形成矽化鎳時在矽化鎳與矽接面處離子活化相關研究

Research of Dopant Activation at the Interface between Nickel Silicide and Silicon during Nickel Silicide Formation

| 研 究 生:楊志祥   | Student : Chih-Hsiang Yang   |

|-------------|------------------------------|

| 指導教授:張國明 博士 | Advisor : Dr. Kow-Ming Chang |

桂正楣 博士

Dr. Cheng-May Kwei

中華民國九十六年七月

### 形成矽化鎳時在矽化鎳與矽接面處離子活化相 關研究

### Research of Dopant Activation at the Interface between Nickel Silicide and Silicon during Nickel Silicide Formation

A Thesis Submitted to Department of Electronics Engineering & Institute of Electronics College of Electrical and Computer Engineering National Chiao Tung University In Partial Fulfillment of the Requirements for the Degree of Master In Electronics Engineering July 2007 Hsinchu, Taiwan, Republic of China

中華民國九十六年七月

# 形成矽化镍時在矽化鎳與矽接面處離子活化相關研究

研究生:楊志祥 指導教授:張國明博士

#### 桂正楣博士

#### 國立交通大學

電子工程學系 電子研究所碩士班

在先進互補式金氧半導體元件裡,當接觸尺寸縮小至奈米等級,源極及汲極 的接觸電阻也會隨之增加。因此,金屬矽化物的技術應用在源極及汲極已經被開 發用來同時降低接觸電阻及接面寄生電阻。在奈米金氧半場效電晶體的製造中, 矽化製程是必須的,為了抑制源極及汲極的超淺接面形成所產生的短通道效應。 所以,是否具有與矽基材完好介面特性的金屬矽化物,是在製造奈米尺寸的元件 時重要的製程考量。在本論文中,我們主要探討離子佈植入矽化鎳再經由後續不 同條件的退火製程後,所呈現出的活化量及電特性的研究。吾人結合離子佈植入 矽化鎳和固態磊晶再成長的概念來達到低溫在介面處的高活化特性,此結果和吾 人準備的傳統高溫退火試片相比較,發現在550度時的片電阻值即可與傳統高溫 所得之片電阻值相當,此外,透過I-V和C-V的量測結果,我們可以對我們所製 作的接面做理想因子和介面活化濃度的推算,總和所有的實驗結果,此低溫活化 的特性是很有潛力取代傳統的高溫退火已獲得高活化的製程。

### Research of Dopant Activation at the Interface between Nickel

Silicide and Silicon during Nickel Silicide Formation

### Student : Chih-Hsiang Yang

Advisor : Dr. Kow-Ming Chang

### Advisor : Dr. Cheng-May Kwei

Department of Electronics Engineering and Institute of Electronics National Chiao Tung University

In advanced CMOS devices, as contact dimensions scale down to nanometer range, contact resistance of source and drain is increased correspondingly. As a result, the technique of metal silicides for poly gate and source/drain has been developed to reduce the contact resistance and the parasitic junction resistance as well. In nanometer MOSFET fabrication, this silicidation process requires considering to suppress short channel effect (SCE) when forming the ultra shallow source and drain junction. Therefore, metal silicides owning a perfect interfacial property with Si above an ultra-shallow junction is considered as a critical module toward the realization of nano-scale CMOS. In the thesis, we want to know the amount of activation and electro-characteristics by different thermal process. The experiments shows that nickel silicide interface dopant activation improved by two-step rapid thermal annealing (RTA) process. We combined the concept of implant into silicide (IIS) and solid phase epitaxial regrowth (SPER) to lowering the process temperature. Compared with the conventional samples, the results for doping interface had nice sheet resistance at RTA 550°C. By means of I-V and C-V method, we could also discuss the ideality factor and interface dosage. The overall results can promote the low temperature activation and have the potential to replace conventional high temperature anneal.

#### 誌 謝

南風又輕輕的吹起,絲絲的離情充滿了整個校園, 艷麗的鳳凰花悄悄在枝頭 綻放, 昔日的讀書聲, 窗外的嬉笑聲, 也將成為美麗的回憶, 想到這裡內心是多 麼沉重, 一股股的心酸不時的湧上心頭。

回憶兩年來在交大電子的學習生活,首先感謝指導教授張國明教授與桂正楣 教授,老師的開明態度跟指導教誨讓我的研究生涯受益匪淺,而每次謝師宴上老 師的信心喊話更讓我們覺得我們生活在一個感情融洽的大家庭裡,謝謝老師。

AND LEAR

同時也要感謝許許多多的博士班學長、同學及學弟。另外特別感謝一直指導 我的林建宏學長,不論是在實驗上,最後論文的修訂,準備口試時提供的建議及 幫助,使我論文能夠盡善盡美。還有感謝交大奈米中心、國家奈米實驗室提供各 種實驗設備,可以讓我順利進行實驗。

最後要感謝我的父母,楊再博先生與王美月女士,謝謝他們從小到大對我的 養育之恩以及教導我待人處世的道理。以及謝謝家人們的支持,沒有你們的支持 與鼓勵我也沒辦法順利考上交大電子,完成碩士學位。

iv

### Contents

| Chinese Abstract | ·i   |

|------------------|------|

| English Abstract | ii   |

| Acknowledgements | iv   |

| Contents         | v    |

| Table Captions   | vii  |

| Figure Captions  | viii |

| Chapter 1 Introduction     | and the second sec |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1General background      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.2Motivation              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1.3Organization of thesis- | 1896 06                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 1.4References              | 07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

### Chapter 2 Formation of nickel silicide

| 2.1 Introduction                        | 09 |

|-----------------------------------------|----|

| 2.2 Sheet resistance test               | 10 |

| 2.3 SEM cross-sectional view inspection | 11 |

| 2.4 References                          | 12 |

### Chapter 3 Characterization of Boron/Phosphorous Implanted To Silicide by Subsequence Thermal Process

| 3.1 Introduction | 13 |

|------------------|----|

| 3.2 Experiment   | 16 |

| 3.3 References   | 18 |

### Chapter 4 Physical Properties and Electrical Characteristics of Boron/Phosphorous Implanted Through Silicide

| 4.1 Compare conventional dopant activation and 2-step RTA result |

|------------------------------------------------------------------|

| of IIS dopant activation21                                       |

| 4.2 I-V measurement23                                            |

| 4.3 C-V measurement                                              |

| 4.3.1 C-V measurement introduction24                             |

| 4.3.2 Results and Discussion26                                   |

| 4.4 SIMS inspection26                                            |

| 4.5 References27                                                 |

|                                                                  |

| Chapter 5 Conclusion28                                           |

| Chapter 6 Future Work29                                          |

### **Table Captions**

- Table.1.1 Comparison the characteristics of Ti, Co and Ni silicides.

- **Table.2.1** The recipes of Nickel silicide formation for different Ni

deposition system

- **Table.2.2** The recipes of Nickel silicide formation for different a-Si

deposition system

- **Table.3.1** Process recipe of P+N and N+/P junction by IIS scheme.

- **Table.3.2** Process recipe of P+N and N+/P junction for comparison samples scheme.

- Table.4.1 Recipes of IIS for I-V and C-V measured experiment

### **Figure Captions**

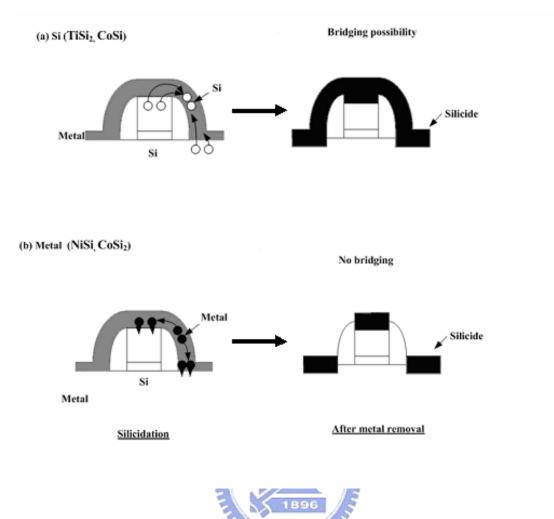

- Fig.1.1 With/without bridging phenomenon of metal silicides.

- Fig.1.2 Continuation of Moor's Law from intel's high-k/metal gate announcement (2003)

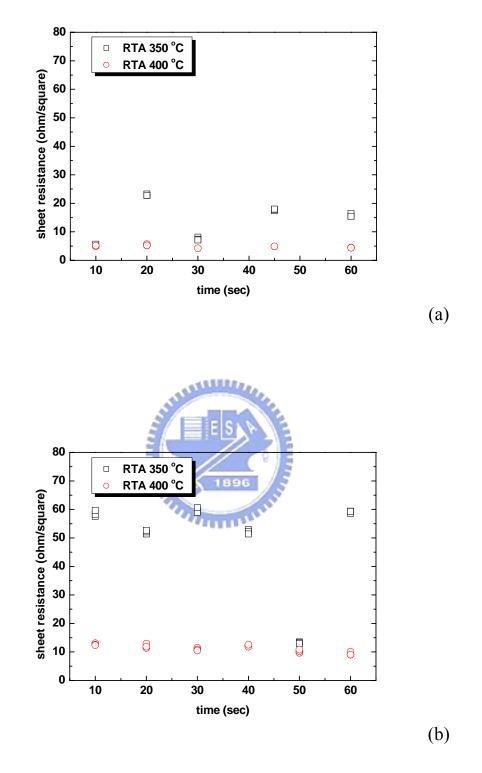

- Fig.2.1 Results of nickel silicide sheet resistance: (a) Dual E-Gun Evaporation System (b) Sputtering System

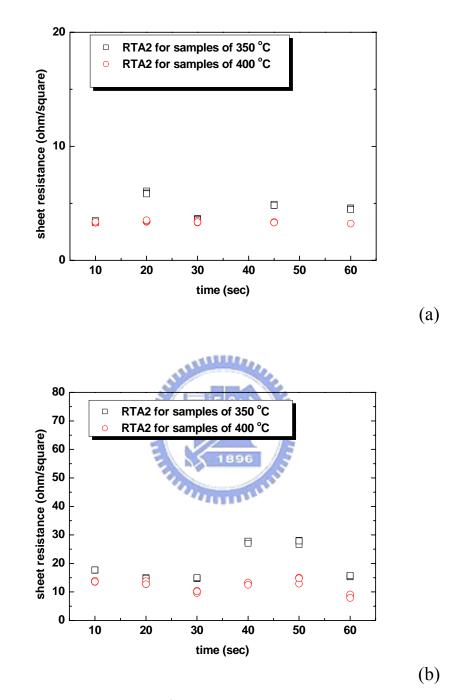

- **Fig.2.2** Results of RTA2, 550°C 50sec, treatment to forming NiSi: (a) Dual E-Gun Evaporation System (b) Sputtering System

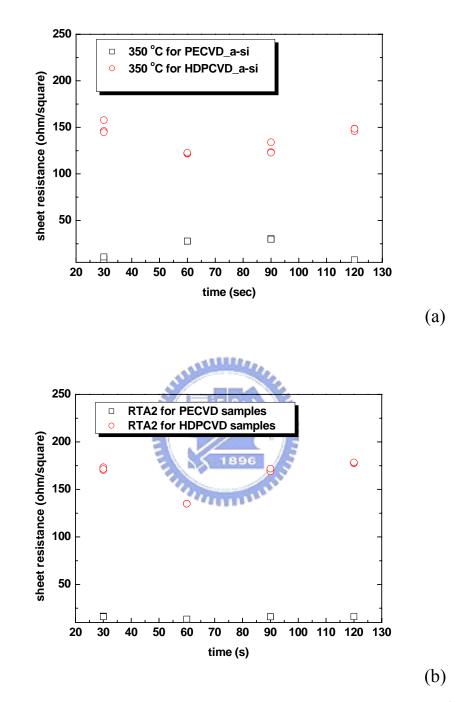

- **Fig.2.3** Results of nickel silicide sheet resistance: (a)first RTA 350°C with different time for PECVD and HDPCVD a-Si samples (b)all samples were treated by second RTA 550°C 50sec

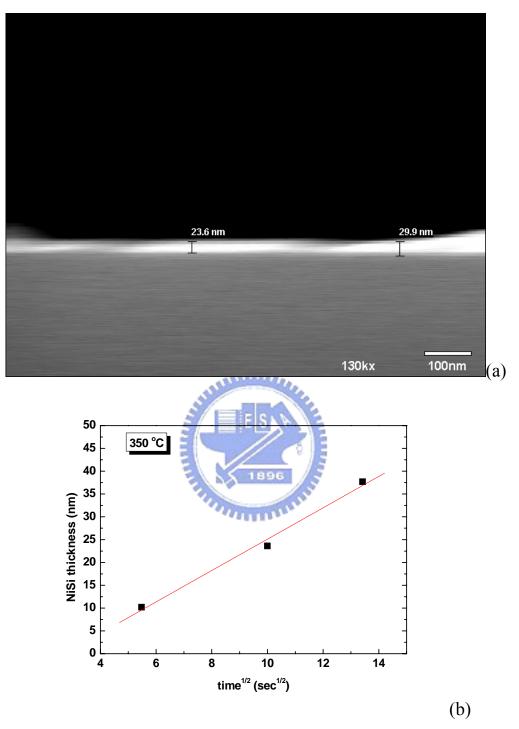

- **Fig.2.4** (a)SEM image for nickel silicide which was formed by Sputtering System Ni with single crystalline Si (b)silicide thickness versus square root of time

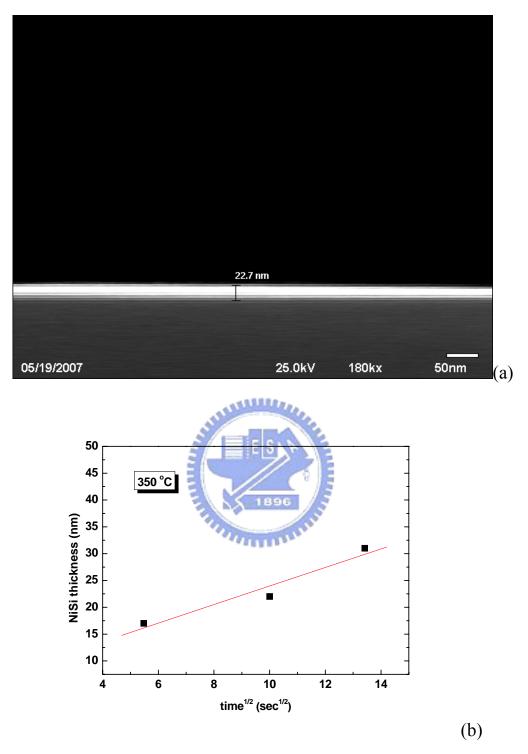

- Fig.2.5 (a)SEM image for nickel silicide which was formed by DualE-Gun Evaporation System Ni with single crystalline Si(b)silicide thickness versus square root of time

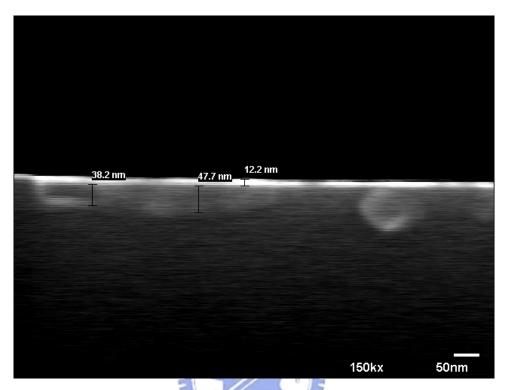

- Fig.2.6 SEM image of nickel silicide which was formed by Dual E-Gun Evaporation System Ni with PECVD deposited a-Si

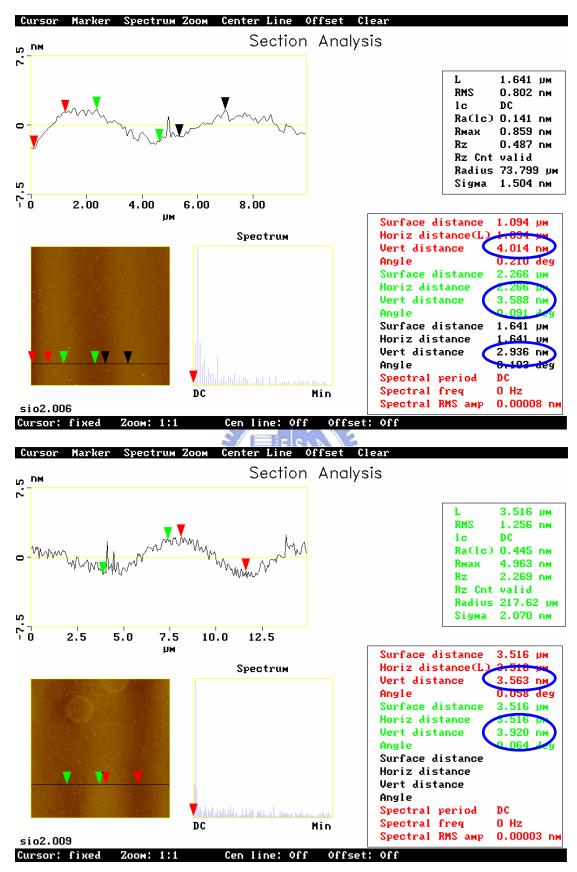

- **Fig.3.1** AFM inspection image of Si substrate etched by silicide etching solvent for 30min

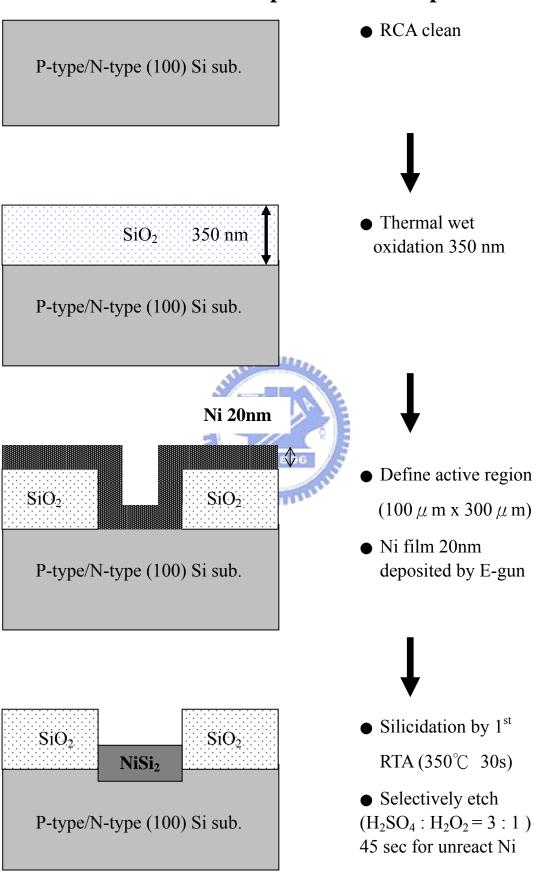

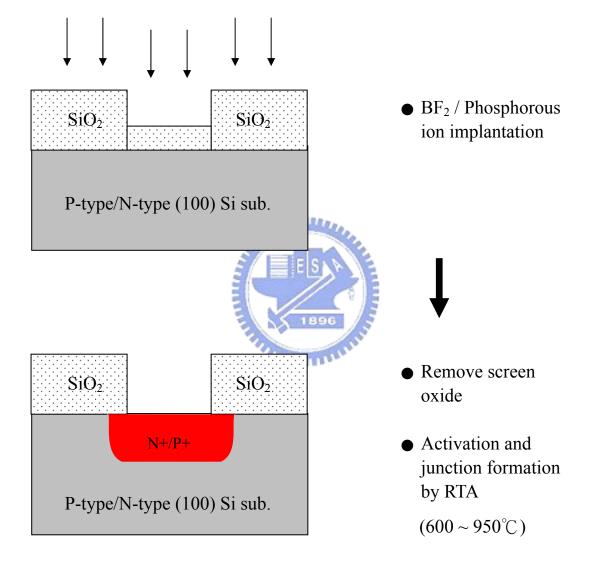

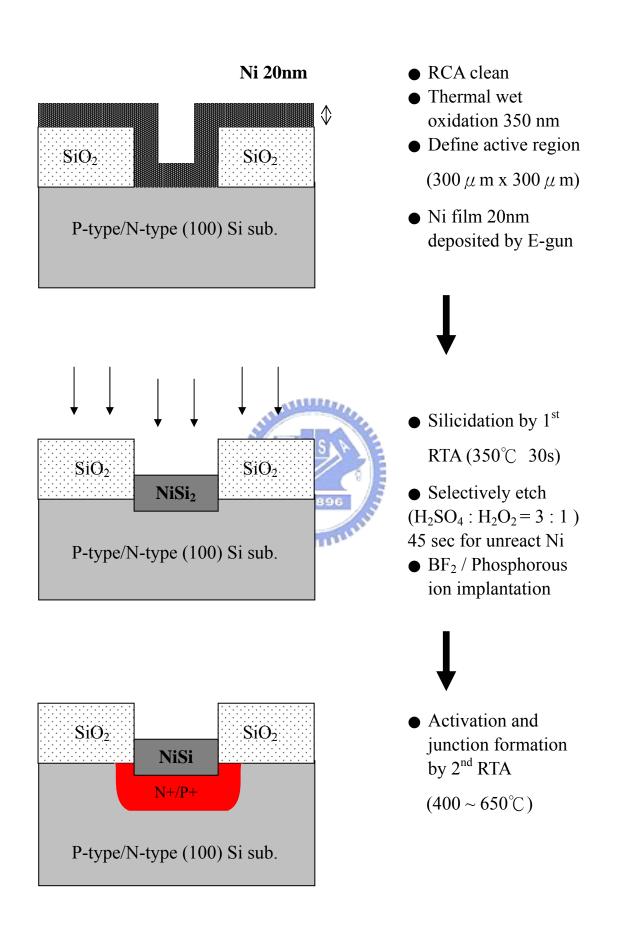

- **Fig.3.2** Process flow of P+N and N+/P junction by IIS scheme

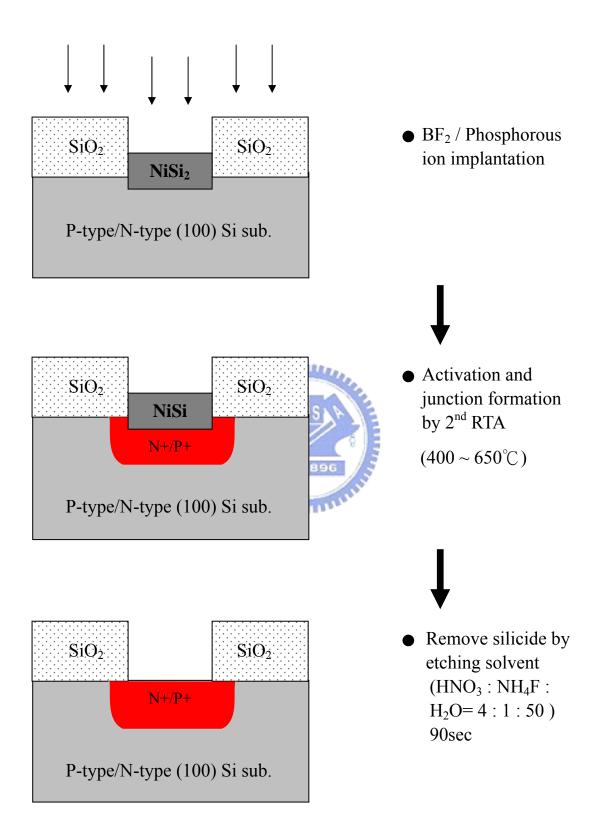

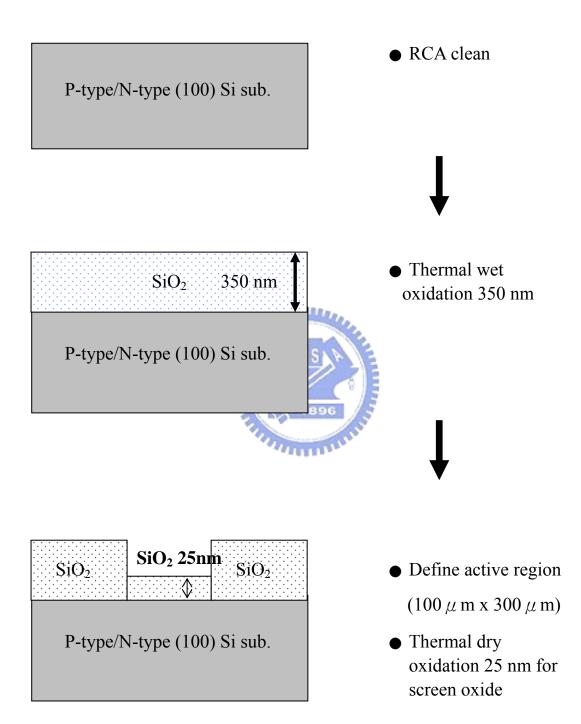

- **Fig.3.3** Process flow of P+N and N+/P junction for comparison samples scheme

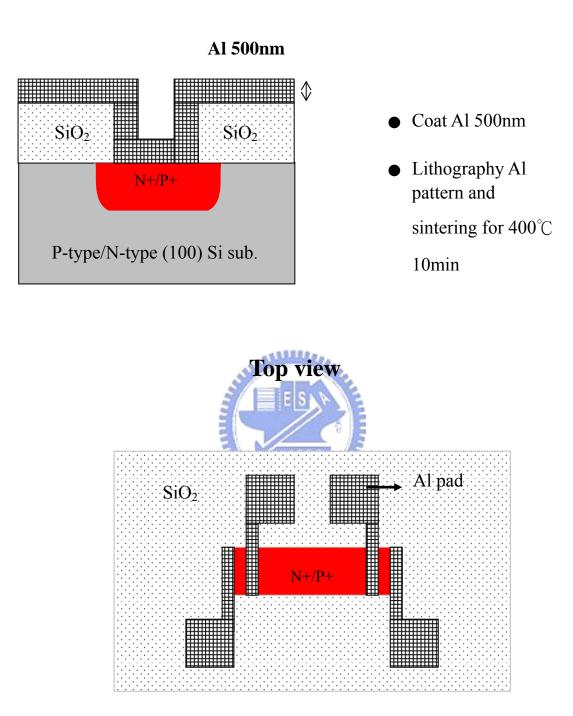

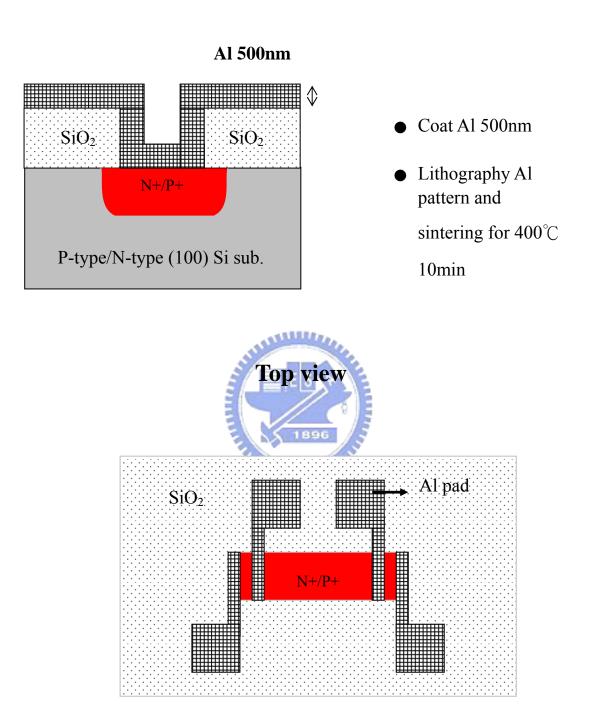

- **Fig.3.4** Process flow of P+/N and N+/P junction samples of silicide contact for I-V and C-V electrical properties measurement.

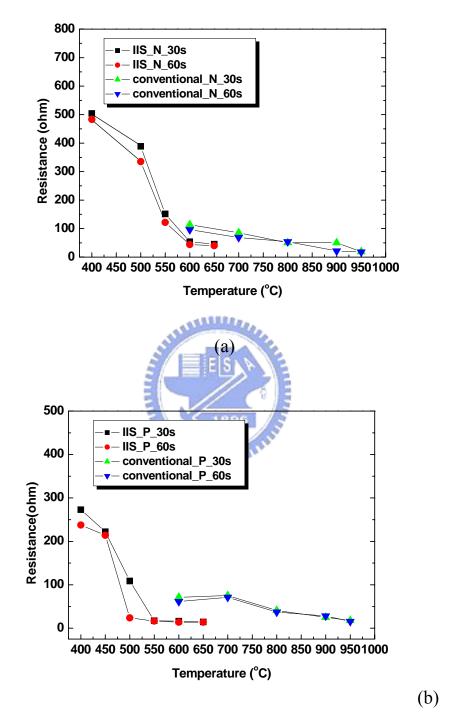

- Fig.4.1 The IIS samples compared with conventional high temperature anneal (a) N-sub Si implanted BF<sub>2</sub> (b) P-sub Si implanted Phosphorous

- Fig.4.2 The comparison of different Si-sub implanted different dopant (a) IIS samples compared (b) conventional high annealing samples compared

- Fig.4.3 The experiment of counter dopingwas N-sub wafer to form silicide and implanted BF<sub>2</sub> then annealed at 400°C 5/15/30/60s, respectively.

- **Fig.4.4** The relationship of doping Si-sub etching time versus reciprocal resistance

- **Fig.4.5** (a)~(f) I-V graphics for IIS N-sub samples

- **Fig.4.6** (a)~(f) I-V graphics for IIS P-sub samples

- Fig.4.7 ideality factor (a)N-sub samples (b)P-sub samples

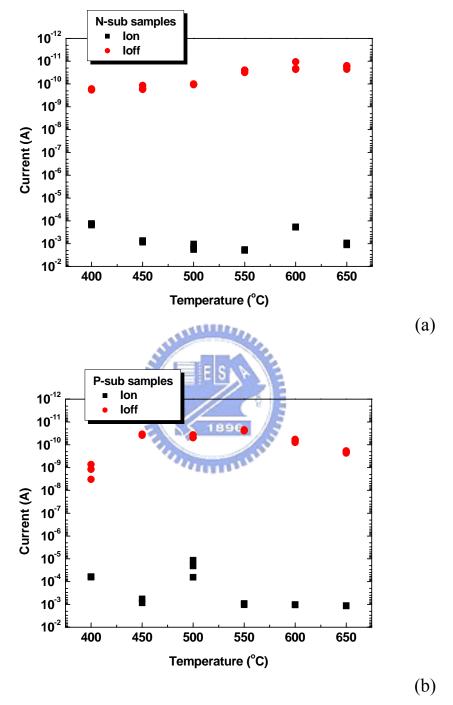

- Fig.4.8 Ion-Ioff relation graphics(a)N-sub samples (b)P-sub samples

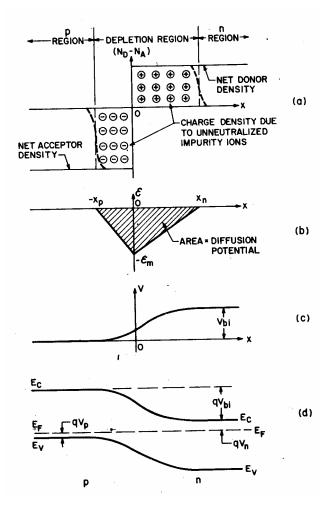

- Fig.4.9 Abrupt p-n junction in thermal equilibrium. (a)Space-charge distribution. Dashed lines indicate corrections to depletion approximation. (b)Electric-field distribution. (c)Potential distribution where Vbi(Ψ<sub>bi</sub>) is the built-in potential.

(d)energy-band diagram.

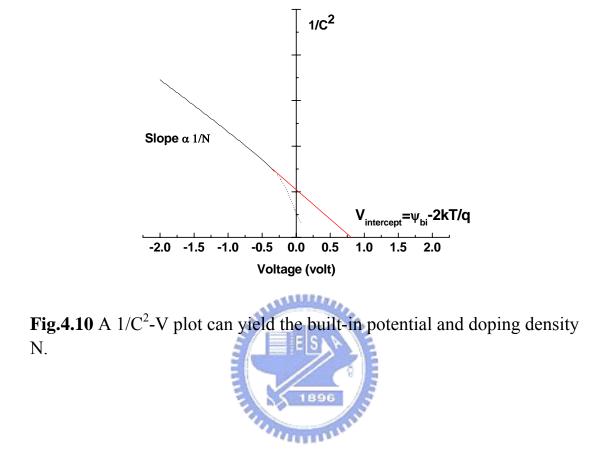

- **Fig.4.10** A  $1/C^2$ -V plot can yield the built-in potential and doping density N.

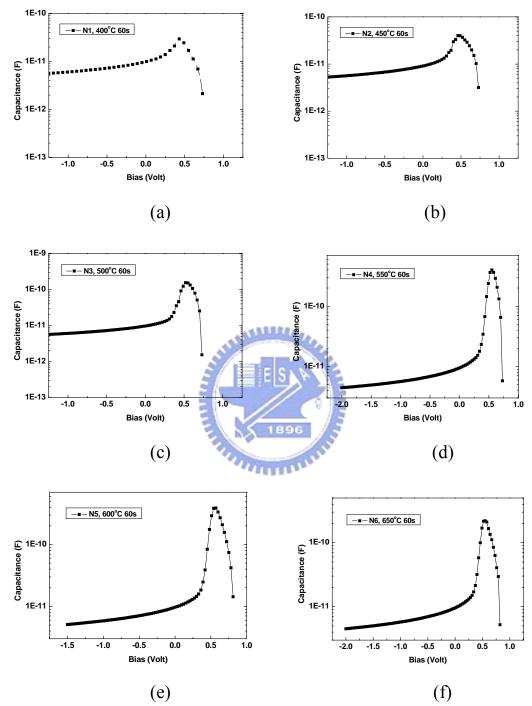

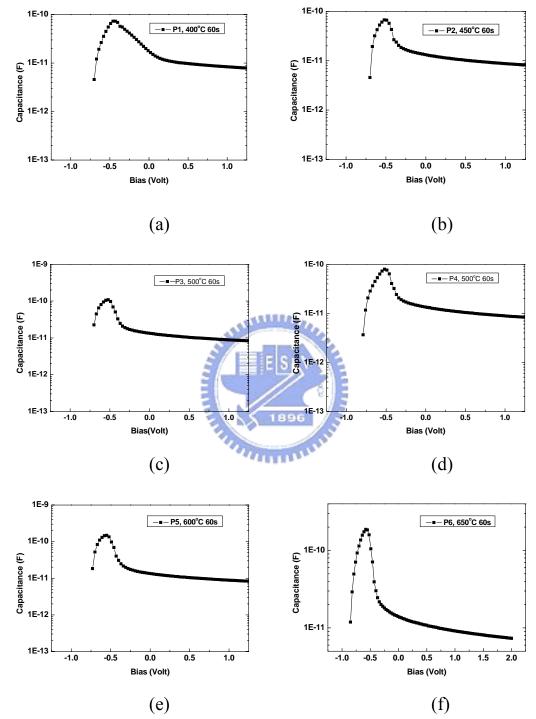

- **Fig.4.11** (a)~(f) C-V graphics for IIS N-sub samples

- **Fig.4.12** (a)~(f) C-V graphics for IIS P-sub samples

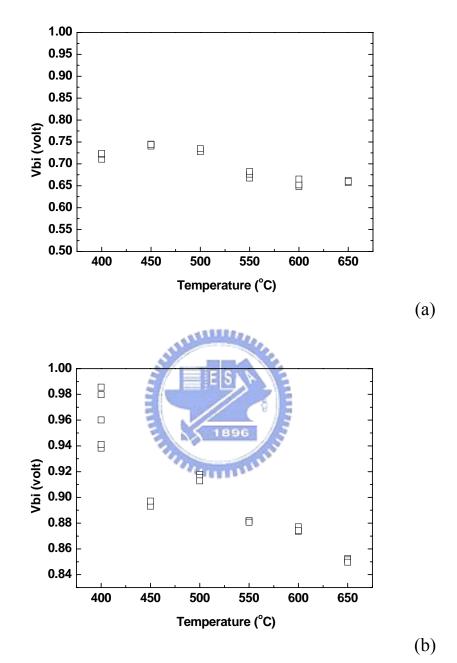

- **Fig.4.13**  $\Psi_{bi}$  (a)N-sub samples (b)P-sub samples

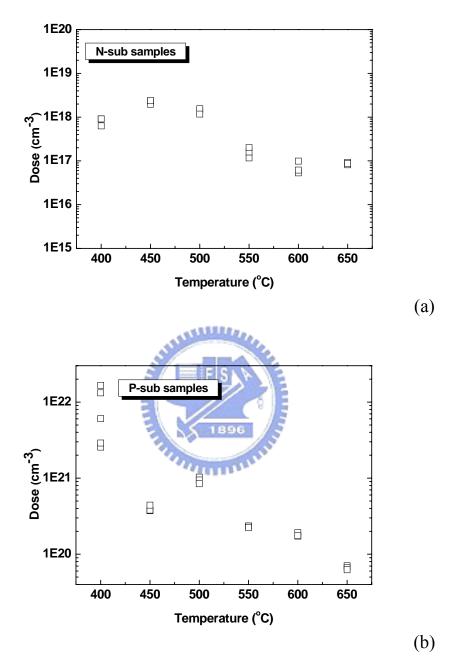

- **Fig.4.14** The dopant activation density of IIS at MS interface (a)N-sub samples (b)P-sub samples

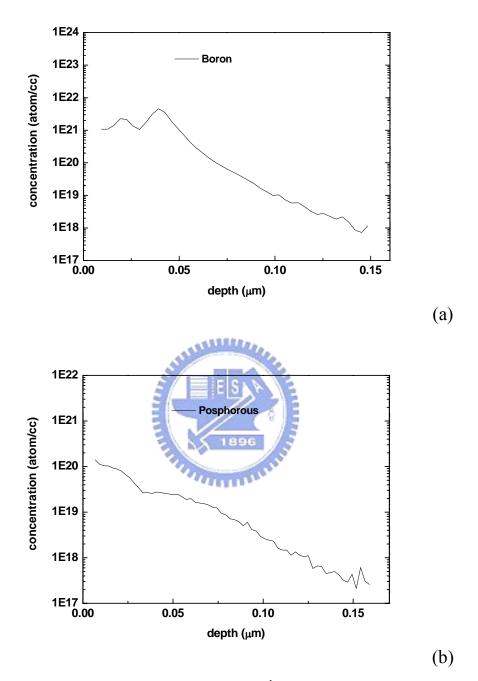

**Fig.4.15** SIMS analysis for IIS samples 2<sup>nd</sup> RTA 650°C 60s (a)N-sub

sample (b)P-sub sample

### **Chapter 1**

### Introduction

#### 1.1 General background

In order to improve the performance and packing density of metal-oxide-semiconductor (MOS) integrated circuit, the device dimension has been scaled down to nanometer region. In nanometer complementary metal - oxide- semiconductor (CMOS) circuit with gate length down to 0.1  $\mu$ m, the parasitic resistance of gate, source and drain region will increase. Those result in the increase of RC time delay and more power dissipation with integrated circuit.

In past years, many people made effort to develop a new technology for reducing parasitic resistance to improve the device and circuit performance. Nowadays, the metal-silicide-related technology has become an integral part of nanometer devices for reducing the parasitic resistance in order to improve the devices and circuit performance. The major advantages of metal silicides can be grouped as follows:

(1) Their low resistivity for gate and interconnect applications

(2) Easy formation by self-aligned technology without any extra mask and compatible with conventional CMOS process.

Where the self-aligned silicide (salicide) process is widely used in MOS manufacturing to reduce the sheet resistance and contact resistance of the gate polysilicon [1]. In nanometer MOSFET fabrication, this silicidation process requires considering to suppress short channel effect (SCE) when forming the ultra shallow source and drain junction. Therefore, metal silicides owning a perfect interfacial property with Si above an ultra-shallow junction that is considered as a critical module toward the realization of nano-scale CMOS. Additionally, as the oxide thickness scaling down with the device dimensions, the gate oxide reliability will also be a concern for the silicided gate process.

Numbers of silicides have been discussed to use to improve device performance, such as TiSi<sub>2</sub>, CoSi<sub>2</sub>, MoSi<sub>2</sub> and NiSi. Some of silicides, TiSi<sub>2</sub>, CoSi<sub>2</sub> and NiSi, have been used for device fabrication. Moreover, different silicides show different characteristics. Some properties have good merits for device fabrication, but others would negatively affect the integrity circuit processes.

Titanium disilicide (TiSi<sub>2</sub>) has been the most commonly used metal-silicide in ULSI process, because its low resistivity and relatively high thermal stability. In addition, Ti is very effective at reducing native oxide in contacts, because of the high solubility of oxygen in Ti [2,3]. There are two phases of TiSi<sub>2</sub>, corresponding to different crystal structures; a base-centered orthorhombic C49 structure and a face-centered orthorhombic C54 structure [4]. The C49 phase forms first and has a high resistivity(60-300  $\mu$  ohm-cm) whereas the C54 phase has low resistivity(13-35  $\mu$  ohm-cm) so that TiSi<sub>2</sub> must be phase transformation from C49 phase to C54 phase [5,6]. However, as line width shrinks below 0.2  $\mu$ m, the width is not enough for C49-TiSi<sub>2</sub> to convert to C54-TiSi<sub>2</sub> completely (even at the temperature above 800  $^{\circ}$ C), and the silicide agglomeration temperature limit is about 950  $^{\circ}$ C. Bridging phenomenon is also a problem of TiSi<sub>2</sub> process. During the silicidation of Ti/Si system, the Si atom is the dominant diffusing species. This facilitates the problem of bridging in the MOSFET salicide structure, silicidation may occur on the sidewalls, as shown in Fig.1.1. The possibility of Silicide bridge forming between the gate and source or drain increases when the physical dimensions of the device decrease. As a consequence, there is an increasing need for new silicide material suitable for nanometer CMOS devices.

Cobalt disilicide (CoSi<sub>2</sub>) is a promising alternative to TiSi<sub>2</sub> for salicide applications [6,7]. The resistivity and thermal stability of CoSi<sub>2</sub> are similar to those of TiSi<sub>2</sub>, but the sheet resistance of CoSi<sub>2</sub> is relatively insensitive to decreasing line width, unlike TiSi<sub>2</sub>[6,7]. In addition, CoSi<sub>2</sub> can be used as a diffusion source to form shallow junctions [7]. However, CoSi<sub>2</sub> have two major drawbacks. First, the formation of CoSi<sub>2</sub> consumes a relatively larger amount of Si to achieve an equivalent silicide sheet resistance or Co spike will lead to the larger junction leakage [8,9]. Large silicon comsuption will restrict the vertical scaling for CoSi<sub>2</sub> to achieve shallow junction and not compatible with the SOI process. Second, surface cleaning is more critical; since Co does not reduce an interfacial oxide as Ti does, the existence of the interfacial oxide will affect the CoSi<sub>2</sub> formation severely increase the contact resistance. Third, cobalt is not compatible to SiGe process, which is the main method to increase the device mobility.

The Nickel monosilicide (NiSi) which shows improved performance with respect to the three limitations presented above is the candidate to replace the CoSi<sub>2</sub>. Four main advantages of NiSi are listed below:

- (1) Reduced thermal budget

- (2) Low Si consumption

- (3) Formation controlled by Ni diffusion

- (4) Low resistivity phase formation possible on SiGe

Multiple factors contribute to the ease of formation of the low resistivity NiSi with low thermal budget such as the high solubility of Ni in Silicon [10,11]. Ni also has a considerably large diffusivity in Si than Co at low temperature [12]. Once low resistivity NiSi is formed, it does not have to anneal further and reach the NiSi phase. The lower Si content of NiSi compared to  $CoSi_2$  is also an advantage. There are two reasons contribute to the lower consumption of Si. The first one is the lower silicon density of NiSi compared to  $CoSi_2$ . This alone allows for a reduction in Si consumption by more than 10%. Second, since the resistivity of NiSi consumption is lower than that of  $CoSi_2$  (~18  $\mu$  ohm-cm), the NiSi silicide films can be considerably thinner for the same sheet resistance. Those factors combined typically lead to a reduction in Si consumption of about 35%.

Besides the silicon consumption, bridging phenomenon during silicide formation is also an important issue. In the case of NiSi, silicidation proceeds by the diffusion of metal into the Si. So it can effectively reduce the bridging phenomenon. Recently, in order to reduce the poly depletion effect, metal gate is adapted to the VLSI manufacturing again. Since the work function of NiSi can be modulated by doping different dopants such like boron, phosphorous, and arsenic [13], this property makes the NiSi suitable for nanometer CMOS technology. In addition, the film stress of NiSi is also much lower than that of TiSi<sub>2</sub> and CoSi<sub>2</sub>. Because of above advantages, nickel monosilicide has received more attention over the last years.

### **1.2 Motivation**

The rapid advance of integrated circuit technology has moved the minimum feature size into nanometer region. In the nano-device generation, the reliability and performances of CMOS have suffered some problems which about gate-leakage and poly depletion. In order to improve these problems, it is a tendency to choose new materials. Metal/high-k gate stack technology is a promising structure since it provides both low gate-leakage and minimal poly depletion effect [14]. Although Metal/high-k gate stack technology will be the mainstream technology in the future, as shown in Fig.1.2, there are still some drawbacks need to be overcome. The one of these is thermal reliability for high-k dielectric.

Hf-silicate which is the most plausible near-term candidate for high-k dielectric. However, it can not tolerate high temperature process, because that high-k dielectric will crystallize under high temperature process. With the high-k dielectric crystallization, the gate-leakage current will increase dramatically. Since the thermal reliability is playing an important role for Metal/high-k gate stack technology, it is why that NiSi will be chosen to the metal gate material. NiSi attributed to the low temperature process window.

However, it needs high temperature annealing to achieve high implanted dopant activation in the S/D region when adapted gate first (self-aligned) process. The threshold voltage (Vt) adjustment in the gate region also needs high level dopant activation (high thermal budgut).

In parallel with the gate dielectric engineering to improve the high-k dielectric's thermal reliability, we are interesting in the project about low temperature activation. If the process temperature after gate dielectric formation can be lowered, the high-k dielectric crystallized problem in process integration can also be minimized. We combined the concept of implant into silicide (IIS) and solid phase epitaxial regrowth (SPER) to lowering the process temperature. These two methods lower the dopant activation temperature through the concept of change the surface energy of silicon and pile up the dopant concentration by dopant segregation (IIS) and/or higher the solubility of the dopant in Si through the Si re-crystallization process. Details about these two methods with our experiment will be discussed in the following chapters.

#### **1.3 Organization of the Thesis**

In this thesis, we concentrate our efforts on the activation of B and P implant through silicide by RTA process. In chapter 1, brief introduction metal-silicide technology history evolution and the motivation of this thesis are mentioned. In chapter 2, find the optimized recipe to forming nickel monosilicde. In chapter 3, first overview of metal-silicide technology is given to describe the various applications and process technologies. Second the process flow of fabrication will be described. In chapter 4, the detail

discussion of characteristics includes physical properties, electrical properties and doping concentration extraction. In chapter 5 is conclusions and chapter 6 is future works.

### **1.4 References**

- [1] Anne Lauwers, An Steegen Muriel de Potter, Richard Lindsay, Alessandra Satta, Hugo Bender, and K. Maex, American Vacuum Society B 19(6) (2001).

- [2] T.B. Massalski, Binary Alloy Phase Diagram, ASM international, Materials Park, OH (1990)

- [3] J.C. Barbour, A.E.M.J. Fischer and J.F. van der Veen, J.Appl. Phys. 62, 2582(1987)

- [4] R. Beyers and R. Sinclair, J.Appl. Phys. 57, 5240(1985)

- [5] J.B. Lasky, J. S. Nakos, O. J. Cain, and P. J. Geiss, IEEE Trans, Electron Device 38, 262 (1991).

- [6] K. Maex, Mater. Sci, Eng. R11, 53 (1993).

- [7] J.B. Lasky, J.S. Nakos, O.J. Cain and P.J. Geiss, IEDM Trans. Electron Devices, ED-3458, 262(1991)

- [8] B. S. Chen, and M. C. Chen, "Formation of Cobalt silicided Shallow Junction Using Implant Into/Through Silicate Technology and Low Temperature Furnace Annealing," IEEE Trans.Electron Devices, vol. 43, no. 2, pp. 258-266, Feb. (1996).

- [9] K. Goto, J. Watanabe, T. Sukegawa, A. Fushida, T. Sakuma, and T. Sugii, "A Comparative Study of Leakage Mechanism of Co and Ni Salicide Processes," IEEE Annual International eliability Physics Symposium, pp. 363-369, (1998).

- [10] M.Y. Lee, P.A. Bennett, Phya. Rev. Lett. 75-4460(1995)

- [11]C.A. Londos, K. Eftaxias, V. Hadjicontis, Phya. Stat. Sol. A118-K13(1990)

- [12]O. Madelung, Semiconductors Basic Data, Springer, 1996

- [13] A. Kinoshita, C. Tanaka, K. Uchida, and J. Koga, Symposium on VLSI Technology Digest of Technical Papers, 9A-3, (2005).

- [14]C. Hobbs et al., Symp. VLSI Tech., 9, (2003)

### **Chapter 2**

### Formation of nickel silicide

#### **2.1 Introduction**

With the lower formation temperature and lower silicon consumption, nickel silicide overcomes some limitations of cobalt silicide, and provides a scaling ability to push the device into the 30 nm technology range. For successful process integration, key material feathers and formation limitations need to be understood to minimize adverse effects on the electrical characteristics of device. A two step RTA process was shown to provide an optimal integration of NiSi technology [1]. Under the two step process, in this chapter, we would compare the sheet resistance of silicide on crystal silicon by different Ni deposition system, and select the better one as our starting deposition source in the following experiments. Also, as being a metal gate material, we compared the silicide sheet resistance formed on different a-Si source. Four point probe was adapted to measure the sheet resistance, SEM cross-sectional image would be inspected the silicide thickness, and using AFM to compare silicide roughness.

#### 2.2 Sheet resistance test

Before the experiment begins, determining the best recipes for silicide formation is necessary. First of all, the Ni deposition source must be decided. P-type (100) oriented Si wafers was prepared for the silicide formation substrate. After a standard RCA clean process, we deposited Ni 20 nm with Dual E-Gun Evaporation System and Sputtering System respectively. Both samples were then rapid thermal annealed (RTA) at  $350^{\circ}C/400^{\circ}C$  with different time duration in N<sub>2</sub> ambient to form nickel silicide, the recipes listed in Table.2.1. The unreacted Ni film was selectively etched using SPM solution of  $(H_2SO_4 : H_2O_2 = 3 : 1)$  at 75~85 °C for 45 sec. The sheet resistance measurement results of the remaining silicide were shown in Fig.2.1. Then, we chosen the temperature which in the NiSi formation process window, 550°C 50sec, as a second RTA process temperature [2], the sheet resistance was shown in Fig.2.2. From the results of Fig.2.1 and Fig.2.2, it shows that the lower sheet resistance of nickel silicide is the nickel deposited with the Dual E-Gun Evaporation System so that the Ni deposition for following experiment was decided by using Dual E-Gun Evaporation System.

Moreover, based on the result of Fig.2.1, it shows that the sheet resistance for the samples annealed at  $350^{\circ}$ C was higher than those annealed at  $400^{\circ}$ C. It is because that  $350^{\circ}$ C is not enough to forming NiSi completely, but it can be utilized by second RTA process to transform the silicide from Ni<sub>2</sub>Si to NiSi. The second RTA process can lower sheet resistance effectively. In addition, excessive silicidation also must be concerned because it was found that the junction leakage measured on diode structures consisting of a large number of small active area islands [3,4] was greatly impoved by a reduction of the first RTA thermal budget. As a result, the excessive silicidation an can be reduced in a 2-step Ni-silicide process with reducing the thermal budget of the first RTA step. From the above mention, we would use  $350^{\circ}$ C 30 sec for the first step RTA being the experiment recipe.

In order to fabricate the fully silicide gate stack MOS capacitor structure, we will test the sheet resistance which use different a-Si source to react with Ni. A 300 nm oxide was thermally grown on the p-type (100) oriented Si wafer, and following a 50 nm thick a-Si was deposited using PECVD and HDPCVD, respectively. After a standard RCA clean process, 20 nm nickel was deposited using Dual E-Gun Evaporation System. Samples were then rapid thermal annealed (RTA) at 350°C for different time duration in N<sub>2</sub> ambient to form nickel silicide, the recipes listed in Table.2.2. The unreacted Ni film was selectively etched using a solution of  $H_2SO_4$  :  $H_2O_2 = 3 : 1$  at 75~85 °C for 45 sec. The results were shown in Fig.2.3(a). Then, we chosen the temperature which in the NiSi formation process window, 550°C 50sec, as a second RTA process temperature, as shown in Fig.2.3(b). From the results of Fig.2.3(a) and Fig.2.3(b), the lower sheet resistance of nickel silicide is formed by the PECVD System so that the a-Si deposition which was used for fully silicide gate material.

#### **2.3 SEM cross sectional view inspection**

In order to identify the real thickness of the as-deposited Ni film and the NiSi layer formed, scanning electron microscope (SEM) was used for cross sectional view inspection. Fig.2.4 and Fig.2.5 shows SEM images of NiSi

layer formed by RTP annealing at 350°C for different Ni deposition source by Dual E-Gun Evaporation System and Sputtering System, respectively.

The SEM image of silicide formed for gate stack technology was shown in Fig.2.6, it is formed by PECVD deposited a-Si with Dual E-Gun Evaporation System deposited Ni.

### **2.4 References**

- [1] John Foggiato, Woo Sik Yoo, Michel Ouaknine, Tomomi Murakami, Takahashi Fukada, Materials Science and Engineering B 114-115, 56-60(2004)

- [2] F. Deng, R. A. Jihnson, P. M. Asbeck, S. S. Lau, W. B. Dubbelday, T. Hsiao, and J. Woo, J.Appl.Phys. 81, 8047(1997)

- [3] Anne Lauwers, Jorge A. Kittl, Mark J.H. Van Dal, Oxana Chamirian, Malgorzata A. Pawlak, Muriel de Potter, Richard Lindsay, Toon Raymakers, Xavier Pages, Bencherki Mebarki, Tushar Mandrekar, Karen Maex, Materials Science and Engineering B 114-115(2004)

- [4] A. Lauwers, J.A. Kittl, M. Van Dal, O. Chamirian, R. Lindsay, M. dePotter, C. Demeurisse, C. Vrancken, K. Maex, X. Pages, K. Van derJeugd, V. Kuznetsov, R. Granneman, Microelectron. Eng., accepted for publication.

### **Chapter 3**

### Characterization of Boron/Phosphorous Implanted To Silicide by Subsequence Thermal Process

### **3.1 Introduction**

As device dimension is scaled down to deep submicron, not only the size of gate electrode is shrunk, but also the vertical dimension of doped source/drain regions must be scaled to avoid device punch through and short channel effects. In the past, PN junctions were formed by dopant ion implantation into Si substrate followed by high temperature furnace annealing for dopant activation and implantation damage annihilation. However, channeling effect and high temperature dopant diffusion limit the formation of shallow junction. This is particularly important for the  $p^+n$ junction because boron is a light element and diffuses fast in silicon. In recent years, many advanced junction formation techniques have been studied using low energy ion implantation, low temperature annealing, and rapid thermal annealing process. These new methods are briefly reviewed as follows :

(1) Pre-amorphization of silicon substrate before dopant implantation

Pre-amorphization has been widely used to control the channeling behavior of implanted dopant atoms. After the pre-amorphization of the silicon substrate surface layer, dopant implantation was performed followed by crystal regrowth and annealing process for the junction formation. Many heavy atoms have been used as pre-amorphization species, such as Si [1] and Ge. [2-3] Solid phase epitaxial (SPE) scheme can be used to regrow the crystal from the amorphous layer at a temperature as low as 550  $^{\circ}$ C [4]. The growth rate depends on the element used for pre-amorphization as well as the dopant implanted following the pre-amorphization. A careful annealing process is needed to annihilate the massive defects and dislocation induced by the pre-amorphization.

### (2) Elevated source/drain structure

This method is to raise the source/drain regions by depositing a polysilicon (poly-Si) or amorphous silicon ( $\alpha$ -Si) film or growing a selective epitaxial Si or SiGe layer[5-6]. Deposition of poly-Si/ $\alpha$ -Si film on the source/drain regions needs an additional lithographic step to define the elevated regions, while the selective epitaxial growth of silicon on the source/drain regions does not need such an additional lithographic step. The elevated source/drain regions made with selective epitaxial growth (SEG) provide a sacrificial layer for silicide formation and an alternative approach for the salicide process. However, the SEG scheme needs a high deposition temperature to obtain good crystallinity in the epitaxial layer. The fact that high temperature process deteriorates the device performance is the main disadvantage of this method[7].

### (3) Low energy ion implantation [8-10]

This is an extension of the conventional ion implantation technique. The implantation energy is lower than 1 keV and the implantation dose is typically from  $1 \times 10^{14}$  to  $5 \times 10^{14}$  cm<sup>-2</sup>. The major disadvantage of this method

is that no commercial implantation system of such a low energy ion beam is available for high throughput mass production with reasonable cost.

#### (4) IIS/ITM technique

The implant into silicide (IIS) and implant through metal (ITM) processes have been investigated for shallow junction formation. The IIS/ITM process consists of implanting dopants into/through silicide or metal layer and the subsequent thermal annealing to form a silicide-contacted shallow junction [11-14]. The IIS scheme in particular is of much benefit to the formation of shallow junction. This is because metal silicides have a larger nuclear stopping power than silicon for the implanted dopant ions and thus can reduce the channeling effect; in addition, the junction formed by the IIS scheme can be almost free of implant damage, which is mostly confined in the silicide layer. Thus, the post-implant annealing temperature can be lowered while shallow junctions with superb characteristics can be obtained. Moreover, the silicided junction is conformal to the silicide/silicon interface, and thus the possibility of junction penetration by the silicide is reduced.

The need for high-activation, diffusionless junctions and low temperature process for advanced gate stacks have promoted further research in shallow junction formation. Because solid phase epitaxial regrowth(SPER)[15-17] works on the principle that dopants in an amorphous region will activate to a level above the equilibrium solid solubility during crystalline regrowth. Temperature even below 600°C allow regrowth, and thus activation, with negligible dopant diffusion[18]. In this thesis, we would combine the dopant pile-up characteristic of IIS at interface and the ability of SPER to achieving the formation of N+/P and P+/N shallow junction.

#### **3.2 Experiment**

Because the experiment will need to remove the NiSi to measuring the sheet resistance which could obtain the silicide/Si interface dopant activation, we had to get the silicide etched solvent(HNO<sub>3</sub> : NH<sub>4</sub>F : H<sub>2</sub>O= 4 : 1 : 50) selectivity of silicide to Si. We prepared the p-type (100) oriented Si wafers to form the NiSi and then used SEM to measure the silicide thickness was around 20nm which as shown in Fig.2.5. Before silicide etching test, we measured the sheet resistance of p-type (100) wafer and had formed silicide wafer by four-point probe. Then, we used the silicide removed solvent to etch silicide and took the duration which sheet resistance value up to the p-type (100) wafer value to be the silicide complete removed duration, 60sec. We took the silicide removed solvent to etched p-type (100) wafer for 30min and inspected the etched thickness by AFM, as shown in Fig.3.1 to obtaining the etching rate of silicide removed solvent to p-type (100) wafer. From the experiment, we got the etching selectivity of NiSi/Si substrate was 100 : 1. In the follow-up experiment, we would take the over etching time for 30s to conform the silicide removed completely because of the high etching selectivity.

The sheet resistance experiment samples for the four-point probe measuring structure included experimental and comparison samples. First, experimental and comparison samples were fabricated on p-type/n-type (100) oriented Si wafers. After a standard RCA clean process. Then, a 350 nm isolation oxide was grown on the wafer by wet oxidation at 1000°C for 35 min. The active regions were defined by the photolithography and etched by BOE (buffered oxide etchant) solution. Then, experimental samples were standard cleaned again to fully remove the contamination.

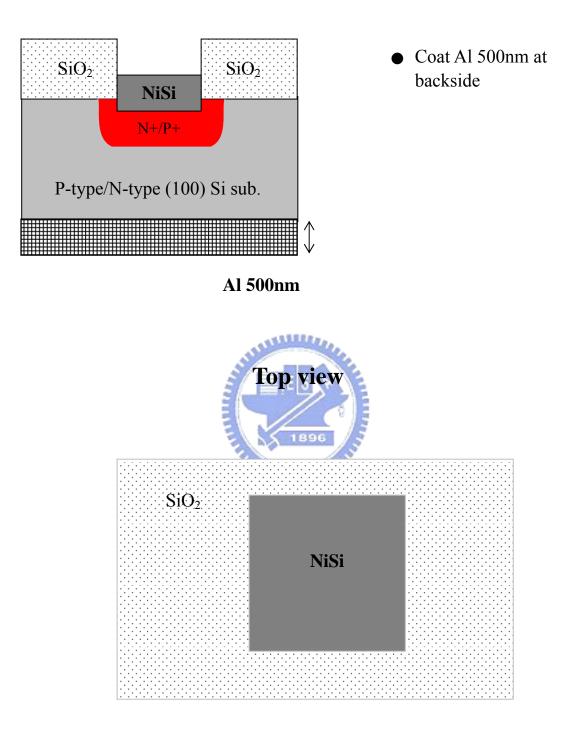

Following, a 20 nm Ni deposited on the wafer in a Dual E-Gun Evaporation system with a base pressure of less than  $5 \times 10^{-6}$  torr, using a Ni target in vacuum ambient with a deposition rate of about 0.7- 1.0 Å/sec. After the Ni film deposition, the samples were rapid thermal annealed (RTA) at 350°C for 30 sec in  $N_2$  ambient to form NiSi. The unreacted Ni film was selectively etched using a solution of  $H_2SO_4$ :  $H_2O_2 = 3$ : 1 at 75~85 °C for 45 sec. Then, the sample of NiSi were implanted with  $BF_2^+$  /  $P^+$  ions at an energy of 50 and 30 keV to a dose of  $5 \times 10^{15} \text{ cm}^{-2}$ . After ion implantation, followed by rapid thermal anneal (RTA) at 400 to 650°C for 30 / 60 sec in N<sub>2</sub> ambient for the activation dopant, as shown in Fig.3.2. Process recipe is listed in Table.3.1. Because the selectivity of silicide to Si is large enough, NiSi was removed by silicide etched solvent(HNO3 :  $NH_4F$ :  $H_2O=4$ : 1: 50) for 90sec that included overetching 20sec. After above process, the samples were coated the Al 500nm by thermal coater, and used photolithography to define the four-point probe measuring pads. Comparison samples were also standard cleaned again to fully remove the contamination. Following, a 20 nm screen oxide was grown on the wafer by dry oxidation at 950°C for 30 min. Then, the sample were implanted with  $BF_2^+ / P^+$  ions at an energy of 28 and 43 keV to a dose of  $5 \times 10^{15} \text{ cm}^{-2}$ . After ion implantation, first, removed screen oxide by BOE and following by rapid thermal anneal (RTA) at 600 to 950°C for 30 / 60 sec in N<sub>2</sub> ambient for the activation dopant, as shown in Fig.3.3. Process recipe is listed in Table.3.2. After above process, the samples were coated the Al 500nm by thermal coater, and used photolithography to define the four-point probe measuring pads. The last step is sintering for  $400^{\circ}$ C 10min by furnace for both experimental and comparison samples.

We would also prepare the P+/N and N+/P junction samples of silicide contact for I-V and C-V electrical properties measurement. The samples prepared steps were the same as the above mentioned experimental samples. The different step with the experimental samples was we had not to remove silicde contact and needed to coat Al 500nm at backside. The fabricated process was shown in Fig.3.4 and process recipe is listed in Table.3.1 with the  $2^{nd}$  RTA duration is only 60s.

#### **3.3 References**

- [1] M. H. Juang and H. C. Cheng, Appl. Phys. Lett. 60, 2092, (1992).

- M. C. Ozturk, J. J. Wortman, C. M. Osburn, A. Ajmera, G. A. Rozgonyi,

E. Frey, W.-K. Chu, and C. Lee, IEEE Trans. Electron Devices 51, 663, (2004).

- [3] K. Suzuki, H. Tashiro, K. Narita, and Y. Kataoka, IEEE Trans. Electron Devices 35, 659, (1988).

- [4] M. Y. Tsai and B. G. Streetman, J. Appl. Phys. 50, 183, (1979).

- [5] H. J. Huang, K. M. Chen, T. Y. Huang, T. S. Chao, G. W. Huang, C. H. Chien, and C. Y. Chang, IEEE Trans. Electron Devices 48, 1627, (2001).

ALL DE LE

- [6] J. J. Sun, J. Y. Tsai, and C. M. Osburn, IEEE Trans. Electron Devices 45, 1946, (1998).

- [7] K. Miyano, I. Mizushima, A. Hokazono, K. Ohuchi, Y, Tsunashima, IEDM Tech Digest, p. 433, (2000).

- [8] Y. V. Ponomarev, P. A. Stolk, A. C. M. C. Van Brandenburg, C. J. J. Dachs, M. Kaiser, A. H. Montree, R. Roes, J. Schmitz, and P. H. Woerlee, VLSI Tech. Digest, p. 65, (1999).

- [9] D. Kirkwood, A. Murrell, E. Collart, P. Banks, R. Fontaniere, and C. Maleville, IEEE International Conference on Ion Implantation Technology, p. 633, (2002).

- [10] A. Nishida, E. Murakami, and S. Kimura, IEEE Trans. Electron Devices 45, 701, (1998).

- [11] C.-Y. Lu, J. J. Sung, R. Liu, N.-S. Tsai, R. Sing, S. J. Hillenius, and H. C. Kirsch, IEEE Trans. Electron Devices 38, 246, (1991).

- [12] Q. Wang, C. M. Osburn, C. A. Canovai, IEEE Trans. Electron Devices 39, 2486, (1992).

- [13] R. Angelucci, S. Solmi, A. Armigliato, S. Guerri, M. Merli, A. Poggi, and R. Canteri, J. Appl. Phys. 69, 3962, (1991).

- [14] B. S. Chen and M. C. Chen, IEEE Trans. Electron Devices 43, 258, (1996).

- [15] C. M. Osburn, et al, Ion implantation Tech. 1996, p832

- [16] K. Tsuji, et al, IEDM Tech Dig 1999, p9

- [17] R. Lindsay, et al, Mat. Res. Soc. Symp. Proc. Vol. 717, C2.1 2002

- [18] R. Lindsay, S. Severi, B. J. Pawlak, K. Henson, A. Lauwers, X. Pages,

A. Satta, R. Surdeanu, H. Lendzian, and K. Maex, "SPER Junction Optimisation in 45nm CMOS Devices", IEEE, 2004

### **Chapter 4**

### Physical Properties and Electrical Characteristics of Boron/Phosphorous Implanted Through Silicide

## 4.1 Compare conventional dopant activation and 2-step RTA result of IIS dopant activation

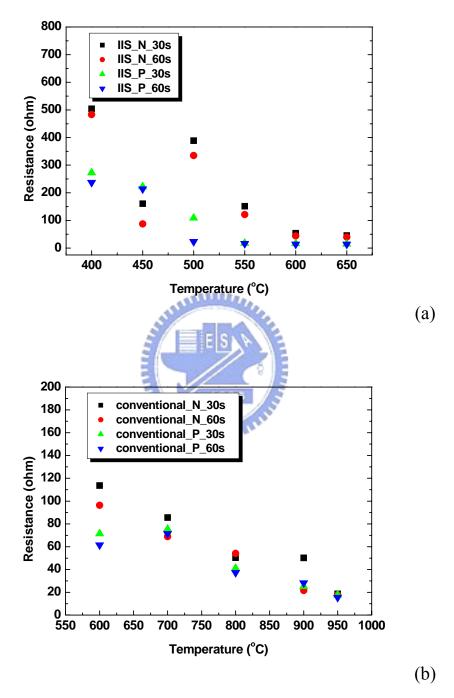

From the data of sheet resistance, we could obtain the result which about dopant activation ability of different situation. In the experimental samples, we used four-point probe to measure the sheet resistance is because that the accuracy of Spreading Resistance Profiling(SRP) in the shallow junction is not enough. So we used four-point probe structure to measure the sheet resistance of experimental and comparison samples and compared them. In order to measure the sheet resistance of shallow junction dopant activation, we must remove the silicide and the method is mentioned in chapter 3. The result of measurement was shown in Fig.4.1(a)(b) and we can obtain that when annealing temperature increased, the sheet resistance would decrease. This method does measure the bulk junction activation so we would get the results of Fig.4.1. The following we compared were the different implanted dopant samples. Because the solubility of phosphorous and electron mobility was higher than boron, the measured sheet resistance of phosphorous implanted was supposed to lower than boron implanted, theoretically. And the graphics was shown in Fig.4.2(a)(b), we could prove that the hypothesis

was correct.

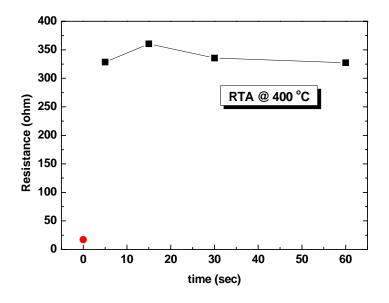

From above results, we could observe that the value of IIS N-sub samples was decreased at 450°C. We speculated that it might be due to the counter doping so that we would make a experiment to verify it. We prepared a sample set which used N-sub wafer to form silicide and implanted BF<sub>2</sub> then annealed by RTA at 400°C 5/15/30/60 s, respectively. The following were that removed silicide and coated Al then measured the sheet resistance, and the results was shown in Fig.4.3. According to the results of experiment, we could obtain the counter doping effect did occur at 400°C 10s so the hypothesis of counter doping was not a main reason. The another opinion which we supposed was the RTA process would affect the grain regrowth so that the overetching of removing silicide would have an influence on sheet resistance measurement.

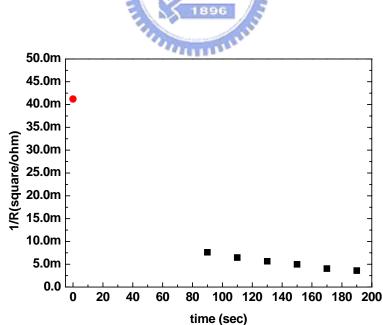

Because the silicide removed overetching time would maybe affect the doping Si substrate, we would want to know the relationship of overetching time with sheet resistance. We prepared a P-sub sample to form silicide and selected a  $2^{nd}$  RTA recipe, 550°C 60s, after implanted phosphorous. Then, we used silicide removed solvent to etching it and measured the sheet resistance. The relationship of sheet resistance was :

$$R_{s} = \frac{\rho}{T - \alpha t} \Longrightarrow \frac{1}{R_{s}} = \frac{1}{\rho} (T - \alpha t)$$

$$T : thickness, \alpha : etch rate, t : time$$

(1)

The graphic was reciprocal sheet resistance versus etchin time, as shown in Fig.4.4. We obtained that silicide overetching would affect the sheet resistance and were sure that the silicide was removed. Because the relation of reciprocal resistance versus etching time was linearity, we could also

calculate effectively the sheet resistance which without overetching time by this relationship and could know that the doping density was uniform.

#### **4.2 I-V measurement**

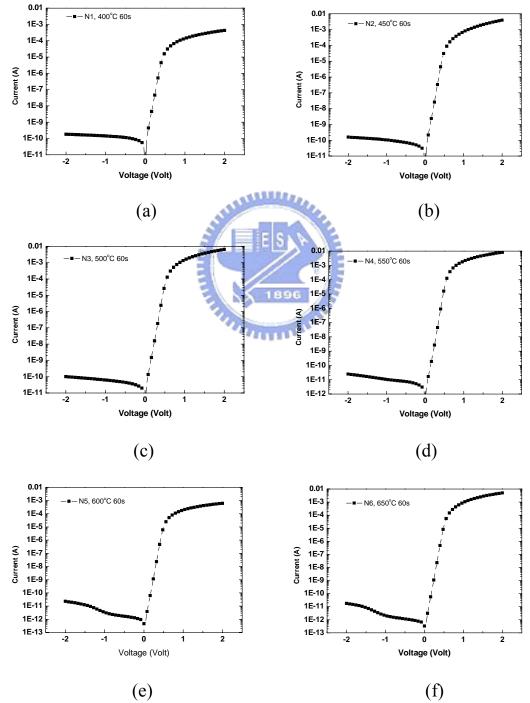

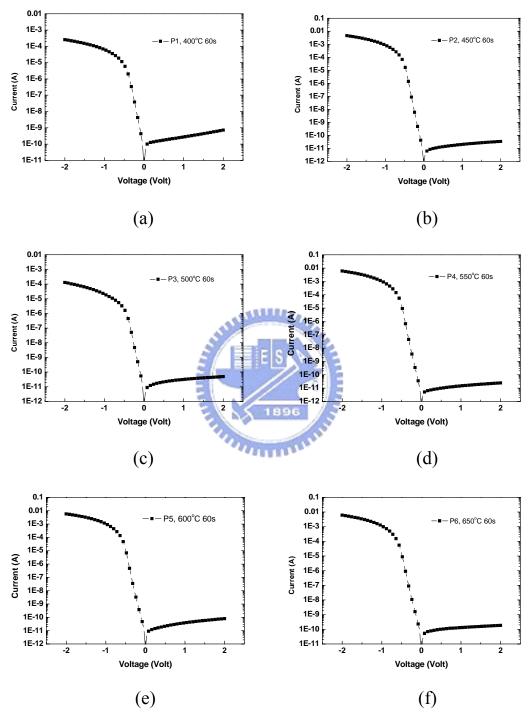

The experiment recipes of these samples prepared for this measurement was shown in Table.4.1. The I-V graphics were shown in Fig.4.5 and Fig.4.6. The measuring sweep voltage for N-sub samples was form 2V to -2V and P-sub was -2V to 2V. From the I-V curve, we could calculate the ideality factor by :

$$I = I_{s} \left( e^{\frac{qV}{kT}} - 1 \right)$$

$$\Rightarrow I = I_{s} e^{\frac{qV}{kT}} \quad as \ qV >> kT$$

$$\Rightarrow n = \frac{q}{kT} \frac{\partial V}{\partial(\ln J)}$$

(2)

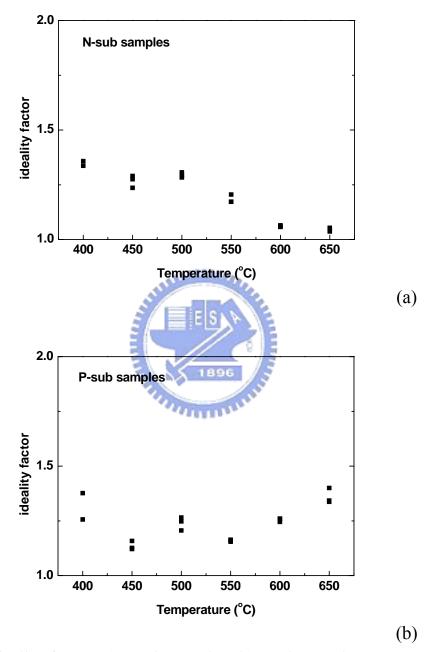

The current range which we used to extrapolate ideality factor was 0.4V to 0.04V for N-sub samples and -0.4V to -0.04V for P-sub samples. The ideality factor results for N and P samples were shown in Fig.4.7(a)(b) and the ideality factor for N samples had a tendency from low temperature anneal to high temperature but the P samples does not. The ideality factor would be affected by four factors : (1)contact resistance (2) generation-recombination current (3)substrate series resistance (4)high level injection. The ideality factor affected analysis for our experiment would be important. For the contact resistance, because our high implanted dosage, the

MS interface would turn from schottky contact to ohmic contact[1]. Because the substrate series resistance related to the bulk resistance, the N-sub samples would better than the P-sub samples but it does not the main reason. And the extrapolated current range does not the high level injection region so this does not dominate reason. In our opinion, the dominated factor might be due to the defect induced generation-recombination current. We could find the relationship by the Ion-Ioff current graphics. We took the Ion at 1/-1V and Ioff at -2/2V, the results was shown in Fig.4.8(a)(b). The Ioff is the reverse bias current and the reverse bias current is related to the Space Charge Region(SCR). The defects in SCR would provide generation-recombination center to affect the reverse current and ideality factor. For N-sub samples, the ideality factor was more and more lower, it is due to the high temperature anneal would recover the defects and the P+/N and N+/P interface moved away from the MS interface. Moreover, high temperature anneal would also activate the implanted bulk dopant so the N-sub samples had this tendency. In addition, the ideality factor of P-sub samples would affect apparently by the defects so the ideality factor of P-sub does not have a good tendency.

#### 4.3 C-V measurement

#### **4.3.1 C-V** measurement introduction

The capacitance-voltage(C-V) measurement was a method which could calculate dopant activation that silicide dopant segregation and pile-up at interface. In this part, the measured capacitance was depletion-layer capacitance and the model was shown in Fig.4.9. The depletion-layer

capacitance per unit area is defined as  $C_D=dQ_D/dV=\epsilon_S/W_D$ , where  $Q_D$  is the incremental depletion charge on each side of the junction(total charge is zero) upon an incremental charge of the applied voltage dV. For one-side abrupt junctions, the capacitance per unit area is given by :

$$C_D = \frac{\varepsilon_s}{W_D} = \sqrt{\frac{q\varepsilon_s N}{2}} (\psi_{bi} - V - \frac{2kT}{q})^{-1/2}$$

(3)

where V is positive/negative for forward/reverse bias. Rearrange the above equation leads to :

$$\frac{1}{C_D^2} = \frac{2}{q\varepsilon_s N} (\psi_{bi} - V - \frac{2kT}{q})$$

$$\frac{d(1/C_D^2)}{dV} = -\frac{2}{q\varepsilon_s N}$$

(4)

It is clear from Eqs.4 that by plotting  $1/C^2$  versus V, a straight line should result from a one-sided abrupt junction(Fig.4.10). The slope gives the impurity concentration of the substrate(N), and the extrapolation to  $1/C^2=0$  gives ( $\Psi_{bi}$ -2kT/q). The interface doping density can be calculate by the equations[2] :

$$N = -\frac{2dV}{q\varepsilon_{s}d(1/C_{D}^{2})}$$

(5)

$$\psi_{bi} = \frac{kT}{q} \ln \frac{N_{A}N_{D}}{n_{i}^{2}}$$

$$\Rightarrow N_{A} = \frac{n_{i}^{2}}{N_{D}} e^{\psi_{bi}q/kT} \text{ and } N_{D} = \frac{n_{i}^{2}}{N_{A}} e^{\psi_{bi}q/kT}$$

(6)

#### **4.3.2 Results and Discussion**

The C-V graphics were shown in Fig.4.11 and Fig.4.12. From C-V measurement, we used Eqs.5 to calculate the average substrate doping density and by plotting  $1/C^2$  versus V to obtain  $\Psi_{bi}$ . The results of  $\Psi_{bi}$  was shown in Fig.4.13(a)(b) and then combined Eqs.5 and Eqs.6 to obtain the doping density P+ and N+ region, as shown in Fig.4.14(a)(b). From above results, we could prove it again that when the annealing temperature was increasing, the doping density were more and more lower was due to the junction went away from interface. Moreover, the dopant activation was started to activate from the pile-up interface of MS. The phenomenon could also be explained that the C-V measurement was measure the junction interface. Because away from the MS interface, the measured result would exhibit the junction interface characteristic so that the higher temperature annealing showed the lower doping density.

#### **4.4** SIMS

We took the IIS N-sub and P-sub samples with 2<sup>nd</sup> RTA 650°C 60s for SIMS analysis. The graphics was shown in Fig.4.15(a)(b). From the SIMS graphics, we could observe the N-sub sample which had two boron peak. The first peak might be the dopant segregation at interface pile-up and the second peak might be the implanted dosage peak. It means that for N-sub sample the implanted energy was maybe too large. According to this result, we could have an another evidence to explain that the ideality factor of N-sub samples does better than P-sub samples. Because the measured I-V characteristic might be the second peak PN junction and at higher annealing temperature would cause dopant activation which excepted interface region so that the ideality factor was better than the P-sub samples. Another is the boron activated ability was higher than phosphorous. Moreover, the reverse bias current would also decrease, the reason was also the PN junction which we measured was away from the more defects MS interface. The SIMS for P-sub did have the result which we expected. It had the shallow junction characteristic and the pile-up just at the MS interface. The result could also explain why the ideality factor and reverse bias current were not good.

#### 4.5 References

- [1] C. Y. Sun, "Research of Low Temperature Activation Nickel Silicide and Interface properties", NCTU(2006)

- [2] S. M. Sze, Physics of Semiconductor Devices, 3<sup>rd</sup> ed., John Wiley & Sons, Taipei, (2007)

### Chapter 5

#### Conclusions

In this thesis, we have been investigated the activation of B and P implant into silicide (IIS) by RTA process. With the device scale down, the shallow junction would be important because shallow junction formation can effectively suppress short channel effect(SCE). Based on the IIS dopant segregation pile-up at interface and SPER, our experiment would achieve the high dosage activation and do not use high temperature annealing. We could find the best recipes for the device fabrication in the future. In the first part experiment, regardless of N and P-sub samples at 550°C annealing that are all had better sheet resistance which compared with conventional high temperature annealing. In spite of overetching time was taken for 30s, the sheet resistance values also closed to the conventional samples. In second part experiment, we would use another method to measure the activation condition. By the C-V and I-V measurement, we could realize the interface dopant distribution and the integrity of P/N or N/P junction. All in all, we achieved our purposes by means of the experiment and the results were beneficial.

# **Chapter 6**

### **Future Work**

In order to improve the shallow junction properties, we could make some experiments to revise it in the future. We could use Spreading Resistance Profiling(SRP) to check the junction depth and the doping density. According to the actuality junction depth, we could also know that our fabricated junction does conform to the shallow junction condition or not. In addition, we could also find the optimum value of annealing temperature. As long as the doping activation density can attain our expectation at more lower annealing temperature, we can replace the high temperature fabrication.

|                     | Resistivity | Silicidation        | Silicon         | Moving  | Film                 |

|---------------------|-------------|---------------------|-----------------|---------|----------------------|

|                     | (μΩ-cm)     | Temperature<br>(°C) | Consumption     | Species | Stress<br>(dyn/cm2)  |

| TiSi <sub>2</sub>   | 12-15       | 800-950             | 0.9× T          | Si      | 1.5×10 <sup>10</sup> |

| CoSi                | -           | 375-500             | 0.91× T         | Si      | -                    |

| CoSi <sub>2</sub> . | 18          | 550-900             | E 1.04× T       | Со      | 1.2×10 <sup>10</sup> |

| NiSi                | 15-16       | 350-700             | 1896<br>0.82× T | Ni      | 6×10 <sup>9</sup>    |

| NiSi <sub>2</sub>   | 35-50       | 700-850             | -               | Ni      | -                    |

T stands for thickness of silicide formed

Table.1.1 Comparison the characteristics of Ti, Co and Ni silicides.

Fig.1.1 With/without bridging phenomenon of metal silicides.

| Process Name          | P856             | P858             | Px60             | P1262            | P1264            | P1266    | P1268          | P1270          |

|-----------------------|------------------|------------------|------------------|------------------|------------------|----------|----------------|----------------|

| 1st Production        | 1997             | 1999             | 2001             | 2003             | 2005             | 2007     | 2009           | 2011           |

| Process<br>Generation | 0.25μm           | 0.18µm           | 0.13μm           | 90 nm            | 65 nm            | 45 nm    | 32 nm          | 22 nm          |

| Wafer Size<br>(mm)    | 200              | 200              | 200/300          | 300              | 300              | 300      | 300            | 300            |

| Inter-connect         | AI               | Al               | Cu               | Cu               | Cu               | Cu       | Cu             | ?              |

| Channel               | Si               | Si               | Si               | Strained<br>Si   | Strained<br>Si   | Strained | Strained<br>Si | Strained<br>Si |

| Gate dielectric       | SiO <sub>2</sub> | High-k   | High-k         | High-k         |

| Gate electrode        | Poly-<br>silicon | Poly-<br>silicon | Poly-<br>silicon | Poly-<br>silicon | Poly-<br>silicon | Metal    | Metal          | Metal          |

| CE H                  | Intro            | oduction         | n targete        | d at this        | s time           | Sub      | ject to ch     | ange           |

Fig.1.2 Continuation of Moor's Law from intel's high-k/metal gate announcement (2003)

**Fig.2.1** Results of nickel silicide sheet resistance: (a) Dual E-Gun Evaporation System (b) Sputtering System

**Fig.2.2** Results of RTA2, 550°C 50sec, treatment to forming NiSi: (a) Dual E-Gun Evaporation System (b) Sputtering System

**Fig.2.3** Results of nickel silicide sheet resistance: (a)first RTA  $350^{\circ}$ C with different time for PECVD and HDPCVD a-Si samples (b)all samples were treated by second RTA  $550^{\circ}$ C 50sec

|            | 1 <sup>st</sup> RTA | 2 <sup>nd</sup> RTA |

|------------|---------------------|---------------------|

| E-gun Ni   | 350/400°C           | 550℃ 50s            |

|            | 10/20/30/45/60s     |                     |

| Sputter Ni | 350/400°C           |                     |

|            | 10/20/30/40/50/60s  |                     |

**Table.2.1** The recipes of Nickel silicide formation for different Ni

deposition system

| Sulling .   |                     |                     |  |  |  |

|-------------|---------------------|---------------------|--|--|--|

|             | 1 <sup>st</sup> RTA | 2 <sup>nd</sup> RTA |  |  |  |

| PECVD a-Si  | 350°C               | 550°C 50s           |  |  |  |

| HDPCVD a-Si | 30/60/90/120s       |                     |  |  |  |

**Table.2.2** The recipes of Nickel silicide formation for different a-Si deposition system

**Fig.2.4** (a)SEM image for nickel silicide which was formed by Sputtering System Ni with single crystalline Si (b)silicide thickness versus square root of time

**Fig.2.5** (a)SEM image for nickel silicide which was formed by Dual E-Gun Evaporation System Ni with single crystalline Si (b)silicide thickness versus square root of time

**Fig.2.6** SEM image of nickel silicide which was formed by Dual E-Gun Evaporation System Ni with PECVD deposited a-Si

**Fig.3.1** AFM inspection image of Si substrate etched by silicide etching solvent for 30min

### **Process flow of experimental samples**

Fig.3.2 Process flow of P+N and N+/P junction by IIS scheme

## **Process flow of comparison samples**

**Fig.3.3** Process flow of P+N and N+/P junction for comparison samples scheme

|             | Implanted ion                             | 1st RTA      | 2nd RTA                    |

|-------------|-------------------------------------------|--------------|----------------------------|

| P substrate | P <sup>+</sup> /30 kev/5E15               | 350°C/30 sec | 400 ~ 650°C<br>30 / 60 sec |

| N substrate | BF <sub>2</sub> <sup>+</sup> /50 kev/5E15 | 350℃/30 sec  | 400 ~ 650°C<br>30 / 60 sec |

**Table.3.1** Process recipe of P+N and N+/P junction by IIS scheme.

|             | Implanted ion                             | RTA                        |  |  |  |

|-------------|-------------------------------------------|----------------------------|--|--|--|

| P substrate | P <sup>+</sup> /28 kev/5E15               | 600 ~ 950°C<br>30 / 60 sec |  |  |  |

| N substrate | BF <sub>2</sub> <sup>+</sup> /43 kev/5E15 | 600 ~ 950℃<br>30 / 60 sec  |  |  |  |

**Table.3.2** Process recipe of P+N and N+/P junction for comparison samples scheme.

**Fig.3.4** Process flow of P+/N and N+/P junction samples of silicide contact for I-V and C-V electrical properties measurement.

**Fig.4.1** The IIS samples compared with conventional high temperature anneal (a) N-sub Si implanted  $BF_2$  (b) P-sub Si implanted Phosphorous

**Fig.4.2** The comparison of different Si-sub implanted different dopant (a) IIS samples compared (b) conventional high annealing samples compared

**Fig.4.3** The experiment of counter dopingwas N-sub wafer to form silicide and implanted  $BF_2$  then annealed at 400°C 5/15/30/60s, respectively.

**Fig.4.4** The relationship of doping Si-sub etching time versus reciprocal resistance.

|             | Implanted ion                             | 1st RTA      | 2nd RTA               |

|-------------|-------------------------------------------|--------------|-----------------------|

| P substrate | P <sup>+</sup> /30 kev/5E15               | 350°C/30 sec | 400 ~ 650°C<br>60 sec |

| N substrate | BF <sub>2</sub> <sup>+</sup> /50 kev/5E15 | 350°C/30 sec | 400 ~ 650℃<br>60 sec  |

Table.4.1 Recipes of IIS for I-V and C-V measured experiment

**Fig.4.5** (a)~(f) I-V graphics for IIS N-sub samples

Fig.4.6 (a)~(f) I-V graphics for IIS P-sub samples

Fig.4.7 ideality factor (a)N-sub samples (b)P-sub samples

**Fig.4.8** Ion-Ioff relation graphics(a)N-sub samples (b)P-sub samples (Ion : Forward bias at 1V and Ioff : Reverse bias at 2V)

**Fig.4.9** Abrupt p-n junction in thermal equilibrium. (a)Space-charge distribution. Dashed lines indicate corrections to depletion approximation. (b)Electric-field distribution. (c)Potential distribution where  $Vbi(\Psi_{bi})$  is the built-in potential. (d)energy-band diagram.

**Fig.4.11** (a)~(f) C-V graphics for IIS N-sub samples

Fig.4.12 (a)~(f) C-V graphics for IIS P-sub samples

Fig.4.13  $\Psi_{bi}$  (a)N-sub samples (b)P-sub samples

**Fig.4.14** The dopant activation density of IIS at MS interface (a)Boron doping density for N-sub samples (b)Phosphorous doping density for P-sub samples

**Fig.4.15** SIMS analysis for IIS samples  $2^{nd}$  RTA  $650^{\circ}$ C 60s (a)Boron distribution of N-sub sample (b)Phosphorous distribution of P-sub sample

簡歷

- 姓 名:楊志祥

- 性 别:男

- 出生日期:民國72年7月16日

- 出 生 地:台灣省雲林縣

- 住 址:台北縣新莊市成德街 22號1樓

- 學 歷:私立元智大學電機工程學系

(民國 90 年 9 月~民國 94 年 6 月)

國立交通大學電子工程研究所

(民國 94 年 9 月~民國 96 年 7 月)

碩士論文:形成矽化鎳時在矽化鎳與矽接面處離子活化相關研究

Research of Dopant Activation at the Interface between Nickel Silicide and Silicon during Nickel Silicide Formation