# 國立交通大學

電子工程學系電子研究所

博士論文

氮化矽快閃式記憶元件可靠度之探討

# Investigation of Reliability Issues in Nitride Trap Storage Flash Memory

研究生: 古紹泓

指導教授:汪大暉 博士

中華民國九十五年十一月

# 氮化矽快閃式記憶元件可靠度之探討

# Investigation of Reliability Issues in Nitride Trap Storage Flash Memory

研究生:古紹泓 Student:Shaw-Hung Gu

指導教授:汪大暉 博士 Advisor: Dr. Tahui Wang

國立交通大學電子工程學系 電子研究所博士班博士論文

# A Dissertation

Submitted to Department of Electronics Engineering & Institute of Electronics

College of Electrical and Computer Enginerring

National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

in

Electronics Engineering

November 2006

Hsinchu, Taiwan, Republic of China

中華民國九十五年十一月

# 氮化矽快閃式記憶元件可靠度之探討

學生: 古紹泓 指導教授: 汪大暉 博士

國立交通大學 電子工程學系 電子研究所

## 摘要

本篇論文主要著重在研究以氮化矽(SiN)為電荷儲存之快閃式記憶元件可靠性議題(reliability issue)研究。一般而言,為了增加電荷保存能力(retentivity),此元件通常選用較厚的底部氧化層(bottom oxide)。元件在未加壓之前,其具有相當優異的可靠度。然而,當經過多次寫入/抹除(program/erase)後,會使得氧化層造成傷害,進而對元件可靠性造成極大的影響。

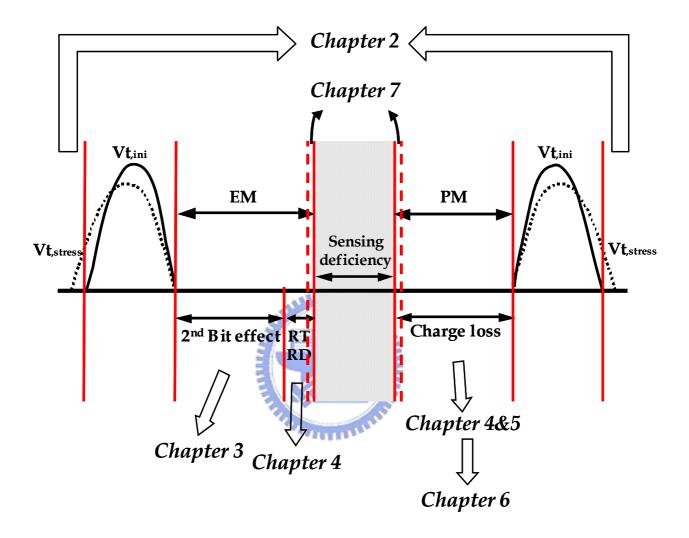

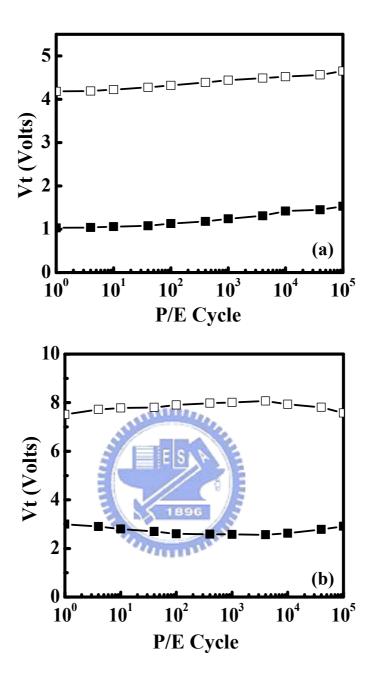

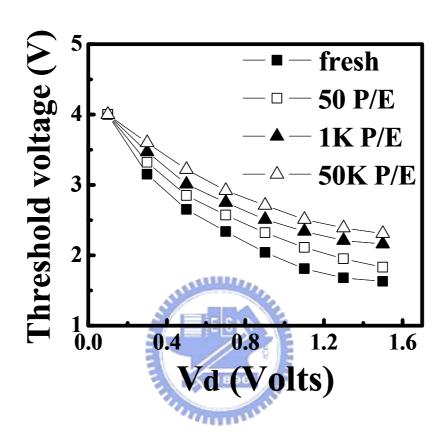

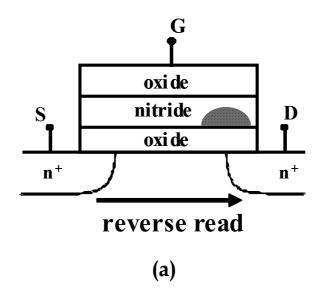

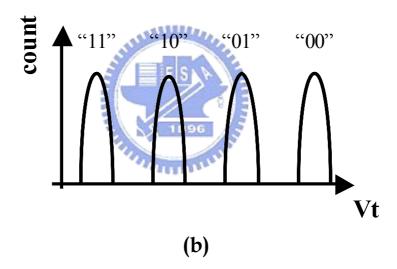

第一章簡介此元件基本的結構以及寫入抹除的方式。對於二位元操作時反向 讀取(reverse reading)的原理,也詳列於其中。第二章探討元件耐久性(endurance) 機制。吾人發現,無論在寫入或抹除狀態之臨界電壓準位,皆會隨著寫入/抹除 次數的增加而皆有向上揚升的現象。

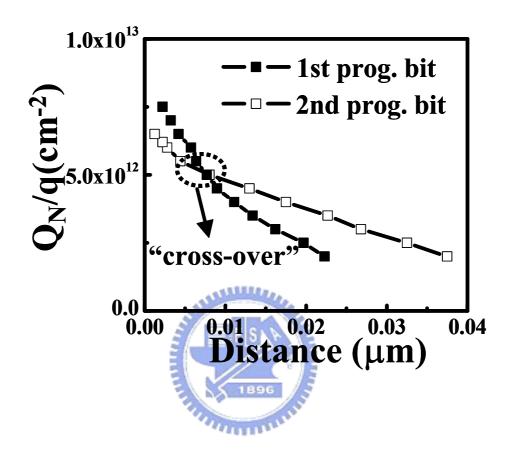

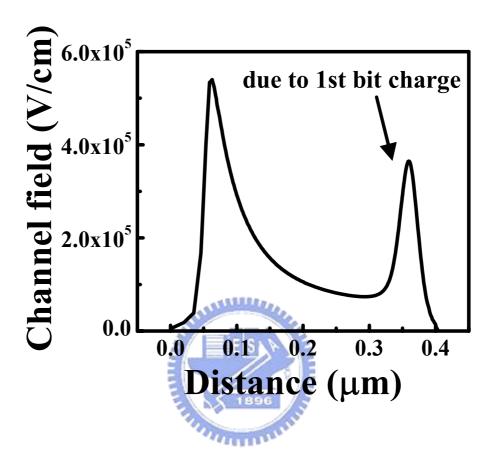

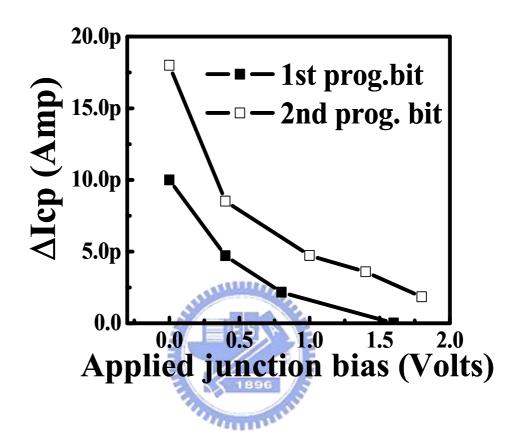

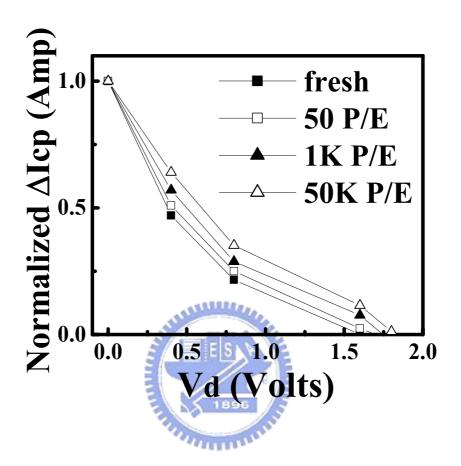

第三章詳述一改良後之電荷幫浦(charge pumping)量測方法。藉由此法,在 汲極/源極接面上之寫入電荷水平分佈,可獨立被萃取出來。吾人研究發現,在 同一元件中,第二寫入的位元有著比第一寫入位元較寬的電荷分佈。此原因為在 寫入第二位元時,第一寫入位元產生的電場會加速通道電子使其提早注入氮化矽 層中。另外,實驗結果顯示,寫入電荷分佈會隨著寫入抹除次數增加而延伸到通 道中央。

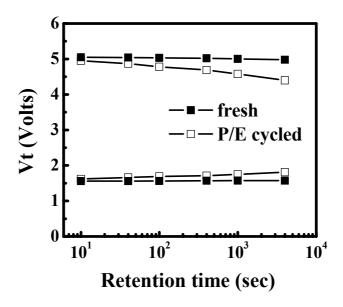

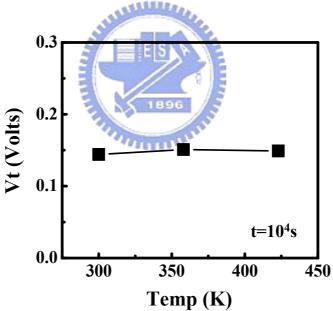

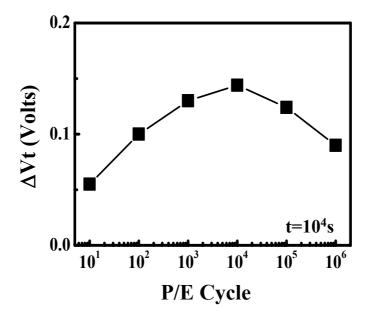

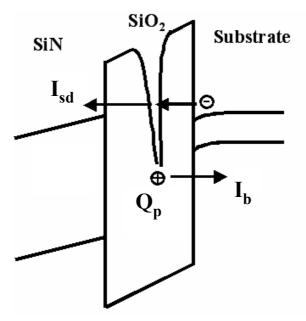

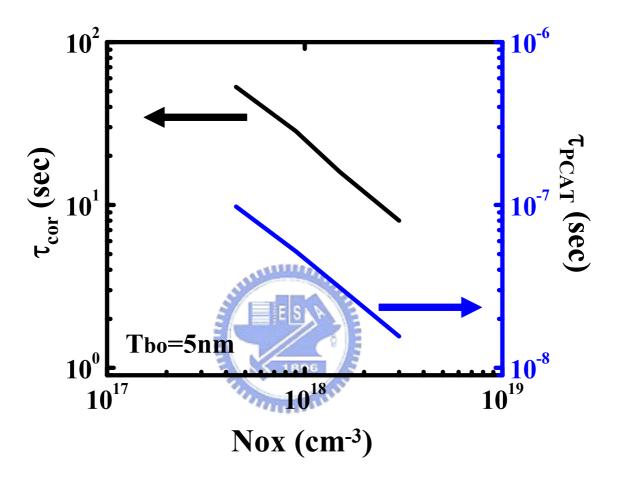

第四章中,吾人對抹除狀態臨界電壓不穩定(threshold voltage instability)、 讀取擾動(read-disturb),以及寫入狀態資料流失(charge loss)有著深入的探討。 首先,對於一經加壓後的元件,抹除狀態之臨界電壓會隨著儲存時間而上升。此 漂移現象與溫度有著微弱的關係並且隨寫入抹除次數呈現奇特的轉彎現象 (turn-around),這與底部氧化層中帶正電性缺陷的生成有著密切關係。吾人實驗結果發現,此臨界電壓漂移與時間呈現對數 (logarithm)的相依性,並可用穿隧波前(tunneling front)模型來做描述。此外,若是讀取偏壓太大,正電性電荷幫助穿隧(PCAT)效應將會主導臨界電壓漂移,與時間將會轉變成指數(power-law)關係。藉由研究垂直電場以及溫度對氮化矽層電荷遺失之影響,吾人提出一解析之物理模型:Frenkel-Poole蒸散進而透過氧化層缺陷穿隧。吾人可利用此模型提出一閘極偏壓加速測試元件資料保存時間之方法。

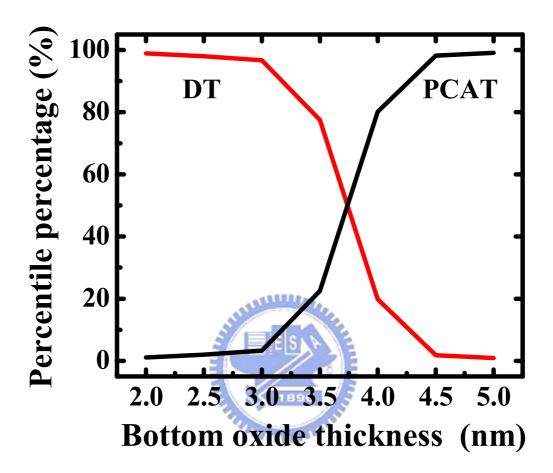

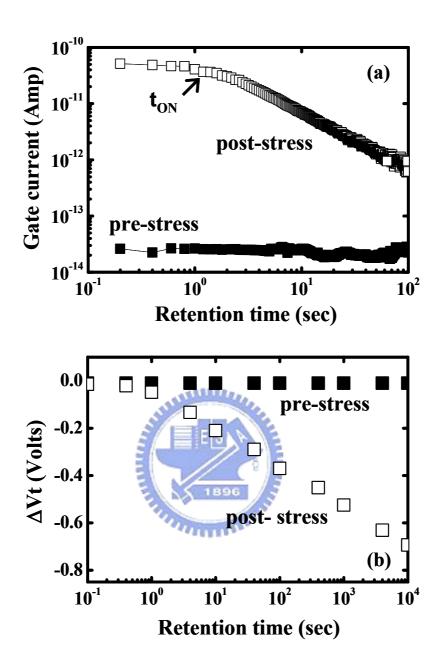

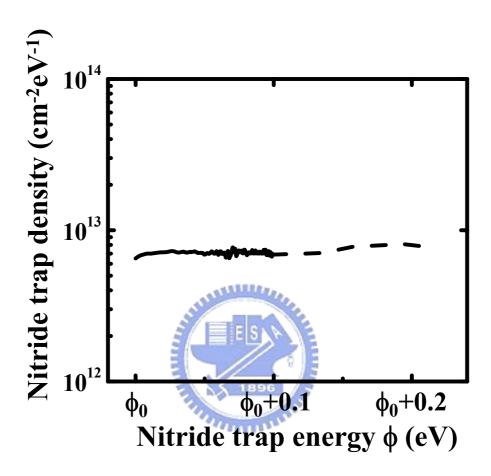

第五章探討底部氧化層厚度以及加壓效應對於氮化矽記憶元件資料流失的影響。根據多電子捕捉(multiple electron trapping)模型,吾人利用一數值分析方法,分別對底部氧化層厚度為 1.8nm 到 5.0nm 的元件模擬其電荷保存特性。在吾人的模型中,假設氮化矽中缺陷為連續性的分佈。傳導帶(conduction band)與氮化矽中缺陷狀態(trap state)的暫態行為,可用一連串 Frenkel-Poole 激發以及電子再度被捕陷(re-capture)來描述。電荷流失可分為兩種途徑:一是傳導帶電子透過正電性氧化層缺陷而流失;二是電子直接穿隧過底部氧化層而散失。透過大面積元件量測,吾人發現在較厚的底部氧化層元件中,經由加壓後引致的電荷逸失現象呈現兩階段(two stages)發展。第一階段電荷漏電流被氧化層缺陷幫助穿隧給限制住。第二階段中,因 Frenkel-Poole 散失使其而遵循 1/t 的時間關係。從第一階段到第二階段之間的過渡時間與氧化層缺陷幫助穿隧時間有關,但是將會被延長一個特定比例。基於以上的了解,吾人在第六章中,利用此 1/t 暫態電流,萃取出氮化矽材料中缺陷的密度。

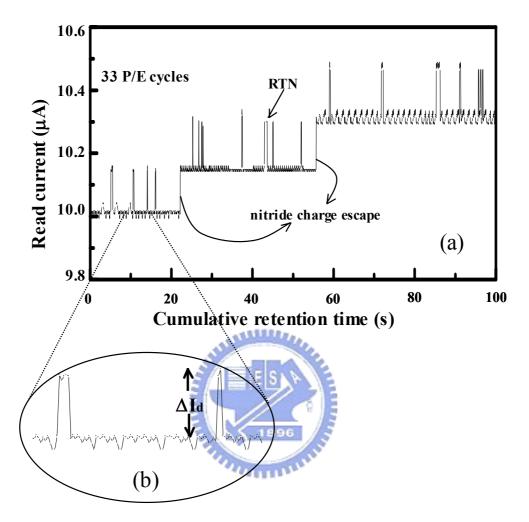

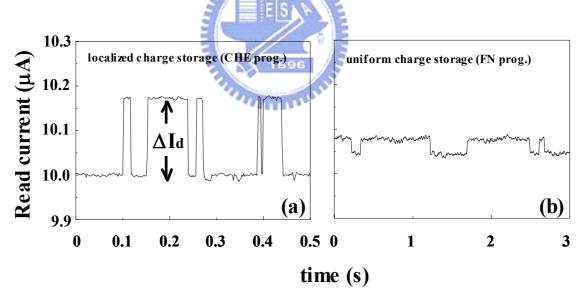

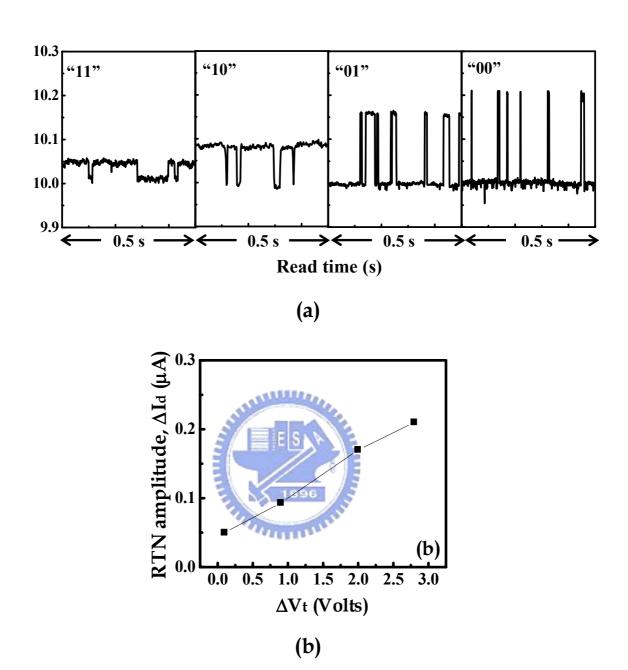

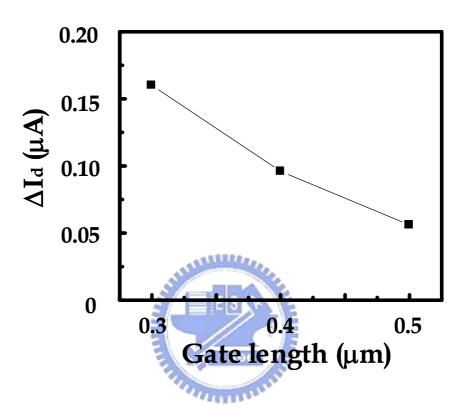

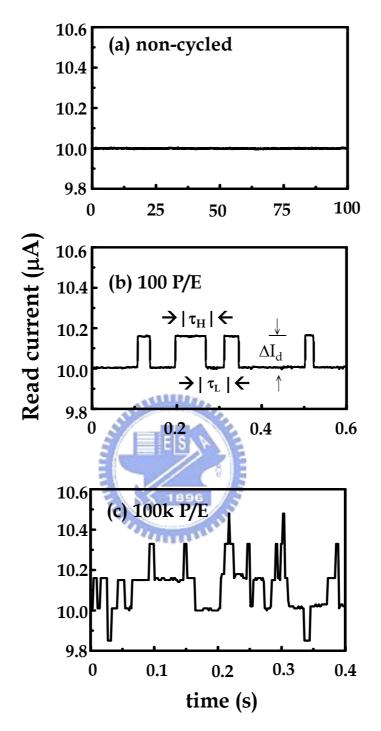

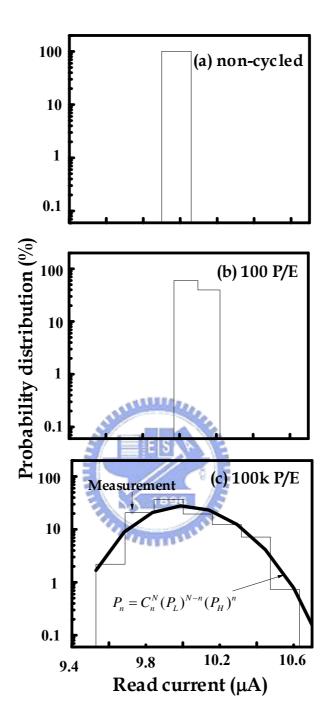

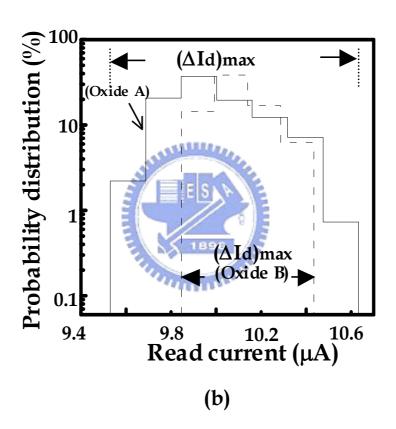

第七章中,吾人針對一局部儲存(localized storage)、多準位(multi-level)氮化矽快閃式記憶元件中,因寫入/抹除加壓後產生隨機電報雜訊(random telegraph noise, RTN)導致之讀取電流擾動作一深入之探討。吾人發現,局部儲存方式明顯地增加 RTN 的擾動。而 RTN 的振幅隨著不同的寫入準位而改變。用一機率模型,可定義此 RTN 造成的讀取電流擾動分佈。例外,利用較好的底部氧化層製程方法,可有效降低此讀取電流雜訊。

最後於第八章, 吾人將對本論文做個總結。

關鍵字: 氮化矽快閃式記憶元件, 耐久性, 電荷幫浦量測, 寫入電荷水平分佈, 抹除狀態 臨界 電壓不穩定, 讀取擾動, 寫入狀態資料流失, 穿隧波前模型, Frenkel-Poole 散失, 底部氧化層厚度, 多電子捕捉模型, 讀取電流擾動, 隨機電報雜訊

**Investigation of Reliability Issues in Nitride Trap**

**Storage Flash Memory**

Student: Shaw-Hung Gu

Advisor: Dr. Tahui Wang

Department of Electronics Engineering & Institute of Electronics,

National Chiao Tung University

Abstract

This thesis will focus on the reliability issues of SONOS-type trapping storage

flash memories. For today's SONOS cells, a thicker bottom oxide is employed to

improve the retentivity. These cells exhibit excellent data retention behavior before

stress. After P/E cycling, the bottom oxide is damaged, thereby degrading the

reliability.

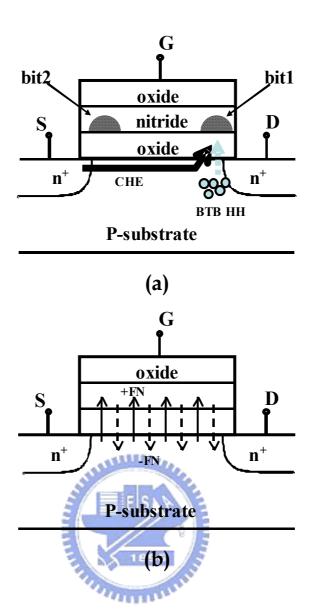

In Chapter 1, the device structure and program/erase methods of the cell are

described. A reverse read scheme for two-bit operation is illustrated. With respect to

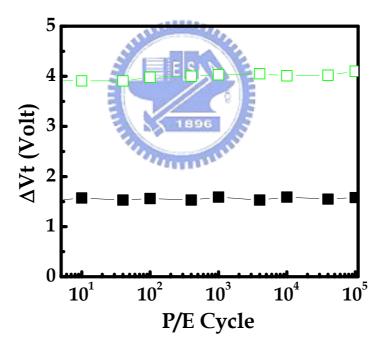

the cell endurance, the threshold voltage in program-state or in erase-state may shift

upward as P/E cycle number increases. The mechanism will be investigated in

Chapter 2.

iii

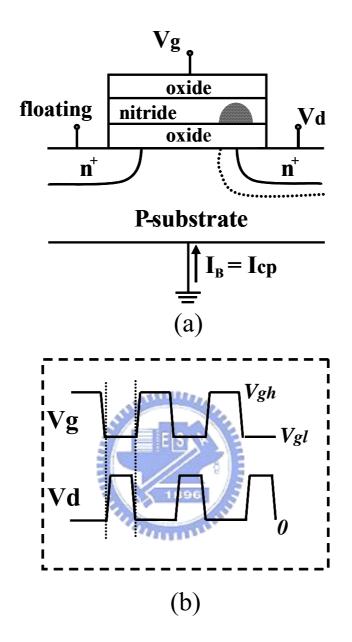

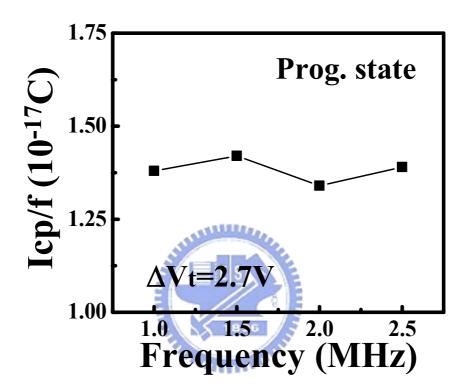

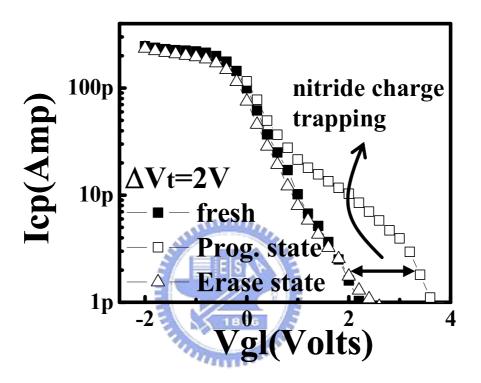

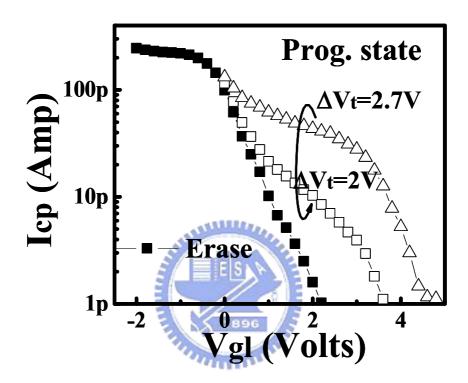

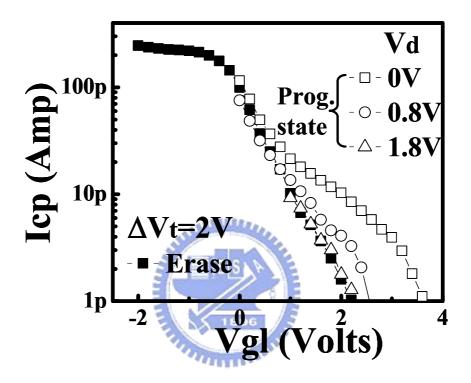

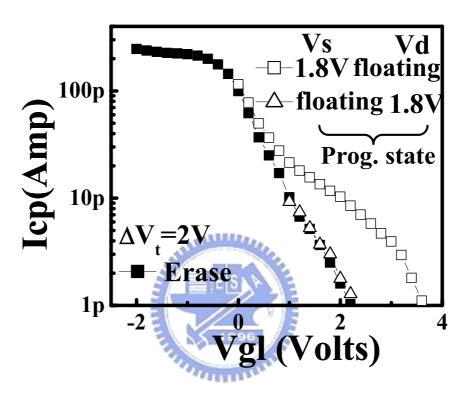

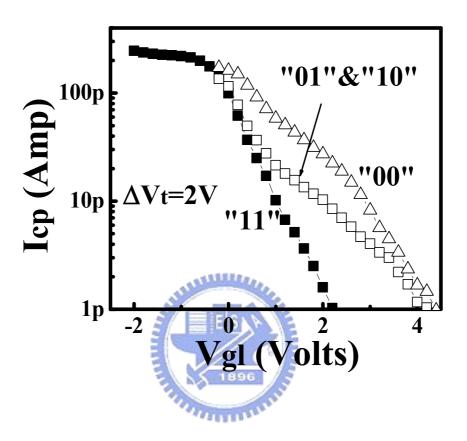

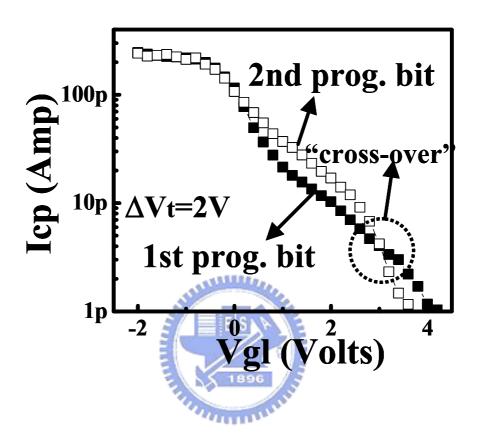

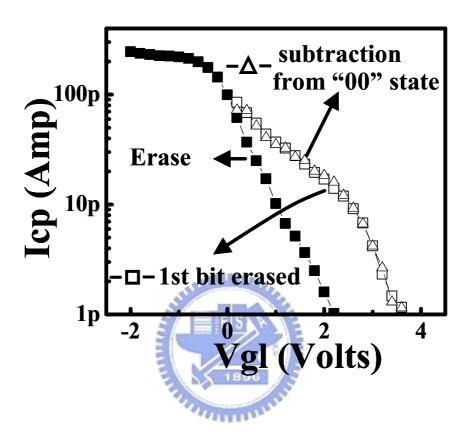

To expound the second-bit effect, a modified charge pumping technique to characterize programmed charge lateral distribution is proposed in Chapter 3. The stored charge distribution of each bit over the source/drain junctions can be profiled separately. Our result shows that the secondly programmed bit has a broader stored charge distribution than the first programmed bit. The reason is that a large channel field exists under the first programmed bit during the second bit programming. Such a large field accelerates channel electrons and causes earlier electron injection into the nitride. In addition, we find that programmed charges spread further into the channel as program/erase cycle number increases.

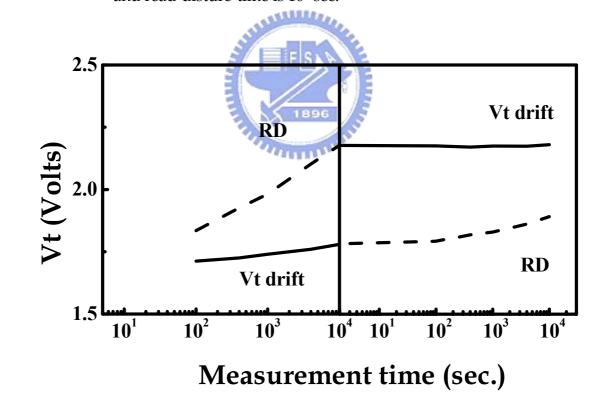

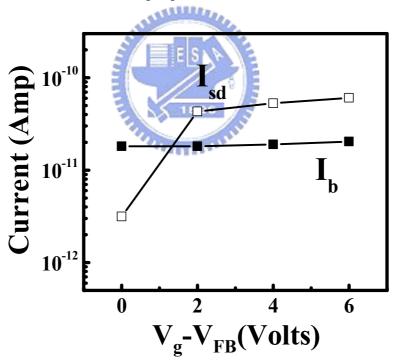

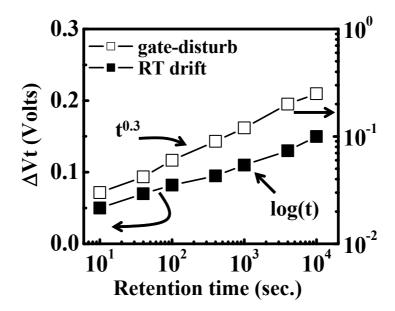

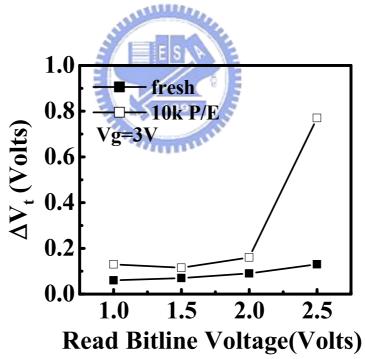

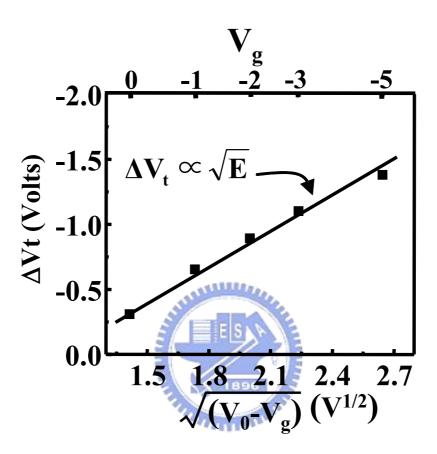

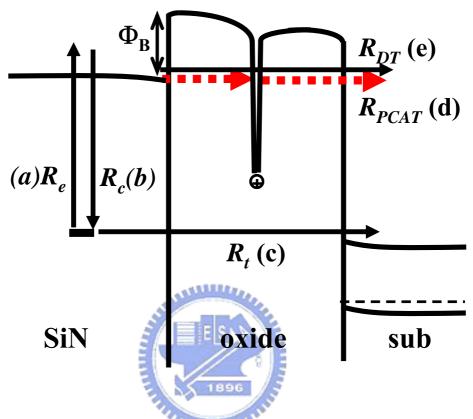

Reliability issues including erase-Vt state threshold voltage instability, read-disturb, and high-Vt state charge loss will be addressed in Chapter 4. First, an erase-state threshold drift with storage time is observed in a P/E cycled cell. This drift has insignificant temperature dependence and exhibits an anomalous turn-around with P/E cycle number. This peculiar phenomenon is strongly related to the creation of positive charged defects in the bottom oxide. The temporal evolution of the threshold voltage drift has log(t) dependence on storage time and can be well described by the tunneling front model. Furthermore, at a sufficiently large read bias, positive charge assisted channel electron tunneling dominates the threshold voltage shift, causing a power-law time relation. By measuring the dependence of electric field and temperature, an analytical model based on Frenkel-Poole emission followed by oxide trap assisted tunneling successfully identifies the mechanism for charge loss. With use this model, a Vg acceleration method for retention lifetime test is also proposed.

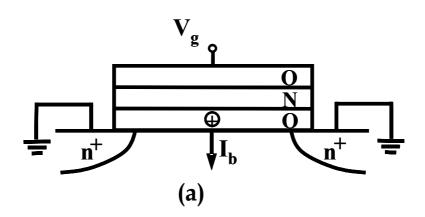

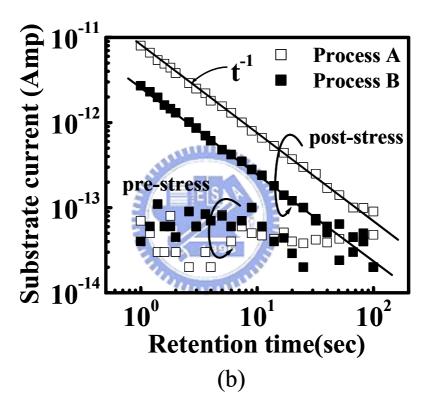

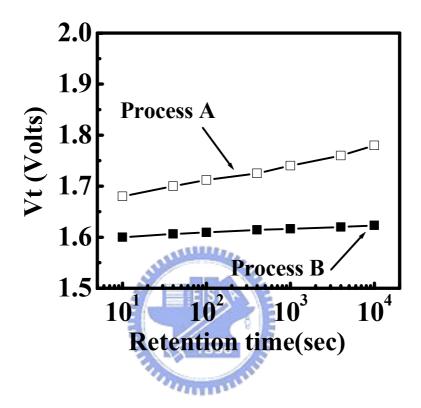

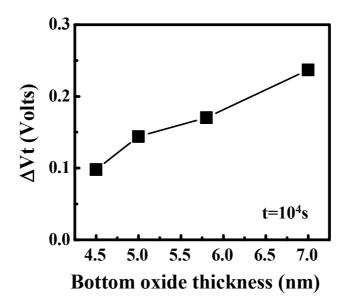

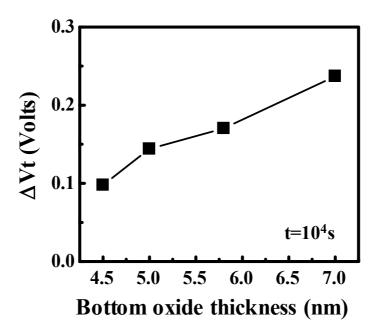

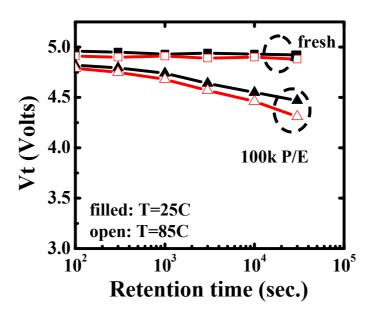

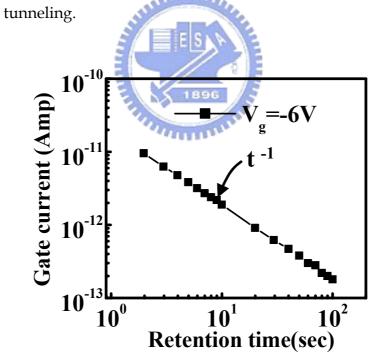

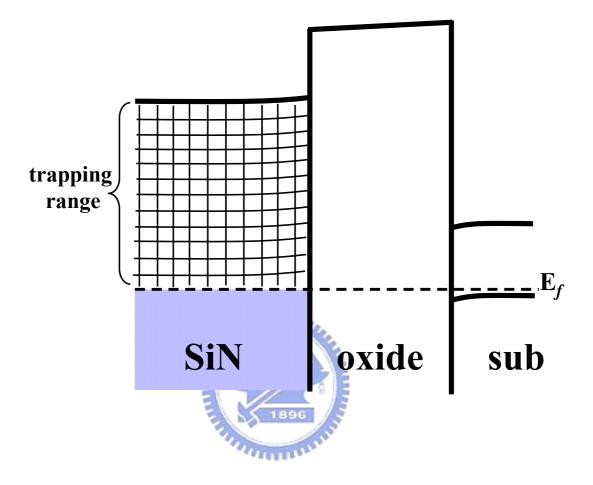

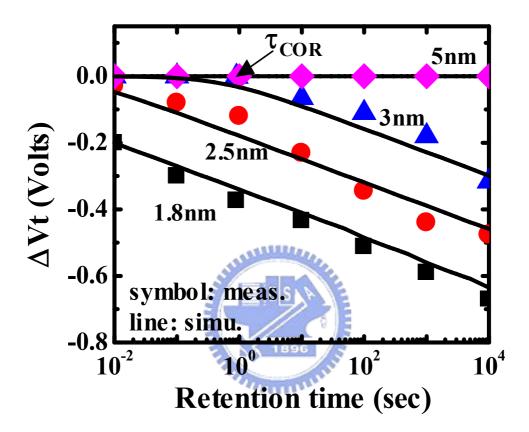

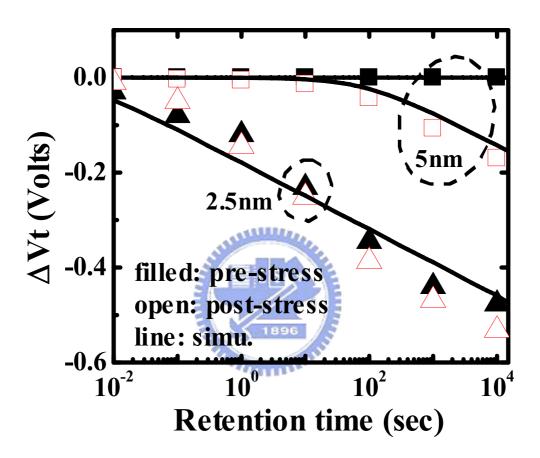

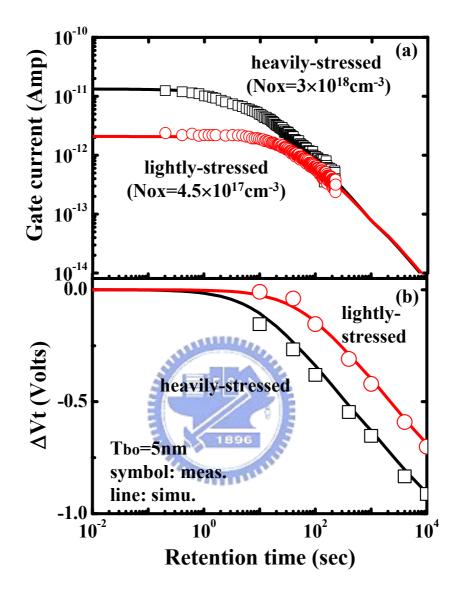

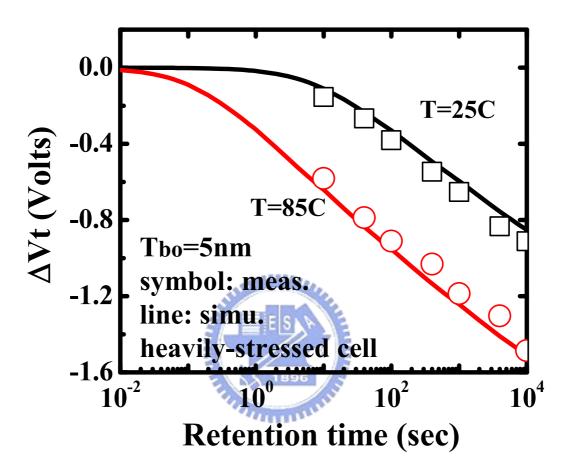

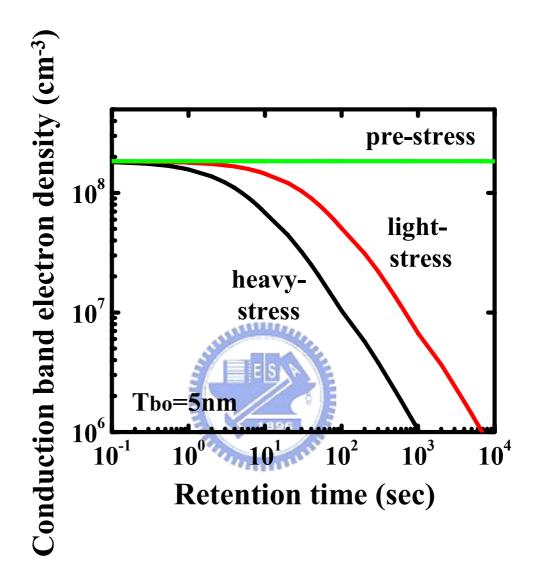

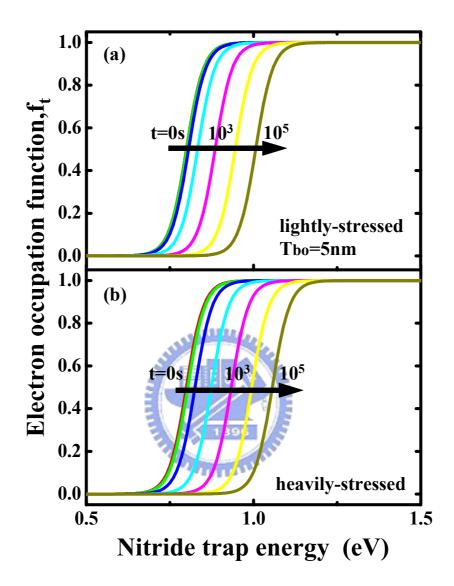

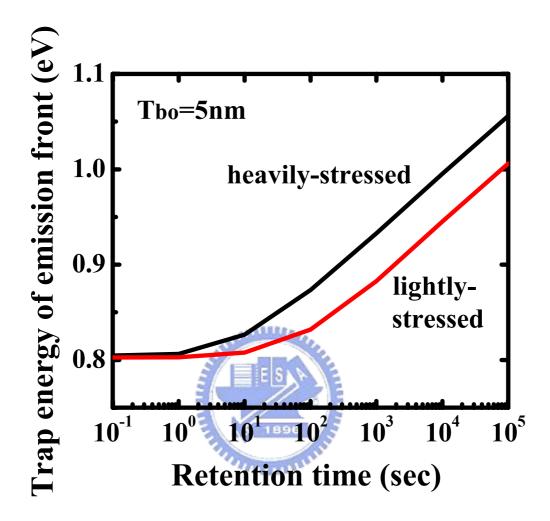

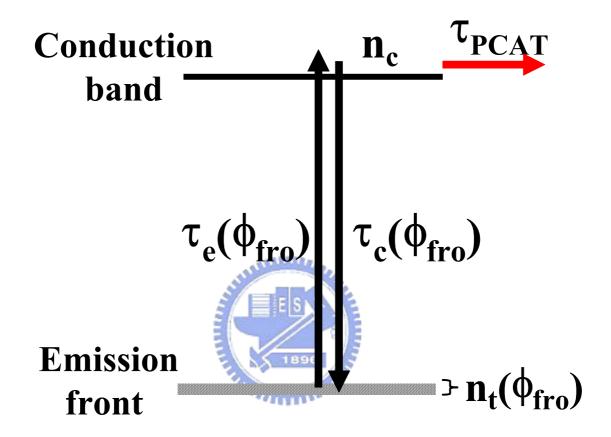

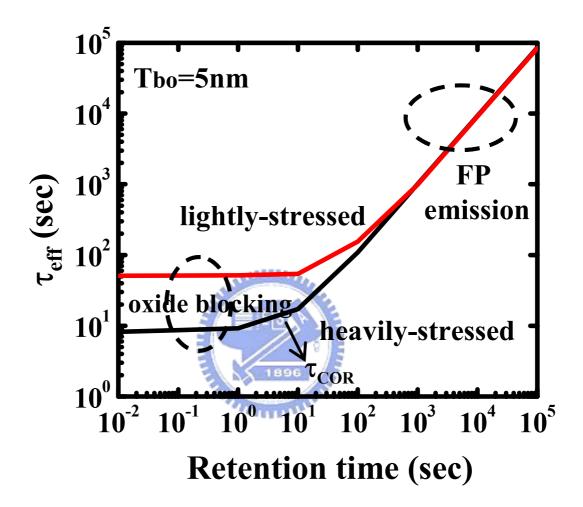

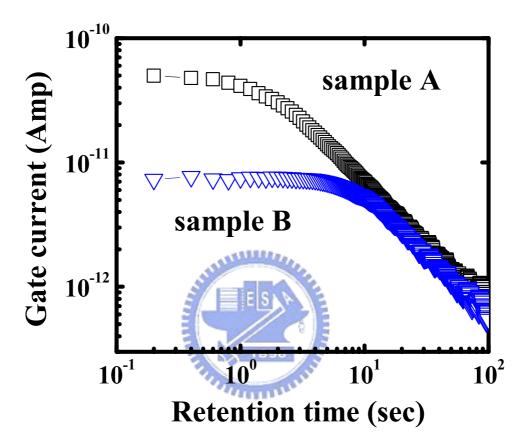

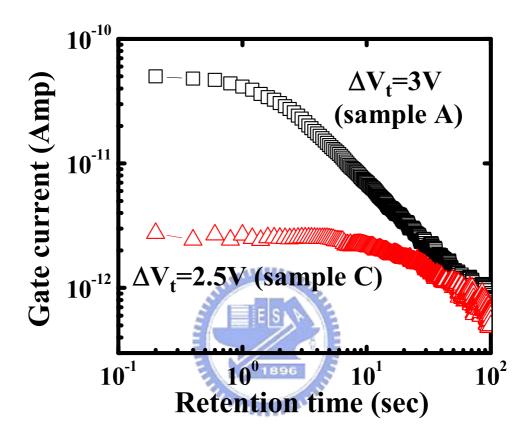

Bottom oxide thickness and program/erase stress effects on charge retention in SONOS flash memory cells with FN programming are investigated. Utilizing a numerical analysis based on a multiple electron trapping model, the electron retention behavior in a SONOS cell with bottom oxide thickness from 1.8nm to 5.0nm is simulated. In our model, the nitride traps have a continuous energy distribution. A series of Frenkel-Poole excitation of trapped electrons to the conduction band and electron re-capture into nitride traps feature the transitions between the conduction band and trap states. Conduction band electron tunneling via positively charged oxide traps created by high-voltage stress and trapped electron direct tunneling through the bottom oxide is included to describe various charge leakage paths. We measure the nitride charge leakage current directly in a large area device for comparison. Our study reveals that the charge retention loss in a high-voltage stressed cell with a thicker bottom oxide (5nm) exhibits two stages. The charge leakage current is limited by oxide trap assisted tunneling in the first stage and then follows a 1/t time dependence due to the Frenkel-Poole emission in the second stage. The transition time from the first stage to the second stage is related to oxide trap assisted tunneling time, but is prolonged by a factor. According to the above understanding, the silicon nitride trap density can be extracted from the 1/t transient current in Chapter 6.

In Chapter 7, program/erase stress induced read current fluctuation arising from random telegraph noise (RTN) in a localized, multi-level SONOS cells is explored. Our study shows that localized charge storage significantly enhances RTN. The amplitude of RTN varies in different program levels of a multi-level cell. The

broadening of read current distribution caused by RTN is characterized and modeled.

Better bottom oxide process can reduce read current noise.

Conclusions are finally made in Chapter 8.

Keyword: SONOS-type trapping storage flash memories, Endurance, Charge pumping technique, Programmed charge lateral distribution, Erase-Vt state threshold voltage instability, Read-disturb, High-Vt state charge loss, Tunneling front model, Frenkel-Poole emission, Bottom oxide thickness, Multiple electron trapping model, Read current fluctuation, Random telegraph noise

## **ACKNOWLEDGEMENT**

First of all, I would like to express my deepest gratitude to my advisor Prof. Tahui Wang for his continuous guidance and encouragement. Without his teaching, I cannot complete my dissertation.

I also show my appreciation to all of my committee for their suggestions and comments. Moreover, I would acknowledge Mr. Wen-Pin Lu and all the members in MD320 for their kindly support during my part-time job.

During my study, many important persons have influenced me. Mr. L. P. Chiang, Mr. N. K. Zous, Mr. C. C. Yeh, Mr. M. H. Lin, Mr. C. W. Tsai, Mr. M. C. Chen, and J. W. Wu have taught me a lot of invaluable knowledge; special thanks are given to Mr. C. T. Chan, Mr. H. K. Chiang, Mr. C. C. Cheng, Mr. H. C. Ma, and Mr. C. J. Tang for sharing experience together. In particular, the assistance in measurement from Mr. M. T. Wang, Mr. C. W. Hsu, Mr. C. W. Lee, and Mr. Z. H. Lee is also greatly appreciated.

Thank for Mr. C. C. Lin and W. F. Lei from Shihmen Rotary Club (District 3480) to recommend me winning the scholarship in Chung Hwa Rotary Education Foundation.

Finally, I would present the deepest love to my parents and Mrs. Ching-Yi Chiu. Their love is the most important power supporting me. This dissertation is dedicated to them.

# 謝誌

首先,要感謝的是我的指導教授汪大暉博士,在我碩士到博士班期間的指導 與鼓勵。從汪老師身上我學到了身為一個博士班學生對於研究所須有的負責與嚴 謹的態度。沒有汪老師的教誨,也沒有這本論文的誕生。

特別感謝論文口試委員在百忙之中前來給予我寶貴的建議與指導。另外,在 旺宏電子工讀期間,技術開發處呂文彬處長以及製程技術研發二處全體同仁在研 究與工作上的大力協助,在此表達由衷的感謝。

在求學過程中,感謝蔣汝平學長、鄒年凱學長、葉致鍇學長、林明賢學長、蔡慶威學長、陳旻政學長、吳俊威學長的經驗傳承,以及詹前泰先生、江欣凱先生、鄭志昌先生、馬煥淇先生、唐俊榮先生的意見分享。此外,感謝王銘德先生、許智維先生、李致維先生、李智雄先生在實驗工作上的分擔。因為有你們的協助,使得這本論文更為充實。

感謝 3480 地區西門扶輪社林錦江先生與雷萬福先生推薦,使得我獲得財團 法人中華扶輪教育基金會獎學金,減輕我的經濟負擔。

最後,感謝我的家人長久以來無怨無悔的付出與關心,使得我能專心一至地 投入在研究中。也謝謝我的女友靜儀,她的愛是我繼續前進的動力。在此,將這 本論文獻給我深愛的家人與女友。

# **CONTENTS**

| Chinese Ab         | stract                                                                             | i    |

|--------------------|------------------------------------------------------------------------------------|------|

| <b>English Abs</b> | stract                                                                             | iii  |

| Acknowled          | gements                                                                            | vii  |

| Contents           |                                                                                    | ix   |

| Table Capti        | ons                                                                                | xii  |

| <b>Figure Capt</b> | ions                                                                               | xiii |

| List of Sym        | bols                                                                               | xxi  |

| Chapter 1          | Introduction                                                                       | 1    |

| 1.1                | Background                                                                         | 1    |

| 1.2                | Uniform charge storage versus localized charge storage                             | 2    |

| 1.3                | Organization of the Dissertation                                                   | 5    |

| Chapter 2          | Program/Erase Cycling Induced Endurance<br>Degradation in Nitride Storage Flash    |      |

|                    | Memory Cell                                                                        | 12   |

| 2.1                | Introduction                                                                       | 12   |

| 2.2                | Endurance Failure in Nbit Cells                                                    | 12   |

| 2.3                | Evidence of Negative Charge Creation                                               | 13   |

| 2.4                | Improvement of Cycling Endurance                                                   | 15   |

| Chapter 3          | Characterization of Programmed Charge<br>Lateral Distribution in Nbit Flash Memory |      |

|                    | Cell by Using Charge Pumping Technique                                             | 23   |

| 3.1                | Introduction                                                                       | 23   |

| 3.2                | Device Structure and Measurement Setup                                             | 24   |

| 3.3                | Measurement Result and Discussion                                                  | 25   |

| 2,0                | 3.3.1 Single-bit Storage                                                           | 25   |

|                    | 3.3.2 Two-bit Storage                                                              | 26   |

| 3.3.3 P/E Cycling Stress Effect                       | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| .4 Summary                                            | 29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Reliability Mechanisms of Data Retention              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| •                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Cells                                                 | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .1 Introduction                                       | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .2 Room-Temperature Threshold Voltage Drift           | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .3 Read-Disturb Effects in Erase State                | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3.1 Commonality between Vt Drift and Read-Disturb   | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.3.2 Gate and Drain Bias Dependences on Read-Disturb |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Behavior                                              | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .4 Program-state Charge Loss                          | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .5 Summary                                            | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Numerical Simulation of Program-State                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Charge Retention in SONOS Flash Memory<br>Cell        | <b>y</b><br>61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| .1 Introduction 1896                                  | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .2 Retention Loss Simulation Model                    | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2.1 Nitride Charge Dynamics and Loss Mechanisms     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.2.2 Assumptions in Simulation                       | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

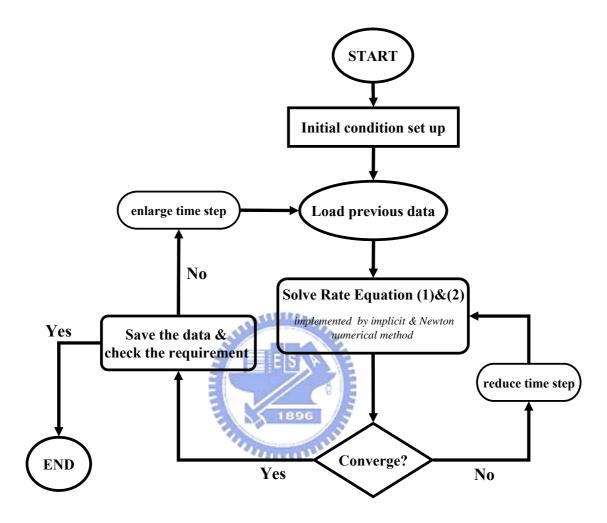

| .3 Numerical Simulation Method                        | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

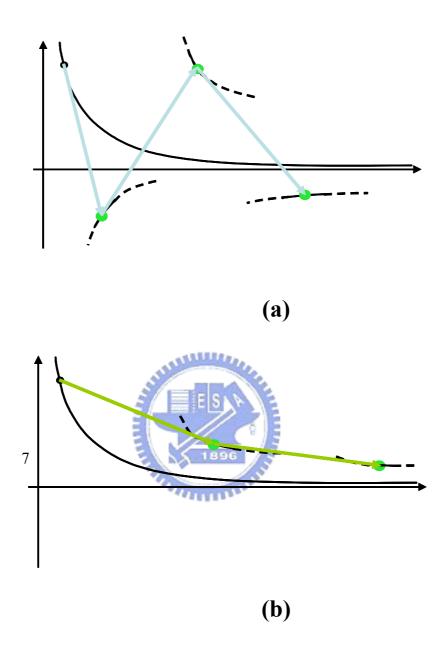

| 5.3.1 Explicit and Implicit Methods                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.2 Non-linear and Stiff System                     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.3 Jacobian Matrix                                 | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3.4 Simulation Flowchart                            | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .4 Results and Discussion                             | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.1 Bottom Oxide Blocking Effect                    | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.2 Post-Stress Two-Stage Retention Loss            | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4.3 Leakage Component Separation                    | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| .5 Summary                                            | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                       | Reliability Mechanisms of Data Retention and Read-Disturb in Nbit Flash Memory Cells  Introduction Room-Temperature Threshold Voltage Drift Read-Disturb Effects in Erase State 4.3.1 Commonality between Vt Drift and Read-Disturb 4.3.2 Gate and Drain Bias Dependences on Read-Disturb Behavior Program-state Charge Loss Summary  Numerical Simulation of Program-State Charge Retention in SONOS Flash Memory Cell Introduction Retention Loss Simulation Model 5.2.1 Nitride Charge Dynamics and Loss Mechanisms 5.2.2 Assumptions in Simulation Numerical Simulation Method 5.3.1 Explicit and Implicit Methods 5.3.2 Non-linear and Stiff System 5.3.3 Jacobian Matrix 5.3.4 Simulation Flowchart Results and Discussion 5.4.1 Bottom Oxide Blocking Effect 5.4.2 Post-Stress Two-Stage Retention Loss 5.4.3 Leakage Component Separation |

| Chapter 6          | Extraction of Nitride Trap Density from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| -                  | Stress Induced Leakage Current in SONOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |  |

|                    | Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94  |  |

| 6.1                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 94  |  |

| 6.2                | Nitride Trap Characterization Technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 95  |  |

| 6.3                | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 98  |  |

| Chapter 7          | Read Current Instability Arising from                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |  |

|                    | Random Telegraph Noise in Localized                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |  |

|                    | Storage, Multi-Level SONOS Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 105 |  |

| 7.1                | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105 |  |

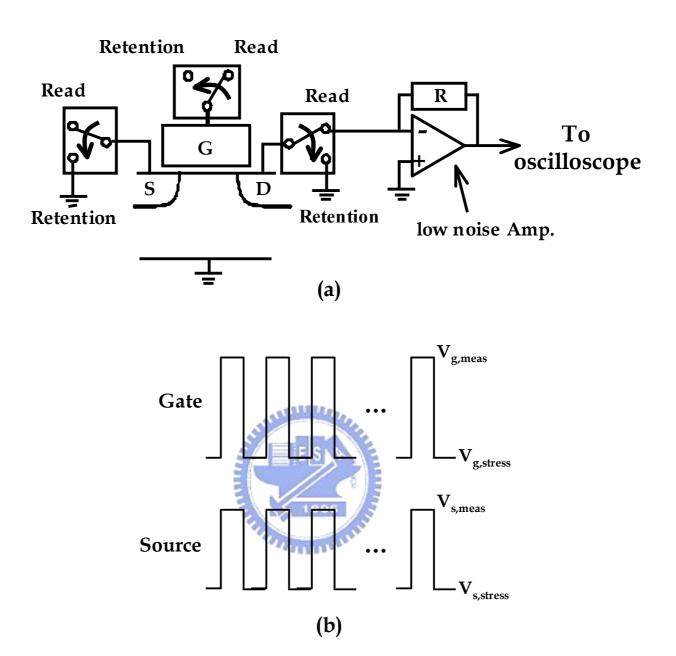

| 7.2                | Experimental Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 106 |  |

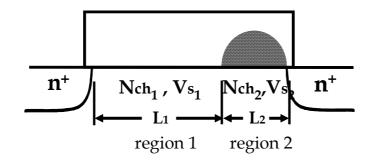

| 7.3                | Two-region model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 106 |  |

| 7.4                | Results and Discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 108 |  |

| 7.5                | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110 |  |

| Chapter8           | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 121 |  |

| References         | The state of the s | 124 |  |

| Vita               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 137 |  |

| <b>Publication</b> | Lists                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 138 |  |

# **TABLE CAPTIONS**

## Chapter 1

Table 1.1Bias conditions for Nbit two-bit operation.

#### Chapter 5

Table 5.1Parameters used for the numerical simulation.

#### Chapter 6

Table 6.1The extracted nitride trap density from sample A, B, C respectively by using our technique.

# FIGURE CAPTIONS

#### Chapter 1

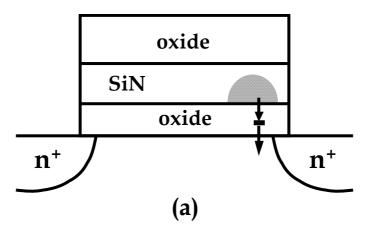

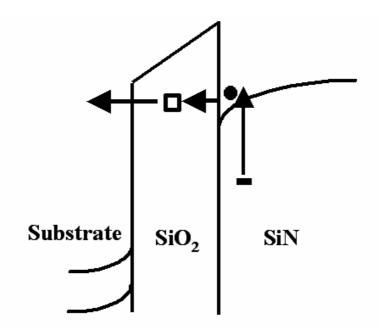

- Fig. 1.1 Charge loss via the bottom oxide trap in a SONOS-type memory (a) and in a FG-type memory (b).

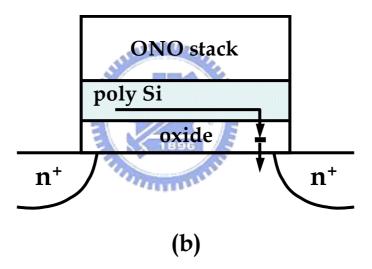

- Fig. 1.2 Scaling limitation of NOR type floating gate flash.  $I_{DTO}$  is drain induced turn-on leakage current,  $I_{BBT}$  is band-to-band tunneling current,  $t_{PGM}$  refers to the hot electron programming time, and  $I_{READ}$  is the current needed for read. The shaded region refers to the design window. For the above design constraints, the design window will no longer exist when device channel length is below  $0.13\mu m$ .

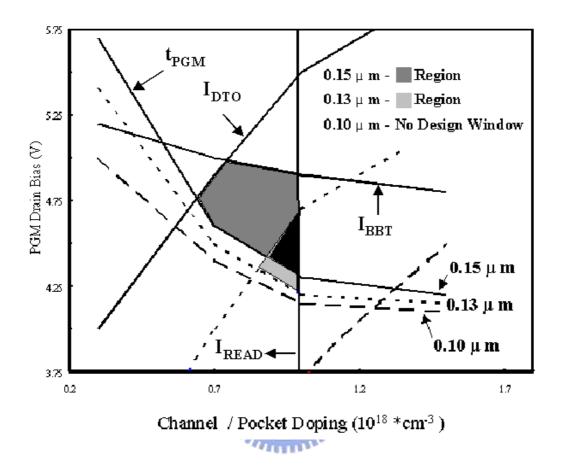

- Fig. 1.3 Evolution of nitride-based NVSM.

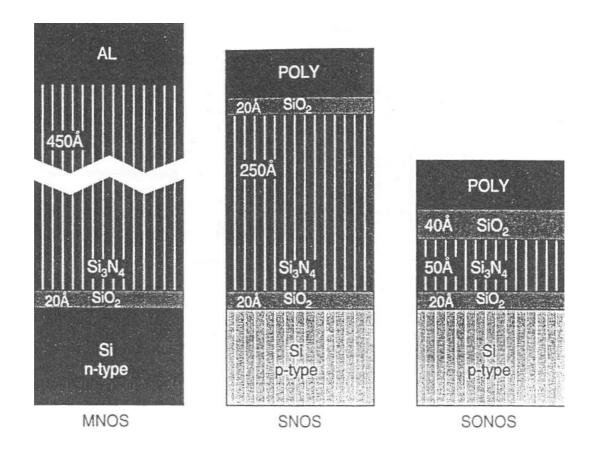

- Fig. 1.4 Program & Erase operations in Nbit cells (a) and in SONOS cells (b). The operation modes are summarized in (c).

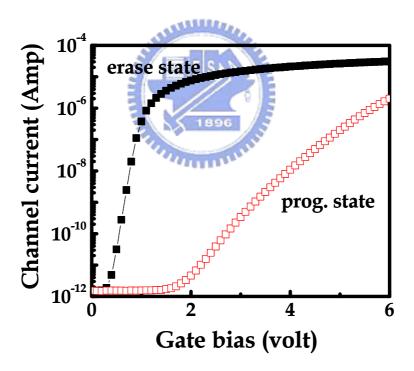

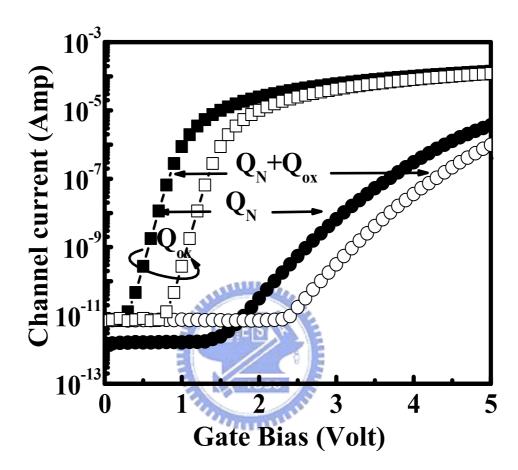

- Fig. 1.5 Channel current versus gate bias in erase state and in program state.

- Fig. 1.6 The design margin for Nbit operation.

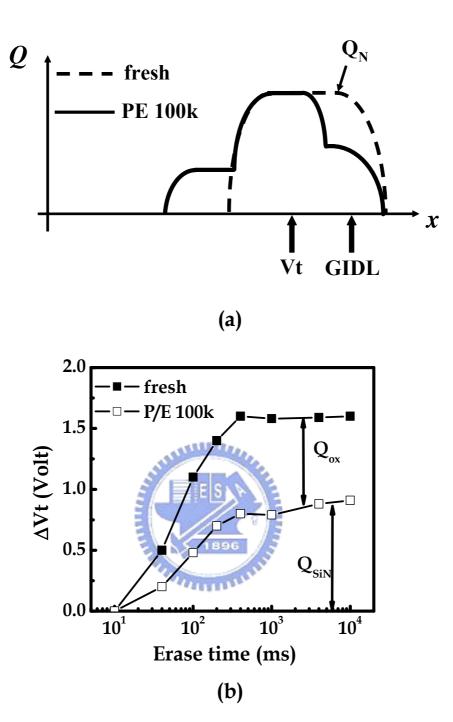

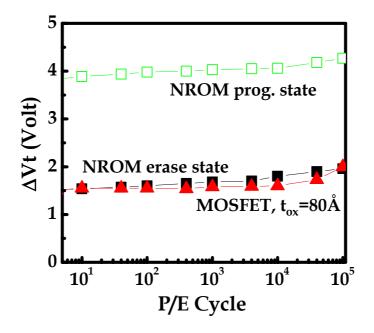

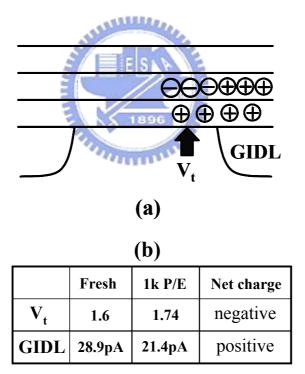

- Fig. 2.1 (a) Endurance characteristics of a Nbit cell operation window. Program bias is Vg/Vd=11V/4.7V, 10μs and erase bias is Vg/Vd=-3V/, 3ms. The thickness of each ONO layer is 7nm, 6nm and 6nm. (b) Endurance characteristics of a floating-gate flash cell showing the window opening and closing.

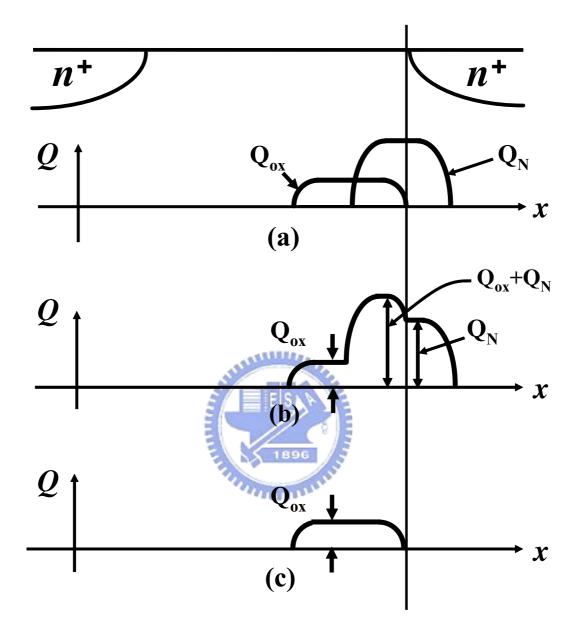

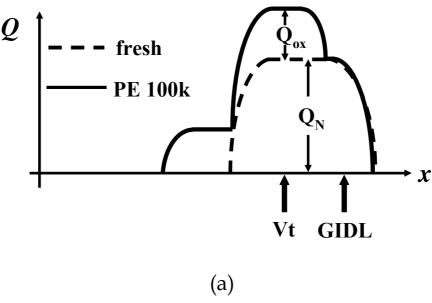

- Fig. 2.2 Nbit cell subthreshold charcateristics in erase state and in program state before stress and after 100k cycling stress. Qpm and QR represent the charge created by P/E stress and the injected charge by programming, respectively.

- Fig. 2.3 (a) The relative position of QR and Qpm in a cycled cell. The x-axis is the channel direction. There is an overlap between QR and Qpm. (b) The charge distribution of QR and Qpm in program state after cycling stress. (c) QR in erase state in a stressed cell.