# 國立交通大學

電子工程學系 電子研究所 碩士論文

AXI 匯流排之系統設計與實現

System Design and Implementation of AXI Bus

研 究 生:廖英澤

指導教授:張添烜 博士

中華民國九十六年十月

System Design and Implementation of AXI Bus

研究生:廖英澤 Student: Ying-Ze Liao

指導教授:張添烜 博士 Advisor: Dr. Tian-Sheuan

Chang

### 國立交通大學

電子工程學系 電子研究所

碩士論文

#### **A** Thesis

# Submitted to **Department of Electronics Engineering & Institute of Electronics**College of Electrical & Computer Engineering

National Chiao Tung University in partial Fulfillment of the Requirements for the Degree of Master

in

Electronics Engineering & Institute of Electronics

October 2007

Hsinchu, Taiwan, Republic of China

中華民國九十六年十月

# AXI 匯流排之系統設計與實現

研究生:廖英澤 指導教授:張添烜博士

國立交通大學 電子工程學系 電子研究所

# 摘要

隨著矽智財整合系統單晶片成為可能,整合連結這些矽智財的晶片匯流排成為整個系統效能上重要的角色,Advanced eXtensible Interface(AXI)是新一代的晶片匯流排通訊協定,AXI通訊協定採用封包基準的方式傳輸資料,使用分離的位址與資料通道,每個通道交握方式使用來源的有效信號與目的的就緒信號在時脈正緣取樣,當取樣到兩者的訊號皆是1則完成交握並傳輸資料,因此可簡單插入暫存器增加每個通道管線級數來提高工作頻率,另外還支援不需依序完成、爆發模式傳輸,提供了更高效率的傳輸能力。

在本論文之前並沒有針對新一代晶片匯流排通訊協定上的特性在連結器架構的硬體成本與頻寬的完整探討,目前已存在的 AXI 匯流排設計都採用交叉開關 (Crossbar Switch)架構,雖然交叉開關提供了高頻寬,但也付出了極高的硬體成本,使用共享匯流排架構可以減少許多硬體成本,運用 AXI 支援不需依序完成的特性在共享匯流排上,仍然可以提供相當高的頻寬,因此我們以 SystemC 在交換層級(Transaction-level)建構了一個可攜式媒體平台(Portable Media Platform)的模型來模擬分析。

由於 AXI 匯流排連接器多了一層的暫存器,交握時為了確保資料傳輸正確,在一般的傳輸模式下頻寬的最高使用率只有 50%,針對這點在本篇論文我們設計了交錯傳輸模式(Interleaved Mode)來提高頻寬使用率最高達 99%。此模式的使用只要連接器提供支援即可,完全不需要協定上的修改。此外,對於系統中有高初始延遲的記憶體控制器裝置,我們另外設計了資料通道鎖定模式(Data Lock Mode)以及混合傳輸模式(Hybrid Mode),可以有效地減少記憶體資料傳輸時間,也給予記憶體控制器高度重新排程的能力,以提高頻寬使用率並進而提昇系統的效能。

在建構的平台上我們驗證了所提出的各種傳輸模式在真實系統環境下的效用,除此之外,實驗中探討了 AXI 介面緩衝器大小、仲裁策略、傳輸模式以及仲裁權重調整方式對系統效能的影響,實驗結果證明在適當傳輸模式配置和系統配置下,可以提高 69%的頻寬使用量、進而提升 40%的系統速度。另外相較於傳統不支援不需依序完成功能的匯流排如 AHB, AXI 匯流排搭配前述提出的傳輸模式

與系統配置,最多可以提高 346%的頻寬使用率及 44%的系統速度。這顯現出採用 AXI 匯流排並恰當地搭配各種傳輸模式可以大幅度並有效地改善系統效能。

最後我們做成實際的硬體,在 0.13 微米的互補式金氧半導體製程下,在 200 百萬赫茲的運作頻率下需要 18.85K 個邏輯閘,提供使用每一千個邏輯閘每秒 84MB 的頻寬。

# System Deign and Implementation of AXI Bus

Student: Ying-Ze Liao Advisor: Dr. Tian-Sheuan Chang

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

### **Abstract**

The on-chip-bus (OCB) which connects silicon intellectual property (SIP) in a system-on-a-chip (SoC) plays a key role in affecting the system performance. Recently, a new generation of packet-based OCB protocol called Advance eXtensible Interface (AXI) has been proposed. The AXI separates the address and data into independent channels. The handshaking of each channel uses two signals which one is VALID from source and the other is READY from destination. Once the VALID and READY are high at the same clock positive edge, the handshaking completed and data transferred. Therefore, it is easy to add pipeline stage to increase operating frequency by inserting the register slice. Besides, the AXI protocol supports out-of-order completion and burst-based transaction to provide more bandwidth than traditional OCB protocol.

Before this thesis, there is no complete analysis on the interconnect architecture and bandwidth of the of new generation OCB protocol. The existed AXI bus interconnect all adopt the crossbar switch as the architecture. Although the crossbar switch provides high bandwidth, it needs extreme hardware cost. Using the characteristic of AXI, we can adopt the shared bus as the architecture of the bus interconnect to obtain low hardware cost and keep fairly high bandwidth. To analyze impact of the architecture, a portable media platform (PMP) is modeled at transaction-level with SystemC for simulations.

However, the AXI bus interconnect can only achieve 50% of bandwidth utilization at most when normal transfer mode is being used. Therefore, we propose an interleaved transfer mode to increase the bandwidth utilization up to 99%. The interleaved transfer mode can be implemented as a totally built in feature of a bus interconnect and does not need any modification to the protocol. In addition, this work also proposes a data lock transfer mode and hybrid mode to handle the transactions to the devices with long initial access latency, such as the memory controller in a system. These modes decrease the transfer time and give the memory

controller a higher degree of access rescheduling capability.

We evaluate impact of the proposed transfer modes in the portable media platform. In addition, the impact of wrapper buffer size, arbitration policy, transfer mode setting, and arbitration parameter settings are also studied. The simulation result shows that the proposed transfer modes improve the bandwidth utilization by 69% and speed up the system by 44%. Compare the performance with the traditional bus such as the AHB; the AXI system can outperform the AHB system in bandwidth utilization by 346% and system speed by 44% at most.

The implemented AXI bus interconnect with the proposed transfer modes has a gate count of 18.85K when synthesized with 0.13  $\mu$  m CMOS process under 200 MHz operating frequency.

# 致 謝

首先誠摯的感謝指導教授張添烜博士,老師耐心的教導使我學習到做 研究的方法,不時的討論並指點我正確的方向,使我在這些年中獲益匪淺。

本論文的完成另外亦得感謝張彥中學長的大力協助,因為有你細心地 跟我討論與我反覆的檢討,使得本論文能夠更完整而嚴謹。

在兩年的日子裡,實驗室裡共同的生活點滴,有學術上的討論與生活 經驗的分享。非常感謝眾位學長、同學、學弟的共同砥礪,你們的陪伴讓 這兩年的研究生活變得絢麗多彩。

感謝林佑昆、蔡旻奇、古君偉、王裕仁、余國亘、吳錦木學長們不厭 其煩的指出我研究中的缺失,且總能在我迷惘時為我解惑,也感謝林嘉俊 同學與我參加了兩年的 IC 競賽,使得我在設計 IC 的技巧更成熟,另外也 感謝吳私景、郭子筠、李得瑋同學給予我的鼓勵,恭喜我們順利走過這兩 年。實驗室的蔡宗憲、曾宇晟、詹景竹、張瑋城、戴瑋呈學弟們當然也不 能忘記,你們的幫忙及搞笑我銘感在心。 最後,謹以此文獻給我摯愛的雙親。

# Content

| Chapter | r 1 Intro    | duction                                | 1  |

|---------|--------------|----------------------------------------|----|

| 1.1     | 1 Background |                                        |    |

| 1.2     | Relat        | ed Work                                | 2  |

| 1.3     | Motiv        | vation and Contribution                | 3  |

| 1.4     | Thesi        | is Organization                        | 3  |

| Chapter | 2 Over       | view of the AMBA Bus                   | 4  |

| 2.1     | AHB          |                                        | 4  |

|         | 2.1.1        | AHB Architecture                       | 4  |

|         | 2.1.2        | AHB Handshaking and Arbitration        | 5  |

| 2.2     | AXI .        |                                        | 7  |

|         | 2.2.1        | AXI Architecture                       | 8  |

|         | 2.2.2        | Channel Handshaking                    | 10 |

|         | 2.2.3        | Transaction Ordering                   | 12 |

| 2.3     | Comp         | parison between AXI and AHB            | 13 |

|         | 2.3.1        | Protocol and Architecture              | 13 |

|         | 2.3.2        | Latency and Bandwidth Utilization      | 13 |

|         | 2.3.3        | Hardware CostES                        | 15 |

| Chapter | r 3 Simu     | lation Modeling for AXI System         | 20 |

| 3.1     | Over         | view of the Modeling Method            |    |

|         | 3.1.1        | Transaction-Level-Modeling             | 20 |

|         | 3.1.2        | Using SystemC as Modeling Language     | 21 |

| 3.2     | Traffi       | ic Generation                          | 22 |

| 3.3     | AXI I        | Master                                 | 24 |

|         | 3.3.1        | Master Behavior Modeling               | 24 |

|         | 3.3.2        | Master Types                           | 25 |

|         | 3.3.3        | States of Mater Processing Transaction | 28 |

| 3.4     | AXI          | Slave                                  | 30 |

|         | 3.4.1        | Slave Types                            | 30 |

|         | 3.4.2        | States of Slave Processing Transaction | 31 |

| Chapter | 4 Design     | gn of AXI Bus Interconnect             | 34 |

| 4.1     | Bus I        | Interconnect                           | 34 |

| 4.2     | Trans        | sfer Mode                              | 36 |

|         | 4.2.1        | Normal Mode                            | 39 |

|         | 4.2.2        | Interleaved Mode                       | 39 |

|         | 4.2.3        | Data Lock Mode                         | 40 |

|         | 4.2.4        | Hybrid Mode                            | 44 |

| 4.3     | Arbi  | itration Policy                              | 45 |

|---------|-------|----------------------------------------------|----|

|         | 4.3.1 | Our AXI Arbitration Flow                     | 45 |

|         | 4.3.2 | Fixed Priority                               | 46 |

|         | 4.3.3 | TDMA                                         | 47 |

|         | 4.3.4 | Round-Robin                                  | 48 |

|         | 4.3.5 | Lottery                                      | 49 |

| Chapter | 5 Sim | ulation and Analysis                         | 51 |

| 5.1     | Intro | oduction                                     | 51 |

| 5.2     | PMI   | P Platform                                   | 52 |

|         | 5.2.1 | Overview                                     | 52 |

|         | 5.2.2 | Scenario                                     | 54 |

| 5.3     | Exp   | eriments                                     | 55 |

|         | 5.3.1 | Performance Metric                           | 55 |

|         | 5.3.2 | Simulation of Video Phone Scenario           | 56 |

| 5.4     | AXI   | I vs. AHB                                    | 75 |

|         | 5.4.1 | AHB PMP Platform                             | 75 |

|         | 5.4.2 | Comparison between AXI and AHB               |    |

| Chapter | 6 Har | dware Implementation                         | 80 |

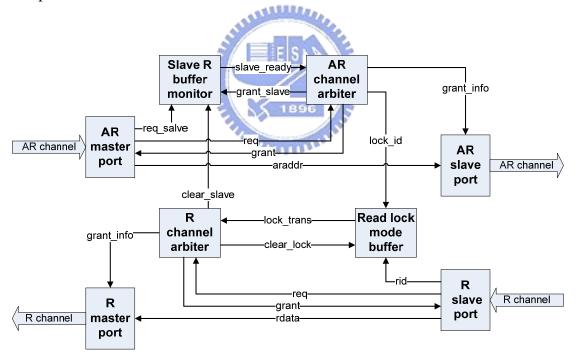

| 6.1     | Hard  | dware Design                                 | 80 |

|         | 6.1.1 | Read Transaction Design                      | 80 |

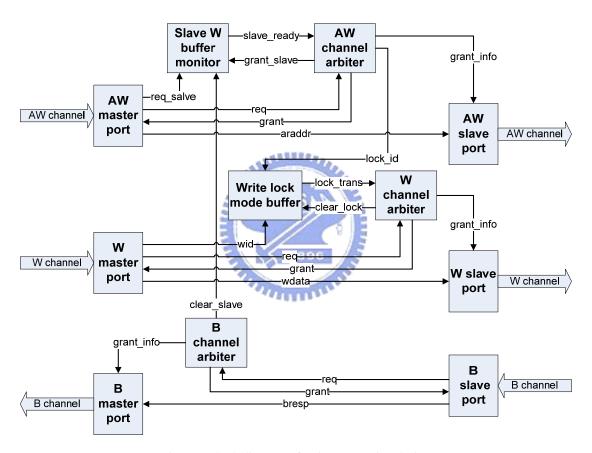

|         | 6.1.2 | Write Transaction Design                     | 81 |

| 6.2     | Imp   | lementation Results                          | 82 |

| Chapter | 7 Con | lementation Resultseclusion and Future Works | 84 |

| 7.1     |       | clusion                                      |    |

| 7.2     | Futu  | re Works                                     | 84 |

| Referen | ice   |                                              | 86 |

# **List of Figures**

| Fig. | 2-1 AHB architecture                                            | 5  |

|------|-----------------------------------------------------------------|----|

| Fig. | 2-2 AHB simple transfer                                         | 6  |

| Fig. | 2-3 Transfer with wait states                                   | 6  |

| Fig. | 2-4 AHB arbitration                                             | 7  |

| Fig. | 2-5 Generic AXI architecture                                    | 8  |

| Fig. | 2-6 Read transaction                                            | 9  |

| Fig. | 2-7 Write transaction                                           | 10 |

| Fig. | 2-8(a)VALID before READY (b)READY before VALID (c)VALID with    |    |

|      | READY                                                           | 12 |

| Fig. | 2-9 AHB continuous transfer                                     | 14 |

| Fig. | 2-10 AXI continuous transfer                                    | 14 |

| Fig. | 2-11 AHB burst transaction                                      | 15 |

| Fig. | 2-12 AXI burst transaction                                      | 15 |

| Fig. | 3-1 System Modeling Graph                                       | 21 |

| Fig. | 3-2 Illustration of a modeling module                           | 22 |

| Fig. | 3-3 Illustration of traffic generation                          | 22 |

| Fig. | 3-4 Example of a task state table file                          | 24 |

| Fig. | 3-5 Flow of transaction generation in master                    | 25 |

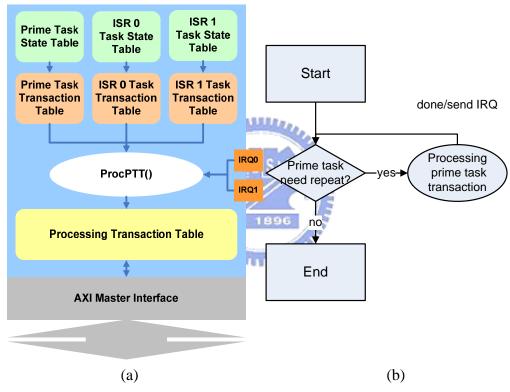

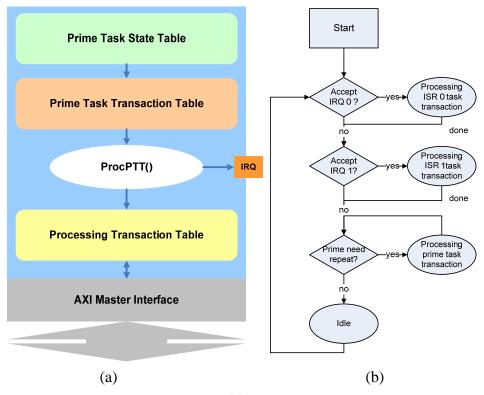

| Fig. | 3-6 Regular type master (a) block diagram (b) Flow of ProcPTT() | 26 |

| Fig. | 3-7 DMAC type master (a) block diagram (b) Flow of ProcPTT()    | 27 |

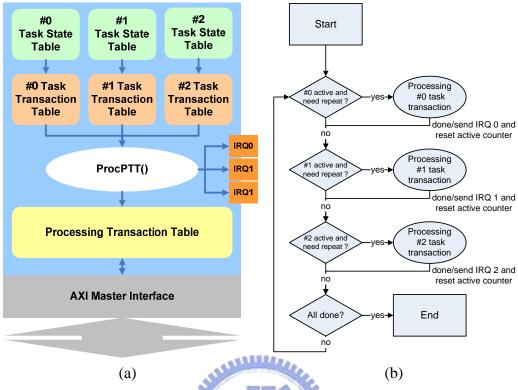

| Fig. | 3-8 MPU type master (a) block diagram (b) Flow of ProcPTT()     | 28 |

| Fig. | 3-9 FSM of master's PTT                                         | 29 |

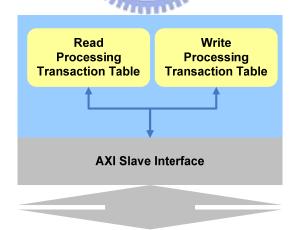

| Fig. | 3-10 Block diagram of regular type slave                        | 30 |

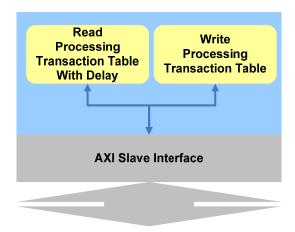

| Fig. | 3-11 Block diagram of MEM type slave                            | 31 |

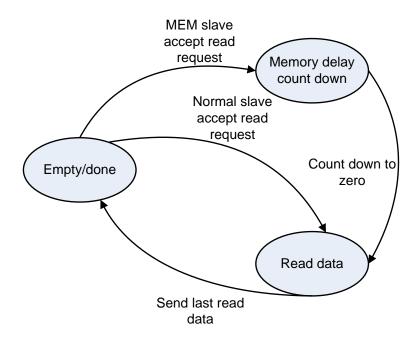

| Fig. | 3-12 FSM of transaction in slave read PTT                       | 32 |

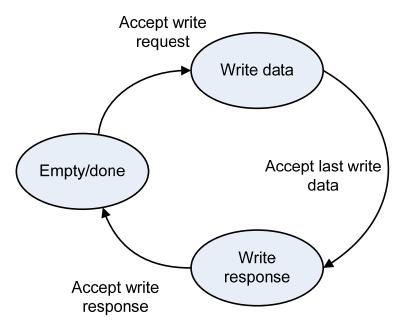

| Fig. | 3-13 FSM of transaction in slave write PTT                      | 33 |

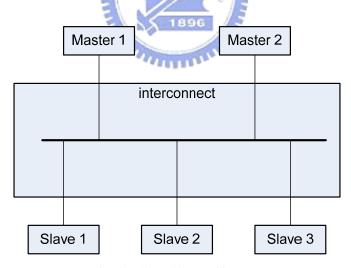

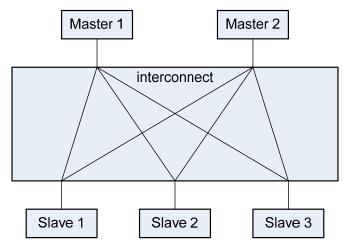

| Fig. | 4-1 Shared bus architecture                                     | 34 |

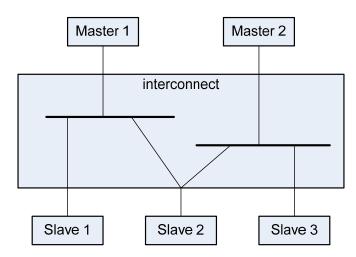

| Fig. | 4-2 Multi-layer architecture                                    | 35 |

| Fig. | 4-3 Crossbar architecture                                       | 36 |

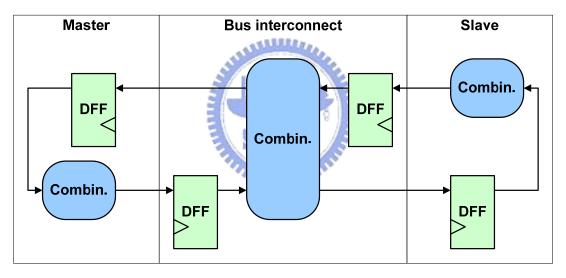

| Fig. | 4-4 Register slice of AXI bus interconnect                      | 37 |

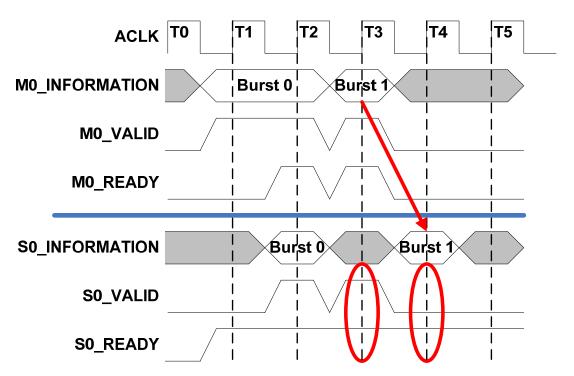

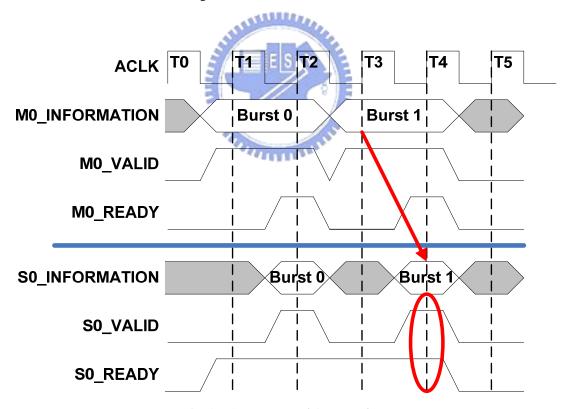

| Fig. | 4-5 Error case of data transfer                                 | 38 |

| Fig. | 4-6 Correct case of data transfer                               | 38 |

| Fig. | 4-7 Timing diagram of normal mode                               | 39 |

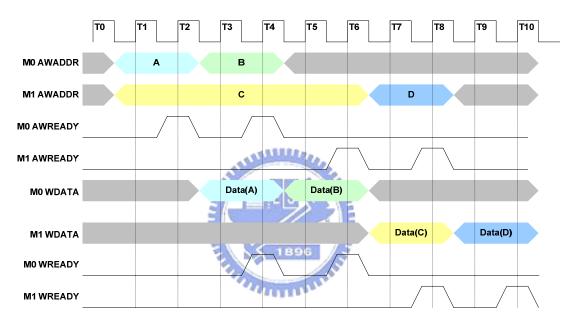

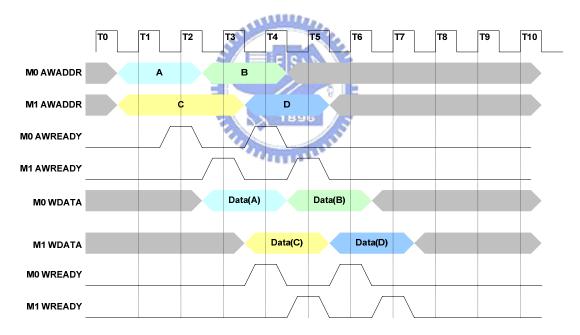

| Fig. | 4-8 Timing diagram of interleaved mode                          | 40 |

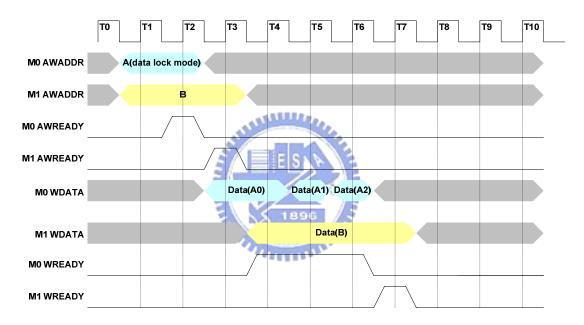

| Fig. | 4-9 Timing diagram of data lock mode                            | 41 |

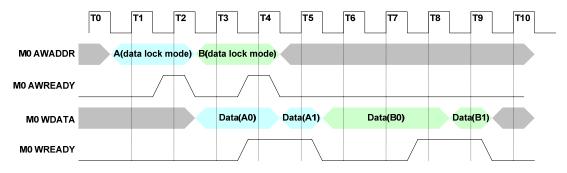

| Fig. | 4-10 The case of data lock mode results in the limitation       | 43 |

| Fig. 4-11 Flow of hybrid mode                                          | 45     |

|------------------------------------------------------------------------|--------|

| Fig. 4-12 Flow of our arbitration                                      | 46     |

| Fig. 4-13 Illustration of TDMA policy                                  | 48     |

| Fig. 4-14 Illustration of Round-Robin policy                           | 49     |

| Fig. 4-15 Example of lottery arbitration                               | 50     |

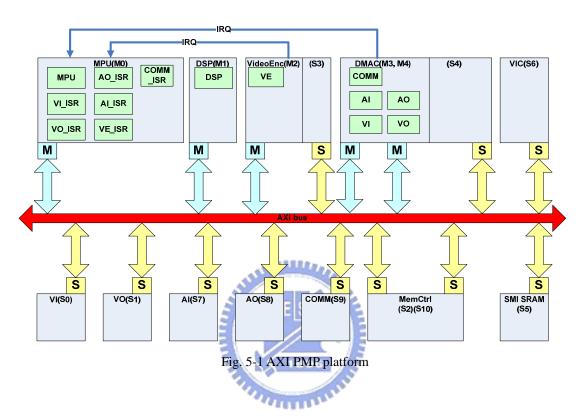

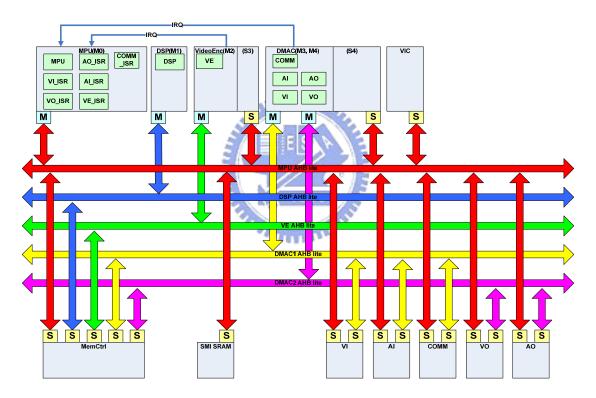

| Fig. 5-1 AXI PMP platform                                              | 52     |

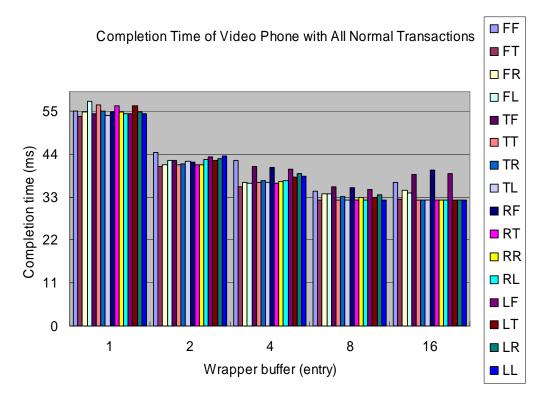

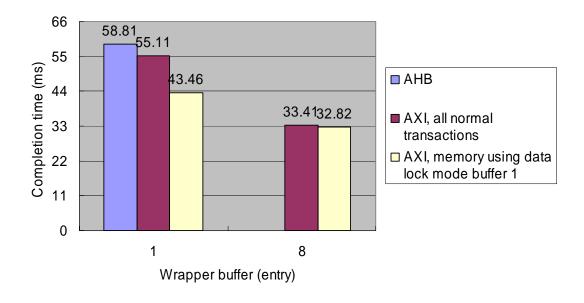

| Fig. 5-2 Completion time of video phone with all normal transactions.  | 60     |

| Fig. 5-3 Bandwidth utilization of video phone with all normal transact | ions60 |

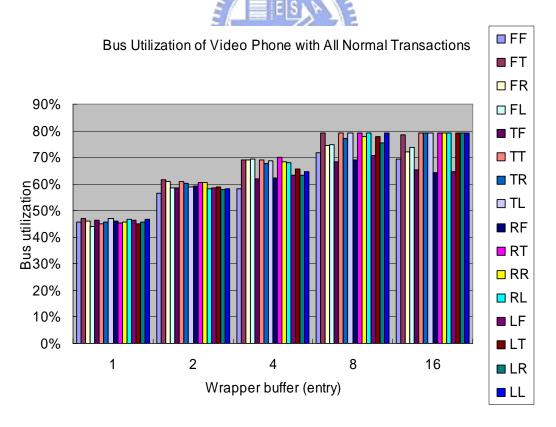

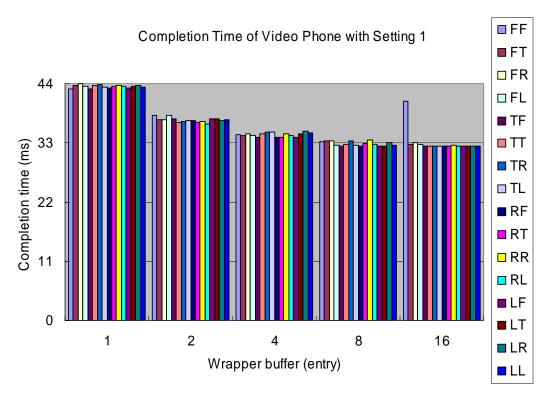

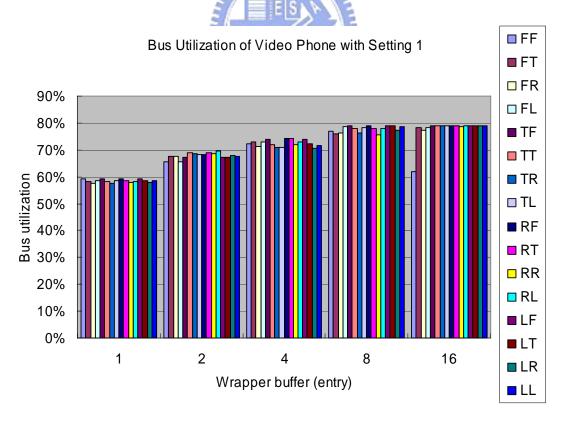

| Fig. 5-4 Completion time of video phone with setting 1                 | 63     |

| Fig. 5-5 Bandwidth utilization of video phone setting 1                | 63     |

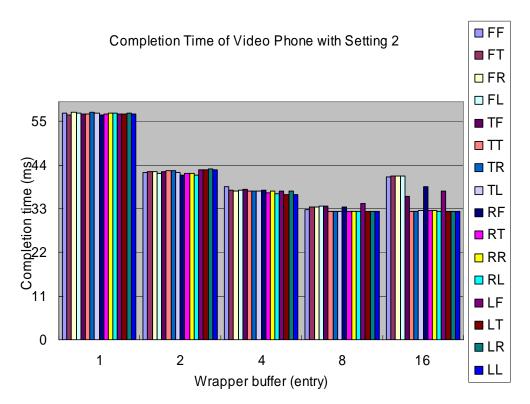

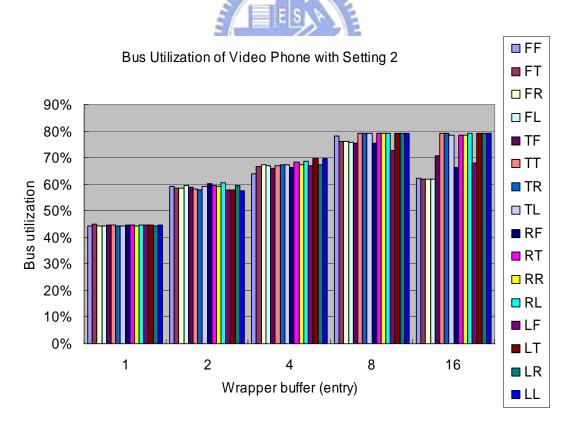

| Fig. 5-6 Completion time of video phone with setting 2                 | 65     |

| Fig. 5-7 Bandwidth utilization of video phone setting 2                | 65     |

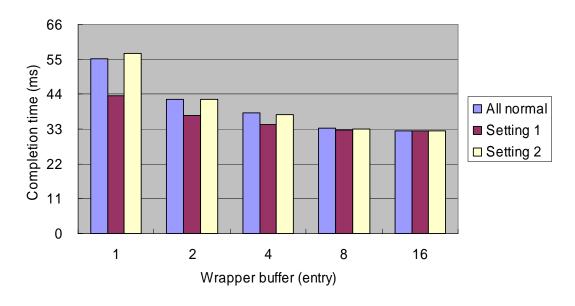

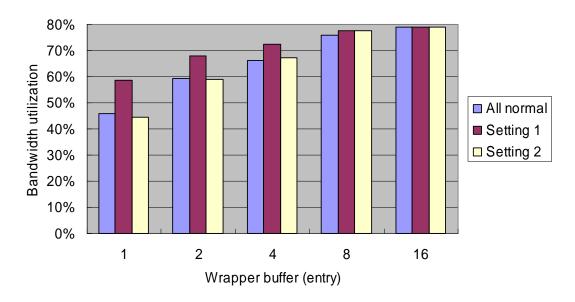

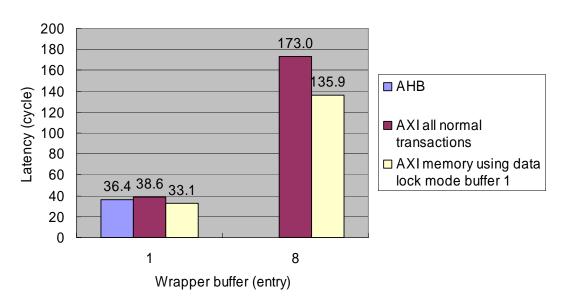

| Fig. 5-8 Average completion time of different task setting             | 66     |

| Fig. 5-9 Average bandwidth utilization of different task setting       | 67     |

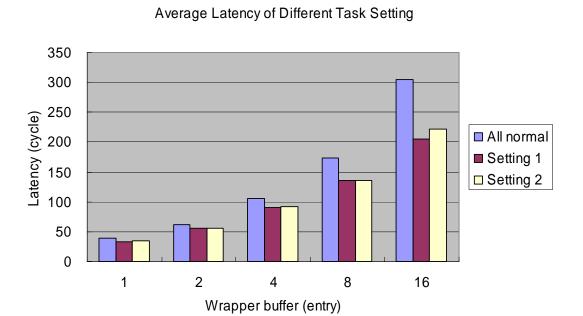

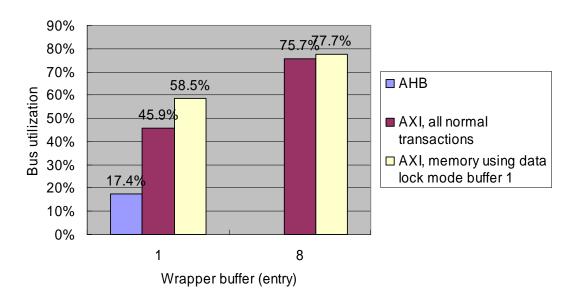

| Fig. 5-10 Average Latency of Different Task Setting                    | 67     |

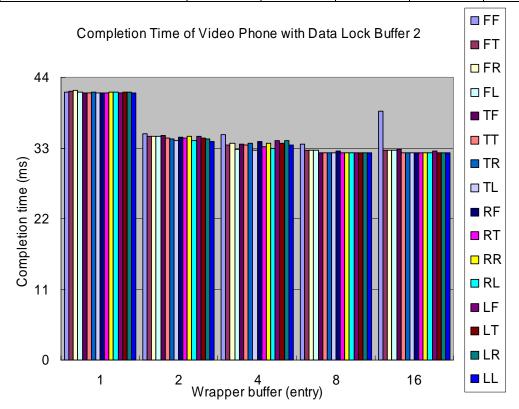

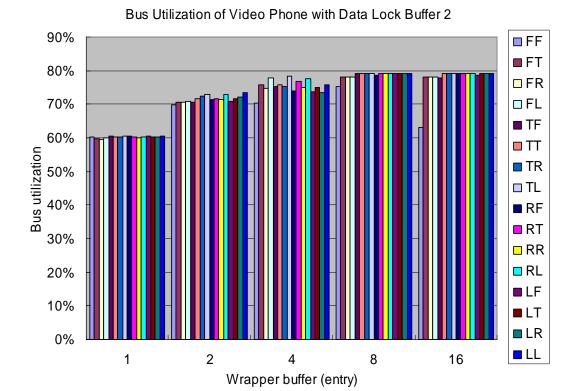

| Fig. 5-11 Completion time of video phone with data lock buffer 2       | 69     |

| Fig. 5-12 Bandwidth utilization of video phone with data lock buffer 2 | 270    |

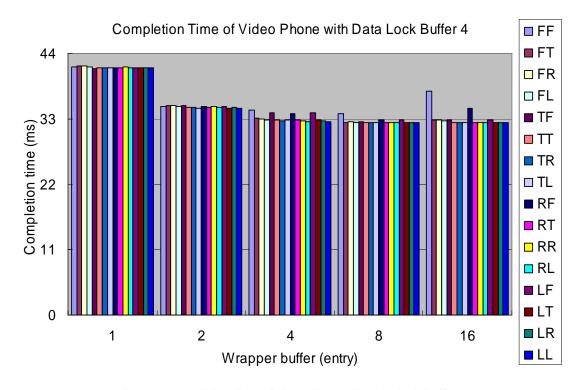

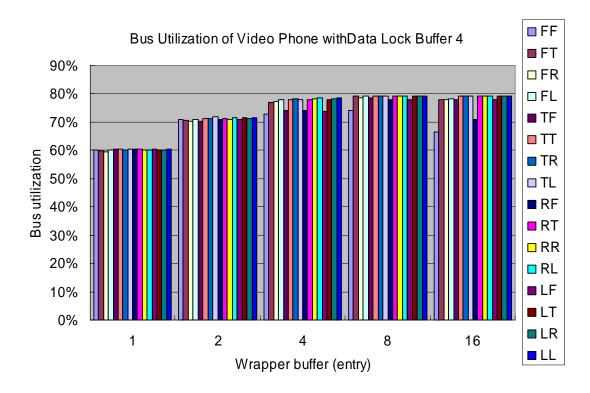

| Fig. 5-13 Completion time of video phone with data lock buffer 4       | 71     |

| Fig. 5-14 Bandwidth utilization of video phone with data lock buffer 4 | ·72    |

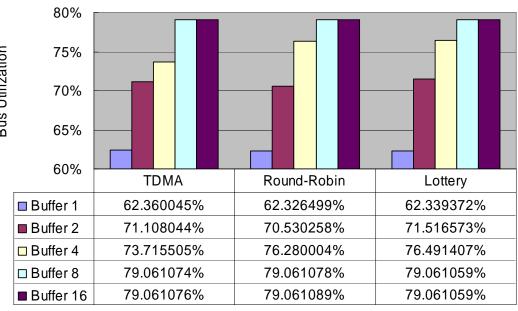

| Fig. 5-15 Average bandwidth utilization of weight tuning               | 74     |

| Fig. 5-16 Standard deviation of bandwidth utilization of weight tuning |        |

| Fig. 5-17 AHB PMP platformFig. 5-18Completion time of AXI and AHB      | 75     |

|                                                                        |        |

| Fig. 5-19 Bandwidth utilization of AXI and AHB                         | 79     |

| Fig. 5-20 Average latency of AXI and AHB                               | 79     |

| Fig. 6-1 Block diagram of read transaction design                      |        |

| Fig. 6-2 Block diagram of write transaction design                     | 82     |

# **List of Table**

| Table 2-1 Main difference between AXI and AHB                                   | 13      |

|---------------------------------------------------------------------------------|---------|

| Table 2-2 Parameters for hardware cost calculation                              | 16      |

| Table 2-3 Comparison of hardware cost between AHB and AXI                       | 19      |

| Table 3-1 Fields of a task state                                                | 23      |

| Table 4-1 Limitation of bandwidth utilization using data lock mode              | 44      |

| Table 5-1 Master configuration of PMP platform                                  | 53      |

| Table 5-2 Slave configuration of PMP platform                                   | 53      |

| Table 5-3 Performance of AXI PMP platform                                       | 54      |

| Table 5-4 Task of video phone scenario                                          | 55      |

| Table 5-5 Factor of configuration                                               | 57      |

| Table 5-6 Setting of simulation A                                               | 58      |

| Table 5-7 Timing constraint status with all normal transaction of video phone s | cenario |

|                                                                                 |         |

| Table 5-8 Configuration of simulation B                                         | 61      |

| Table 5-9 Configuration of data lock mode of simulation B                       | 61      |

| Table 5-10 Timing constraint status with setting 1 of video phone scenario      | 62      |

| Table 5-11 Timing constraint status with setting 2 of video phone scenario      | 64      |

| Table 5-12 Configurations of simulation for data lock mode buffer size          | 68      |

| Table 5-13 Timing constraint status with data lock mode buffer 2                | 68      |

| Table 5-14 Timing constraint status with data lock mode buffer 4                |         |

| Table 5-15 Configuration of weight tuning                                       | 73      |

| Table 5-16 Met configurations of buffer size 4 in weigh tuning                  | 75      |

| Table 5-17Performance of AHB PMP platform                                       | 76      |

| Table 5-18                                                                      | 77      |

| Table 6-1 Implementation result and comparison                                  | 83      |

# **Chapter 1 Introduction**

# 1.1 Background

Recently, VLSI technology has improved significantly and more transistors can be integrated into a chip. This makes the ideal of system-on-a-chip [1] more of an achievable goal than an abstract dream. However, along with the increasing transistor count comes along the increasing design and verification complexities. Although EDA tools have also been developed in hope of helping system designer to handle the massive complexity, proper system-level design and verification methodology have played a much more important role. One such methodology is the platform-based design methodology which uses pre-verified silicon intellectual property (SIP) and an on-chip-bus (OCB). The OCB connects SIPs and provides communication among SIPs.

Since OCB is often the bottleneck of a system, a good OCB protocol plays an important role. One of the industry's de facto standard bus protocols is ARM's Advanced High-performance Bus (AHB). AHB is an OCB which adopts traditional bus architecture. It transfers the data in a pipeline way and completes the transaction in order. The exploration of AHB has been done for years [2]~[4], which includes architecture, low power and arbitration policy. However, Advance eXtensible Interface (AXI) is the successor of AHB but the study on AXI is still few. AXI contains lots of features which improves the performance of the OCB, such as packet-based transfer, out-of-order completion, and single address transaction. However, the related research of AXI is rare and lacks comparison with AHB. Thus, a complete analysis of AXI is necessary.

### 1.2 Related Work

In a system design, the bus arbitration policy plays an important role. The traditional arbitration policies include fixed priority, Round-Robin, and time division multiple access (TDMA) [5]. The fixed priority is the simplest policy which uses a static priority to arbitrate when contention occurs, but it has a fatal drawback that starvation. The Round-Robin and TDMA solve the starvation and provide a fair arbitration. In addition, There is a novel one: lottery [6] which is a probability-based arbitration policy. The lottery provides a good bandwidth allocation than the other polices. Mixing these polices brings out various characteristic of polices. However, in these papers, they mostly focus the analysis on the arbitration policy itself but lack a complete analysis on a system platform running a real application. Being aware of this, Poletti [6][5] builds an AHB platform and uses various patterns to analyze the impact of the fixed priority, TDMA, Round-Robin, and a time-slot reserve arbitration. Later, Lee [7] builds a shared bus AHB platform and a crossbar AXI platform to evaluate the performance of the two platforms. The comparison between the two platforms reveals that AXI bus has a superior performance. With the multi-core system becoming a trend, Ruggiero [8] builds a multi-core system with AHB, AXI and STBus to analyze the scalability of modern OCB protocol. Although the new generation OCB protocol has been analyzed in these two papers, their AHB bus architectures all adopt the shared bus and their AXI bus architectures adopt the crossbar, hence the comparison is not fair and the hardware cost is not taken into consideration. In addition, their arbitration policy in AXI bus interconnects are fixed priority so the potential of AXI may not have been fully explored. Until now, there has been no thorough analysis and exploration on AXI's arbitration policy, architecture, and hardware cost.

### 1.3 Motivation and Contribution

The issues mentioned above motivate us to investigate the performance of AXI bus in a system platform running an application. Being aware of the cost difference between the share bus and crossbar architecture, we focus our investigation in share bus architecture. In addition, the analysis result of using basic transfer which showed poor performance also motivated us to propose more efficient AXI transfer mode. Finally, the question of whether AHB or AXI is better for a system motivates us to conduct comparison on their performance and cost.

The contribution of this thesis includes the following.

- 1. The designed Transaction Level Models (TLM) are able to build various platforms and perform various scenarios to evaluate the system performance and to obtain proper configuration.

- 2. We analyze the impact of the AXI on various arbitration policies.

- 3. We give a proper way to design a shared bus AXI bus interconnect.

- 4. The designed AXI bus interconnect provides high bandwidth and low hardware cost

# 1.4 Thesis Organization

In chapter 2, we give a brief overview of the AMBA bus protocol. In chapter 3, we describe the methods we used in modeling AXI system. In chapter 4, we proposed an AXI interconnection which is able to provide high bandwidth and configuration of arbitration policy. In chapter 5, we show the result of simulation and analysis. In chapter 6, we implement the AXI interconnection hardware according to result of chapter 5. Chapter 7 is the conclusion and future works.

# **Chapter 2 Overview of the AMBA Bus**

### **2.1 AHB**

Advanced High-performance Bus (AHB) was proposed in AMBA 2.0 in 1999 and has been widely adopted since. Since then, AHB has been regarded as the industries de facto on-chip communication protocol. The basic architecture and protocol are described in this sub section. The features of AHB list below:

- Pipelined transfer

- Burst transfer

- Single-cycle bus master handover

- Single-clock edge operation

- Non-tri-state implementation

- Wider data bus configurations (64/128 bits)

#### 2.1.1 AHB Architecture

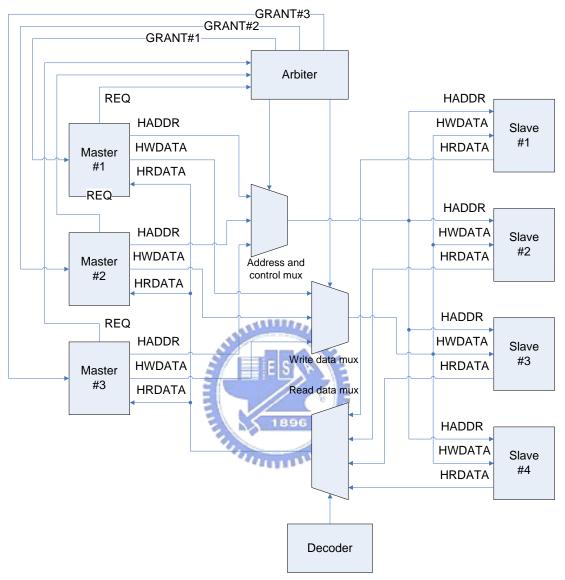

Fig. 2-1 shows the simplified AHB architecture which contains masters, slaves, arbiter, decoder and mux.

Each master and slave has three ports which are HADDR, HWDATA and HRDATA. HWDATA and HRDATA share the signal "HADDR" to indicate the destination of data transfer and therefore there is only one date transfer which is either HWDATA or HRDATA.

In the specification of AHB, it defined that bus interconnect is composed of arbiter, decoder and mux and the bus ownership is controlled by the centralized

arbiter to guarantee that only one master can use the shared bus.

Fig. 2-1 AHB architecture

# 2.1.2 AHB Handshaking and Arbitration

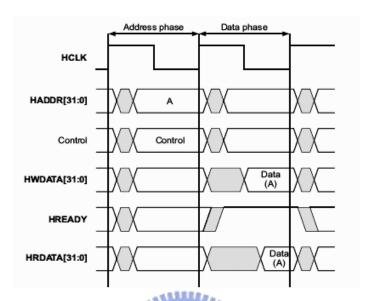

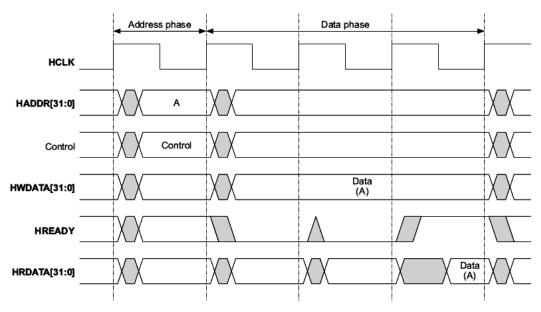

Each transaction of AHB contains two phases which are address phase and data phase as shown in Fig. 2-1. The address phase and data phase are sent in pipelined order, which means that data can only be sent after its address has been sent. This pipelined mechanism is controlled by the signal "HREADY". If HREADY is high, no

pipeline stall is introduced; otherwise, a pipelined stall is introduced as shown in Fig. 2-3.

Fig. 2-2 AHB simple transfer

Fig. 2-3 Transfer with wait states

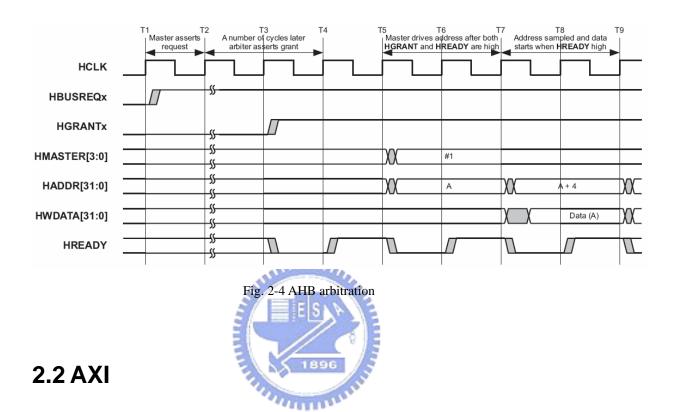

The ownership of the bus is controlled by a centralized arbiter. Fig. 2-4 shows an example of the arbitration process. First, each master sends a request to the arbiter by pulling HBUSREQ high. After several cycles, the arbiter asserts HGRANT but the

ownership of the bus still has not changed. Once both HGRANT and HREADY are high (Fig. 2-4,cycle T5), the granted master gets the ownership of bus. The ownership of the bus would remain until its transaction has been completed.

Advanced eXtensible Interconnect (AXI) was introduced in AMBA 3.0 as the successor on-chip bus protocol of the AHB in AMBA 2.0. The basic architecture and protocol are introduced in this sub section. The AXI protocol is targeted at high-performance, high-frequency system designs and includes a number of features that make it suitable for high-speed submicron interconnect.

The key features of the AXI are:

- Separate address/control and data phases

- Support for unaligned data transfer using byte strobes

- Burst-based transaction with only start address issued

- Separate read and write data channels to enable low-cost Direct Memory

Access

- Ability to issue multiple outstanding addresses

- Out-of-order transaction completion

- Easy addition of registers stages to provide timing closure

### 2.2.1 AXI Architecture

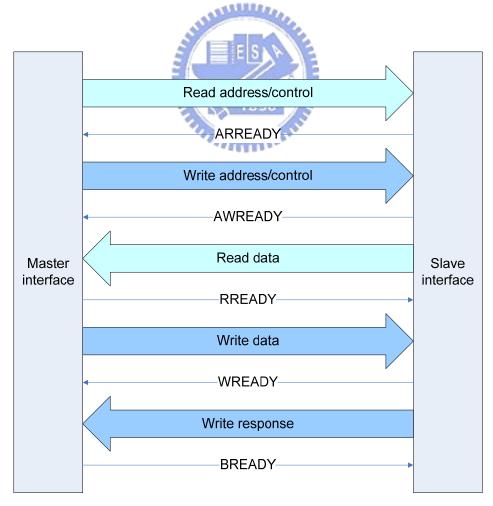

Fig. 2-5 shows a generic AXI architecture. There are five independent channels which communicate with master and slave. The five channels are read address channel, write address channel, read data channel, write data channel and write response channel. Each channel has a set of forward signals and one feedback signal for handshaking.

Fig. 2-5 Generic AXI architecture

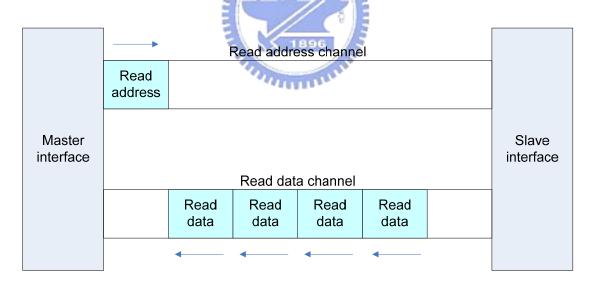

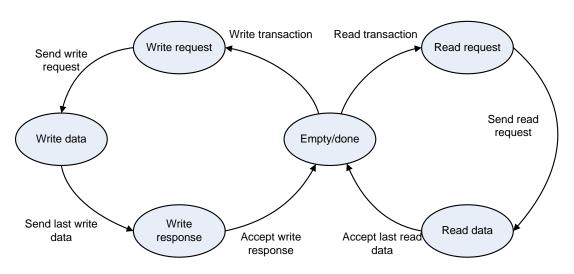

Fig. 2-6 shows an AXI read transaction. When an AXI master performs a read transaction, it sends a read address transfer which contains a start address and control information through the read address channel to a slave. When the slave accepts the address and control transfer, it starts its process according to the transfer accepted. Once the slave completes its process, it sends the data requested by the master through the read data channel. This transaction is not done until the master accepted the last burst data which contains read transaction status.

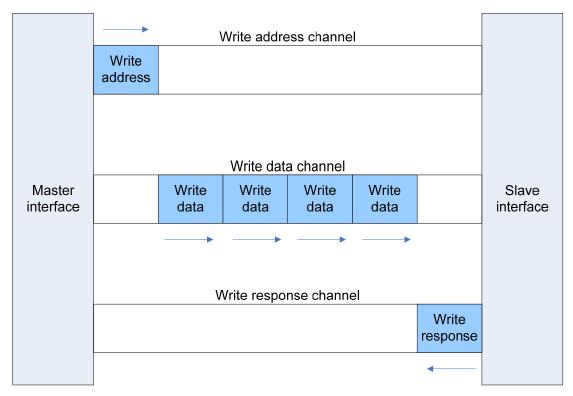

Fig. 2-7 shows an AXI write transaction. A master sends a write address transfer which also contains a state address and control information through the write address channel to a slave. Then, the master sends write data to the slave through the write data channel. After the slave accepted all write data, the salve sends a write response to tell the master the write transaction status through the write response channel.

Fig. 2-6 Read transaction

Fig. 2-7 Write transaction

# 2.2.2 Channel Handshaking

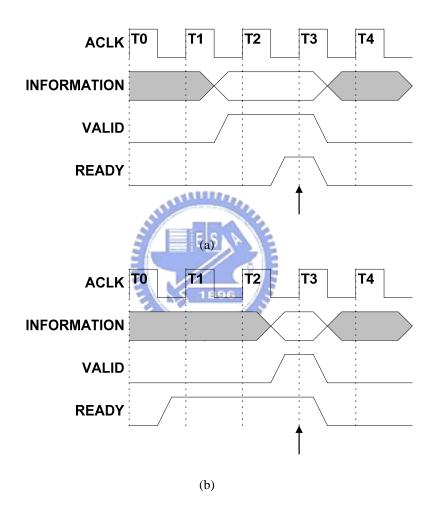

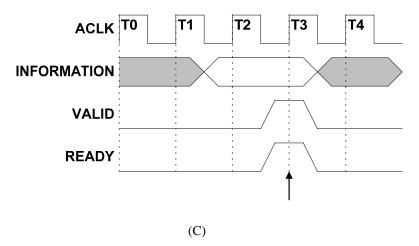

Each channel has a VALD and READY signals for handshaking. The source asserts VALID when the control information or data is available. The destination asserts READY when it can accept the control information or data. Transfer occurs only when both the VALID and READY are asserted. Fig. 2-8 shows all possible cases of VALID/READ handshaking. Note that when source asserts VALID, the corresponding control information or data must also be available at the same time. The arrows in Fig. 2-8 indicate when the transfer occurs.

A transfer takes place at the positive edge of clock. Therefore, the source needs a register input to sample the READY signal. In the same way, the destination needs a register input to sample the VALID signal. Considering the situation of Fig. 2-8(c), we assume the source and destination use output registers not combination circuit,

they need one cycle to pull low VALID/READY and sample the VALID/READY again at T4 cycle. When they sample the VALID/READY again at T4, there should be another transfer which is an error. Therefore source and destination should use combinational circuit as output. In short, AXI protocol is suitable register input and combinational output circuit.

Fig. 2-8(a)VALID before READY (b)READY before VALID (c)VALID with READY

# 2.2.3 Transaction Ordering

Unlike AHB which only allows one granted transaction to access the bus interconnect until this transaction is finished, AXI allows granted transactions to access bus interconnect simultaneously. AXI uses "ID tag" to identify different transactions and enables out-of-order transaction completion.

Out-of-order transaction completion improves system performance in two ways:

- Bus interconnect allows the transactions to fast slave to complete in advance without waiting for the completion of the transaction to slow slave.

- Complex slave can return read data which is available for later transaction without waiting data of prior transaction.

AXI supports out-of-order transaction completion but it doesn't mean that there is no restriction of reordering transactions. The rule is "Transactions with the same ID must be completed in order". In other words, if a master requires multiple transactions to be completed in order, the master must assign the same ID to these transactions. If there is no restriction on in-order transaction completion, a master can assign different IDs to those transactions.

The ID assignment rule only applies to single master system. In multi-master

system, bus interconnect must append additional master ID to each transaction so that each transaction becomes unique in the system.

# 2.3 Comparison between AXI and AHB

### 2.3.1 Protocol and Architecture

Table 2-1 shows the main difference of protocol and architecture between AXI and AHB. There are seven key points as shown in below:

Table 2-1 Main difference between AXI and AHB

| AXI                                 | AHB                             |

|-------------------------------------|---------------------------------|

| 5 separated channels for address    | Pipelined address and data      |

| and data transfer                   | transfer                        |

| Every channel is uni-direction,     | Complex timing relation in      |

| except handshake signal             | read/write connection           |

| Easy register insertion to isolate  | Hard to isolate timing          |

| timing                              |                                 |

| Easy register insertion to increase | Limited operating frequency     |

| operating frequency                 |                                 |

| Burst-based transaction with only   | Every data transfer need a      |

| one address issued                  | address                         |

| Out-of-order transaction            | Fixed order transaction         |

| completion                          | completion                      |

| Suitable for memory controller      | Unfriendly to memory controller |

| with high initial latency           | device                          |

### 2.3.2 Latency and Bandwidth Utilization

The separate channels in AXI provide less latency in transfer task of read/write transaction pair than AHB. The reason is that AXI is able to perform read and write

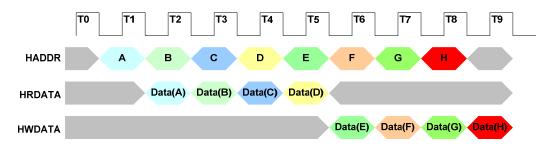

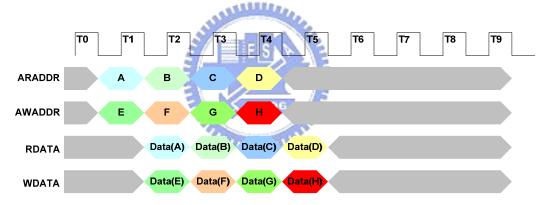

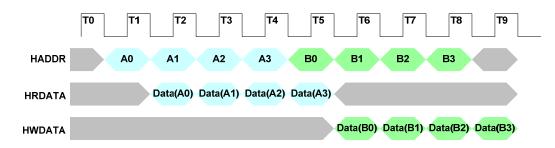

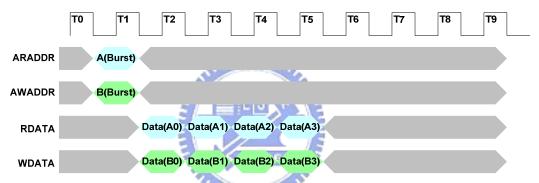

transactions at the same time. Fig. 2-9 and Fig. 2-10 show the difference in AHB and AXI transferring the same task. Fig. 2-9 shows AHB's continuous transfer. There are four read data transfers and four write data transfers. Form Fig. 2-9, all eight data transfers spend eight cycles from T2 to T9. Fig. 2-10 shows the same task in AXI bus. In AXI case, it only spends four cycles form T2 to T5.

Fig. 2-9 AHB continuous transfer

Fig. 2-10 AXI continuous transfer

As for the bandwidth utilization, AXI is more efficient than AHB. The reason is the same with the case of latency. Fig. 2-11 and Fig. 2-12 show the difference of AHB and AXI. In Fig. 2-11 and Fig. 2-12, AHB and AXI perform four beats read burst transaction and a four bests write burst transaction respectively. AHB totally takes eight cycles to complete these two transactions and the bandwidth utilization of data bus HRDATA/HWDATA is only 50%. As to AXI, it only takes four cycles to complete transactions and the bandwidth utilization of data bus RDATA/WDATA is 100%. The bandwidth utilization of AHB is naturally 50% and AXI can increase

bandwidth utilization to 100% based on transferring read/write transaction pair. In short, AXI is capable to perform read/write transaction pair which improves the latency of transaction and bandwidth utilization.

Fig. 2-11 AHB burst transaction

Fig. 2-12 AXI burst transaction

### 2.3.3 Hardware Cost

In this section, we analyze the protocol of AXI and AHB to estimate the hardware cost of them based on the amount of mux and register which they used. Table 2-2 is the parameters defined for the hardware cost calculation and the following are the formula for hardware cost. The constants in the formula are indispensable bits.

Table 2-2 Parameters for hardware cost calculation

| Parameter     | Description                                                 |  |

|---------------|-------------------------------------------------------------|--|

| Master_Num    | Number of masters                                           |  |

| Slave_Num     | Number of slaves                                            |  |

| Address_Width | The maximum width of used address                           |  |

| Data_Width    | Bus data width                                              |  |

| Buffer_Size   | Buffer size of master/slave wrapper; number of out-of-order |  |

|               | transactions                                                |  |

#### AHB master port register

$AHB\_Master\_Port\_Register = 4 + Data\_Width$

#### AHB slave port register

$AHB\_Slave\_Port\_Register = 11 + Address\_Width + Data\_Width + \left\lceil \log_2 Master\_Num \right\rceil$

#### AHB arbiter register

$AHB\_Arbiter\_Register = 24 + Address\_Width + Master\_Num \times 2$

#### AHB master buffer register

$AHB\_Master\_Buffer\_Register = 9 + Address\_Width + Data\_Width \times 16$

#### AHB slave buffer register

$AHN\_Slave\_BufferRegister = 9 + Address\_Width + Data\_Width \times 16$

#### **AXI** master port register

$AXI\_Master\_Port\_Register = 10 + Data\_Width + \left\lceil \log_2 Buffer\_Size \right\rceil \times 2$

#### **AXI** slave port register

$$AXI\_Slave\_Port\_Register = \\ 46 + Address\_Width \times 2 + Data\_Width + (\lceil \log_2 Buffer\_Size \rceil + \lceil \log_2 Master\_Num \rceil) \times 3$$

#### **AXI** interconnection master port register

$$AXI\_Interconnect\_Master\_Port\_Register =$$

$$46 + Address\_Width \times 2 + Data\_Width + \lceil \log_2 Buffer\_Size \rceil \times 3$$

#### **AXI** interconnection slave port register

$$AXI \_Interconnect \_Slave \_Port \_Register = 10 + Data \_Wdith + (\lceil log 2Master \_Num \rceil + \lceil log_2 Buffer \_Size \rceil) \times 2$$

#### **AXI interconnection WDATA table register**

$$AXI\_Interconne\ ct\_WDATA\_Table = Master\_Num \times Buffer\_Size \times \lceil \log_2 Slave\_Number \rceil$$

#### 1896

#### **AXI** master buffer register

$$AXI\_Master\_Buffer\_Register = (18 + Address\_Width + Data\_Width \times 16) \times Buffer\_Size$$

#### **AXI** slave buffer register

$$AXI\_Slave\_Buffer\_Register = \\ \left(17 + \left\lceil \log_2 Buffer\_Size \right\rceil + \left\lceil \log_2 Master\_Num \right\rceil + Address\_Width + Data\_Width \times 16 \right) \times Buffer\_Size \right]$$

#### AHB Master\_Num to 1 mux

$$AHB \_ Master \_ num \_ to \_ 1 \_ Mux = 15 + Address \_ Width + Data \_ Wdith$$

#### AHB Slave\_Num to 1 mux

$$AHB\_Slave\_num\_to\_1\_Mux = 19 + Data\_Wdith$$

#### AXI Master\_Num to 1 mux

$$AXI\_Master\_Num\_to\_1\_MUX =$$

$41 + \lceil \log_2 Buffer\_Size \rceil \times 3 + Address\_Width \times 2 + Data\_Width$

#### AXI Slave\_Num to 1 mux

$$AXI\_Slave\_Num\_to\_1\_MUX = 5 + \lceil \log_2 Buffer\_Size \rceil \times 2 + Data\_Width$$

According to the formula, we give a system to compare the hardware cost between AXI and AHB. The system consists of 5 masters, 11 slaves and AHB system has one buffer and AXI system has eight buffers. The arbitration policy in system is fixed priority so we ignore the registers in arbiter. If we ignore the register used in master and slave buffer, the hardware cost of AXI is 3.18 times of AHB. The hardware cost of AXI is more than AHB indeed.

Table 2-3 Comparison of hardware cost between AHB and AXI

|                                |                                   | AHB      | AXI      |

|--------------------------------|-----------------------------------|----------|----------|

|                                |                                   | 1 buffer | 8 buffer |

|                                | 1 master port                     | 36       | 48       |

| Wrapper interface register     | 1 slave port                      | 78       | 160      |

|                                | Total                             | 114      | 208      |

|                                | AHB arbiter                       | 66       | n/a      |

|                                | AXI interconnection 1 master port |          | 151      |

| Interconnection register       | AXI interconnection 1 Slave port  | n/a      | 54       |

|                                | AXI WDATA table                   |          | 160      |

|                                | Total                             | 66       | 365      |

|                                | 1 master buffer                   | 553      | 562      |

| Wrapper buffer register        | 1 slave buffer                    | 553      | 567      |

|                                | Total                             | 1106     | 1129     |

|                                | Master_Num to 1 mux               | 79       | 146      |

| Interconnection mux            | Slave_Num to 1 mux                | 51       | 43       |

|                                | Total                             | 130      | 189      |

| System register without buffer | 5 master, 11 slave                | 1104     | 3509     |

| System register with buffer    | 5 master, 11 slave                | 2210     | 12541    |

# **Chapter 3 Simulation Modeling for AXI**

# **System**

# 3.1 Overview of the Modeling Method

### 3.1.1 Transaction-Level-Modeling

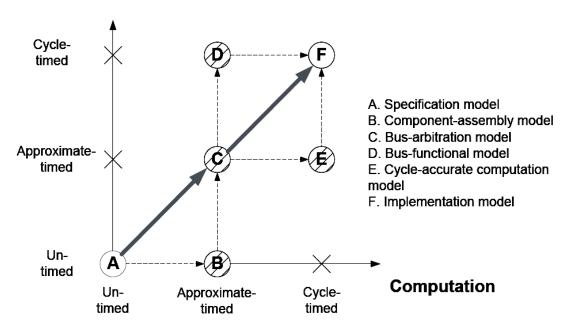

Transaction-level-modeling (TLM) [9] is a popular method to modeling a system. There are many kind of modeling level in modeling a system as shown in Fig. 3-1. We choose the node D in Fig. 3-1 as our modeling level. The communication model is modeled at transaction abstraction level. The computation model is modeled at behavior level, but we do not model the functions because of that our emphasis is on the bus communication. Choosing the node D, we check the correctness of bus protocol but also obtain precise analysis of system performance.

A read/write transaction on the AXI protocol can be decomposed into address/control transfer, data transfers and response transfer. Each transfer we used is referred as the transaction on each channel. This is because of supporting the AXI's capability of out-of-order transaction completion so we treat each transfer as an independent transaction and provide a cycle accurate timing transaction-level-modeling to archive our goal.

#### Communication

Fig. 3-1 System Modeling Graph

## 3.1.2 Using SystemC as Modeling Language

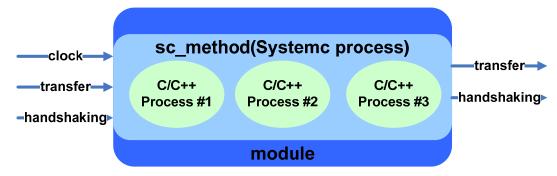

We use SystemC [11] as our modeling language. SystemC has been widely used to model system at various abstraction levels. The reason we decided to use SystemC is because the timing simulation kernel and primitives are already available. SystemC is also a subset of C++ so that we can also use regular C++ expressions. It's easy to use and there's no need to learn another language.

Fig. 3-2 shows how we use model a module using SystemC. The communication interface is implemented using SystemC input and output port. The SystemC processes related to the communication interface are implemented using SystemC method with clock edge trigger. Other internal SystemC processes are also implemented using SystemC method but some are event driven instead of clock driven. In addition to SystemC processes, there are also C/C++ processes inside the module. These un-timed processes implement basic computation and functionality whereas the SystemC processes provide cycle accurate behavior.

Fig. 3-2 Illustration of a modeling module

### 3.2 Traffic Generation

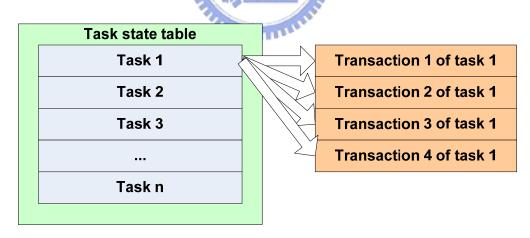

In this section, we introduce our traffic generation. The bus traffic is generated on transaction basis. Each transaction is generated by a bus access task which is associated with master device. Each master device possesses multiple bus access tasks. Many bus access tasks comprise a task state table (TST). In other words, each master device generates transactions from a task of TST as shown Fig. 3-3.

Fig. 3-3 Illustration of traffic generation

In the task state table, each task describes a set of transactions with the same direction and address pattern. Table 3-1 shows the fields of a task which includes current task number, next task number, task type, task transaction count, transaction burst length, pattern type, base address and vertical shift base address.

Table 3-1 Fields of a task state

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Possible value                        |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| 0     | Total task count                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Total task count                      |

| 1     | Current task number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Current task number                   |

| 2     | Next task number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Next task number                      |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0. Read channel idle                  |

| 2     | Task type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1. Write channel idle                 |

| 3     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2. Read transaction                   |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3. Write transaction                  |

| 4     | Transaction count of took                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1. Access transaction count           |

| 4     | Transaction count of task                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2. Idle cycle count                   |

| 5     | Burst length of transaction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Each access transaction burst length  |

|       | THE PARTY OF THE P | 1. Random                             |

| 6     | Access pattern type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2. 1D, horizontal continuously access |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3. 2D, vertical continuously access   |

| 7     | Base address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Base address of transaction           |

| 8     | Vertical shift base address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Vertical shift address of 2D access   |

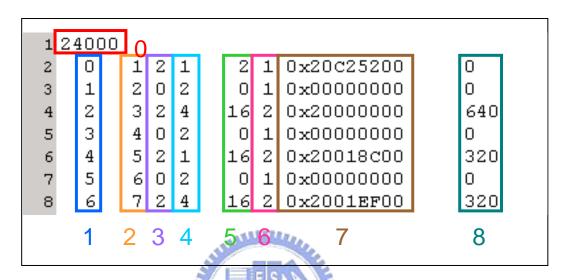

Fig. 3-4 is an example of a task state table file. The total task count is 24000. We take the row 8 of Fig. 3-4 as a example to explain how a set of transactions are generated from a task. The current task number is 6 and next task number is 7 meaning that when this task 6 finished it will take task 7 as next task. The remainder information means that this task generates 4 read transaction with burst length 16, base address 0x2001EF00 and the base address of each transaction shifts a base address 320.

This transaction generation using task state description allows us to specify bus access behavior at task level. In contrast to specify each transaction individually, we can specify related transaction using only one task. In other words, the traffic description can be greatly reduced by using task level description.

Fig. 3-4 Example of a task state table file

# 3.3 AXI Master

This subsection describes how to model master devices.

### 3.3.1 Master Behavior Modeling

To model the behavior of a master device, we use task state table (TST), transaction table (TT) and processing transaction table (PTT) to control the master device's behavior.

#### A. Task State Table

The task state table has mentioned in previous section. It is used to store all tasks of a master. However, a master may have multiple TST.

#### **B.** Transaction Table

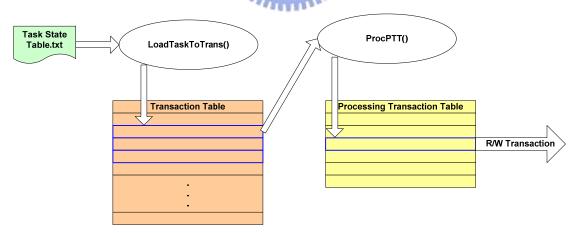

The transaction table exists in each master and each transaction table is associated with a TST. It is used to store the transactions which are generated by the tasks. Once the master device is reset, there is a process called LoadTaskToTrans() which starts to load all tasks and generates all transactions to store into TT.

### **C.** Processing Transaction Table

The processing transaction table actually is the buffer of a master device. The entry of it is a processing transaction which is a state machine. The detail of processing transaction will describe in later section. The processing transaction table stores the transactions from TT and is controlled by a process called ProcPTT(). The ProcPTT() checks the state of processing transaction to decide which entry is processing or is done to be able to refill a new transaction. We use different ProcPTT() to model different behavior of the master.

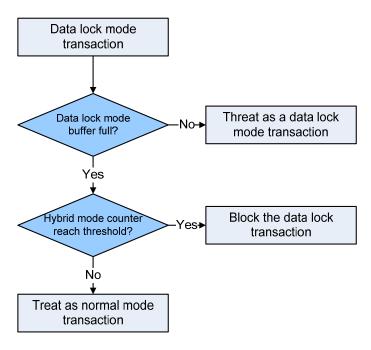

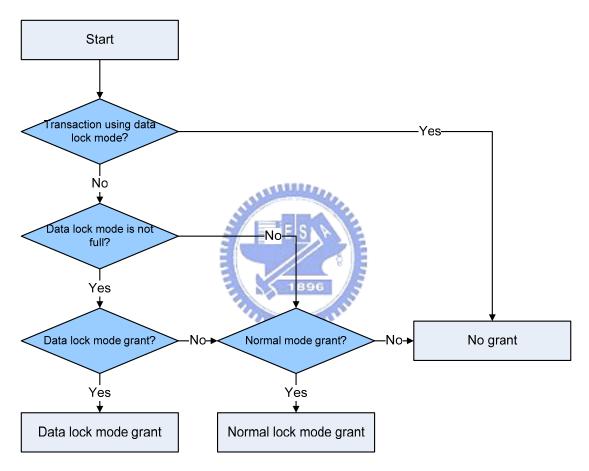

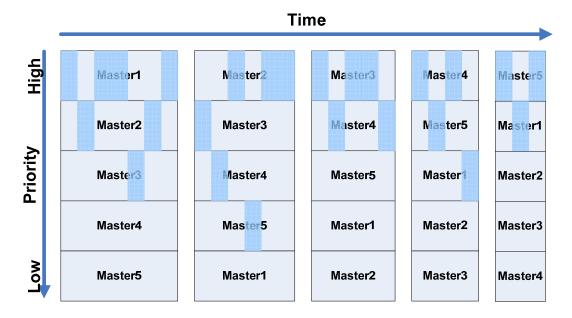

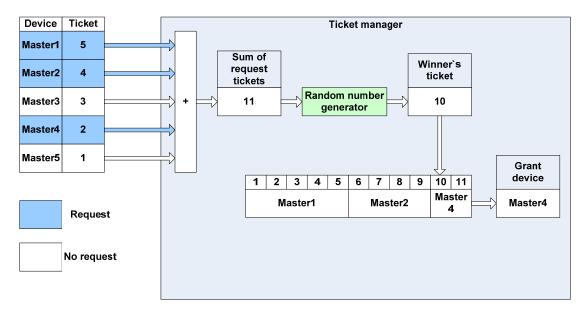

Fig. 3-5 show the relation of TST, TT, PTT, LoadTaskToTrans() and ProcPTT.