# 國立交通大學電子工程學系電子研究所博士論文

先進金氧半場效電晶體閘極工程對 改善元件特性及可靠度之研究 Gate Engineering of Advanced MOSFETs for Device Performance and Reliability Improvement

研究生:羅文政

指導教授 :張俊彦博士

趙天生博士

中華民國 九十六 年 九 月

# 先進金氧半場效電晶體閘極工程對 改善元件特性及可靠度之研究

# Gate Engineering of Advanced MOSFETs for Device Performance and Reliability Improvement

研究生:羅文政 Student: Wen-Cheng Lo

指導教授:張俊彥 博士 Advisor: Dr. Chun-Yen Chang 指導教授:趙天生 博士 Advisor: Dr. Tien-Sheng Chao

國立交通大學

電子工程學系》電子研究所

博士論文

A Dissertation

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical Engineering and Computer Engineering National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in

September 2007

Hsinchu, Taiwan, Republic of China

**Electronics Engineering**

中華民國 九十六 年 九 月

先進金氧半場效電晶體閘極工程對改善元件特性及可靠度之研究

研究生:羅文政 指導教授:張俊彦 博士

趙天生 博士

#### 國立交通大學電子工程學系電子研究所

#### 摘 要

在本論文中,我們針對先進元件的閘極工程整合部分對特性及可靠度的改善進行研究,涵蓋的內容包括淺溝渠隔離(STI)所造成的區域性單向壓縮應力在<110>及<100>通道方向的比較;在(111)晶向基版上利用氮化矽覆蓋層來改善N型金氧半場效電晶體的特性;以電漿氮化氧化層或熱氮化氧化層使用在雙閘極氧化層厚度的P型金氧半場效電晶體上在負電壓溫度不穩定性及熱載子注入等可靠度之比較,以及元件使用以給為基本材料之高介電係數介電層在正電壓溫度不穩定性分析中捕捉/反捕捉電子的可靠度分析。

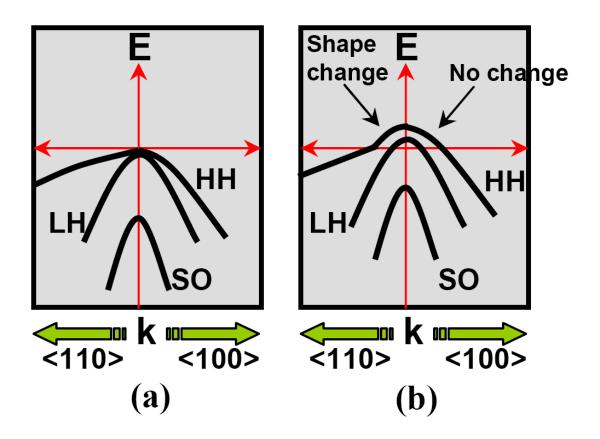

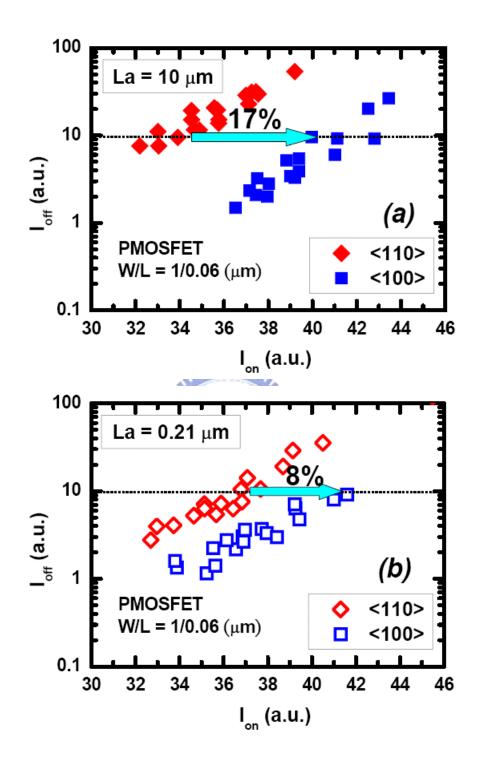

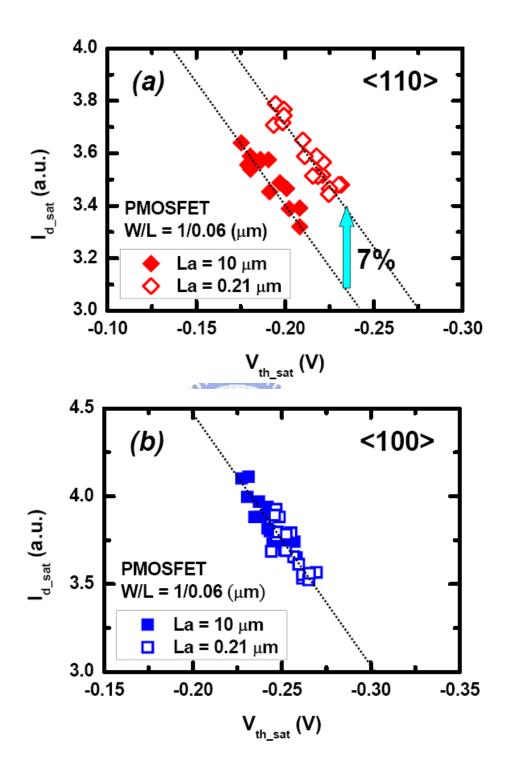

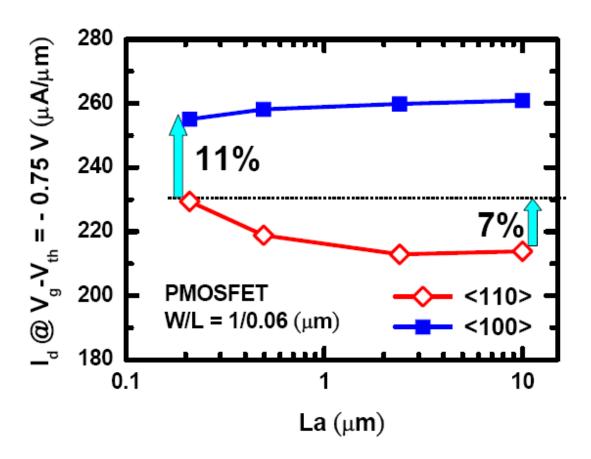

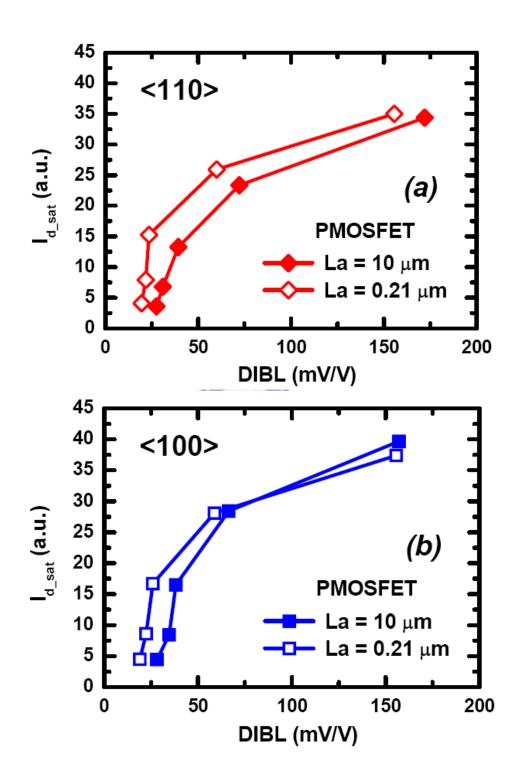

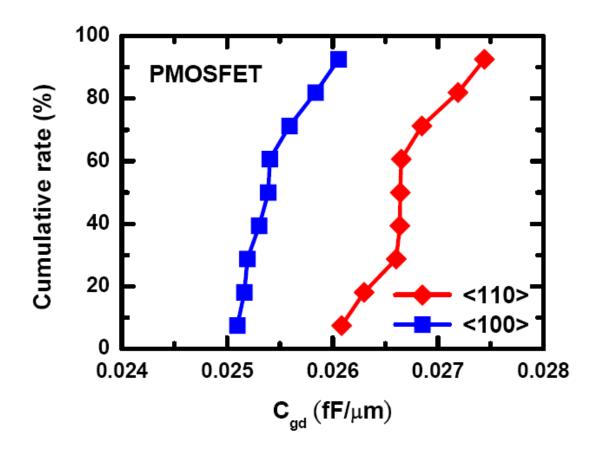

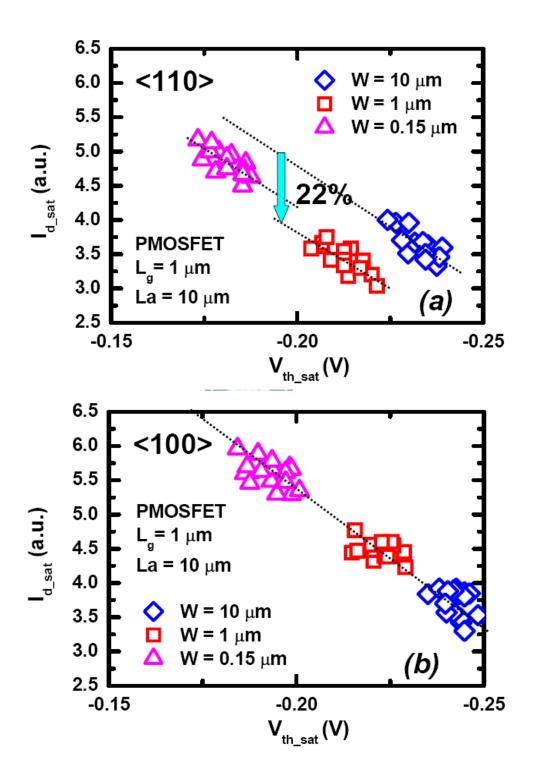

我們完整地研究了 65 奈米技術的 P型金氧半場效電晶體在<110>及<100>通道方向上對主動區佈局的相依性以及淺溝渠隔離所造成的單向壓縮應力對其特性的影響。對 65 奈米的 P型金氧半場效電晶體而言,當源/汲極長度從 0.21 微米增加到 10 微米,<100>通道方向在飽和汲極電流特性方面會比<110>通道的元件高出約從 8 % 提高到 15 %。 再者,我們也證明了對於不管在通道長度或寬度方向來說,<100>通道的元件對硼的擴 散有較高的抑制能力以及對淺溝渠隔離所造成的應力也有較低的感受度。

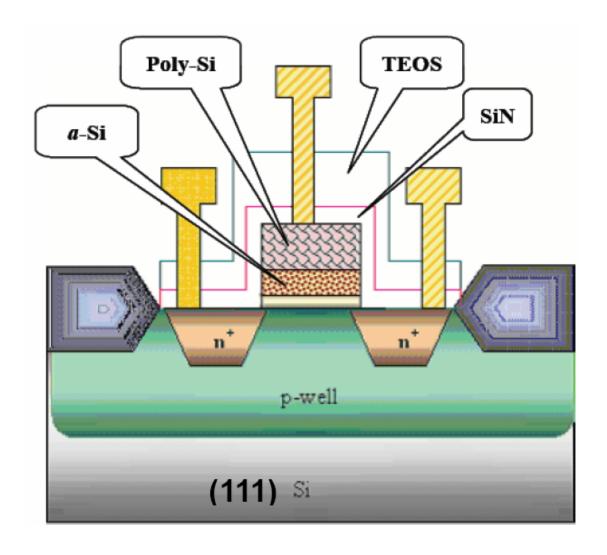

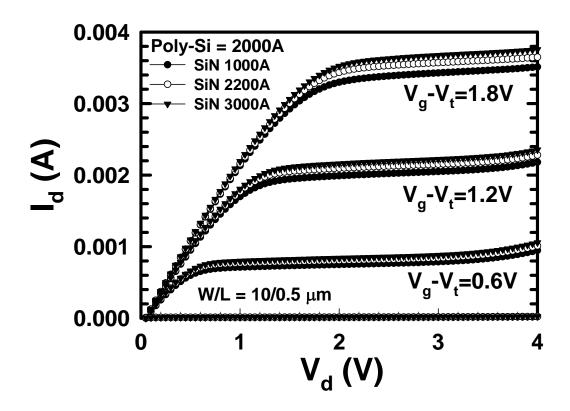

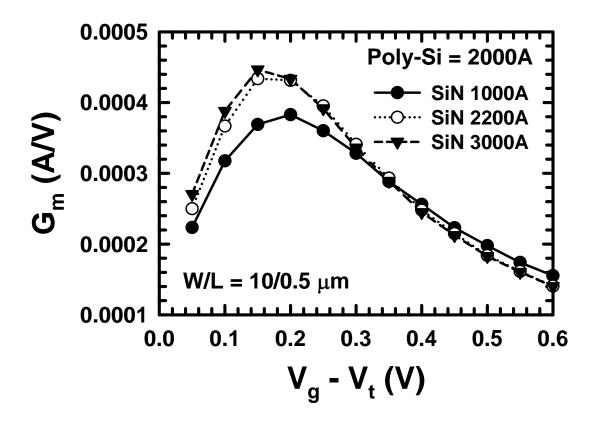

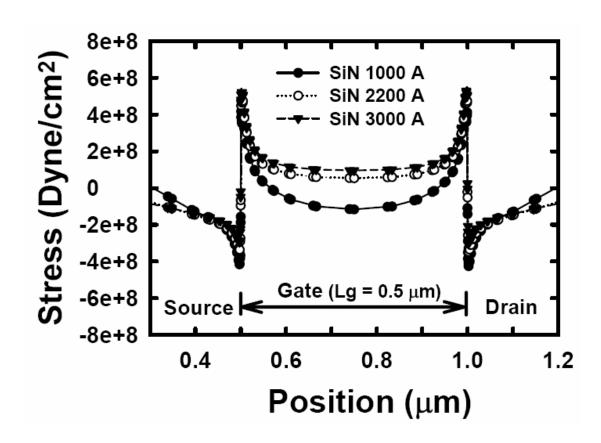

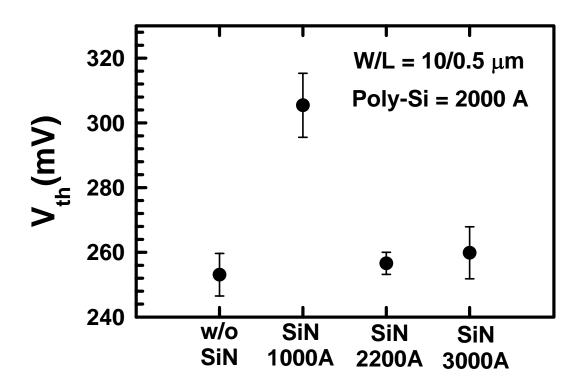

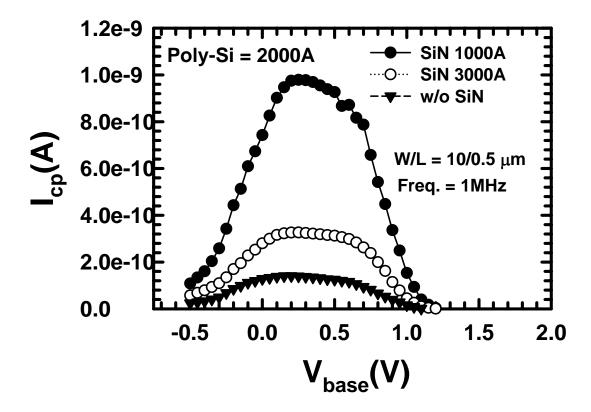

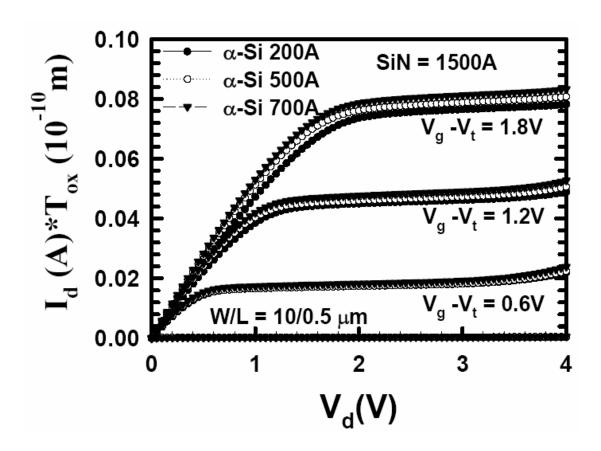

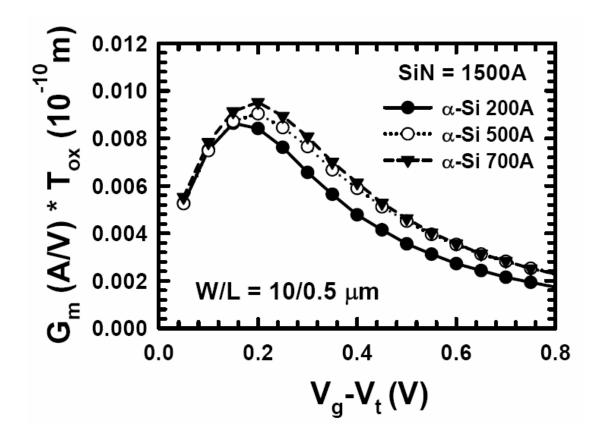

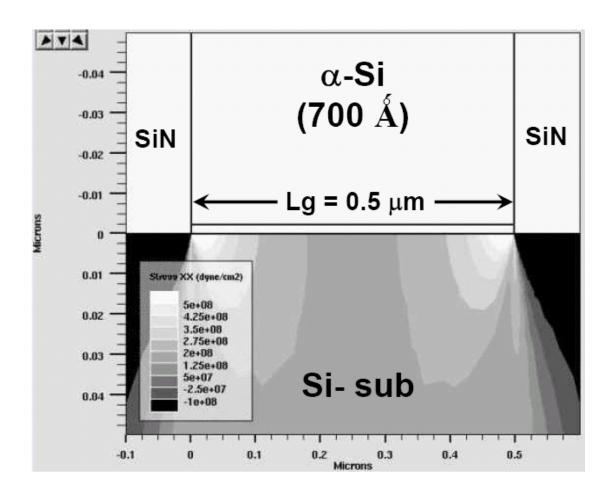

我們亦利用高應力之氮化矽覆蓋層以及非晶矽與多晶矽堆疊之閘極結構等區域應 變通道技術在(111)晶向矽基版上製作出 N 型金氧半場效電晶體。當氧化矽覆蓋層或非 晶矽層厚度增加時,元件的飽和電流及轉移電導也隨之上升。我們的實驗結果顯示相對 於非晶矽厚度為20奈米的元件而言,非晶矽厚度為70奈米的元件在飽和電流方面有約 6.7%的改善;在轉移電導方面則有約10.2%的增加。

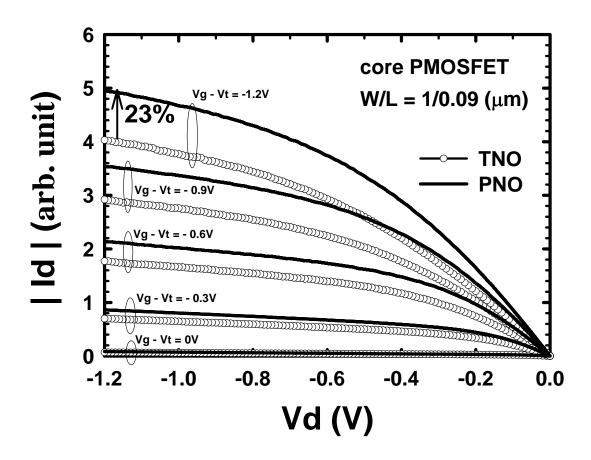

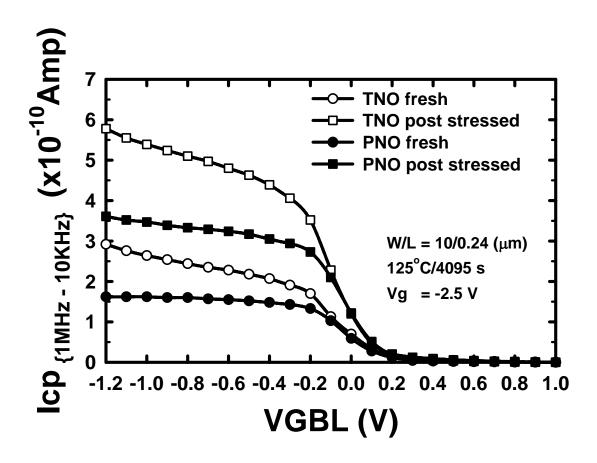

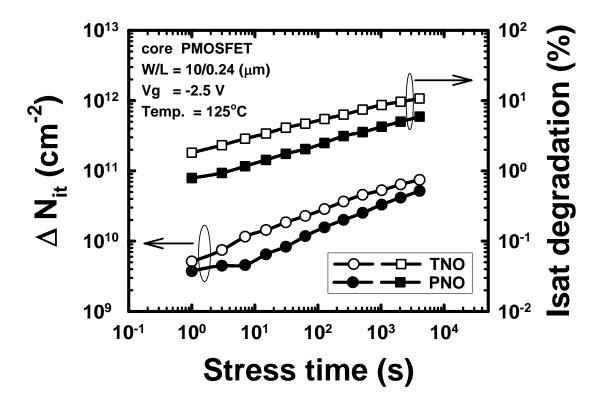

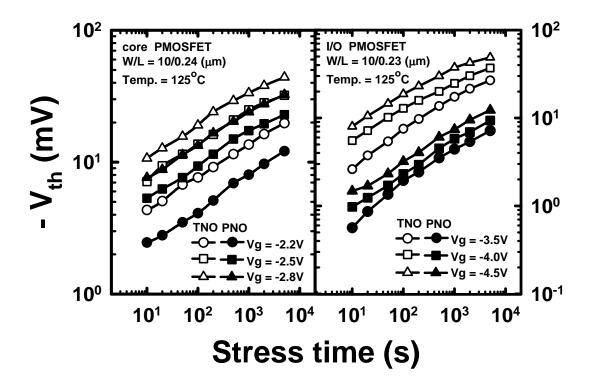

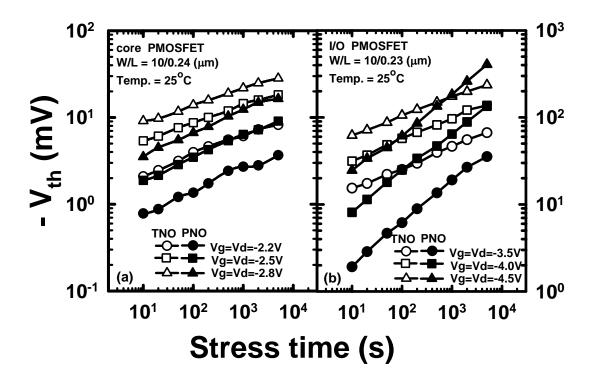

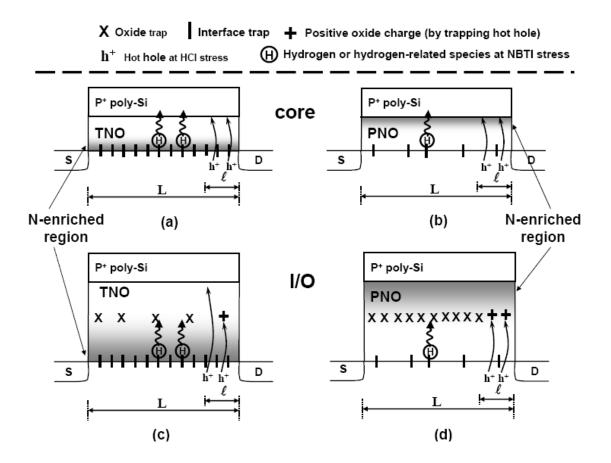

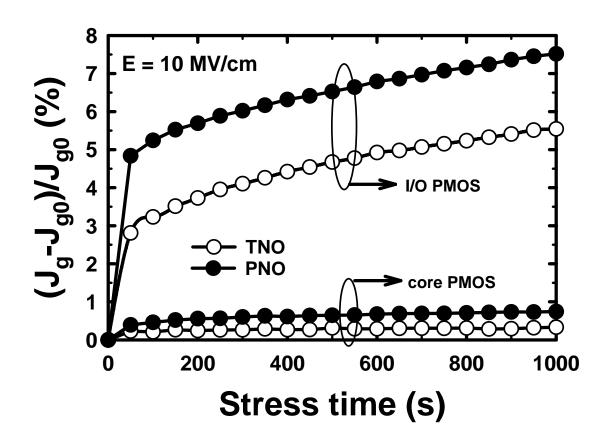

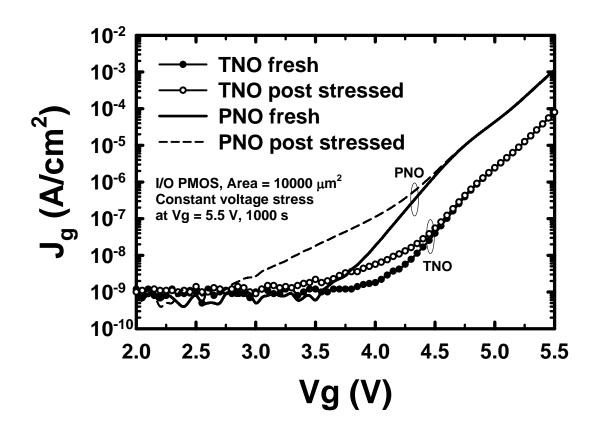

此外,我們比較了使用電漿氮化氧化層及熱氮化氧化層兩種不同開極介電層的核心 與輸入/輸出之 P 型金氧半場效電晶體受到負電壓溫度不穩定性及熱載子注入等可靠度 的影響。以電漿氮化氧化層作為開極氧化層材料之 P 型金氧半場效電晶體在漂移率方面 比熱氮化氧化層元件高了約 30 %,定電壓過驅動電流的值也比熱氮化氧化層高了約 23 %。相較於熱氮化氧化層,電漿氮化氧化層之核心 P 型金氧半場效電晶體因為在氧化 層與矽基版界面有較低之氮的濃度,所以有較佳的負電壓溫度不穩定性及熱載子注入抵 抗能力。然而,電漿氮化氧化層之輸入/輸出 P 型金氧半場效電晶體則表現出較高的熱 載子注入造成的特性退化率因為其有較高的氧化層內的主體缺陷。不過對於操作在一般 電壓之負電壓溫度不穩定性方面,仍是優於熱氮化氧化層歸因於較低的界面缺陷密度。

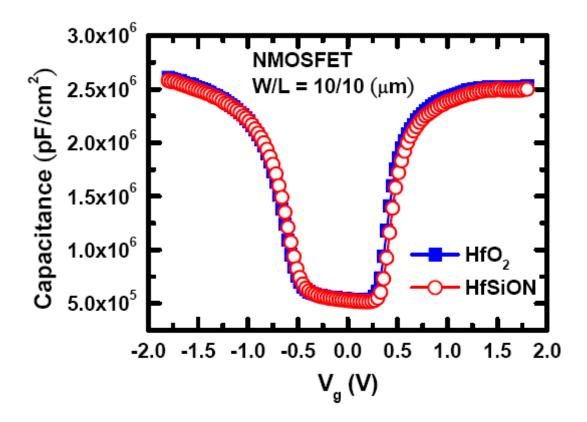

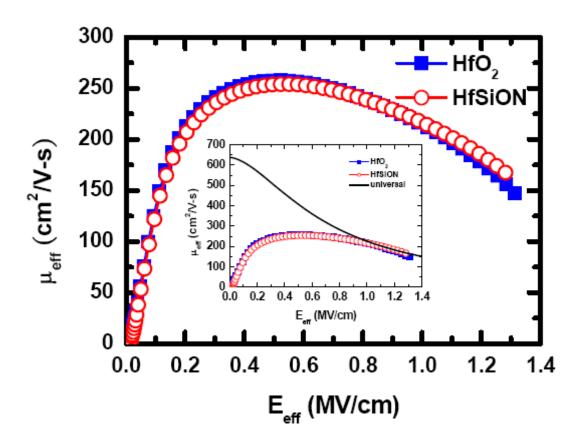

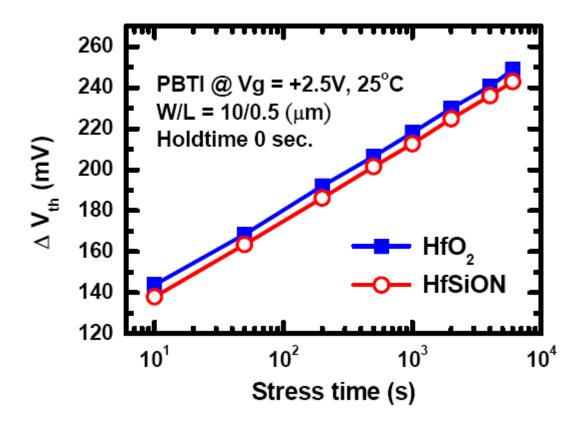

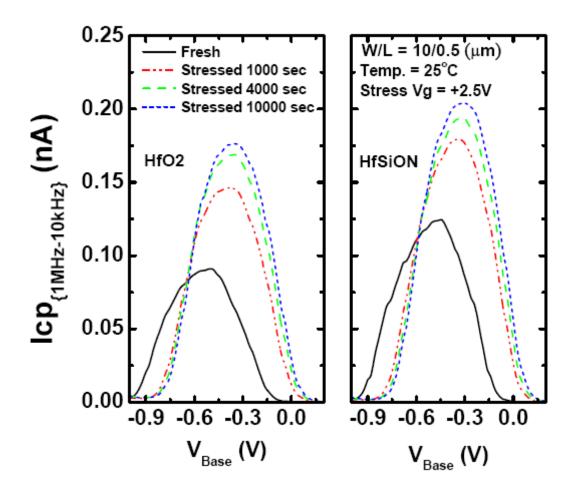

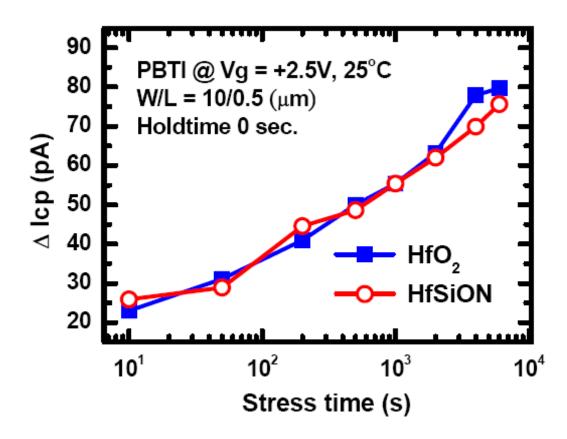

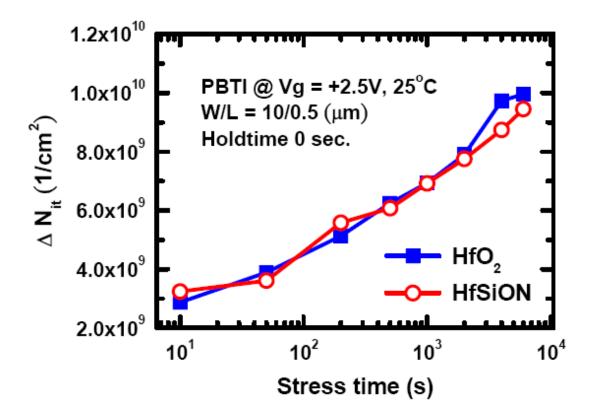

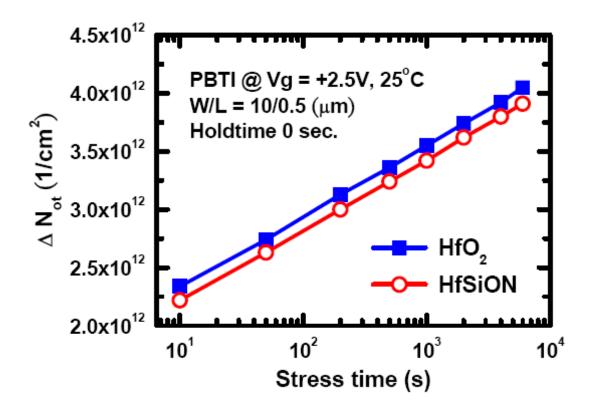

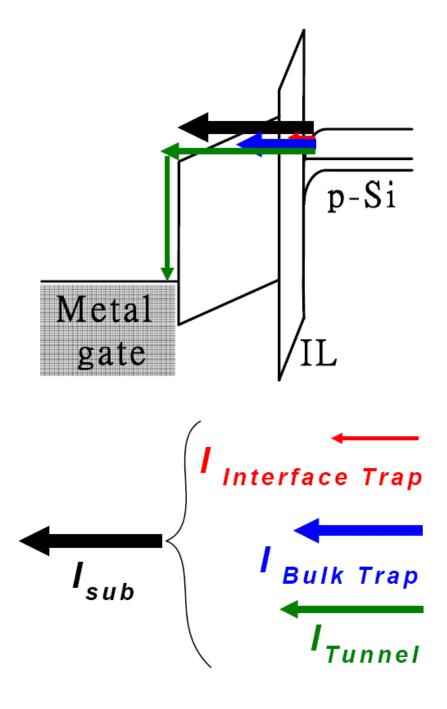

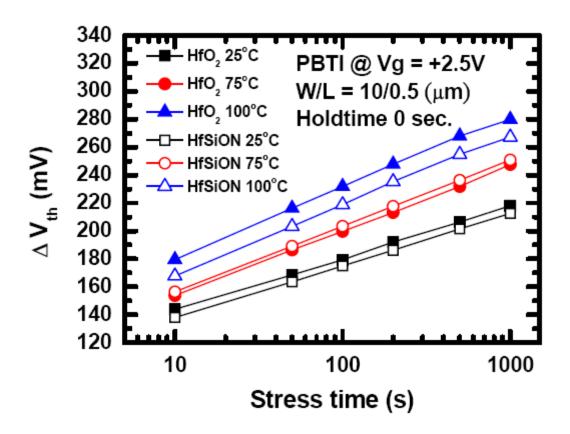

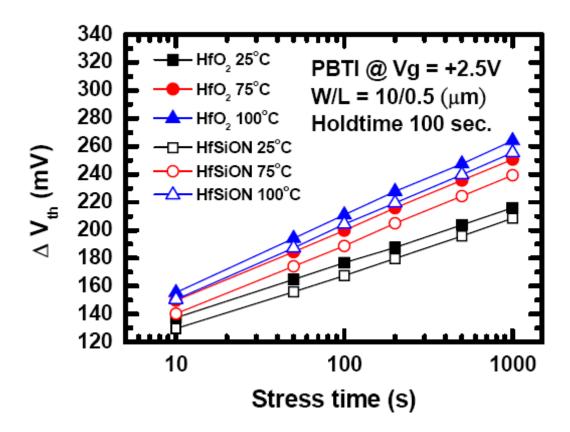

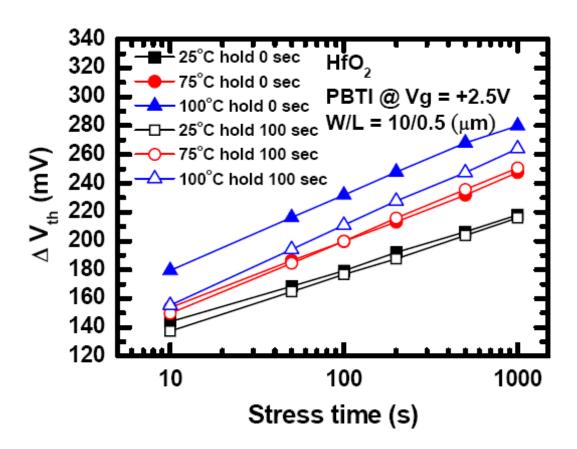

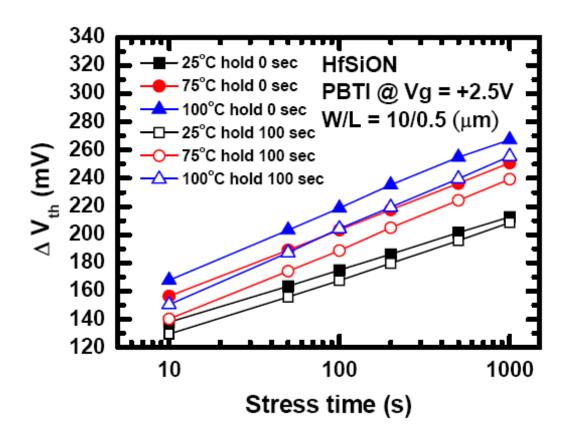

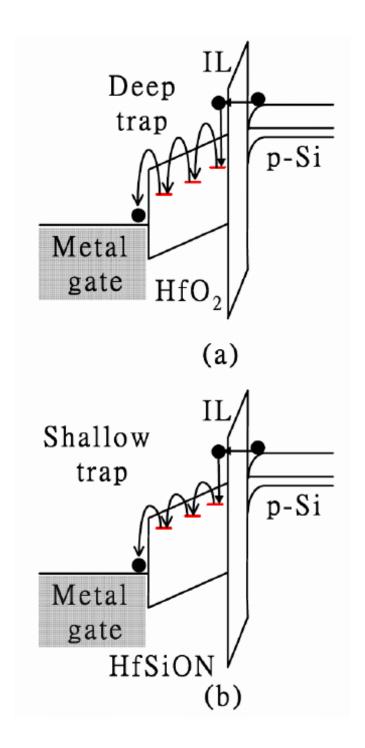

最後,我們論證了以二氧化鉿(HfO<sub>2</sub>)及鉿之氮氧化矽(HfSiON)兩種材料作為閘極氧化層的N型金氧半場效電晶體在正電壓溫度不穩定性可靠度的特性退化。對以鉿為基本材料之高介電係數介電層而言,在正電壓溫度不穩定性可靠度測試期間所產生的氧化層主體缺陷會主導元件的正電壓溫度不穩定性之特性退化。在正電壓溫度不穩定性可靠度測試中,較低的臨界啟始電壓退化以及氧化層主體缺陷產生率,證明了鉿之氮氧化矽的薄膜品質優於二氧化鉿。此外,在正電壓溫度不穩定性可靠度測試期間,相對於二氧化鉿介電層而言,鉿之氮氧化矽則有較淺的電荷捕捉能階。

**Gate Engineering of Advanced MOSFETs**

for Device Performance and Reliability Improvement

Student: Wen-Cheng Lo

Advisors: Dr. Chun-Yen Chang

Dr. Tien-Sheng Chao

Department of Electronics Engineering & Institute of Electronics

National Chiao Tung Univerity

Abstract

In this dissertation, we investigated the gate engineering integration for advanced device

performance and reliability improvement including the comparison of STI-induced local

uniaxial compressive stress in <110>- and <100>-channel directions, the use of SiN capping

layer on (111) orientation substrate to improve the NMOSFET performance, the reliability

comparisons in negative-bias temperature instability (NBTI) and hot-carrier injection (HCI)

between dual gate oxide PMOSFETs using plasma nitrided oxide (PNO) and thermally

positive-bias nitrided instability oxide (TNO) and the temperature (PBTI)

trapping/de-trapping reliability issues for devices using Hf-based high-k dielectrics.

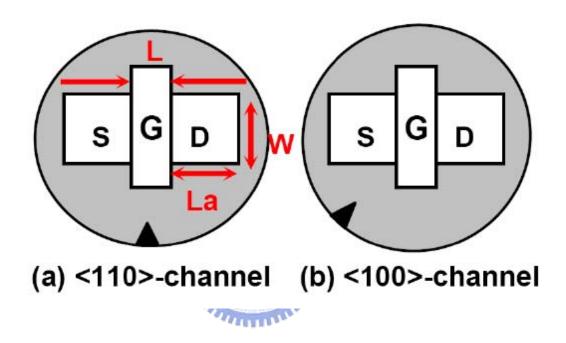

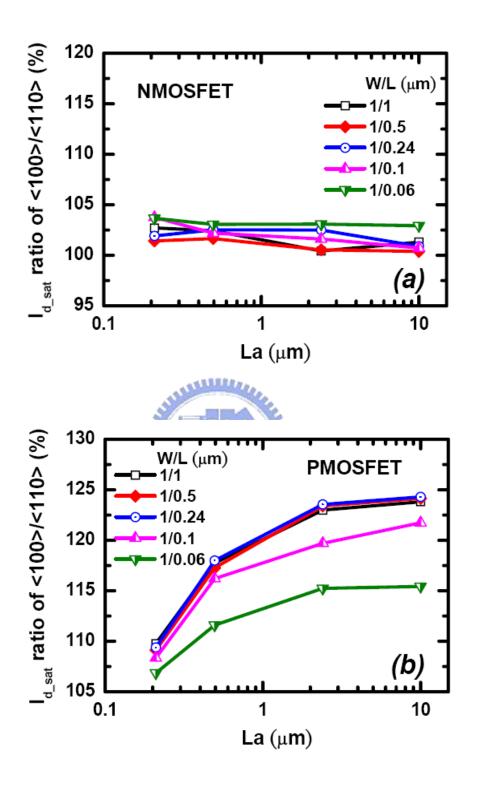

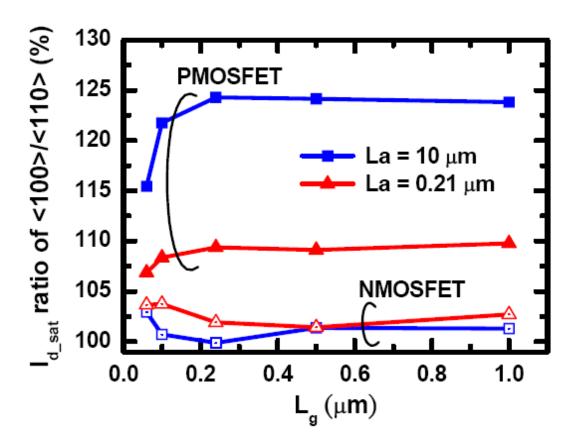

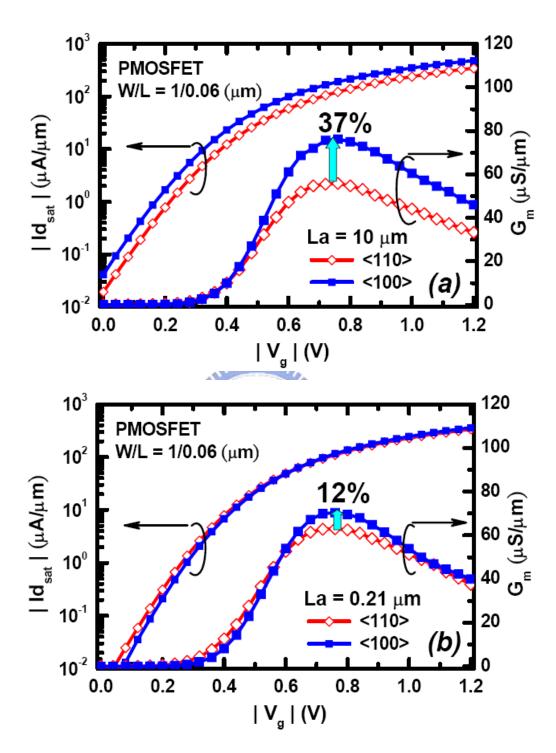

Active-region layout dependence and STI-induced uniaxial compressive stress impact on

the performance of 65 nm technology PMOSFETs with <110>- and <100>-channel directions

were fully investigated. For 65 nm PMOSFET, <100>-channel show as higher as about 8 ~

iii

15% in Id\_sat than <110>-channel devices as S/D length increased from 0.21 m to 10 m. Furthermore, higher immunity to boron diffusion and less sensitivity on STI-induced strain in both of channel length and width directions for <100>-channel devices were also demonstrated.

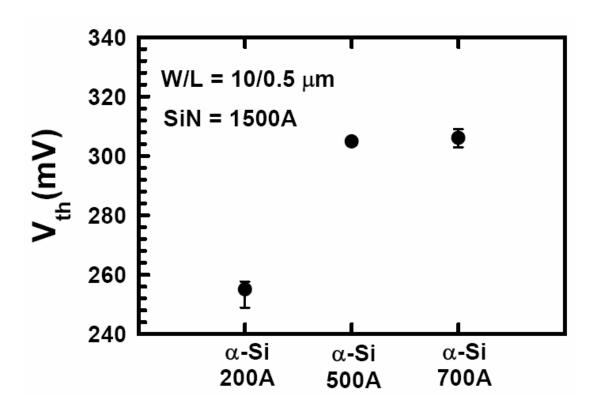

We also investigated NMOSEFT fabricated with local strained channel techniques on a (111) Si substrate using a SiN capping layer with high mechanical stress and the stack gate of amorphous silicon ( $\alpha$ -Si) and polycrystalline silicon (poly-Si). The on-current and transconductance ( $G_m$ ) increased with increasing SiN capping layer or  $\alpha$ -Si layer thickness. Our experimental results show that devices with a 700 Å  $\alpha$ -Si layer show a 6.7% on-current improvement percentage relative to those with a 200 Å  $\alpha$ -Si layer, and a corresponding  $G_m$  improvement percentage of 10.2%.

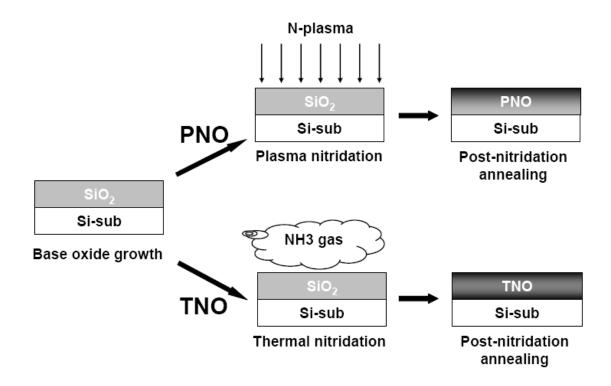

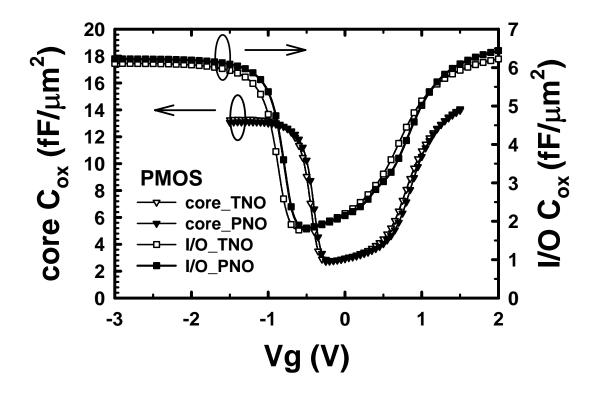

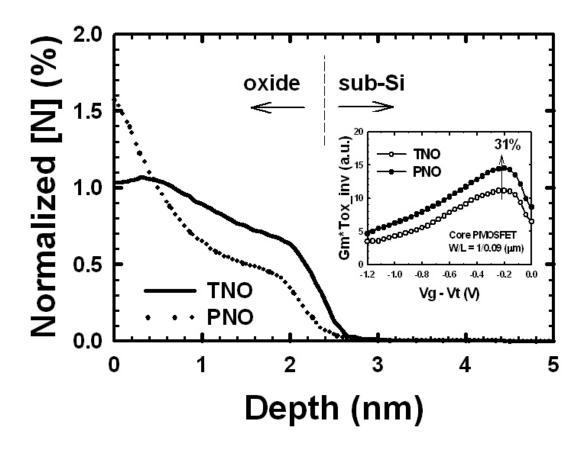

Besides, we compared the effects of NBTI and HCI on the core and input/output (I/O) PMOSFET fabricated using the different gate dielectrics of PNO and TNO. The mobility and constant overdrive current of the PMOSFETs fabricated using PNO as a gate oxide material are about 30% and 23% higher than those of the devices fabricated using TNO, respectively. The core PMOSFETs fabricated using PNO show a better NBTI and HCI immunity than those fabricated using TNO owing to the lower nitrogen concentration at the SiO<sub>2</sub>/Si-substrate interface. However, the I/O PMOSFETs fabricated using PNO show a higher HCI-induced degradation rate because of a higher oxide bulk trap density but a better NBTI than the

devices fabricated using TNO at a normal stressed bias due to a low interface trap density.

In the final part, PBTI degradation for HfO<sub>2</sub> and HfSiON NMOSFETs with the metal gate electrode has been successfully demonstrated. The generated oxide trap during PBTI stress will dominate the PBTI characteristics for Hf-based gate dielectrics. The reduction of threshold voltage degradation and oxide trap generation under PBTI stress indicates that the HfSiON thin film quality is better than HfO<sub>2</sub>. In addition, as compared to HfO<sub>2</sub> dielectrics, the HfSiON has shallower charge trapping level under PBTI stress.

#### 致 謝

終於…畢業了!一本薄薄百來頁的博士論文,也許可以顯示出了這幾年的研究成果,但卻描述不出這些年遇到的挫折、低潮與掙扎。無論如何,總算是完成了我人生的 一個重要目標。

首先要感謝我的指導教授張俊彥博士在這個領域上給我的指導與幫助,從老師身上 也讓我看到了身為一個領導者該有的風範。另外,我還要感謝共同指導教授趙天生博士。 老師對我來說,是亦師亦友。對於有關我畢業的事情,總是比我還要關心與在乎。老師 的一句話:「家庭就是我們最大的事業」,讓我感動到幾度熱淚盈框,我會一直將這句話 謹記在心並奉為圭臬。

感謝在我博士求學生涯帶我、指導我的張勝傑學長與李耀仁學長。在學校求學以及在台積電工作的期間,因為有張勝傑學長對我的許多指導與幫助,讓我學到很多,也讓我人生規劃明確的多。李耀仁學長在學術實驗上嚴謹的態度是我最推崇的,在我畢業前這一年,也給予我很多課業上的討論與想法。在此也感謝在台積電工作期間一起工作的所有同事們,你們讓我的人生眼界寬廣不少。也感謝一起渡過漫長求學路的實驗室成員們,讓我在學校的生活更加多采多姿。相信不久之後在職場中,我們會再相遇的。

要感謝的,還有一群交心的麻吉幫兄弟:偉成(軟成)、弘彬(娘彬)、亦臺(娘臺)、百騏(百娘)、克竣(克軟)、智維等等,和你們的兄弟聚會,是我最輕鬆、最快樂的時光。在我學業跟感情低潮那時,能夠遇到你們這群交心的好兄弟,是我最開心也最珍惜的一件事!

感謝在我漫長求學期間曾經陪在我身邊、離開我身邊的女人,妳們豐富了我的感情生活,讓我能夠用更成熟、更自省的心態去完善我以後的感情與人生。感謝 Foxy 的關心與包容,讓我在最後這段壓力最大,脾氣最煩躁的關頭能夠順利將論文衝刺出來。

最後,謹以這本博士論文,獻給我的爸媽,沒有你們無怨無悔的犧牲奉獻,不會有 今日的我。還有我的老弟。我的成就,因為有你們,一切才具有了意義。你們永遠都是 我最最愛的家人!

2007 于 風城 • 交大

# **Contents**

| Abstract (in | Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | i       |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Abstract (in | English)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | iii     |

| Acknowledg   | ge (in Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | vi      |

| Contents     | •••••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | vii     |

| Table Capti  | ions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | X       |

| Figure Cap   | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | xi      |

| Chapter 1    | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1       |

|              | 1-1 General background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1       |

|              | 1-2 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6       |

|              | 1-2 Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9       |

|              | 1-4 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12      |

| Chapter 2    | Systematical Comparisons on Performance Improvements STI-Induced Strain between <110>- and <100>- Ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •       |

|              | Directions Sub-65 nm PMOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |         |

|              | 2-1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 23      |

|              | 2-2 Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25      |

|              | 2-3 Results and discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 26      |

|              | 2-4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 31      |

|              | 2-5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 32      |

| Chapter 3    | Performance Enhancement by Local Strain in <110> Connection of the contract of | sistors |

|              | on (111) Substrate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40      |

|           | 3-1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|           | 3-2 Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 49               |

|           | 3-3 Results and discussions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51               |

|           | 3-3-1 Single-poly-Si gate structure with SiN cap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ping layer of    |

|           | different thicknesses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51               |

|           | 3-3-2 Stack of α-Si and Poly-Si gate with SiN capping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | g layer of fixed |

|           | thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54               |

|           | 3-4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56               |

|           | 3-5 References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 57               |

| Chapter 4 | Systematical Study of Reliability Issues in Plasma-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Nitrided and     |

|           | Thermally Nitrided Oxides for Advanced Dual-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Gate Oxide       |

|           | PMOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 70               |

|           | AND THE PARTY OF T |                  |

|           | 4-1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 70               |

|           | 4-2 Experiment E.S.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71               |