# 國立交通大學

# 電子工程學系 電子研究所 博士論 文

應用於系統面板之各種薄膜電晶體元件結構之研究 Study on the Thin Film Transistors with Various Device Structures for System-on-Panel Applications

研究生:廖大傳Ta-Chuan Liao指導教授:鄭晃忠 博士Dr. Huang-Chung Cheng

中華民國九十八年八月

#### 應用於系統面板之各種薄膜電晶體元件結構之研究

# Study on the Thin Film Transistors with Various Device Structures for System-on-Panel Applications

研究生:廖大傳Student: Ta-Chuan Liao指導教授:鄭晃忠博士Advisor: Dr. Huang-Chung Cheng

國立交通大學

電子工程學系 電子研究所

Submitted to Department of Electronics Engineering and Institute of Electronics College of Electrical Engineering and Computer Engineering National Chiao-Tung University In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electronics Engineering 2009 Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 八 月

#### 應用於系統面板之各種薄膜電晶體元件結構之研究

研究生:廖大傳

#### 指導教授:鄭晃忠 博士

#### 國立交通大學電子工程學系暨電子研究所

#### 摘要

在此論文中,分別針對汲極、開極與通道等三項工程提出不同改善結構與技術以提 昇低溫多晶矽薄膜電晶體之電特性。除此之外,為使系統面板能更具多元化,我們也開 發以低溫多晶矽薄膜電晶體技術為基礎之非揮發性記憶體與場發射元件。

首先,針對低溫多晶矽薄膜電晶體汲極工程的開發,有別於傳統須複雜製程或額外 光罩來製做的降電場結構,我們提出僅需簡單選擇性蝕刻法與臨場真空封裝技術製作出 具有真空腔洞之T型開極低溫多晶矽薄膜電晶體,利用製做出的偏移區域(offset region) 與真空腔洞可有效降低其汲極端之大電場,因而可大幅降低漏電流、提高開關電流比、 降低紐結電流(kink current)、與改善可靠度問題。

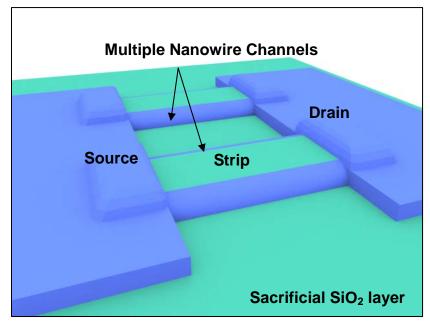

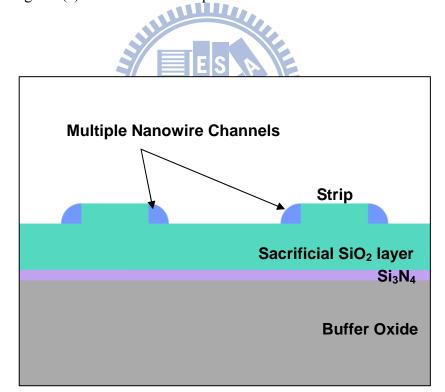

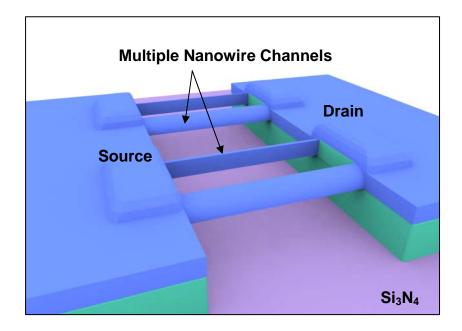

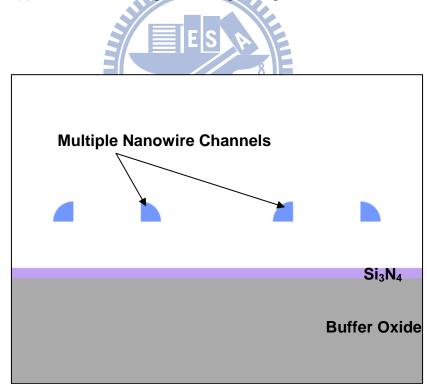

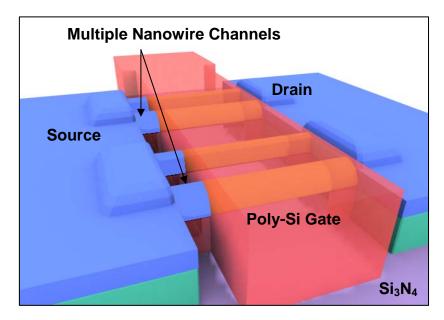

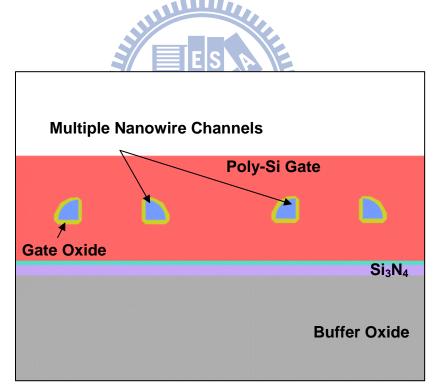

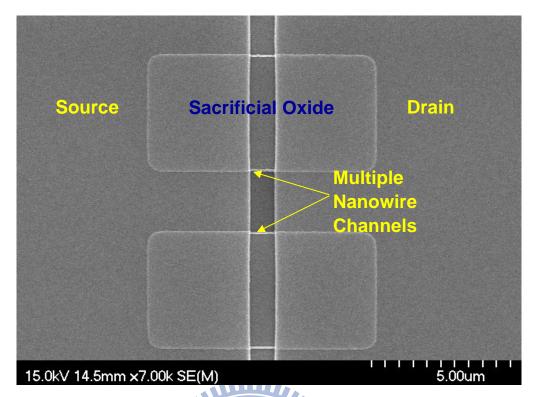

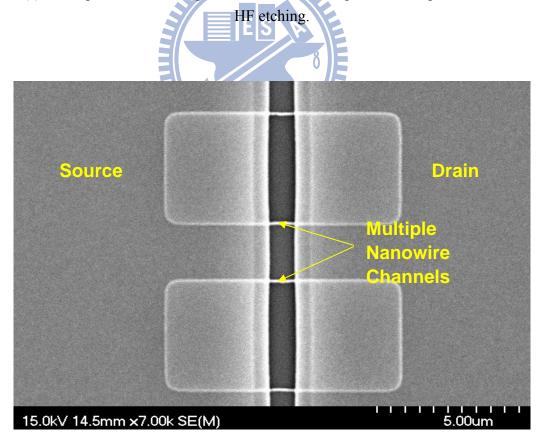

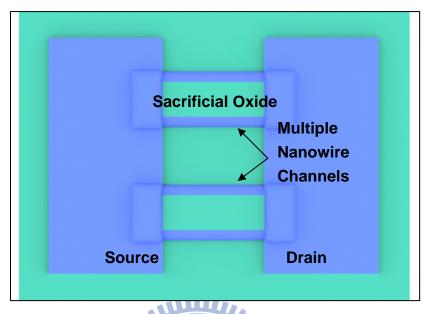

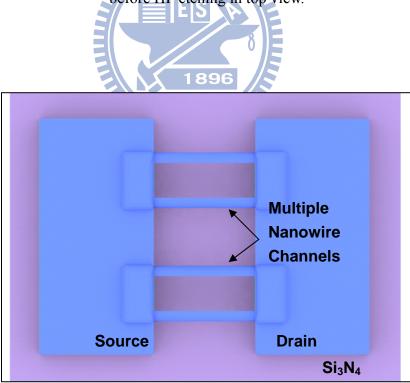

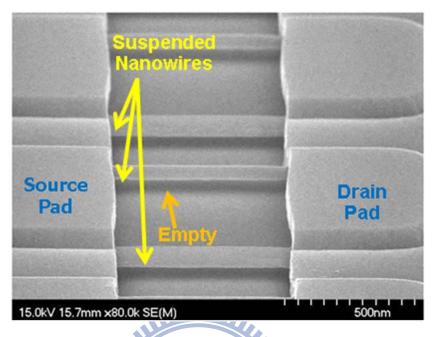

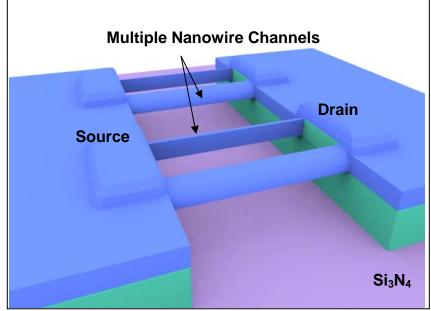

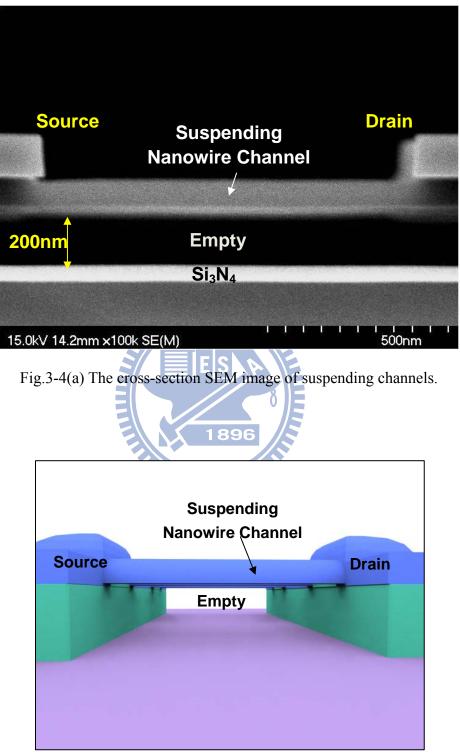

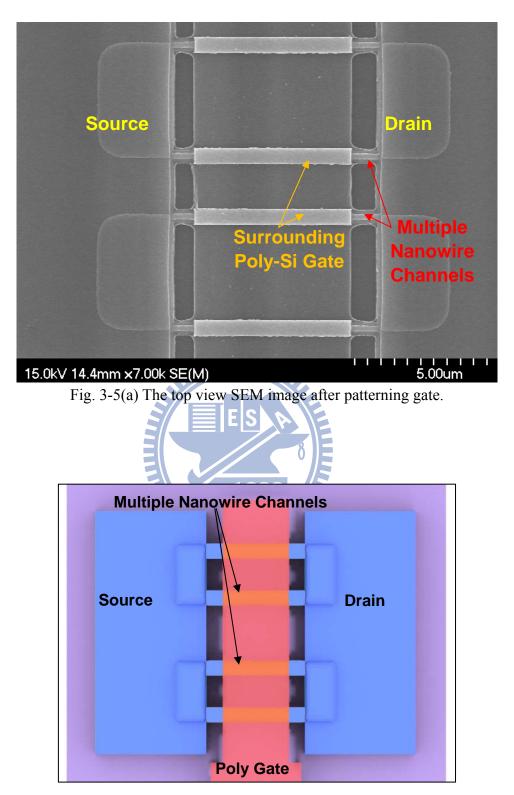

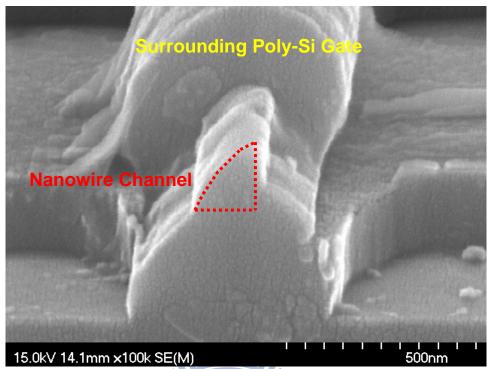

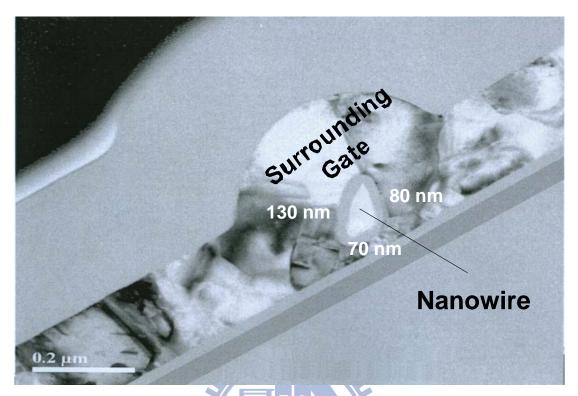

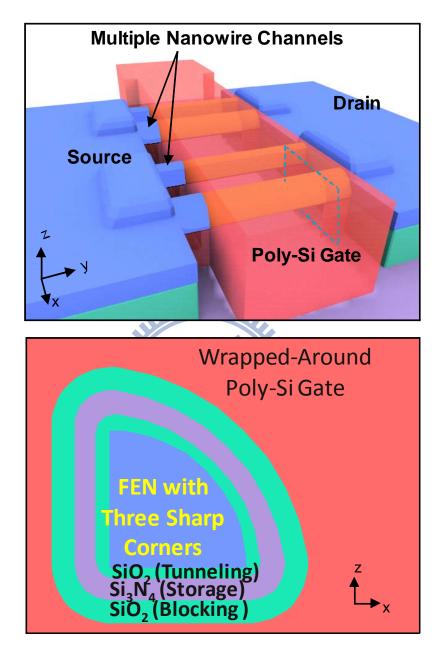

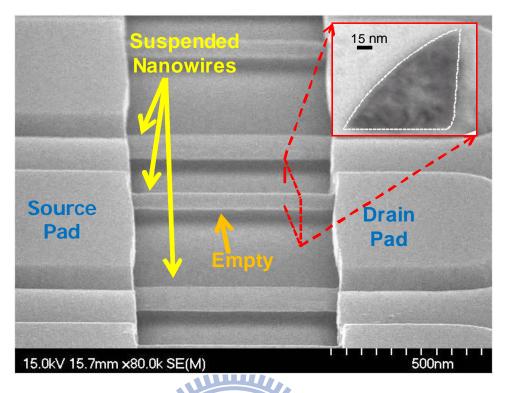

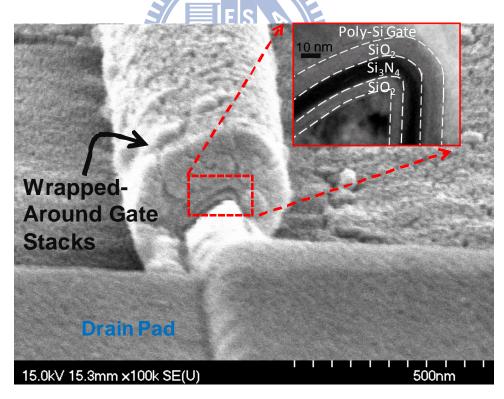

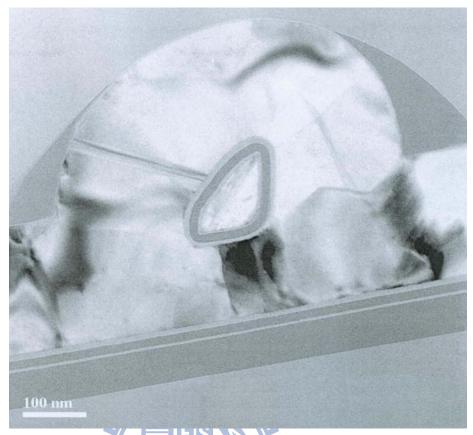

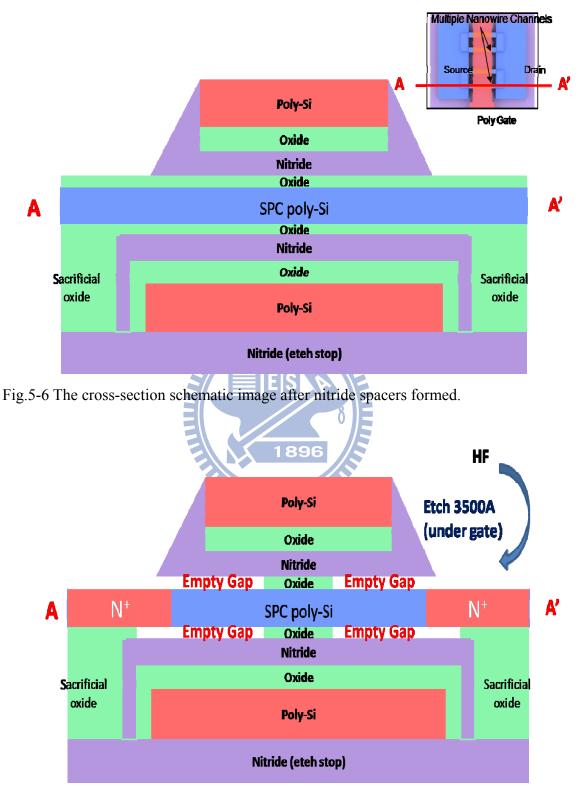

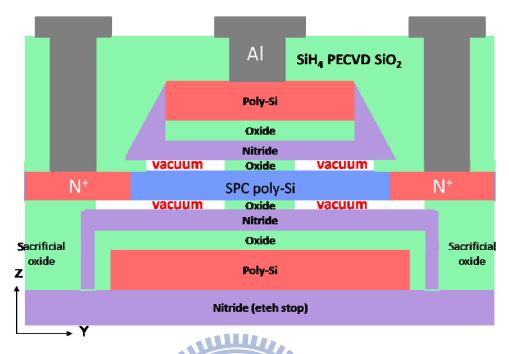

其次,針對低溫多晶矽薄膜電晶體閘極工程的開發,我們提出一種簡單且低成本的 方式來製作新穎環繞式閘極與多重奈米通道之複晶矽薄膜電晶體。利用簡單間隙壁技術 (spacer technique)來製作高寬比趨近於一之奈米通道,而不需先進微影技術。並利用蝕 刻犧牲氧化層來讓奈米通道懸空以至於能被閘極完全包覆形成環繞閘極結構。製作出的 具環繞閘極與多重奈米通道之複晶矽薄膜電晶體和傳統的元件比較起來有相當良好的 電特性。該元件擁有較高載子移動率、較低的臨界電壓、較高開關電流比、與極佳之短 通道效應之抑制能力。這些改善主要可歸功於環繞閘極增強閘極之控制能力、奈米線中 的三個尖端與較少的缺陷量。

針對通道工程的改善,我們提出兩種新穎製程方式可製作具高結晶性矽奈米線之多 晶矽薄膜電晶體。第一種為控制最佳準分子雷射能量,直接對奈米線做結晶,由於利用 前敘之隙壁技術會造成奈米線區域之非晶矽較薄,而汲/源區域較厚,故在雷射照射下, 可控制晶種分別由汲/源區域兩區域成長過來,因而可達成只有一個晶界之奈米線,利 用該法製作出的環繞式開極薄膜電晶體擁有 273 cm<sup>2</sup>/V-s 之場效載子移動率。另一種, 則利用奈米尺寸之氮化矽隙壁(nitride spacer)當硬光罩直接蝕刻定義奈米線在連續側向 固化結晶法(sequential-lateral-solidification)之大晶粒多晶矽薄膜上,由於奈米線尺寸遠 小於大矽晶粒的尺寸,故可製作出幾乎是單晶的矽奈米線,利用該法製作出的環繞式開 極薄膜電晶體擁有 **596** cm<sup>2</sup>/V-s 之場效載子移動率與極陡之次臨界擺幅(101 mV/decade),因此非常適用於未來系統面板(system-on-panel)的應用。

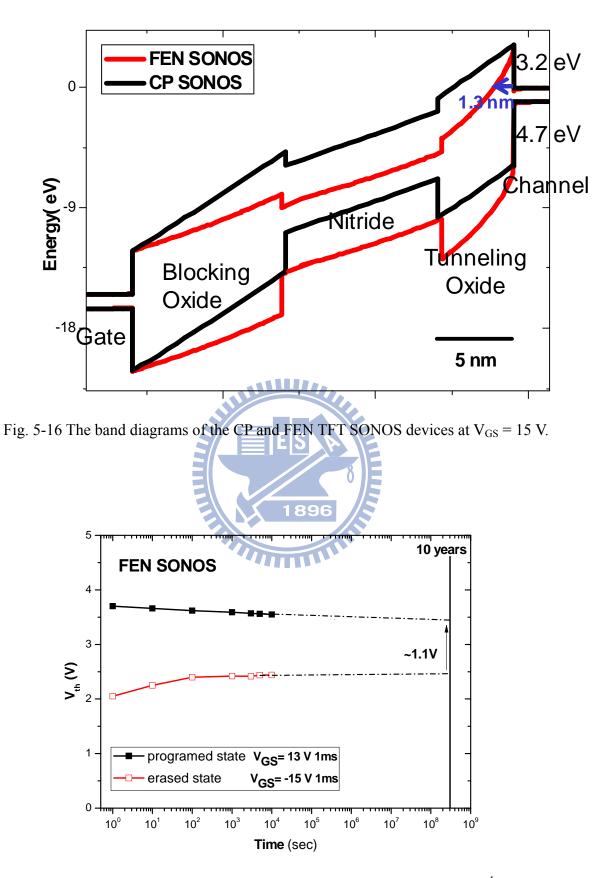

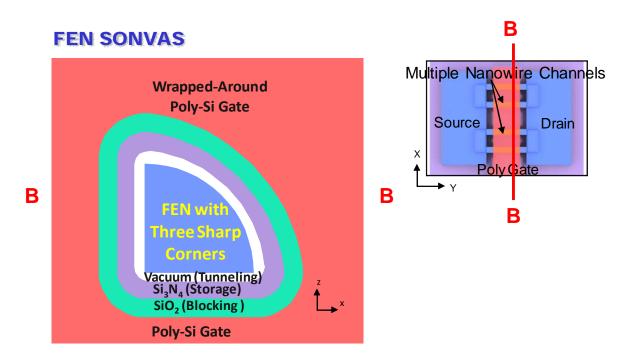

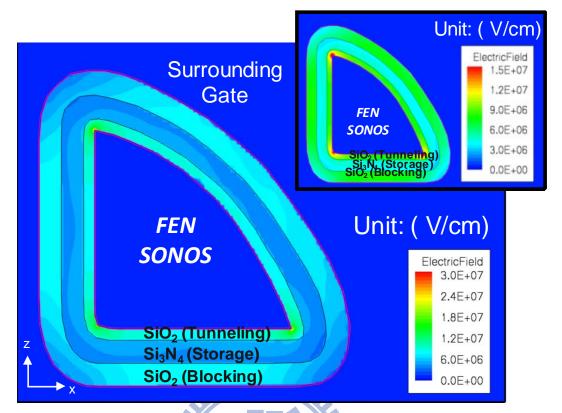

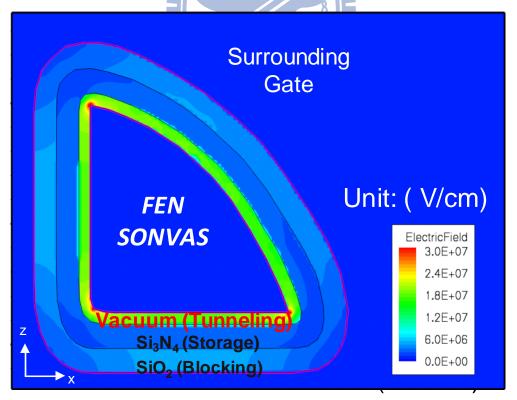

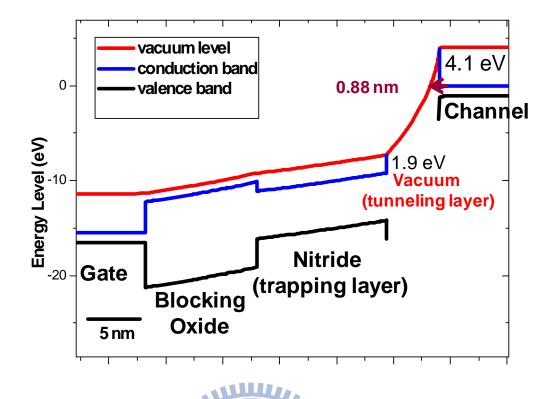

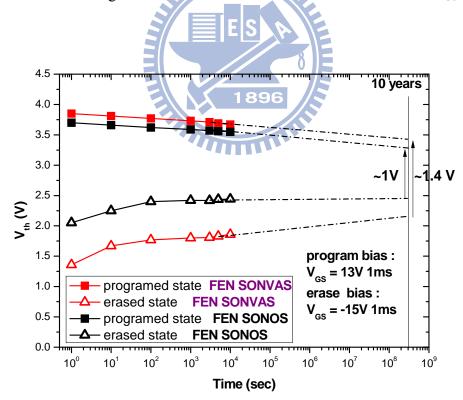

針對非揮發性記憶體開發,我們提出利用隙壁直接造成的三個尖端之電場增強式奈 米線,使有效的提高 SONOS (silicon-oxide-nitride-oxide-silicon)記憶體之寫入/抹除效 率。除此之外,我們也第一次提出將穿隧氧化層置換成真空之 SONVAS (silicon-oxide-nitride-vacuum-silicon)結構,由於穿隧層為為最低介電係數之真空,所以 亦可進一步將穿隧層之電場提高,因而可進一步提高記憶體之寫入/抹除效率;且穿隧 層為真空,可以降低傳統因多次寫入/抹除對穿隧氧化層造成的傷害,因而也可大幅提 升其耐久(endurance)可靠度。

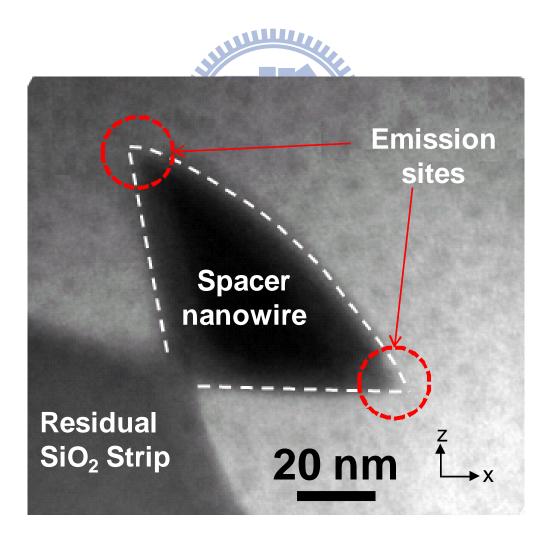

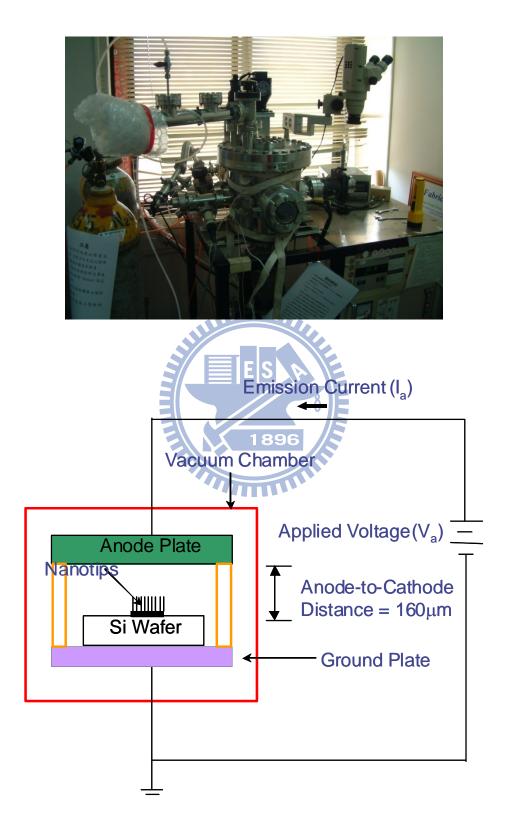

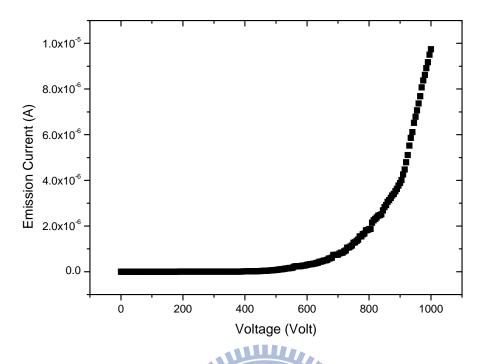

針對場發射顯示開發,我們也利用以低溫多晶矽為基礎之隙壁技術(spacer technique) 製作兩種場發射元件,使其有機會能直接整合於系統面板上而取代傳統液晶顯示器。第 一種為直接以隙壁矽奈米線之尖端當成場發射源,其導通電場為 2.06 V/μm。此外,我 也利用前敘之環繞式電極直接當成陽極,懸空之三個尖端隙壁奈米線當成陰極,直接由 E-Gun 沉積的二氧化矽封成真空,利用該法製作出場發元件,導通電壓僅 0.14 V,為目 前最低的導通電壓。

最後,該論文結論與針對未來系統面板研究可著重的工作方向亦討論之。

## Study on the Thin Film Transistors with Various Device Structures for System-on-Panel Applications

Student : Ta-Chuan Liao

Advisor : Dr. Huang-Chung Cheng

Department of Electronics Engineering & Institute of Electronics National Chiao Tung University

#### <u>ABSTRACT</u>

In this thesis, various structures and techniques are studied for the fabrication of high-performance low temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) through drain, gate, and channel engineering. In addition, for further versatile system-on-panel (SOP) applications, the novel nonvolatile memories and field emitters based on LTPS technology are developed as well.

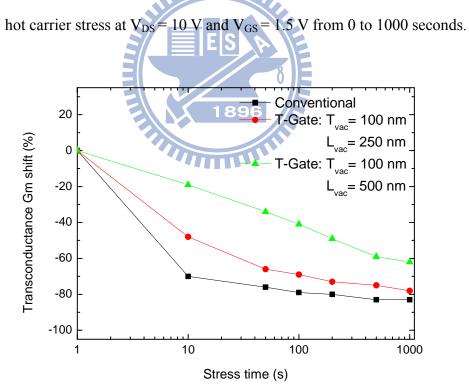

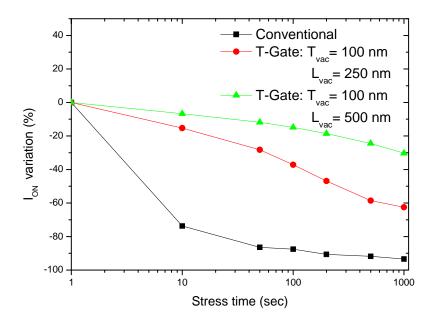

At first, for drain engineering, the T-shaped-gate (T-Gate) LTPS TFTs with symmetric vacuum gaps have been proposed and fabricated simply only with a selective-etching technique and an *in-situ* vacuum encapsulation. Due to the great reduction of electric field near the drain junction by the resulting offset region and vacuum gap, the fabricated T-Gate LTPS TFTs exhibit ultra low leakage current, high on/off current ratio, reduced kink current, and high reliability.

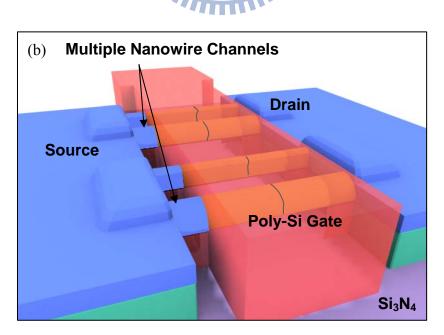

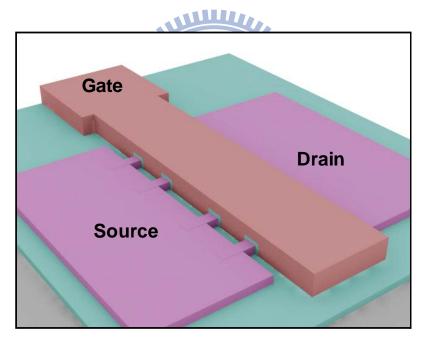

Secondly, for gate engineering, the novel gate-all-around (GAA) poly-Si TFTs with multiple nanowire channels (MNCs) have been, for the first time, fabricated using a simple process to demonstrate high performance electrical characteristics and high immunity to short channel effects (SCEs). The nanowire channel with high body thickness-to-width ratio, approximately equals to one, is realized only with a sidewall-spacer formation. Moreover, the unique suspending MNCs are also achieved to build the GAA structure. The resultant GAA-MNC TFTs show outstanding three-dimensional gate controllability and excellent electrical characteristics, which reveal a high on/off current ratio, a low threshold voltage, a steep subthreshold swing, a near-free drain-induced barrier lowering, as well as an excellent SCE suppression.

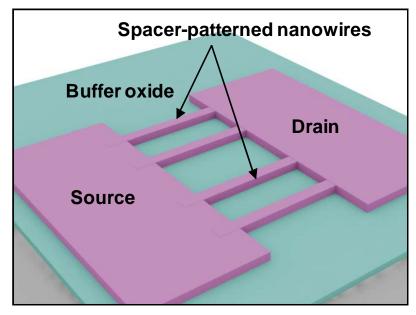

For channel engineering, two types of novel processes are subsequently demonstrated for fabricating high-crystallinity Si-nanowire LTPS TFTs. The one is to utilize the previously proposed sidewall-spacer nanowire structure to control the lateral grain growth from the thicker S/D pads to the center of thinner nanowire channel. Due to the necking effect in such nanowire structure, only-one grain boundary exists in the middle nanowire channel. LTPS TFTs with field-effect mobility of 273 cm<sup>2</sup>/V-s have been fabricated by using this method. The other is to utilize spacer lithography to directly transfer the nanowire pattern onto the large-grain sequential-lateral-solidification (SLS) poly-Si thin film. In term of probability, the nanowire pattern (8 nm) is much smaller than the SLS grain width (0.8  $\mu$ m), which makes the nanowire locate within a single grain, thus the resulting nanowire can be performed like a single-crystal simply. Due to the high-crystallinity formed in the nanowire channel, the nanowire TFT exhibits an excellent mobility of **596** cm<sup>2</sup>/V-s and steeper subthreshold slope of 101 mV/decade. As a result, it is very suitable for future system-on-panel (SOP) applications.

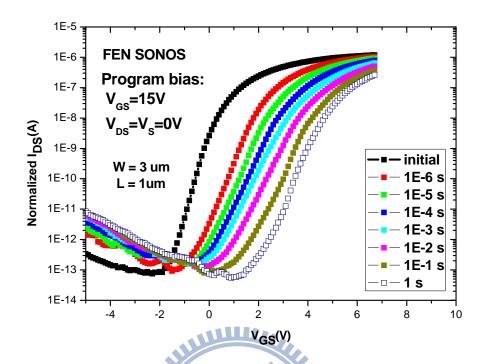

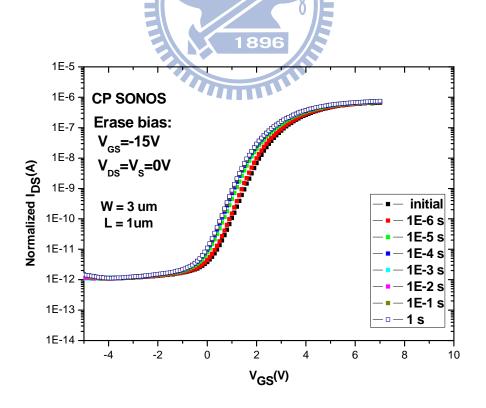

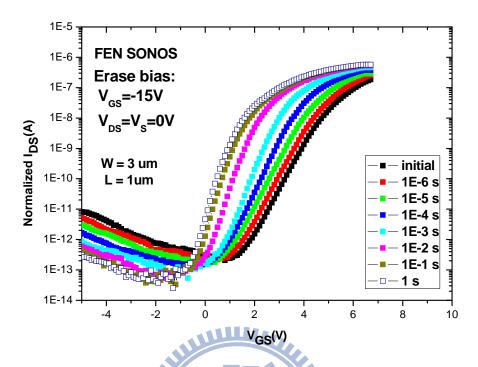

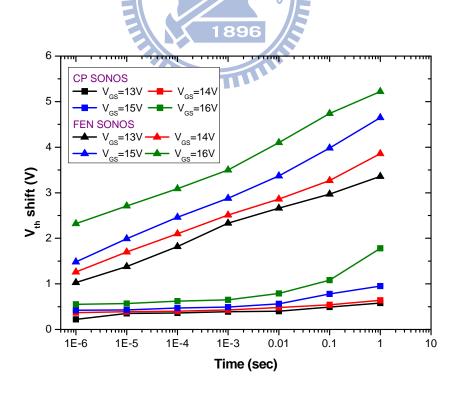

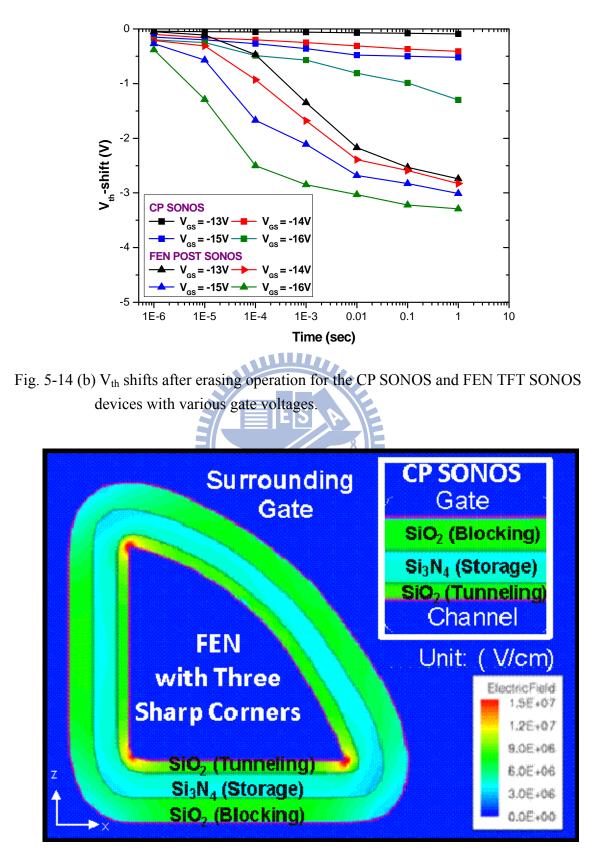

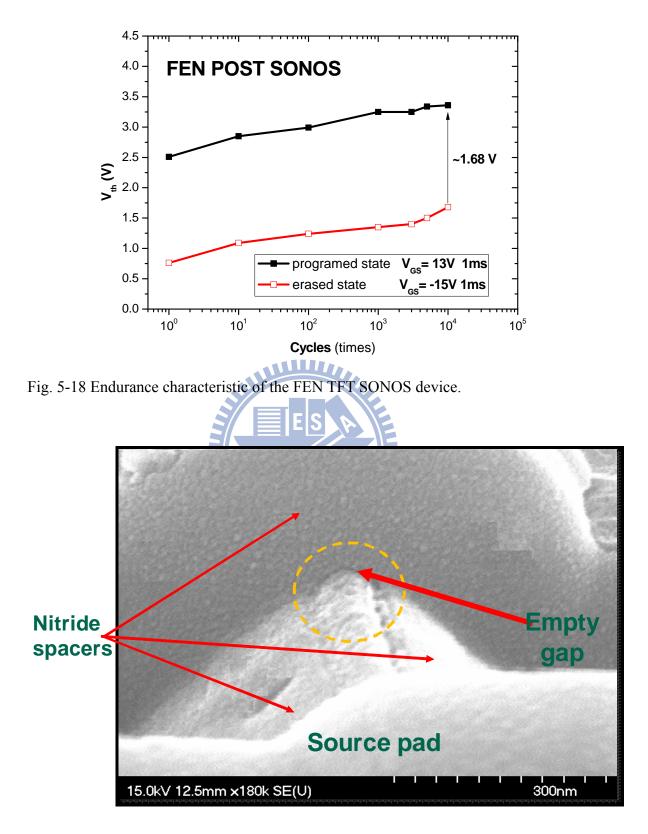

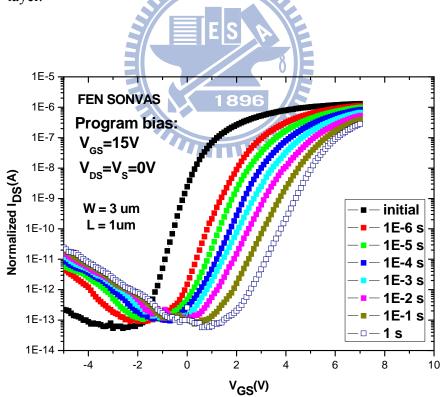

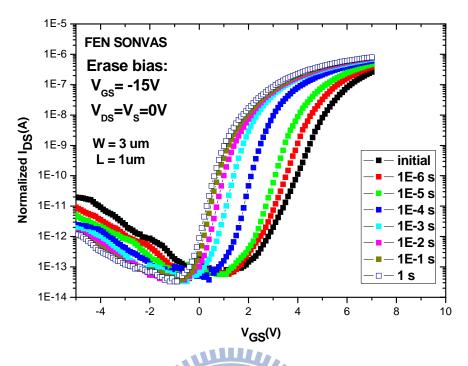

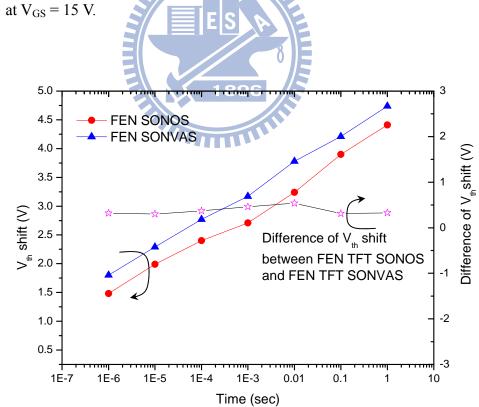

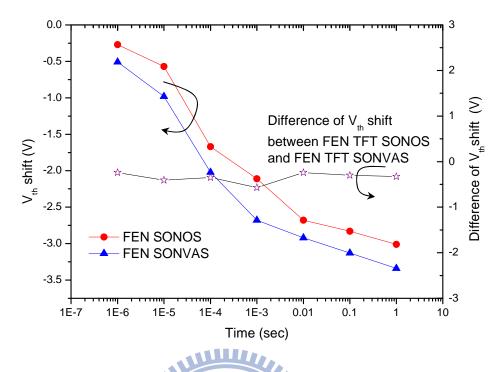

For nonvolatile memory development, a field-enhanced nanowire (FEN) LTPS-TFT silicon-oxide-nitride-oxide-silicon (SONOS) memory with a gate-all-around (GAA) structure has been proposed to improve the program and erase (P/E) performance. Each nanowire inherently has three sharp corners fabricated simply by sidewall spacer formation to obtain high local electric fields. The field-enhanced carriers tunneling via such a structure lead to faster P/E speed and wider memory window for the FEN SONOS as compared to the

conventional planar (CP) counterpart. The FEN LTPS TFT SONOS device exhibits a V<sub>th</sub> shift of 2.71 V and 2.11 V at V<sub>GS</sub> = +15/-15 V in 1 ms for FN programming and erasing (P/E) operations, respectively. Other than FEN structure, a vacuum counterpart is further as a substitute for tunneling oxide to perform the novel <u>silicon-oxide-nitride-va</u>cuum-<u>silicon</u> (SONVAS) structure, for the first time. Due to the further electric field enhancement from the vacuum introduction in tunneling layer, the FEN SONVAS exhibits larger V<sub>th</sub> shifts of 3.17V and 2.68V at V<sub>GS</sub> = +15/-15V in 1 ms for FN P/E operations, correspondingly. Besides, due to the empty property of vacuum, there are less dangling bonds and tunneling-oxide traps produced during P/E cycles, so that FEN SONVAS exhibits much improved endurance reliability as well.

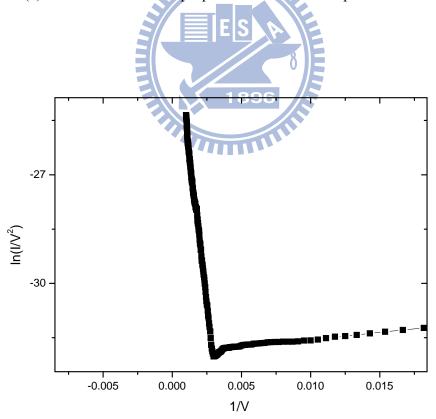

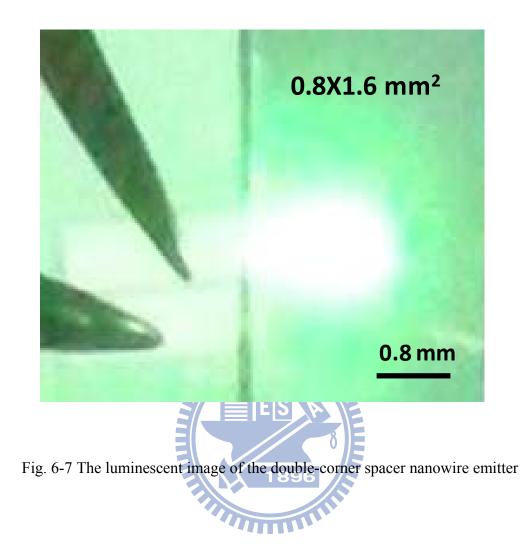

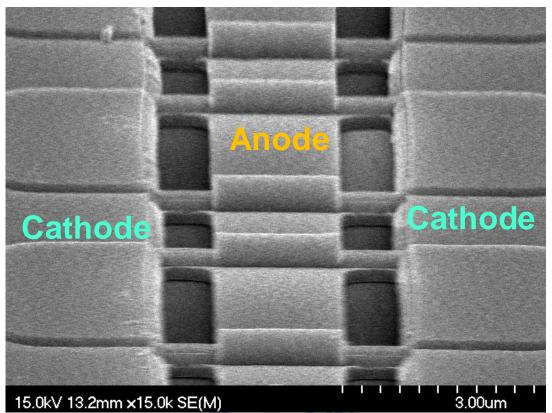

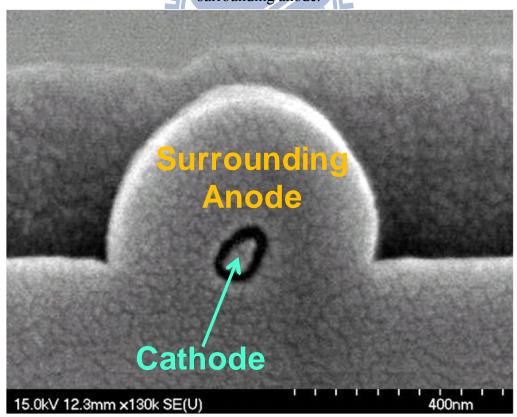

For field emitter development, spacer technique are applied on two types of LTPS-based field emitters for the possibilities of the replacement of LCD display elements in terms of system integration and image performance. For spacer nanowire field emitters, the F-N characteristics with turn-on field of 2.06 V/um have been performed. For the triple-corner **1896** nanowire emitter *in-situ* vacuum-encapsulated by the surrounding silicon dioxide, the F-N characteristics have been performed with a turn-on voltage of 0.14 V, which is the lowest one in the record to date.

Finally, conclusions as well as prospects for further research are also summarized.

#### 誌 謝

僅以此論文獻給我的父母親廖錦然先生與林玉葉女士,感謝你們多年來的養育之 恩,與無怨無悔的支持,我才得能無後顧之憂地完成學業;同時也謝謝我的哥哥廖志晟 先生與弟弟廖守有先生,感謝你們在我求學期間對整個家的付出。

特別感謝我的論文指導教授鄭晃忠老師,恩師在為人處事及論文研究上的熱心指導,都讓我獲益良多,我才得能順利取得博士學位,在此表達由衷感謝。

感謝實驗室的學長、學弟妹們,有了你們在生活上及實驗上相互的扶持與砥礪,漫 長的研究生涯才能顯得更多采多姿。特別感謝與我一起打拼的學弟們, 吳俊諭學弟、林 偉凱學弟、涂仕煒學弟、劉政欽學弟、陳聖凱學弟、徐邦祐學弟、林家名學弟、王俊凱 學弟、賴立軒學弟、黃浚豪學弟以及劉晏廷學弟,有了你們的相互扶持與合作此論文才 能順利完成。另外, 更感謝實驗室其他夥伴在生活與實驗上的幫忙、討論與打氣,才得 以讓實驗更順利完成,其中包含了張國瑞學長、游明華學長、阮全平學長、蔡春乾學長、 朱芳村學長、林高照學長、賴瑞霖學長、陳柏廷學長、李逸哲學弟、楊柏宇學弟、胡采 綸助理、陳旭信學弟、劉全豐學弟、張加聰學弟、王昭龍學弟、李宏顯學弟、黃昱智學 弟、蔡萬霖學弟、陳俠威學弟、韋凱方學弟、李建穎學弟、許育瑛學妹、胡明哲學弟、 魏英彰學弟、鄧茜云學妹、....等,在此一併致謝。

此外,我更要感謝逢甲大學簡鳳佐教授、康宗貴教授、以及元智大學沈幼敏教授, 謝謝老師一直以來不間斷的指導與關心,學生銘感於心。

我也得感謝其他實驗室的學長、同學學弟們及我的好朋友們,如溫華強博士、黃柏 鈞同學、簡鐸欣同學、蘇清源同學、朱永明同學、蔡宗閔學弟、廖健男學弟、詹明宏學 弟及方金木學弟於實驗上的大力協助與相互勉勵。感謝中科院黃重鈞博士、戴涪博士; 工研院楊豐瑜博士;中美晶徐文慶協理、陳宛如小姐;義隆電子顏國隆副總、林錫琨經 理;華映莫啟能處長、陳司芬經理、陳盈惠小姐,謝謝你們於計畫與實驗上的鼎力協助。

最後感謝所有曾經幫助過我、支持過我及關心過我的朋友及長輩們。

vi

# Contents

| Abstract (in Chinese) | i   |

|-----------------------|-----|

| Abstract (in English) | iii |

| Acknowledgements      | vi  |

| Contents              | vii |

| Table Lists           | xiv |

| Figure Captions       | xvi |

| Chapter 1 | Introduction                                                               |

|-----------|----------------------------------------------------------------------------|

| 1         | ESP                                                                        |

| 1.1       | Overview of Low Temperature Polycrystalline Silicon Thin Film Transistors1 |

| 1.2       | Key Processes in the Fabrication of LTPS TFTs                              |

| 1.3       | Channel Engineering                                                        |

| 1.4       | Drain Engineering                                                          |

| 1.5       | Gate Engineering9                                                          |

| 1.6       | System on Panel (SOP) Issues10                                             |

| 1.7       | Motivation11                                                               |

| 1.8       | Thesis Organization                                                        |

| 2.1 | Introduction | 1 | 7 |

|-----|--------------|---|---|

|-----|--------------|---|---|

| 2.2 | Electr | ical Simulations for T-Gate LTPS TFTs with Vacuum Gaps          | 18 |

|-----|--------|-----------------------------------------------------------------|----|

| 2.3 | Exper  | iments                                                          | 20 |

|     | 2.3.1  | Fabrication Sequence of T-Gate LTPS TFTs with Vacuum Gaps       | 20 |

| 2.4 | Result | s and Discussion                                                | 21 |

|     | 2.4.1  | Method of Electrical Parameter Extraction                       | 21 |

|     | 2.4.2  | Electrical Characteristics of T-Gate LTPS TFTs with Vacuum Gaps | 23 |

|     | 2.4.3  | Effect of Gate Oxide Thickness                                  | 24 |

|     | 2.4.4  | Oxide Breakdown Characteristics of T-Gate LTPS TFTs             | 25 |

|     | 2.4.5  | Drain Avalanche Hot Carrier Stress on T-Gate LTPS TFTs          | 25 |

| 2.: | 5 Sun  | ımary                                                           | 26 |

| Chapter 3 No | ovel Gate-All-Around Polycrystalline Silicon Thin Film                    |

|--------------|---------------------------------------------------------------------------|

| Tra          | nsistors with Multiple Nanowire Channels                                  |

|              | 1896                                                                      |

| 3.1 Introdu  | uction                                                                    |

| 3.2 Experi   | ments                                                                     |

| 3.2.1        | Fabrication Sequence of Gate-All-Around Polycrystalline Silicon Thin      |

| I            | Film Transistors with Multiple Nanowire Channels                          |

| 3.2.2        | Material Analyses for Gate-All-Around Poly-Si TFTs with Multiple          |

| 1            | Nanowire Channels                                                         |

| 3.3 Results  | s and Discussion                                                          |

| 3.3.1 I      | Electrical Characterization of Gate-All-Around Poly-Si TFTs with Multiple |

| 1            | Nanowire Channels                                                         |

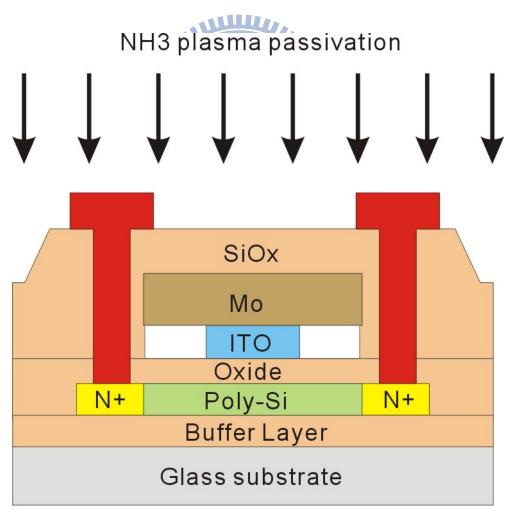

| 3.3.2        | NH <sub>3</sub> Plasma Passivation54                                      |

| 3.4 Dimen    | sional Scalability55                                                      |

| 341 8        | Short Channel Effects 56                                                  |

|     | 3.4.2 Narrow Width Effects |  |

|-----|----------------------------|--|

| 3.5 | Summary                    |  |

#

| 4.1 | Introc | luction                                                                     |

|-----|--------|-----------------------------------------------------------------------------|

| 4.2 | Expe   | riments                                                                     |

|     | 4.2.1  | Fabrication Sequence of Excimer-Laser-Crystallized Nanowire Thin Film       |

|     |        | Transistors                                                                 |

|     | 4.2.2  | Fabrication Sequence of Gate-All-Around Thin Film Transistors with          |

|     |        | Single-Crystalline-Like Nanowire Channels                                   |

| 4.3 | Resul  | ts and Discussion                                                           |

|     | 4.3.1  | Material Analyses of Excimer-Laser-Crystallized Nanowire                    |

|     | 4.3.2  | Electrical Characteristics of Excimer-Laser-Crystallized Nanowire Thin      |

|     |        | Film Transistors                                                            |

|     | 4.3.3  | Material Analyses of Single-Crystalline-Like Silicon Nanowire with          |

|     |        | Spacer Patterned Method                                                     |

|     | 4.3.4  | Electrical Characteristics of Single-Crystalline-Like Silicon Nanowire Thin |

|     |        | Film Transistors with Spacer Patterned Method                               |

| 4.4 | Summ   | nary                                                                        |

|     |        |                                                                             |

#

| 5.2    | Expe  | eriments                                                       |             |

|--------|-------|----------------------------------------------------------------|-------------|

|        | 5.2.1 | Fabrication Sequence of Field-Enhanced-Nanowire Poly-Si T      | FT SONOS    |

|        |       | Memory with a Gate-All-Around Structure                        | 109         |

|        | 5.2.2 | Fabrication Sequence of Field-Enhanced-Nanowire Poly-Si TF     | T SONVAS    |

|        |       | Memory with a Gate-All-Around Structure                        | 110         |

| 5.3    | Resu  | Ilts and Discussion                                            | 111         |

|        | 5.3.1 | Electrical Characteristics of Field-Enhanced-Nanowire P        | oly-Si TFT  |

|        |       | SONOS Memory with a Gate-All-Around Structure                  |             |

|        | 5.3.2 | Electrical Characteristics of Field-Enhanced-Nanowire P        | oly-Si TFT  |

|        |       | SONVAS Memory with a Gate-All-Around Structure                 |             |

| 5.4    | Sum   | mary                                                           | 115         |

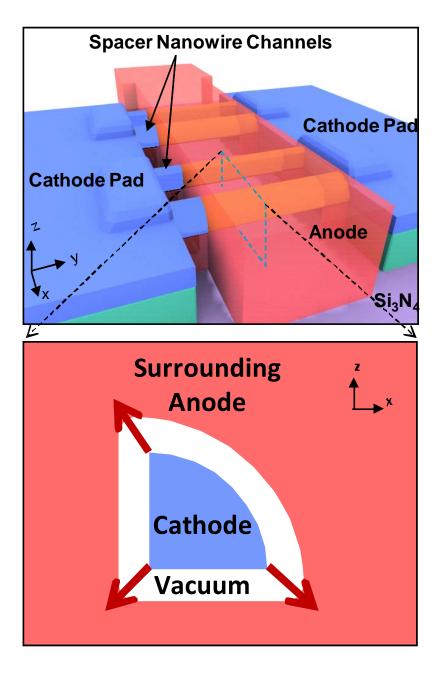

| Chapte | r6N   | ovel Polycrystalline Silicon Nanowire Field Emitters           | 135         |

| 6.1    | Intro | oduction                                                       | 135         |

| 6.2    | Expe  | eriments.                                                      | 135         |

|        | 6.2.1 | Fabrication Sequence of Spacer Nanowire Field Emitters         | 135         |

|        | 6.2.2 | Fabrication Sequence of Triple-Corner Nanowire Emitter in-     | situ Vacuum |

|        |       | Encapsulated with Surrounding Anode Electrode                  | 137         |

| 6.3    | Resu  | Ilts and Discussion                                            | 138         |

|        | 6.3.1 | Emission Characteristics of Spacer Nanowire Field Emitters     |             |

|        | 6.3.2 | Emission Characteristics of Triple-Corner Nanowire Emitter in- | situ Vacuum |

|        |       | Encapsulated with Surrounding Anode Electrode                  | 140         |

| 6.4    | Sum   | mary                                                           | 141         |

| Chapter 7   | Summary and Conclusions |     |

|-------------|-------------------------|-----|

| Chapter 8   | Future Prospects        | 155 |

| References  | ·····                   | 155 |

| Publication | ı List                  | 177 |

| Vita        |                         |     |

# **Table Lists**

#### Chapter 2

- Table 2-1 Measured electrical characteristics of conventional and T-Gate TFTs. On current is defined as the drain current measured at  $V_{GS}$ = 15 V,  $V_{DS}$ = 3 V. Leakage-current is defined as the drain current measured at  $V_{GS}$ = -15 V,  $V_{DS}$ = 3 V.......28

#### Chapter 3

#### Chapter 4

| TFTs | 91 |

|------|----|

|------|----|

Table 4-3The electrical characteristics of GAA-SLS MNC and CP-SLS MNC TFTs.....91

### Chapter 5

| Table 5-1 | The $V_{th}$ shifts after programming and erasing operation at a gate voltage 15 V |

|-----------|------------------------------------------------------------------------------------|

|           | and -15 V, respectively, for the CP, FEN TFT SONOS and FEN TFT SONVAS              |

|           | devices                                                                            |

| Table 5-2 | The subthreshold swing of FEN TFT SONOS and FEN TFT SONVAS devices                 |

after P/E cycles......117

# **Figure Captions**

#### Chapter 1

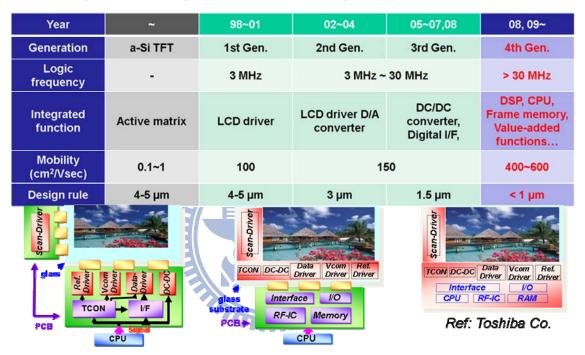

| Fig. 1-1. | Development of system on a panel (SOP) | .15 |

|-----------|----------------------------------------|-----|

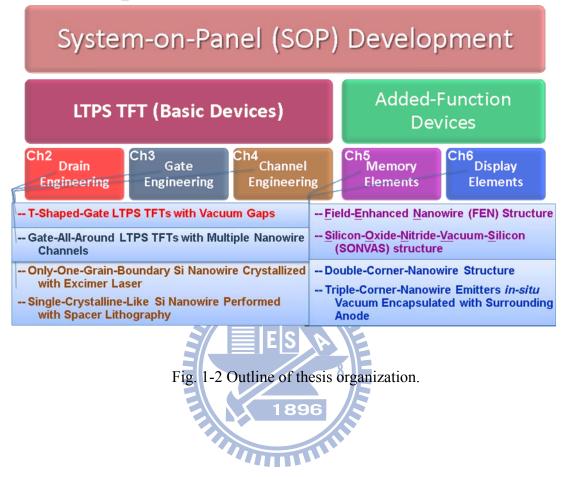

| Fig. 1-2. | Outline of thesis organization         | 16  |

#### **Chapter 2**

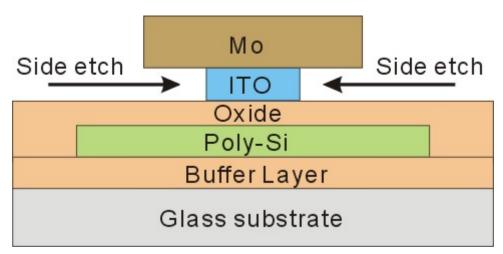

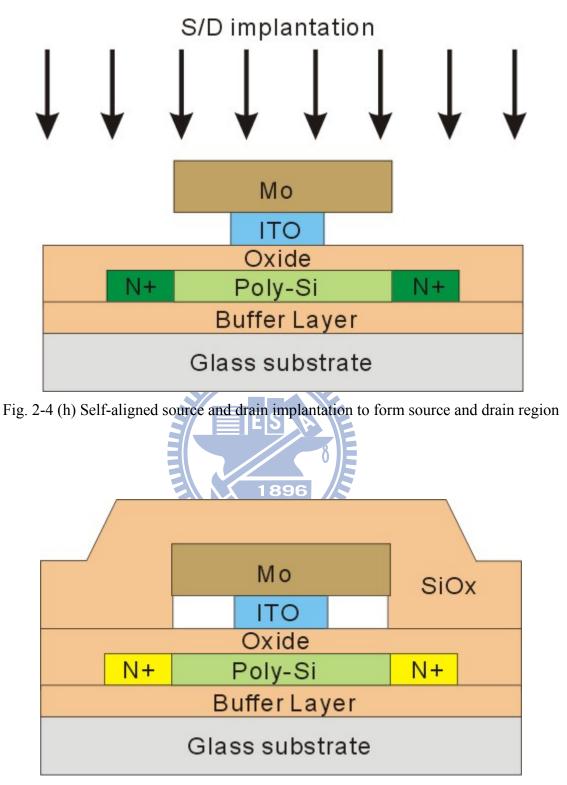

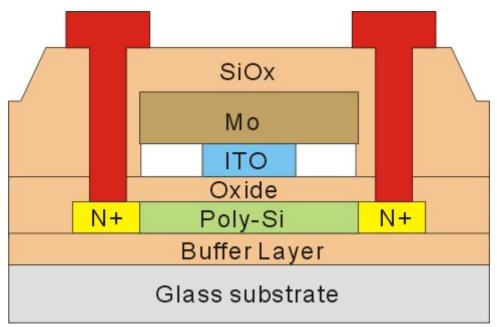

- Fig. 2-4. (a) Buffer layer deposition on the glass substrate. (b) Amorphous Silicon layer deposition by PECVD system. (c) Crystallization of the amorphous-Si film using excimer laser irradiation. (d) Definition of active region. (e) Gate oxide deposition

|            | by PECVD system at 300°C. (f) The stacked ITO/Mo layer deposition followed by                         |

|------------|-------------------------------------------------------------------------------------------------------|

|            | patterning as the gate electrode. (g) Selective side etching of the ITO layer to form                 |

|            | the T-shape gate electrode structure. (h) Self-aligned source and drain implantation                  |

|            | to form source and drain region. (i) Silane-base $SiO_x$ passivation layer deposition                 |

|            | by PECVD system resulting in the in-situ vacuum gaps and then dopant activation                       |

|            | by RTA system. (j) Contact hole opening and metallization. (k) NH3 plasma                             |

|            | passivation. (1) The conventional structure                                                           |

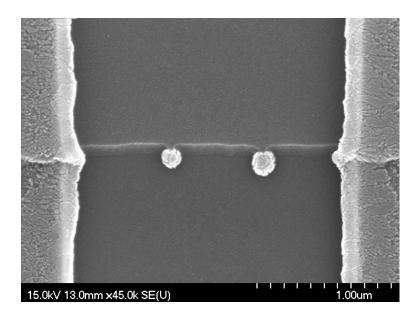

| Fig. 2-5.  | The SEM image of the fabricated T-Gate structure. ( $T_{vac} = 100$ nm, $L_{vac} = 500$               |

|            | nm)                                                                                                   |

| Fig. 2-6.  | The SEM image of the fabricated conventional-gate structure. ( $T_{vac} = 0 \text{ nm}$ , $L_{vac} =$ |

|            | 0 nm)                                                                                                 |

| Fig. 2-7.  | Transfer Characteristics of T-Gate LTPS TFTs with different $T_{vac}$ and fixed $L_{vac}$ , in        |

|            | which channel length is 5 $\mu$ m, channel width is 10 $\mu$ m, and the thickness of gate             |

|            | oxide is 40 nm                                                                                        |

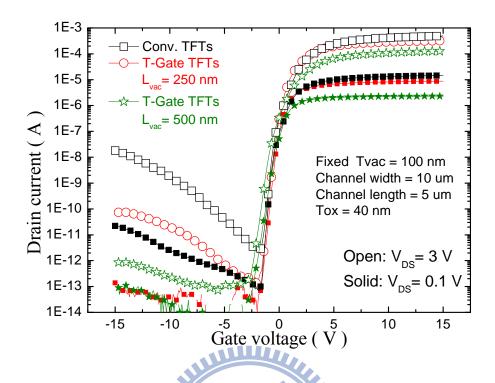

| Fig. 2-8.  | Transfer Characteristics of T-Gate LTPS TFTs with different $L_{vac}$ and fixed $T_{vac}$ , in        |

|            | which channel length is 5 $\mu$ m, channel width is 10 $\mu$ m, and the thickness of gate             |

|            | oxide is 40 nm                                                                                        |

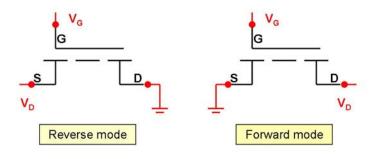

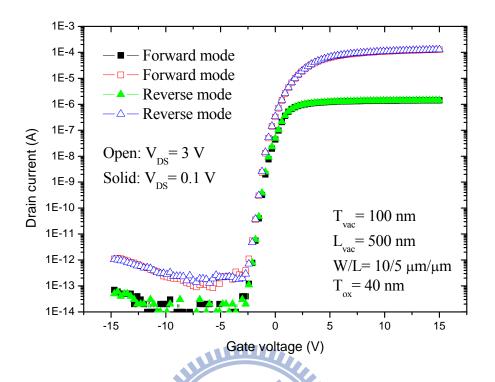

| Fig. 2-9   | The schematic illustration of the forward mode and reverse mode measurement39                         |

| Fig. 2-10. | Symmetry transfer characteristics of T-Gate TFTs ( $T_{vac}$ = 100 nm and $L_{vac}$ = 500             |

|            | nm)40                                                                                                 |

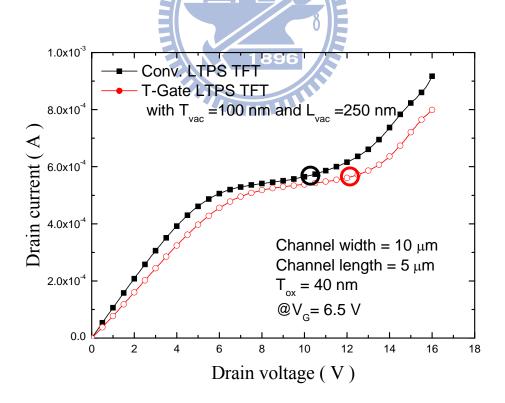

| Fig. 2-11. | Output characteristics of conventional and T-Gate LTPS TFTs, in which channel                         |

|            | length is 5 $\mu m,$ channel width is 10 $\mu m,$ and the thickness of gate oxide is 40               |

|            | nm40                                                                                                  |

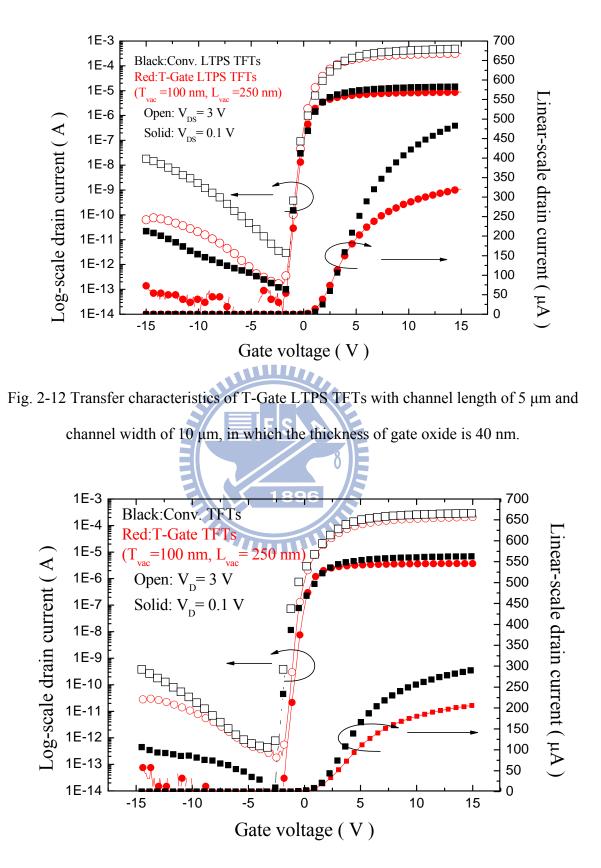

| Fig. 2-12. | Transfer characteristics of T-Gate LTPS TFTs with channel length of 5 $\mu m$ and                     |

|            | channel width of 10 $\mu$ m, in which the thickness of gate oxide is 40 nm41                          |

|            |                                                                                                       |

Fig. 2-13. Transfer characteristics of T-Gate LTPS TFTs with channel length of 5  $\mu m$  and

channel width of 10 µm, in which the thickness of gate oxide is 80 nm......41

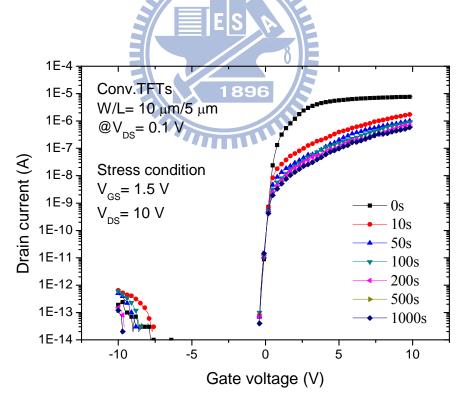

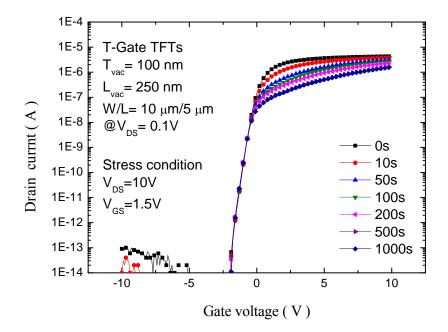

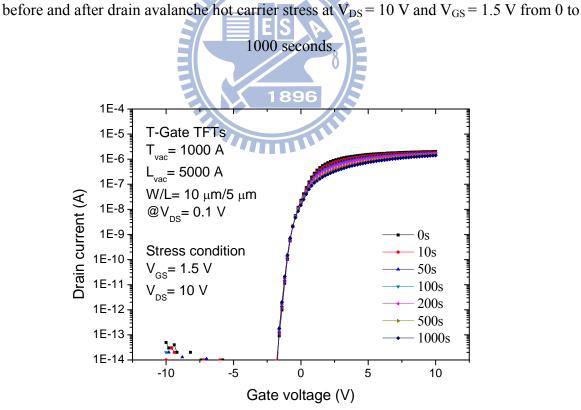

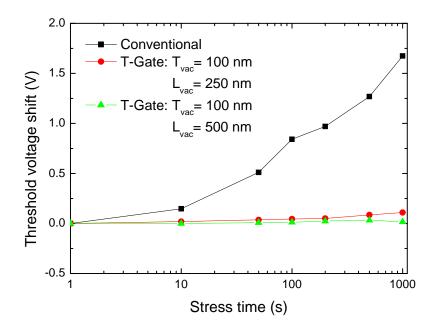

variation of T-Gate and conventional TFTs after drain avalanche hot carrier stress

#### **Chapter 3**

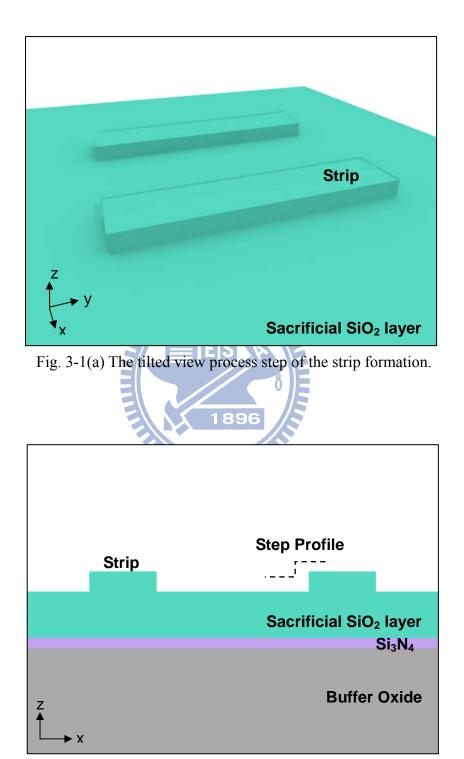

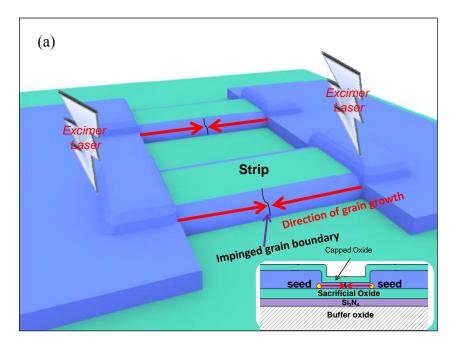

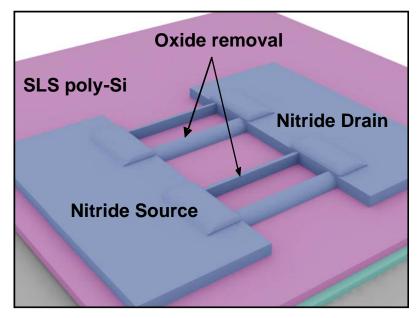

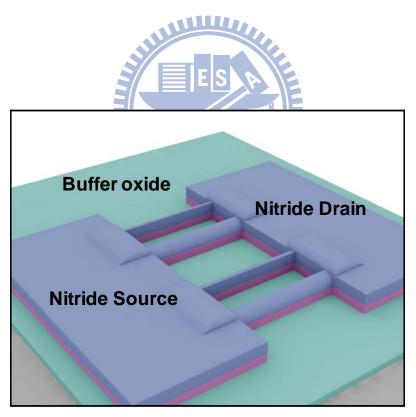

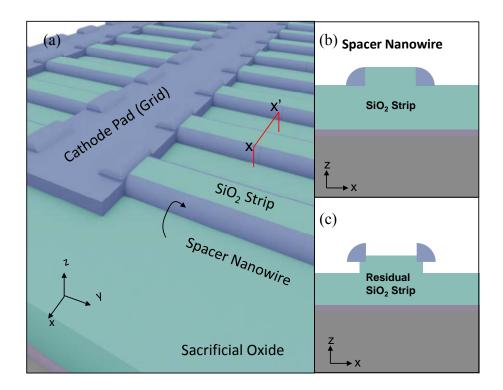

Fig. 3-1. (a) The tilted view process step of the strip formation. (b) The cross-section view step of the strip formation. (c) The tilted view step of the nanowire-channel

| formation. (d) The cross-section view step of the nanowire-channel formation. (e)  |

|------------------------------------------------------------------------------------|

| The tilted view step of the suspending nanowire-channel formation. (f) The         |

| pross-section view step of the suspending nanowire-channel formation. (g) The      |

| ilted view step of the gate formation. (h) The cross-section view step of the gate |

| ormation                                                                           |

- Fig. 3-9. Output characteristics of gate-all-around poly-Si TFTs with multiple nanowire

|            | channels and conventional TFTs71                                                             |

|------------|----------------------------------------------------------------------------------------------|

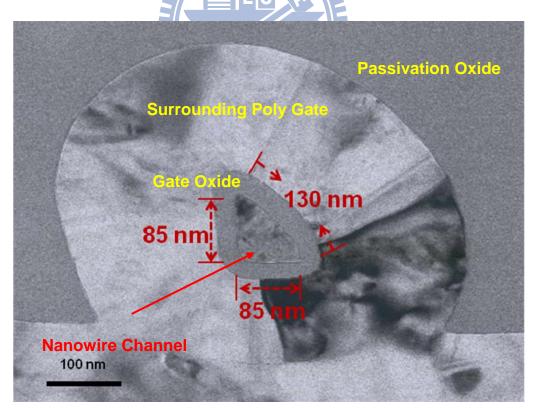

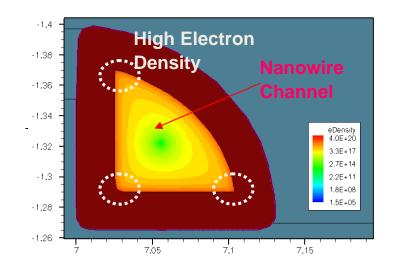

| Fig. 3-10. | The electron density simulation of gate-all-around poly-Si TFTs with multiple                |

|            | nanowire channels by ISE-DESSIS72                                                            |

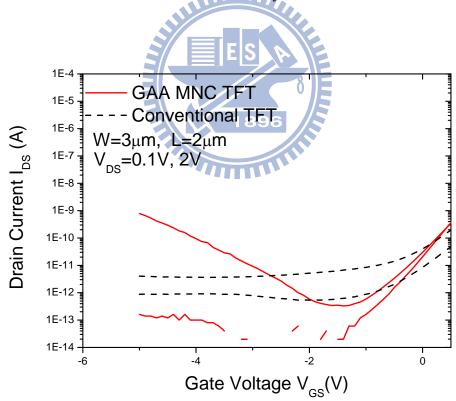

| Fig. 3-11. | Leakage current of gate-all-around poly-Si TFTs with multiple nanowire channels              |

|            | and conventional TFTs72                                                                      |

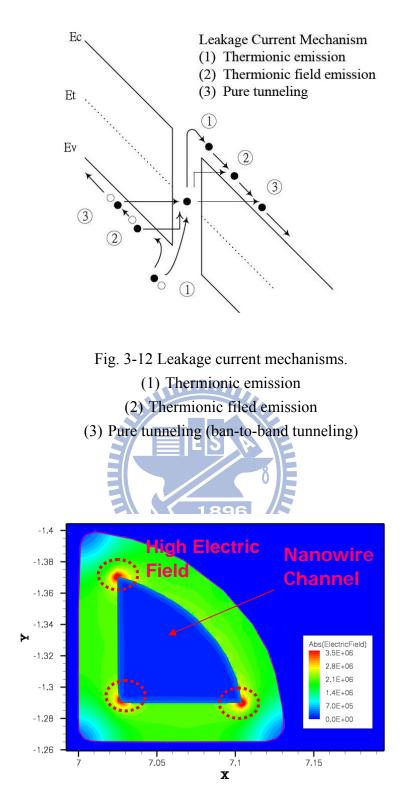

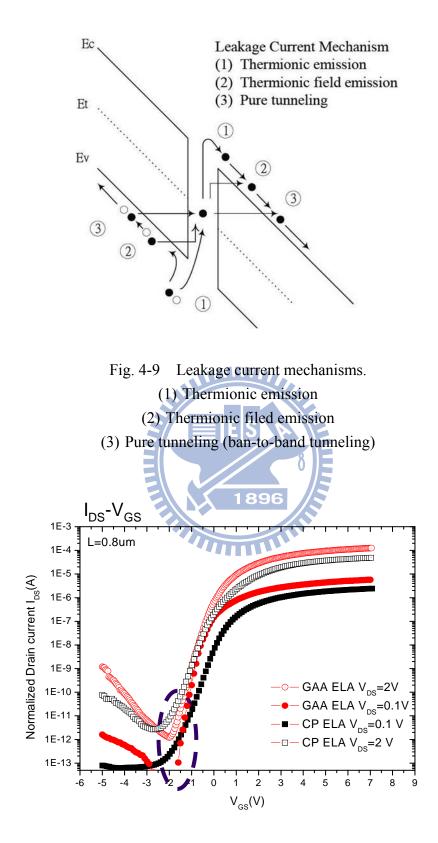

| Fig. 3-12. | Leakage current mechanisms.(1)Thermionic emission (2)Thermionic filed                        |

|            | emission (3) Pure tunneling (ban-to-band tunneling)73                                        |

| Fig. 3-13. | The electric field simulation of gate-all-around poly-Si TFTs with multiple                  |

|            | nanowire channels and conventional TFTs by ISE-DESSIS73                                      |

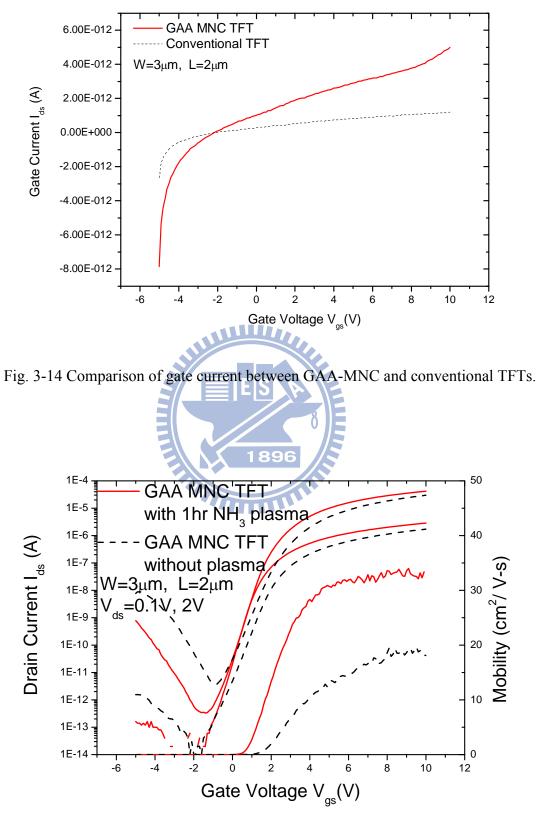

| Fig. 3-14. | Gate current of gate-all-around poly-Si TFTs with multiple nanowire channels                 |

|            | and conventional TFTs                                                                        |

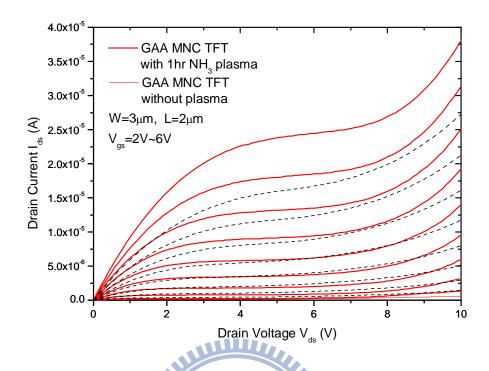

| Fig. 3-15. | Transfer characteristics of gate-all-around poly-Si TFTs with multiple nanowire              |

|            | channels before and after 1-hour NH <sub>3</sub> plasma passivation74                        |

| Fig. 3-16. | Output characteristics of gate-all-around poly-Si TFTs with multiple nanowire                |

|            | channels before and after 1-hour NH <sub>3</sub> plasma passivation75                        |

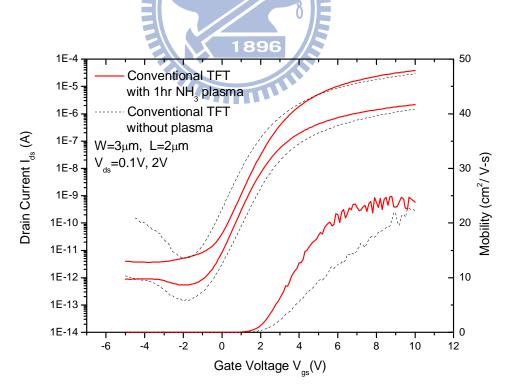

| Fig. 3-17. | Transfer characteristics of conventional TFTs before and after 1-hour NH <sub>3</sub> plasma |

|            | passivation75                                                                                |

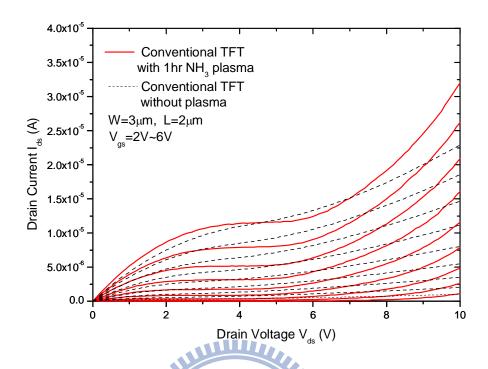

| Fig. 3-18. | Output characteristics of conventional TFTs before and after 1-hour NH <sub>3</sub> plasma   |

|            | passivation                                                                                  |

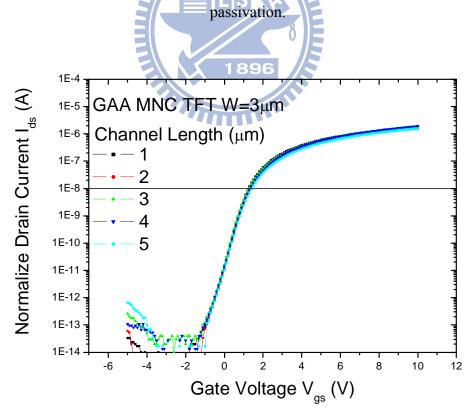

| Fig. 3-19. | Normalized transfer characteristics of gate-all-around poly-Si TFTs with multiple            |

|            | nanowire channels                                                                            |

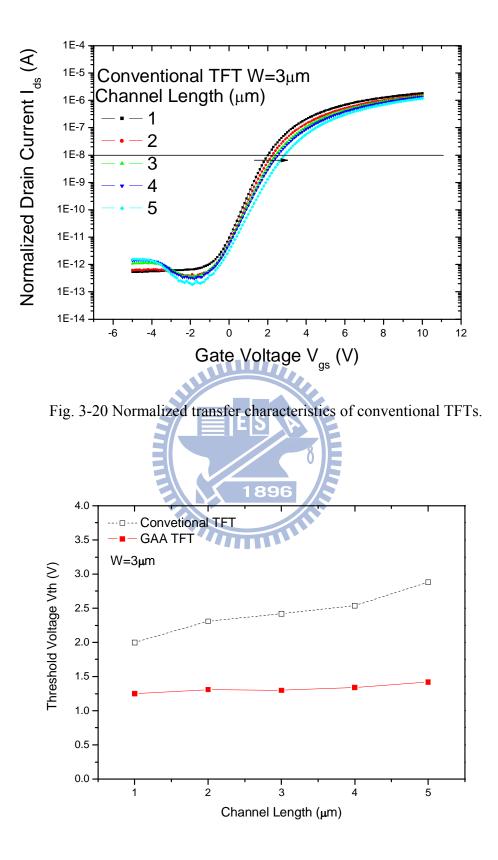

| Fig. 3-20. | Normalized transfer characteristics of conventional TFTs77                                   |

| Fig. 3-21. | The threshold voltage of poly-Si TFTs with multiple nanowire channels and                    |

|            | conventional TFTs with various channel length77                                              |

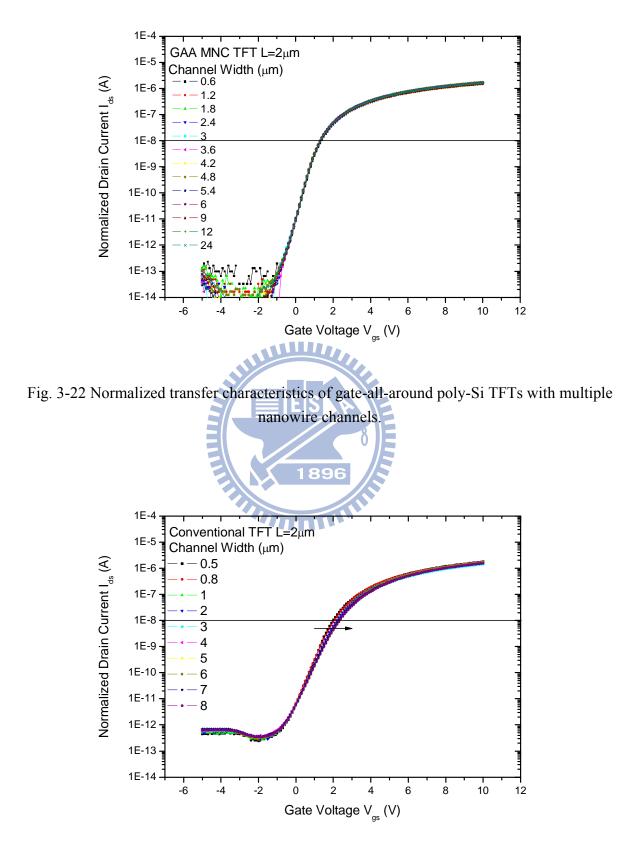

| Fig. 3-22. | Normalized transfer characteristics of gate-all-around poly-Si TFTs with multiple            |

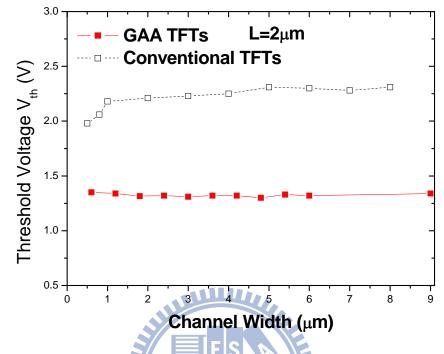

|            | nanowire channels                                                                            |

| Fig. 3-23. | Normalized transfer | characteristics of | conventional | TFTs | .78 |

|------------|---------------------|--------------------|--------------|------|-----|

|------------|---------------------|--------------------|--------------|------|-----|

# Chapter 4

| (a) The schematic diagram for the nanowire-channel formation and the grain                     |

|------------------------------------------------------------------------------------------------|

| growth during excimer laser irradiation. (b) The schematic diagram of gate                     |

| formation                                                                                      |

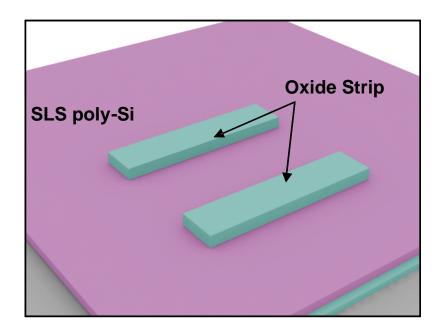

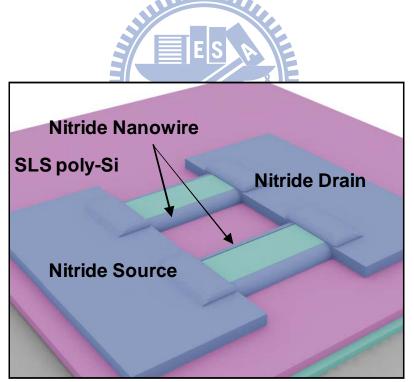

| (a) The oxide strip formation. (b) The nitride spacer nanowire formation. (c) Oxide            |

| removal by DHF. (d) A dry etching was performed to pattern the nanowire from                   |

| the nano-scale nitride hard mask. (e) Nitride removal by $H_3PO_4$ acid. (f) the gate          |

| formation                                                                                      |

| Si nano dots formation after excimer laser irradiation with 200 mJ/cm <sup>2</sup> and without |

| capping oxide                                                                                  |

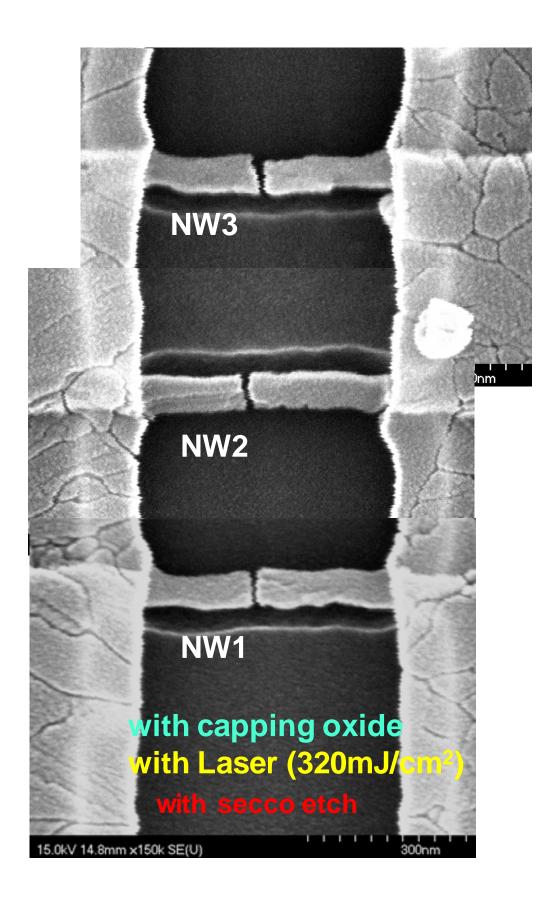

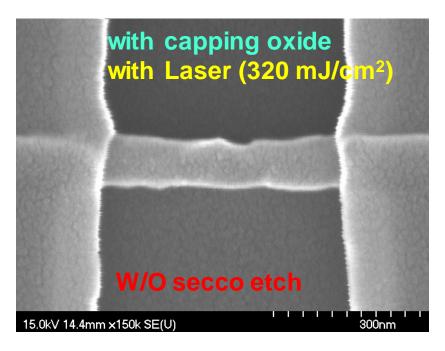

| (a) SEM graphs of laser-crystallized poly-Si nanowire after the Secco-etch                     |

| treatment. (b) SEM graphs of excimer laser-crystallized poly-Si nanowire before                |

| the Secco-etch treatment                                                                       |

| (a) SEM observation of the fabricated excimer-laser-crystallized nanowire GAA                  |

| TFT. (b) X-TEM observation of excimer-laser-crystallized nanowire GAA                          |

| TFT                                                                                            |

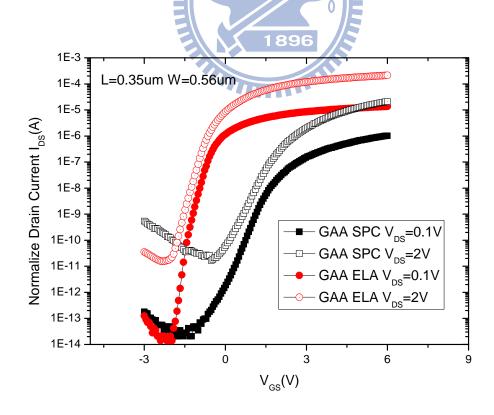

| The comparison of normalized transfer characteristics between GAA-ELA MNC                      |

| TFTs and GAA-SPC MNC TFTs99                                                                    |

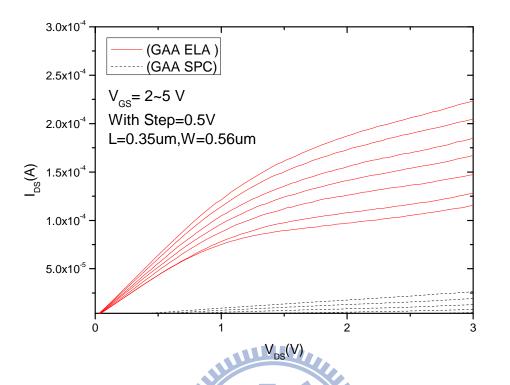

| The output characteristics of GAA-ELA MNC TFTs as compared to CP-ELA                           |

| TFTs100                                                                                        |

|                                                                                                |

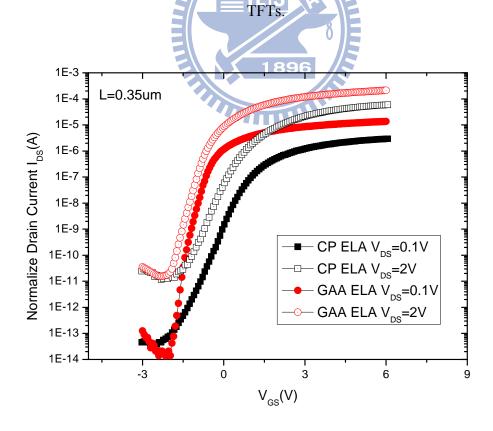

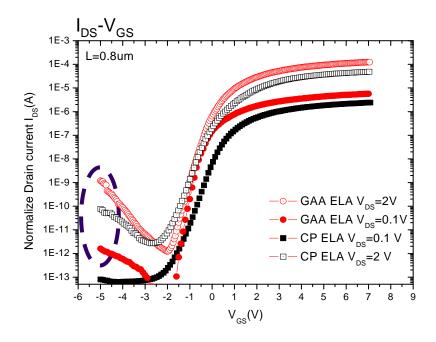

| Fig. 4-8.  | The comparison of normalized transfer characteristics between GAA-ELA MNC                |

|------------|------------------------------------------------------------------------------------------|

|            | TFTs and CP-ELA TFTs                                                                     |

| Fig. 4-9.  | Leakage current mechanisms. (1) Thermionic emission, (2) Thermionic filed                |

|            | emission, (3) Pure tunneling (ban-to-band tunneling)101                                  |

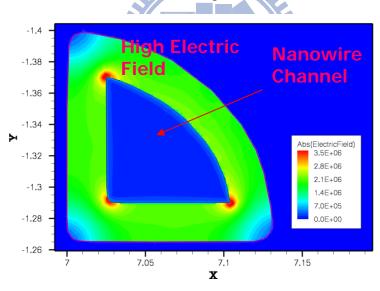

| Fig. 4-10. | The low leakage current at the low gate electric field region of GAA-ELA MNC             |

|            | TFTs as compared to CP TFTs101                                                           |

| Fig. 4-11. | The high leakage current at the high gate electric field region of GAA-ELA MNC           |

|            | TFTs as compared to CP TFTs102                                                           |

| Fig. 4-12. | The electric field simulation of GAA-ELA with multiple nanowire channels TFTs            |

|            | by ISE-DESSIS102                                                                         |

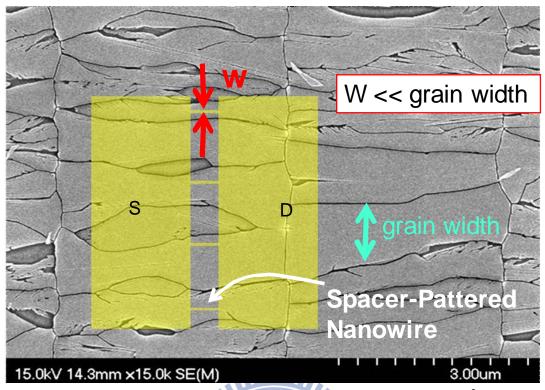

| Fig. 4-13. | The uniformly-distributed poly-Si grain with size of 3 $\times$ 0.8 $\mu m^2$ in average |

|            | prepared by SLS crystallization                                                          |

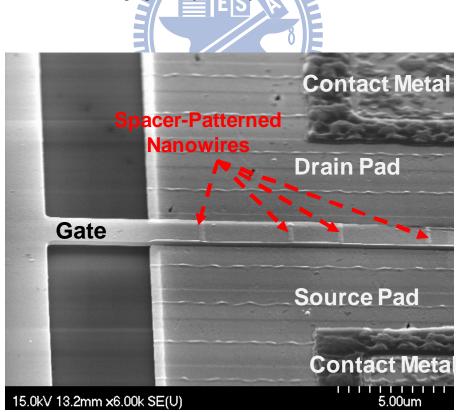

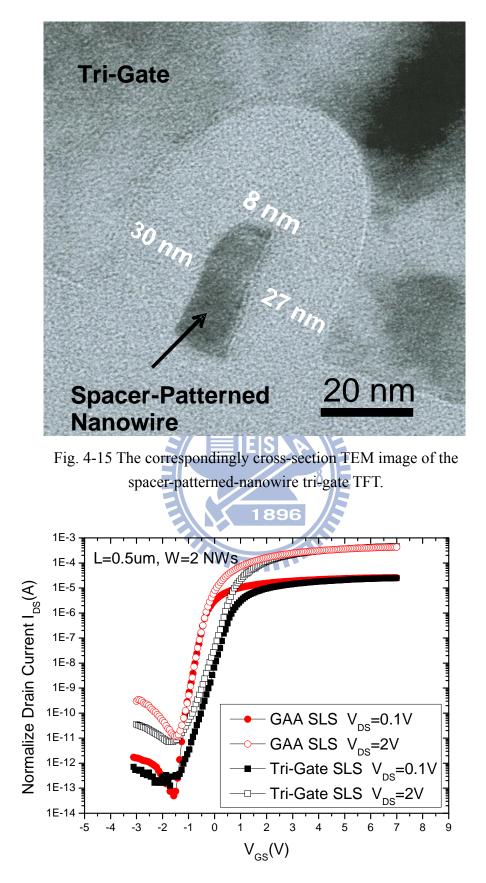

| Fig. 4-14. | SEM observation of the fabricated spacer-patterned-nanowire tri-gate TFT103              |

| Fig. 4-15. | The correspondingly cross-section TEM image of the spacer-patterned-nanowire             |

|            | tri-gate TFT                                                                             |

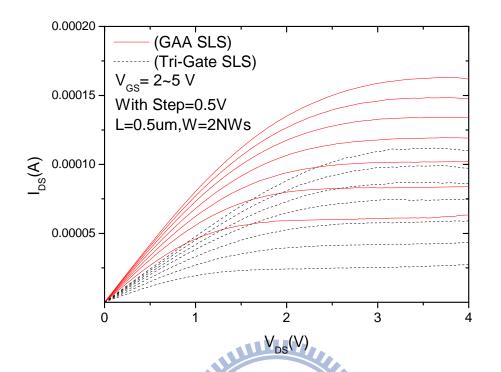

| Fig. 4-16. | The normalized transfer characteristics of GAA-SLS MNCs with TRI-Gate-SLS                |

|            | MNCs TFTs104                                                                             |

| Fig. 4-17  | . The output characteristics of GAA-SLS MNCs with TRI-Gate-SLS MNCs                      |

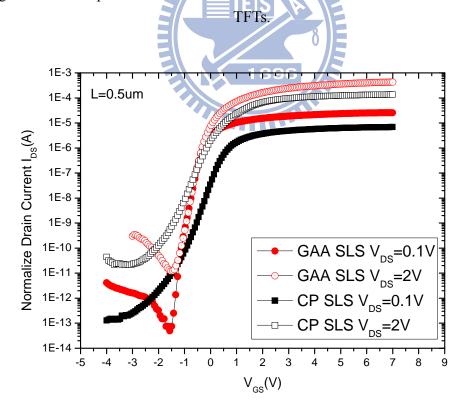

|            | TFTs105                                                                                  |

| Fig. 4-18  | . The normalized transfer characteristics of GAA-SLS MNCs with CP-SLS                    |

|            | TFTs105                                                                                  |

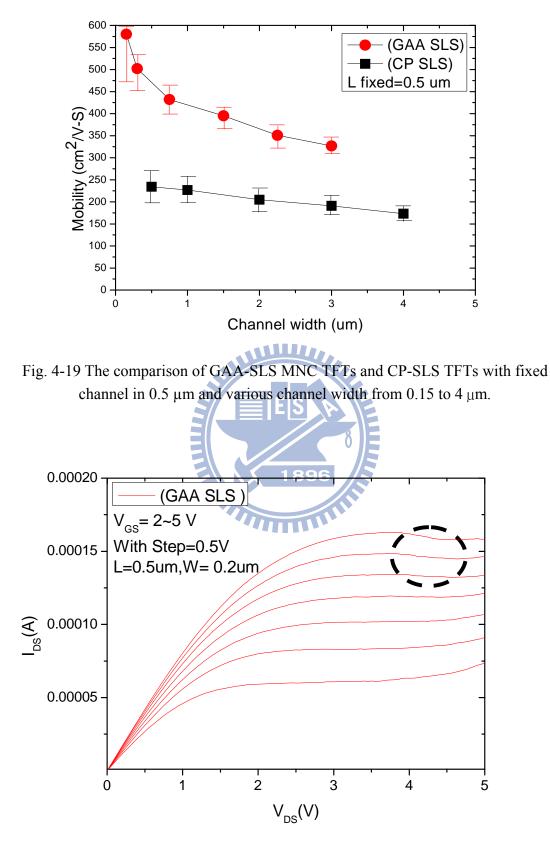

| Fig. 4-19. | The comparison of GAA-SLS MNC TFTs and CP-SLS TFTs with fixed channel                    |

|            | in 0.5-um and channel width from 0.5 µm to 4 µm106                                       |

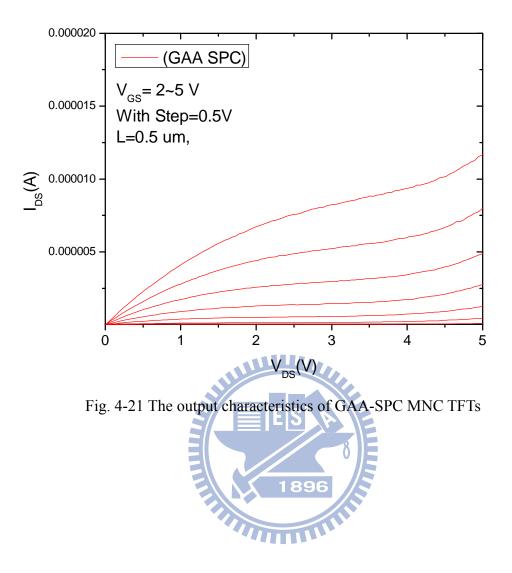

| Fig. 4-20. | The output characteristics of GAA-SLS MNC TFTs106                                        |

| Fig. 4-21. | The output characteristics of GAA-SPC MNC TFTs107                                        |

# Chapter 5

| Fig. 5-1.  | (a) Tilted view of schematic device structure of the proposed FEN-TFT SONOS.          |

|------------|---------------------------------------------------------------------------------------|

|            | (b) Schematic cross-sectional image of each field-enhanced (spacer) nanowire          |

|            | channel with three sharp corners                                                      |

| Fig. 5-2.  | Tilted view of schematic device structure of the proposed FEN-TFT SONOS119            |

| Fig. 5-3.  | Schematic cross-sectional image of each each field-enhanced (spacer) nanowire         |

|            | channel with three sharp corners. The inset shows its corresponding TEM image of      |

|            | the conformal ONO dielectric deposition on the top sharp corner119                    |

| Fig. 5-4.  | the XTEM image of the conformal ONO dielectric deposition on the three sharp          |

|            | corners of the fabricated FEN TFT SONOS                                               |

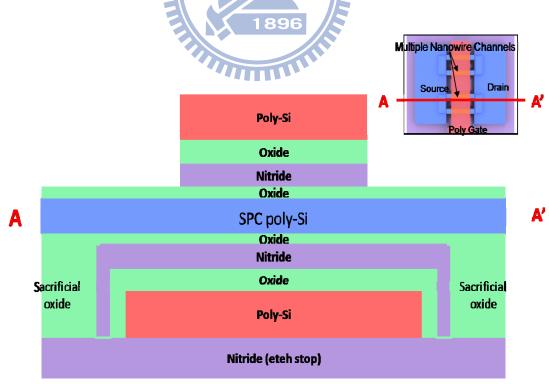

| Fig. 5-5.  | The cross-section schematic image after patterning the in-situ doped poly-Si          |

|            | gate                                                                                  |

| Fig. 5-6.  | The cross-section schematic image after nitride spacers formed121                     |

| Fig. 5-7.  | The cross-section schematic image after tunneling oxide etched with 1:10 diluted      |

|            | BOE                                                                                   |

| Fig. 5-8.  | The cross-section schematic image after passivation and metallization122              |

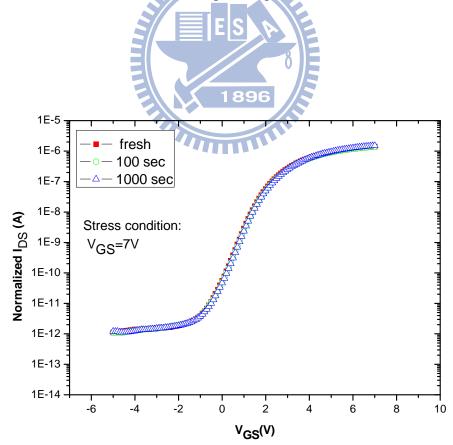

| Fig. 5-9.  | (a) Transfer characteristics of the CP SONOS device after DC stress at $V_{GS}$ = 7 V |

|            | condition. (b) Transfer characteristics of the FEN TFT SONOS device after DC          |

|            | stress at $V_{GS}$ = 7 V condition. Transfer characteristics of the CP SONOS device   |

|            | with various programming times at $V_{GS} = 15 V$                                     |

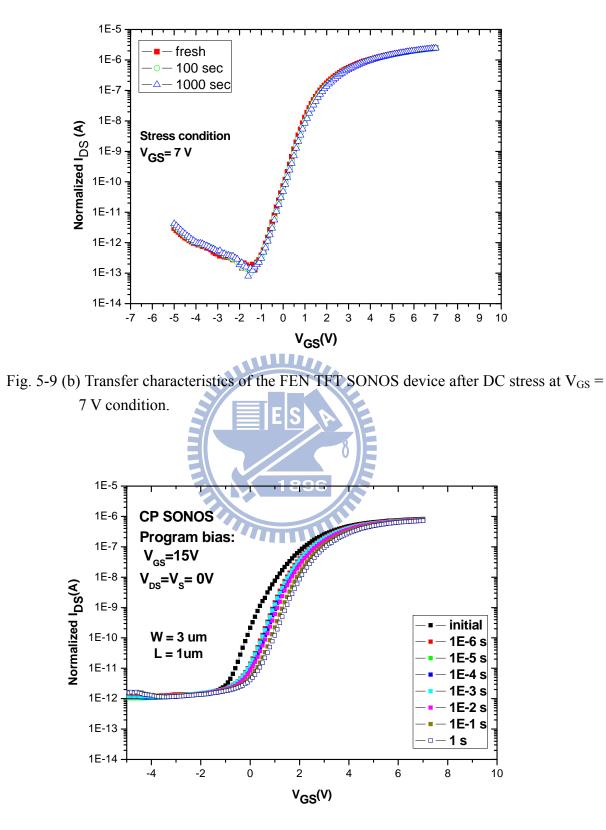

| Fig. 5-10. | Transfer characteristics of the CP SONOS device with various programming times        |

|            | at $V_{GS} = 15 V_{}$ 123                                                             |

| Fig. 5-11. | . Transfer characteristics of the FEN TFT SONOS device with the various               |

|            | programming times at $V_{GS} = 15$ V                                                  |

Fig. 5-12. Transfer characteristics of the CP SONOS device with the various erasing times at Fig. 5-13. Transfer characteristics of the FEN TFT SONOS device with the various erasing Fig. 5-14. (a) Vth shifts after programming for the CP SONOS and FEN TFT SONOS devices with various gate voltage. (b)  $V_{th}$  shifts after erasing operation for the CP SONOS and FEN TFT SONOS devices with various gate voltage......125~126 Fig. 5-15. The distribution of electrical field across the stacked ONO dielectrics for the CP Fig. 5-16. The band diagrams of the CP and FEN TFT SONOS devices at  $V_{GS} = 15 V.....127$ Fig. 5-17. Retention characteristic of the FEN TFT SONOS deviceafter 10<sup>4</sup> P/E cycles.....127 Fig. 5-19. The tiled-view SEM image of the FEN TFT SONVAS device......128 Fig. 5-20. The cross-section schematic image of nanowire channel with vacuum tunneling 1896 Fig. 5-21. Transfer characteristics of the FEN TFT SONOS device with various programming times at  $V_{GS} = 15 V.....129$ Fig. 5-22. Transfer characteristics of the FEN TFT SONOS device with various erasing times Fig. 5-23. The comparison of Vth shift between the FEN TFT SONOS and FEN TFT SONVAS devices with various programming times at  $V_{GS} = 15 V....130$ Fig. 5-24. The comparison of Vth shift between the FEN TFT SONOS and FEN TFT Fig. 5-25. The distribution of electrical field across the stacked ONO dielectrics for the FEN

Fig. 5-26. The distribution of electrical field across the stacked ONO dielectrics for the FEN

|            | TFT SONVAS devices at $V_{GS} = 15$ V                                               | 32  |

|------------|-------------------------------------------------------------------------------------|-----|

| Fig. 5-27. | The band diagrams of the CP and FEN TFT SONOS devices at $V_{GS} = 15 V_{\dots}$    | 33  |

| Fig. 5-28. | Retention characteristic of FEN TFT SONVAS device after 10 <sup>4</sup> P/E cycles1 | 33  |

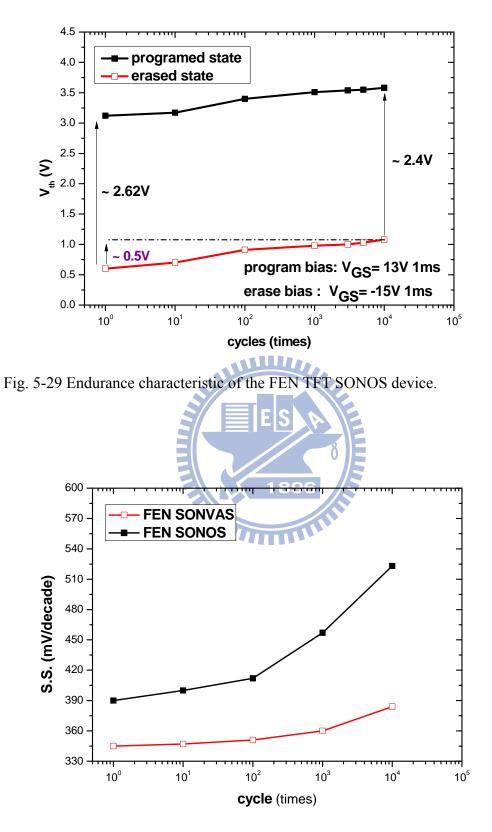

| Fig. 5-29. | Endurance characteristic of the FEN TFT SONOS device1                               | 34  |

| Fig. 5-30. | The subthreshold swing of the FEN TFT SONOS and FEN TFT SONVAS device               | ces |

|            | after P/E cycles1                                                                   | 34  |

# Chapter 6

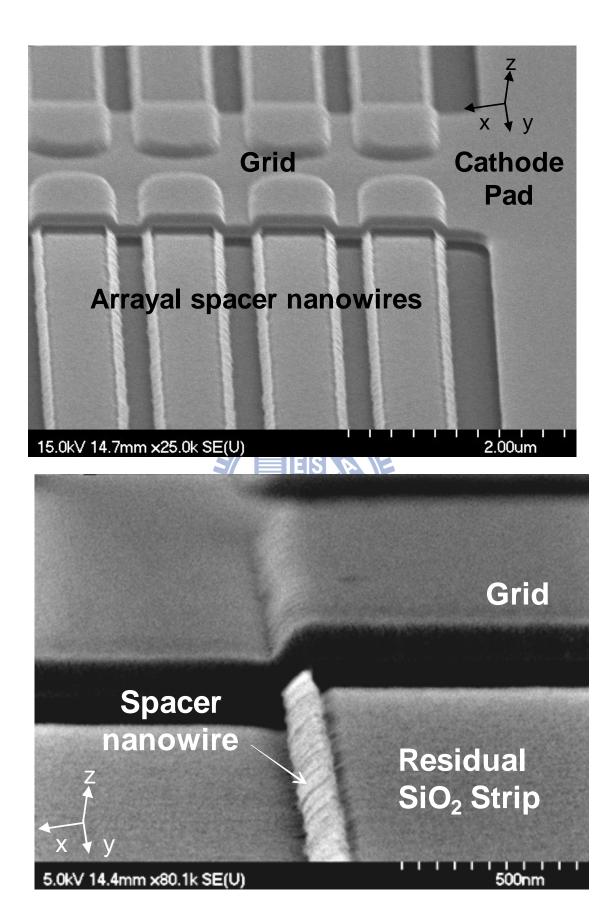

| Fig. 6-1.  | The key fabrication steps of the proposed spacer field emission emitter142         |

|------------|------------------------------------------------------------------------------------|

| Fig. 6-2.  | The key fabrication steps of the triple-corner nanowire emitter in-situ vacuum     |

|            | encapsulated by surrounding Anode Electrode                                        |

| Fig. 6-3.  | SEM image of the arrayal double-corner spacer nanowire emitter144                  |

| Fig. 6-4.  | TEM image of the arrayal double-corner spacer nanowire emitter                     |

| Fig. 6-5.  | The apparatus and schema of the vacuum measure unit146                             |

| Fig. 6-6.  | (a) The I-V curve of the proposed double-corner spacer nanowire emitter. (b) The   |

|            | F-N plot of the proposed double-corner spacer nanowire emitter147                  |

| Fig. 6-7.  | The luminescent image of the double-corner spacer nanowire emitter148              |

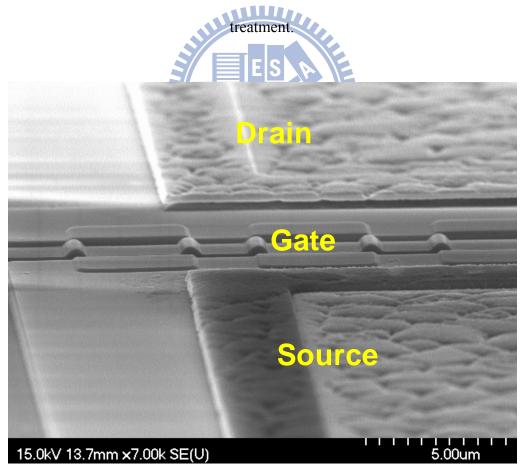

| Fig. 6-8.  | Top-view SEM image of the fabricated triple-corner-nanowire emitter with           |

|            | surrounding anode149                                                               |

| Fig. 6-9.  | Cross-session-view SEM image of the fabricated triple-corner-nanowire emitter      |

|            | with surrounding anode149                                                          |

| Fig. 6-10. | FIB-prepared TEM image of the triple-corner nanowire emitter in-situ vacuum        |

|            | encapsulated with surrounding anode, in which the dash line indicates the original |

|            | position of the triple-corner nanowire before FIB cutting150                       |

|            |                                                                                    |

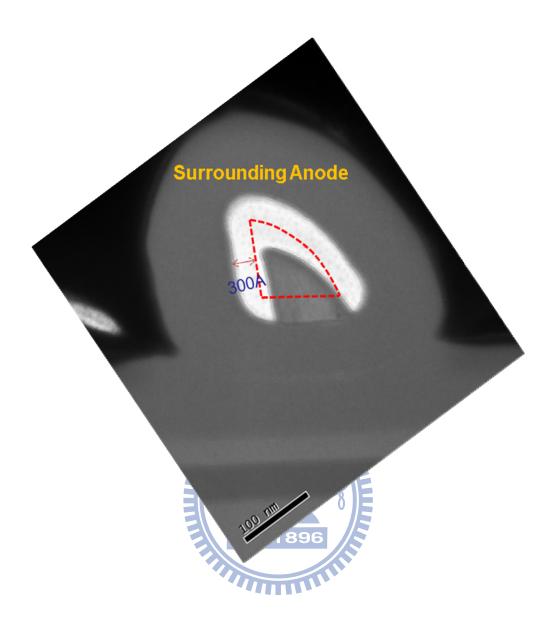

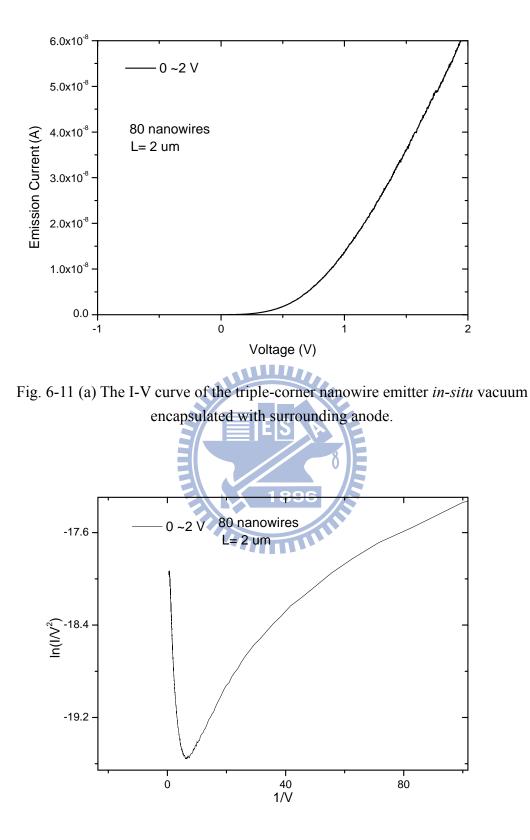

Fig. 6-11. (a) The I-V curve of the triple-corner nanowire emitter in-situ vacuum

encapsulated with surrounding anode. (b) The F-N plot of the triple-corner nanowire emitter *in-situ* vacuum encapsulated with surrounding anode......151

# **Chapter 1**

## Introduction

# 1.1 Overview of Low Temperature Polycrystalline Silicon Thin Film Transistors (LTPS TFTs)

During the last three decades, low temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) have been increasingly used in active matrix displays, such as active matrix liquid crystal displays (AMLCDs) [1.1]-[1.7] and active matrix organic light emitting displays (AMOLEDs) [1.8]-[1.14]. In 1980s, polycrystalline silicon (poly-Si) thin film transistors (TFTs) fabricated using a maximum temperature below 600 °C commenced to study. The original motivation of this concept was to replace expensive quartz substrate with low-cost glass for active matrix display applications. This would make large-area high-resolution active matrix displays more practical and cost-effective.

In the initial stage of active matrix liquid crystal displays (AMLCDs), hydrogenated amorphous silicon (a-Si:H) TFTs were predominantly applied as the pixel switching device. The major advantages of a-Si:H TFT technology are low processing temperature compatible with large-area glass substrate as well as its low leakage current due to the high off-state impedance. However, the low electron field-effect mobility (typically less than 1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>) of a-Si:H TFTs confines their application to the switching elements only. Integration of driver circuitry with display panel on the same substrate is very desirable not only to reduce the module cost but also to improve the system reliability. Thus, poly-Si becomes a very attractive alternative material for the active elements of AMLCDs.

Essentially, the effective carrier mobilities in poly-Si are significantly higher (by two orders of magnitude) than those in a-Si, so that transistors with reasonably high drive currents can be achieved in poly-Si [1.15]. The higher drive current allows smaller TFTs to be used as the pixel-switching elements, resulting in higher aperture ratio and lower parasitic gate-line capacitance for improved display performance [1.16]. In addition, the capability to realize complementary metal-oxide-semiconductor (CMOS) circuits allows low-power driver circuitry to be integrated with the active-matrix elements, for reduced display-module cost and improved reliability [1.17].

Previously, poly-Si TFT technology was primarily applied on small, high-definition LCD panels for projection display systems, because the required high processing-temperature made it incompatible with commercially available large-area glass substrates and necessitated the use of high-cost quartz substrates. In recent years, rapid progress of poly-Si has been made in the development of fabrication processes which are compatible with glass substrates and also in the improvement of process-module throughput, so that the cost-effective manufacture of LTPS TFT AMLCDs and AMOLEDs on large-area substrates increasingly flourishes.

#### **1.2 Key Fabrication Processes of LTPS TFTs**

As compared to modern complementary metal-oxide-semiconductor field-effect transistor (CMOS FET) process technology, the processes of LTPS TFTs technology only can be performed at relative low temperatures which are compatible with glass substrates. As a result, some maturely developed semiconductor fabrication processes in CMOS-FET technology cannot be applied to LTPS TFTs technology, especially on the high-temperature oxidation and dopant activation. Large-area glass substrates used in LTPS TFTs technology

also make precise lithography difficult, including fine critical dimension (CD) definition and layer-to-layer registration. Basically, all kinds of processes in the fabrication of LTPS TFTs would affect the resulting TFT performance. Other than poor crystallinity of poly-Si by nature, there are still some unique processes profoundly affecting the LTPS TFT characteristics, including crystallization of amorphous silicon (a-Si) thin films, dopant activation, defect passivation, and deposition of gate dielectric.

In the following sections, more detailed information about fabrication processes, electrical characteristics, device architectures, and applications of LTPS TFTs is introduced to give an overall concept of LTPS TFT technology.

#

# **1.3 Channel Engineering: Crystallization of Amorphous Silicon** (a-Si) Thin Films

1896

Due to the crystallized poly-Si thin films always served as channel in the poly-Si TFTs, the quality of poly-Si active layer places a profound influence on the performance of poly-Si TFTs. A good-quality poly-Si thin film always results in good electrical characteristics of poly-Si. Thus, crystallization of a-Si thin films has been considered the most important process in the fabrication of LTPS TFTs. The defect density is generally a gauge for assessing the quality of poly-Si. In polycrystalline material, most of defects are always generated in the grain boundaries and intra-grain defects. Essentially, enlarging grain size can reduce the quality of grain boundaries. Hence, enlarging grain size can effectively promote the quality of poly-Si. It is desirable that reducing defect density in poly-Si to approach the quality of single-crystalline to obtain the excellent performance comparable to that of silicon-on-insulator (SOI) device.

Various technologies have been proposed for a-Si crystallization. They can be classified into two groups: solid phase crystallization and liquid phase crystallization.

In solid phase crystallization, thermal annealing provides the energy required for grain nucleation and growth. In general, intrinsic solid phase crystallization needs a long duration to fully crystallize a-Si at low temperature, and large defect density always exists in crystallized poly-Si. In liquid phase crystallization, a laser is usually employed to melting the silicon thin film.

In the following, three kinds of low temperature crystallization methods, which have been most widely studied, are roughly reviewed, including solid phase crystallization (SPC), and liquid phase crystallization.

#### 1.3.1 Solid Phase Crystallization

Solid phase crystallization (SPC) of a-Si is a simple and effective method to acquire poly-Si thin film with large grains [1.18]. In the SPC furnace annealing, the a-Si film is annealed in a furnace for as long as 24 hours at temperatures as high as 600°C. SPC of a-Si thin films involves two distinct processes, namely the nucleation of seeds (formation of clusters of crystalline silicon) and their growth to polycrystalline films [1.19]. The transformation in the a-Si annealing proceeds after an apparent incubation period via nucleation and dendritic-like growth of crystal domain within the amorphous matrix [1.20]. The nucleations of the crystals likely occur through the thermal reaction of seeds, which has an activation energy of about 5 eV [1.20]. The rate of the crystal growth has an activation energy of about 2.7 eV [1.20], [1.21].

Final grain size is known to be large when the nucleation rate is low and the grain growth rate is high [1.20]. Many alternatives to enlarge grain size of the annealed poly-Si thin film

are to modify the structure disorder of the starting a-Si or poly-Si thin film. Previous studies indicated that the grain size was enlarged up to a few micrometers by means of solid-state crystallization of a-Si produced by self-ion bombarded polycrystalline or amorphous films deposited by LPCVD. It is possible that ion-bombardment amorphizes the embryo of crystallines which pre-exist at the interface of the as-deposited amorphous thin films so that the incubation period of nucleation is lengthened [1.22]-[1.24]. On the other hand, it has also been reported that the grain size of the recrystallized films formed from disilane (Si<sub>2</sub>H<sub>6</sub>) is larger than that formed from silane (SiH<sub>4</sub>) [1.25]-[1.28]. The average grain size of the poly-Si thin film resulting from the crystallization of a film deposited in the amorphous phase by thermal decomposition of disilane, is a increasing function of the deposition rate, while as a function of the deposition temperature it exhibits a maximum at certain temperature (about 470°C) [1.29]. This can be attributed to the minimum nucleation rate resulting from the maximum structural disorder of the Si network. For deposition temperature higher than 470°C, the as-deposited silicon thin films have higher structural order (in the form of crystal-like clusters) which results in higher nucleation rate and thus small grain size; whereas at lower deposition temperature the higher structural disorder of the as-deposited film (or equivalently, the higher free energy) provides a driving force for accelerating the nucleation process. The increase in the grain size can also be obtained by increasing the deposition rate of the film [1.29]. Deposition rate also affects the structural order of the as-deposited film. A-Si thin films deposited at higher rates have higher structural disorder which results in lower nucleation rate during crystallization and thus larger grain size. Therefore, crystallization of a-Si thin films deposited by thermal decomposition of disilane yield very large grain size.

On the other hand, a number of researchers have examined the introduction of metal impurities during the SPC process, which is so called metal induced crystallization (MIC). In some case, this has enhanced the crystallization of the a-Si thin films at lower temperature. When a certain metal, for example, Al [1.30], Cu [1.31], Au [1.32], Ag [1.33], Pd [1.34], or Ni

[1.35], is deposited on a-Si, the a-Si crystallizes to poly-Si at a lower temperature than its SPC temperature. The reaction between a metal and a-Si occurs at an interlayer by diffusion and its lowers the crystallization temperature. Such enhancement of crystallization is due to an interaction of the free electrons from the metal with covalent Si bonds near the growing interface. Considering the metal-Si eutectic temperature, an a-Si thin film can be crystallized at below 500°C. A grain size up to 4-5 um has been achieved. However, with this method, the metal contamination is still an issue.

#### **1.3.2 Liquid Phase Crystallization (Laser Crystallization)**

Presently, a widely used method to prepare poly-Si on glass substrates is laser crystallization. Laser crystallization is a much faster process than SPC and MIC and can produce large grained poly-Si with a low dislocation density. The basic principle of laser crystallization is the transformation from amorphous to crystalline silicon by melting the silicon for a very short time. Poly-Si with large grains results from the subsequent solidification [1.36]. Strictly speaking, laser crystallization is not a low temperature process as the silicon is heated well above 1200 °C. However, the high temperatures are only sustained for a very short time. Due to the short time scale the thermal strain on the low-temperature substrates does not lead to severe damage or destruction of these substrates.

Laser crystallization of amorphous silicon has been a subject of intense research for a considerable time. Laser crystallization of a-Si can be performed using a variety of lasers and different techniques [1.37]-[1.40]. However, excimer laser crystallization (ELC) is by far the most widely used method at the moment [1.41], [1.42]. The principal advantage of excimer lasers is the strong absorption of UV light in silicon. In consequence, most of the laser energy is deposited close to the surface of the thin film and the thermal strain on the substrate is much lower than in case of lasers with longer wavelength. The basic transformation processes

for excimer laser crystallization are divided into three crystallization regimes depending on the applied laser fluences and are relatively well understood [1.43], [1.44].

#### **1.3.3 Defect Passivation**

Other than mentioned crystallization, the incorporation of hydrogen into the channel layer (also called hydrogenation) to passivate the defect states is effective and essential for attaining good device performance and also for improving the uniformity of device performance. The electrical behavior of a poly-Si TFT is dominated by the effects of defect states within the poly-Si thin film. The high density of defect states result in poor device performance, such as low field-effect mobility, large leakage current, large threshold voltage, and large subthreshold swing. Because significant hydrogen diffusion occurs at temperatures above  $350^{\circ}$ C, the defects passivation process must be performed after all the high-temperature-processing steps in the poly-Si TFT fabrication processes. On the other hand, it has been reported that TFTs exposed to hydrogen plasma suffer from poor hot carrier endurance and a low thermal stability due to the weak Si-H bond [1.45]. NH<sub>3</sub> and N<sub>2</sub> have also been proposed instead of H<sub>2</sub>. Better hot carrier endurance has been shown as the Si-N bond is stronger than Si-H bond [1.45], [1.46]. Alternative approach, which generates high-density plasma, such as ECR and TCP, may result in equivalent performance with high throughput [1.47].

#### **1.4 Drain Engineering**

For switching devices applications, the off-state leakage current of LTPS TFTs is the major concern. Although the field effect mobility of poly-Si TFTs is much higher than that of amorphous TFTs, the higher anomalous off-state leakage current in poly-Si TFTs is still an issue. The leakage currents can be reduced by either decreasing the trap state density or reducing the high electric field near the drain junction. For the driving circuit applications, the hot carriers phenomena are likely to occur in poly-Si TFTs, where supply voltages can be relatively high in the range 10-30 V [1.48]. As well known in crystalline Si (c-Si) MOSFET's, hot carrier phenomena are strongly depended upon the maximum electric field near the drain junction [1.49]. It is worth pointing out that in poly-Si TFTs, due to the high density of trap states localized at the grain boundaries, it is possible to achieve high electric fields, even at moderate biases. Moreover, poly-Si TFTs also suffer from floating body effect due to impact ionization occurring in the high electric field region at the drain end of the channel. This effect results in an increase of the output conductance, and it is responsible for degradation of the device characteristics both in digital and in analog applications such as noise margins and available voltage gain loss [1.50].

All these undesirable effects, including off-state leakage currents, hot carrier reliability, kink effect are all related to the high electric field near the drain junction.

Drain-field-relief structures are widely adopted to solve these undesirable effects. Lightly doped drain (LDD) and offset gate are commonly used structures for reducing leakage current. However, although the high resistivity of LDD and offset regions can effectively reduce the leakage current, unfortunately, the driving capability of TFTs is also degraded thereby. The resistivity of LDD regions depends on the length of LDD and the dose in LDD. In order to reduce leakage current without degrading driving current significantly and to get a maximum on/off current ratio, the length and dose of LDD should be carefully determined. As well as LDD structure, the length of offset region of offset gate structure should be carefully determine to keep the driving capability. Recently, advanced field-relief-structure such as field

induced drain (FID) [1.51], [1.52] and gate-overlapped LDD (GOLDD) structure has been adopted to suppress the high drain field effects for improving device reliability and reducing leakage current while a high on-state current remains. In FID structures, the offset region is coupled by a sub-gate. The sub-gate is biased to induce inversion carriers in the offset region when the TFTs operate in the on state, so that the inversion carriers contribute to a lower resistivity in on state. In GOLDD structures, the LDD region is overlapped under gate edge. As well as FID structures, the surface of LDD region is inverted to a lower resistivity current path when the TFTs operate in the on state. A high on/off ratio can be achieved by such those advanced application because reducing leakage current while a high on-state current remains. However, the formation of FID or GOLDD structure generally requires an additional lithography step or complex fabrication process. Besides increasing fabrication cost, the misalignment in layer registration can result in asymmetrical characteristics of TFT and poor uniformity of TFT performance, especially for large-area glass substrates.

1896

#### **1.5 Gate Engineering**

For the consideration of low power consumption, high speed and high packing density in system on a panel, there is a need to scale down poly-Si TFTs' device geometries However, scaling down the channel length will leads to undesirable short-channel effects. It will result in the threshold voltage roll-off, degradation in drain breakdown and severe kink effect. Comparing with single-crystalline Si MOSFET, poly-Si TFTs show more seriously short channel effect due to the presence of rich defect in the grain boundaries which enhance the impact ionization effects [1.53]. Since the defect traps play an intense influence on the electrical characteristics of poly-Si TFTs, one effective approach is to reduce the defects by

improving the quality of poly-Si thin film. The other method is to enhance gate controllability to suppress the large filed near drain by modifying the device structures. Recently, for single-crystalline-Si MOSFETs, lots of efforts on non-planar device structures have been developed for better gate electrostatic control of the channel potential, such as double-gated, triple-gated,  $\Pi$ -gated,  $\Omega$ -gated, nanowire channel, and GAA [1.54]-[1.58]. Among those, GAA FETs together with the nanowire channel have been reported to be the best structure for extreme geometry scaling [1.56]-[1.58].

#### 1.6 System on a Panel (SOP) Issues

The advantages of integrating poly-Si TFTs circuits in the panel are not only it can allow pixel pitch to go beyond the bonding pitch of IC chips, but also permit to integrate a variety of circuitry not merely drivers [1.59]. However, the poly-Si TFT LCD module still costs a lot and consumes much power since it needs high driving speed and a wide voltage range analog interface [1.60]. If the TFT driver achieves full digital interface of transistor to transistor logic (TTL) or a lower voltage level, the cost of LCD module will be reduced and power consumption will be decreased.

#### **1.6.1** Concept of System on a Panel

In short, the meaning of system on panel can be defined as the entire system integration on a single substrate including active matrix displays, integrated peripheral circuits, memory circuits, and controller circuits [1.60]-[1.63]. The first system on panel prototype was proposed by Sharp Corp. and Semiconductor Energy Laboratory Co. in 2004, which realizes the integration of CPU, an audio circuit, a graphic controller, and memories on the liquid crystal display by continuous grain silicon (CGS) technology. CG silicon fabricated in low temperature by catalyst assists solid phase crystallization, which doesn't subject to the effects of variations in laser density [1.64]. This crystallization method offers superior reliability and uniformity. The 8-bit CPU contains about thirteen thousand TFTs and operates at 3MHz with 5V voltage supply.

Various kinds of voltage or signal losses come into existence in the module because the system has to transfer enormous data between the large scale circuits at high frequency [1.60]. If the large scale circuits can be entirely integrated in the same substrate without sacrificing functional properties, the total performance will be improved and the power consumption will be diminished theoretically. More importantly, the size, weight, and cost of the system will be cut down which is beneficial to the consumers.

There are two main considerations to achieve the goal of system on panel. First, the properties of poly-Si TFTs must be improved such as better mobility (larger than 400 cm<sup>2</sup>/Vs), shorter channel device (less than 1  $\mu$ m), lower sub-threshold swing (~0.1 V/dec), lower threshold voltage(~±0.7 V), higher on/off current ratio (~10<sup>9</sup>) are needed. Second, the circuit interconnection technique needs to be promoted. When shrinking the transistor size, excellent uniformity and reliability are critically required for the development of SOP.

#### **1.7 Motivation**

Low temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) have received much attention in recent years because of their increasing use in active matrix

displays, such as active matrix liquid crystal displays (AMLCDs) [1.1]-[1.7] and active matrix organic light emitting displays (AMOLEDs) [1.8]-[1.14], and potential for 3-dimension ICs' applications [1.65]. The ability of fabricating high-performance LTPS TFTs enables their use in further applications of SOPs. Therefore, there is great interest in improving the performance of LTPS TFTs. Considering the issues of system on panel (SOP) mentioned in former section, both the LTPS TFT performance and the added-value functionality need to be further promoted and developed. For the further development, high versatile circuits and systems need to be fully integrated to achieve system-on-panel (SOP). As performance and complexity requirements increase, there is a need to scale down device geometries to achieve higher speeds and packing densities. Unfortunately, those undesirable effects in the electrical characteristics that mentioned above become particularly important as the channel length and gate insulator thickness are reduced. Those all are increased with the higher drain electric field near the drain junction. These undesirable effects prohibit the use of poly-Si TFTs in many high-performance circuit applications. Therefore, the drain-field-relief structure plays an essential role for the future prospection. However, those structures often required complicated process (such as, spacer and damascene processes), or additional mask step which may raise the mis-alignment problem. In chapter 2, a novel and simple process was introduced to fabricate T-shaped gate (T-Gate) structures.

Especially for high-speed and low-power applications, the scaled-down LTPS TFTs with high performance are required. Unfortunately, several short-channel effects are known to aggravate with reducing device dimension, such as threshold voltage roll-off, higher subthreshold swing, larger drain-induced barrier lowering (DIBL), and acuter kink effect. The short-channel effects seriously restrict these applications. Recently, for single-crystalline MOSFETs, lots of efforts on non-planar device structures have been developed for better gate electrostatic control of the channel potential, such as double-gated, triple-gated,  $\Pi$ -gated,  $\Omega$ -gated, NW fin-channel, and gate-all-around (GAA). Among those structures, the GAA structure with nanowire channels is proposed to be the best structure to provide the immunity of short-channel effects. Additionally, the poly-Si TFTs suffer more serious short-channel effects than SOI devices due to the presence of grain boundary and intra-grain defects in channel region. However, there are few works presented such structures on poly-Si TFTs so far. In chapter 3, the gate-all-around poly-Si TFTs with multiple nanowire channels, for the first time, are proposed by using simple process sequence to achieve high electrical performance and effectively suppress the short-channels effects.

Since the quality of poly-Si active layer places a profound influence on the performance of poly-Si TFTs, crystallization of a-Si thin films becomes the most important process issue in the fabrication of high-performance LTPS TFTs. A good-quality poly-Si thin film always results in good electrical characteristics of poly-Si. Various crystallization technologies have been propose to create high-quality poly-Si thin films on foreign substrates at low temperature, however, most of them are still complex and not easy to control. As a result, in chapter 4, two types of simple process sequences were demonstrated for fabricating gate-all-around LTPS TFTs with high-crystallinity Si nanowire (NW) channels. The one is the excimer-laser-crystallized (ELC) nanowire TFT, in which the nanowire structure features only-one grain boundary. The other is the spacer-patterned nanowire TFT based on large-grain poly-Si thin film prepared with sequential-lateral-solidification (SLS) crystallization, in which the nanowire can be controlled to be approximated single-crystalline.

In addition to promoting the device performance of basic LTPS TFTs, for system-on-panel (SOP) developments, other added-value functional elements based on poly-Si TFT technology, such as memory and display elements are also needed to develop to fully integrate on the same display panel. In chapter 5, we utilized the spacer technique to promote nonvolatile memory performance on SONOS NVM for SOP applications. In chapter 6, we further applied this technique on two types of field emitters for the opportunity of replacement of LCD display elements in terms of system integration and image performance.

#### **1.8 Thesis Organization**

In this thesis, various structures and techniques are studied for the fabrication of high-performance low temperature polycrystalline silicon (LTPS) thin film transistors (TFTs) through drain, gate, and channel engineering. In addition, for diversified SOP application, the SONOS memory, field emitters and flexible electronics are developed. The outline of thesis organization is shown in Fig. 1-2.

In chapter 2, a novel and simple process was introduced to fabricate T-shaped gate (T-Gate) structures.

In chapter 3, the gate-all-around poly-Si TFTs with multiple nanowire channels are proposed by using simple process sequence to achieve high electrical performance and effectively suppress the short-channels effects.

In chapter 4, two types of novel and simple processes were demonstrated for fabricating high-crystallinely Si nanowire LTPS TFTs with gate-all-around structures for channel engineering development.

In chapter 5, based on previous proposed gate-all-around structure, two kinds of trapping-charge memory devices with field-enhanced nanowire and/or <u>silicon-oxide-vacuum-oxide-silicon</u> (SONVAS) structures were proposed for the first time to improve the memory performance and reliability with a simple process sequence for SOP applications.

In chapter 6, we further applied this technique on two types of field emitters for the opportunity of replacement of LCD display elements in terms of system integration and image performance.

Finally, summary and conclusions as well as recommendation for further research are given in chapter 7 and chapter 8, respectively.

# Figures

### Development of System On Panel (SOP)

Fig. 1-1 Development of system on panel (SOP)

### **Thesis Organization**

# **Chapter 2**

# Novel T-Shaped-Gate Polycrystalline Silicon Thin Film Transistors with *in-situ* Embed Vacuum

#### 2.1 Introduction

Poly-Si thin film transistors (TFTs) have been widely applied as switching elements in active matrix liquid crystal displays (AMLCDs), and active matrix organic light emitting diodes (AMOLEDs) [2.1]-[2.5]. Unlike the conventional amorphous silicon TFTs, poly-Si TFTs exhibit higher driving current. For further SOP development, high versatile circuits and systems need to be fully integrated on the display panel substrate [2.6], [2.7]. Unfortunately, conventional poly-Si TFTs suffer from anomalous off-state leakage current, serious kink effect, and hot-carrier instability, which are all related to the high electric field near the drain junction. Those undesirable effects prohibit the use of poly-Si TFTs in many high-performance and low-standby-power circuit applications. The dominant off-state leakage current is due to the field emission via grain boundary traps induced by the high electric field in the drain depletion region [2.8], [2.9]. It has been widely reported that the offset-gated and lightly doped drain (LDD) poly-Si TFTs can effectively reduce the maximum drain electric field in the channel. However, the offset-gated poly-Si TFTs cause a high parasitic resistance in the offset region which severely decreases the on-current [2.10], [2.11]. Besides, in LDD structure, the device degradations due to the additional n- implant damage caused by low-temperature activation of dopants (< 600 °C) and difficulty in doping control at the grain boundaries are also serious problems [2.12]. Recently, the offset-gated poly-Si TFTs with

sub-gate structures together with thicker dielectrics below sub-gate, which have lower off-state leakage current, while maintain high turn-on characteristics, as well as free from LDD implant damage, have been reported [2.13]-[2.15]. However, those structures often required complicated process (such as spacer and damascene processes), or additional mask step which may raise the mis-alignment problem [2.16].

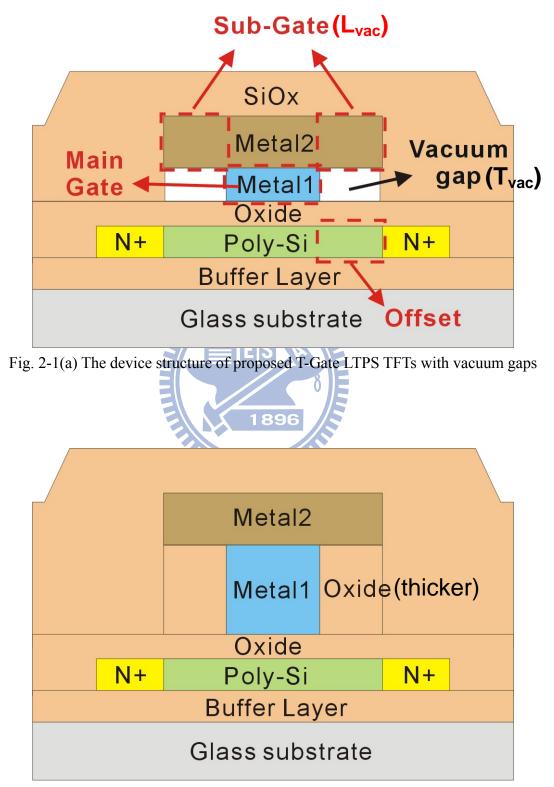

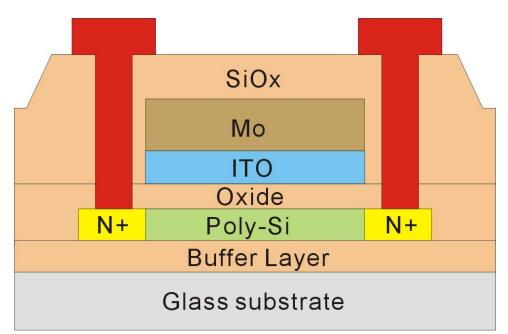

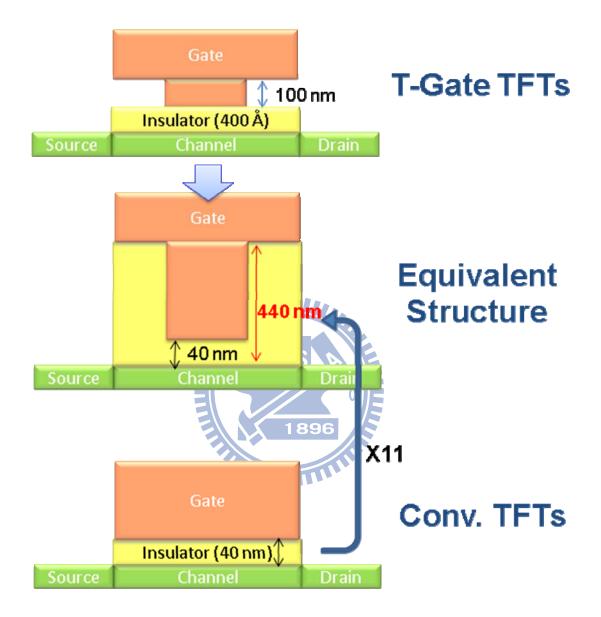

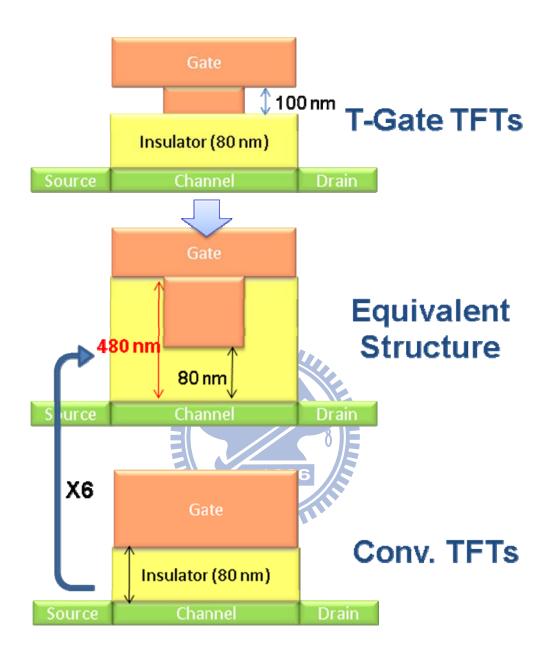

In this chapter, a T-shaped-gated (T-Gate) poly-Si thin-film transistor with self-aligned sub-gates and *in-situ* embed vacuum is proposed and fabricated only with a simple selective side-etching process and without any additional photo-lithography step. Besides, novel vacuum (the lowest permittivity of k=1 in nature) gaps embedded in this T-Gate structure are *in-situ* created via capping the SiH<sub>4</sub>-based passivation oxide in plasma enhanced chemical vapor deposition (PECVD) system [2.17].

The schematic figure of the proposed T-Gate TFTs and its equivalent structure were shown in Figs. 2-1(a) and (b), respectively. The vacuum gaps can reduce the vertical electric field near the drain due to its lowest permittivity of k=1. The vacuum gaps serve as an equivalent thicker oxide. Due to the relative static permittivity SiO<sub>2</sub> of 3.9, the equivalent oxide thickness of the vacuum gap is as high as 3.9 times [2.18]-[2.20]. The poly-Si region under vacuum gaps can be considered as the offset region and the gate edge over the vacuum cavity serves as a field plate connected with the main gate, so that the proposed TFT operates similar as the field induced drain (FID) TFTs.

# 2.2 Electrical Simulations for T-Gate LTPS TFTs with Vacuum Gaps

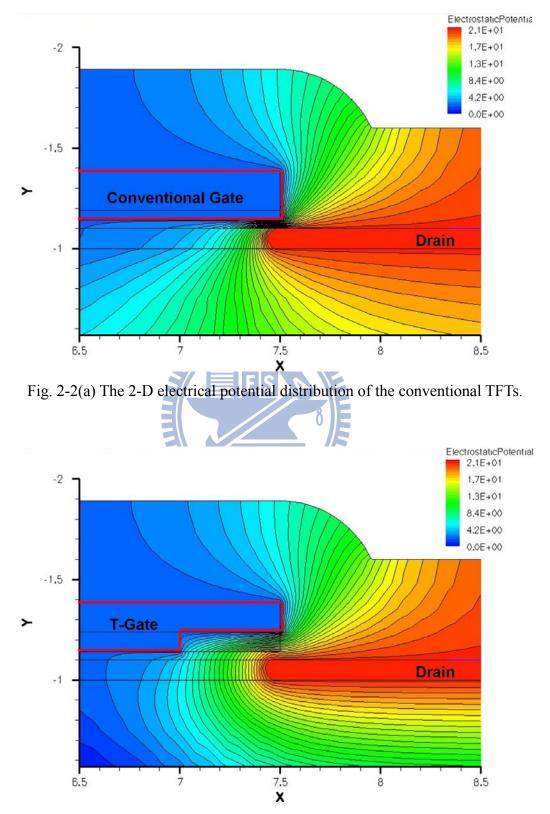

Device simulation is first carried out to compare the electric field distributions of T-Gate

TFTs with different vacuum-gap thickness ( $T_{vac}$ ) and length ( $L_{vac}$ ) which are followed by the experimental details of device fabrication. The 2-D numerical simulation was carried out using ISE which is a commonly used numerical simulator for device analysis [2.21]. Figs. 2-2 (a) and (b) display the simulated potential contours of the proposed T-Gate and the conventional poly-Si TFTs at  $V_{GS} = 1.5$  V and  $V_{DS} = 20$  V, respectively. It can be seen evidently that in the T-Gate LTPS TFT, the electrostatic potential contours at channel surface near the drain can be relaxed remarkably by the additional offset region and vacuum gap, as compared with that in the conventional device. Under higher negative gate bias, the effective thicker gate insulator resulting from the extra vacuum gap can make less gate voltage couple to the drain junction [2.22]-[2.24]. Thus, not only the maximum lateral electric field ( $E_{ML}$ ) but also the maximum vertical electric field ( $E_{MV}$ ) can be effectively reduced for the proposed T-Gate poly-Si TFT.

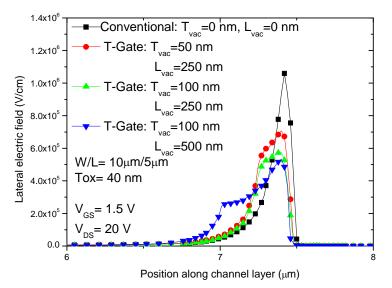

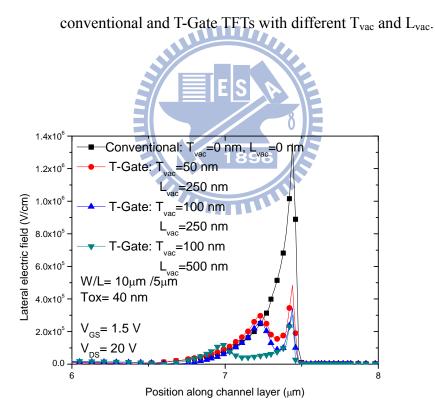

Figs. 2-2 (a) and (b) show the 2-D electrical potential distribution of the conventional and T-Gate TFTs, respectively. The dense equi-potential lines near the drain region in conventional TFTs can be significantly relaxed in the T-Gate TFTs, indicating that electric field is consequently reduced by T-Gate structure. Figs. 2-3 (a) and (b) shows the corresponding simulated lateral and vertical electric field distributions along the channel surface near the drain junction for T-Gate TFTs with various  $T_{vac}$  and  $L_{vac}$ , respectively. The maximum lateral and vertical electric field decreases with increasing  $T_{vac}$  and  $L_{vac}$  in the T-Gate TFT. The reduction of vertical electric field is dominated by the vacuum-gap height ( $T_{vac}$ ), while reduction of lateral electric field is dominated by the offset length (i.e. the side-etching length,  $L_{vac}$ ).

Thus, the maximum electric field near the drain can be effectively decreased by applying the T-Gate structure.

#### 2.3 Experiments

#### 2.3.1 Fabrication Sequence of T-Gate Poly-Si TFTs with Vacuum Gaps

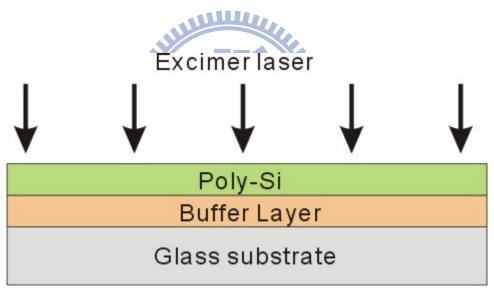

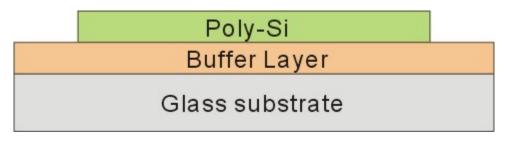

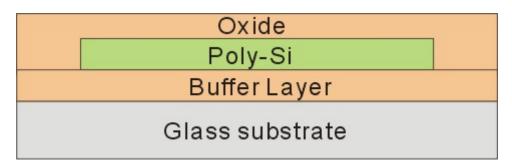

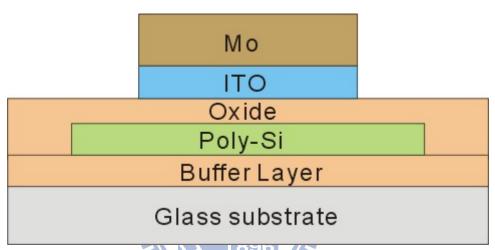

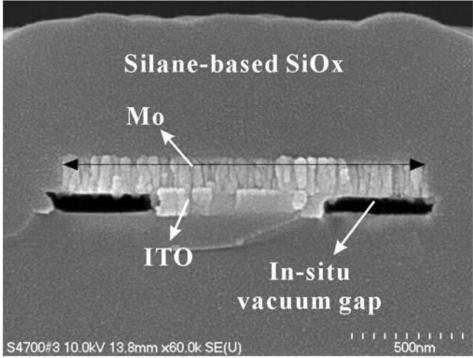

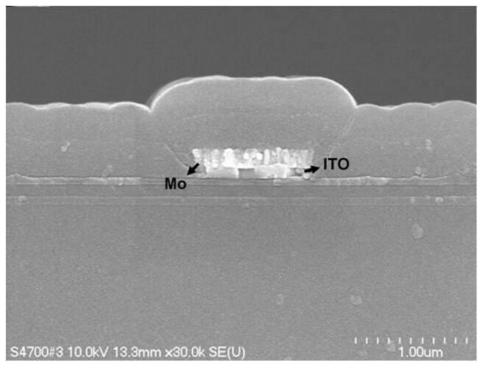

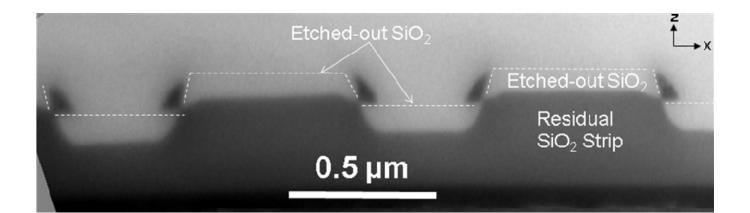

The detailed process flow of device fabrication is shown in Figs. 2-4 (a)-(k). At first, a buffer layer that composed of 50nm-thick SiN and 130nm-thick SiO<sub>2</sub> thin films was deposited by plasma-enhanced chemical vapor deposition (PECVD) system on the glass substrate. Then, a 50 nm amorphous silicon (a-Si) thin film was deposited by PECVD system on buffer layer. Before excimer laser crystallization, dehydrogenation at 500 °C for 15 minutes was carried out to prevent the hydrogen explosion during laser irradiation. The a-Si thin film was transferred into poly-Si by 308-nm XeCl excimer laser with laser energy density of 257 mJ/cm<sup>2</sup> and shot overlapping of 99%. After defining the active layer, a 40 nm or 80 nm-thick SiO<sub>2</sub> was deposited as gate insulator by PECVD system at 420 °C. A 50 or 100 nm-thick indium tin oxides (ITO) and a 200 nm-thick Mo films were deposited by sputter system at room temperature sequentially. The stacked Mo/ITO films were simultaneously etched to pattern as the gate electrode. An oxalic acid, (COOH)<sub>2</sub> • 2H<sub>2</sub>O, solution was then used to selectively etch the ITO layer without harming Mo layer to form the T-shaped structure. Different side etching lengths of ITO thin film were carefully controlled to 250 and 500 nm confirmed by the scanning electron microscope (SEM) analyses. A self-aligned phosphorous implantation was carried out to form source and drain regions with the implantation energy and dosage of 15 keV and 2  $\times$  10<sup>14</sup> cm<sup>-2</sup>, respectively. Then, a 500-nm-thick inter-layer dielectric of silane (SiH<sub>4</sub>)-based SiO<sub>2</sub> was deposited by PECVD system. It should be noted that the vacuum gaps were *in-situ* formed during the inter-layer dielectric deposition by PECVD due to the active chemical properties of silane-based (SiH<sub>4</sub>) free radicals [2.25]. Then, the dopants were activated through rapid thermal annealing (RTA) at 620 °C for 30 seconds.

After standard contact hole opening, 500-nm-thick Al was deposited and patterned as interconnect metal. Finally, some TFTs were subjected to the NH<sub>3</sub> plasma treatment at 300 °C for 1 hour to passivate the dangling bonds at the poly-Si/SiO<sub>2</sub> interface and the trap-states within the poly-Si film. For the purpose of comparison, the conventional poly-Si TFTs without side-etching process shown in Fig. 2-11(1) were also fabricated with the same process sequence. For all T-Gate devices, the channel length (L) is defined as the length of the patterned Mo gate electrode, the height of vacuum gap (labeled as  $T_{vac}$ ) is determined by the thickness of deposited ITO, and the length of vacuum gap (labeled as  $L_{vac}$ ) is determined by the length of side-etched ITO. The split conditions of various  $T_{vac}$  and  $L_{vac}$  were designed and listed in Table 2-1. The corresponding SEM images of the fabricated T-Gate and the conventional TFTs are shown in Figs. 2-5 and 2-6, respectively.

2.4.1 Method of Electrical Parameter Extraction

In the whole thesis, all the electrical characteristics of LTPS TFTs were measured by HP 4156C semiconductor parameter analyzer. Extraction methods of all the electrical parameters mentioned in this thesis, including the threshold voltage ( $V_{th}$ ), subthreshold swing (S.S.), maximum on-current ( $I_{on}$ ), minimum off-current ( $I_{off}$ ) and the on/off current ratio, are introduced.

#### Threshold Voltage (V<sub>th</sub>)

The method to determine the threshold voltage in this thesis is the constant drain current

method, that is, defined as the gate voltage required to achieve a normalized drain current of  $I_D = (W/L) \times 10^{-8} \text{ A at } |V_{DS}| = 0.1 \text{ V}.$

#### Field effect mobility ( $\mu$ )

The field effect mobility is extracted from the maximum transconductance in the linear region of  $I_{DS}$ - $V_{GS}$  characteristics at  $|V_{DS}| = 0.1V$  using the formula:

$$\mu^* = \frac{g_m}{C_{ox}(\frac{W}{L})V_{DS}} (@V_{DS} = 0.1V) \dots (1)$$

, where  $C_{ox}$  is the gate oxide capacitance per unit area, and the transconductance  $(g_m)$  is defined as:

$$g_m = \frac{\partial I_D}{\partial V_g} |_{V_{DS} = 0.1V}$$

(2)

Field effect mobility is an important parameter for carrier transport; it describes how strong the motion of an electron or hole is influenced by the applied electric field.

1896

#### Subthreshold swing (S.S.)

Substhreshold swing (SS) is defined as:

It is a typical parameter to describe the control ability of gate toward channel.

#### Maximum on-current and Maximum leakage-current

In this chapter, on-current is defined as the drain current measured at  $V_{GS}$ = 15V,  $V_{DS}$ = 3V. Maximum leakage current is defined as the drain current measured at  $V_{GS}$ = -15V,  $V_{DS}$ = 3V.

#### **On/off current ratio**

The on/off current ratio is defined as the ratio of maximum drain current over minimum drain current at  $|V_{DS}| = 3 \text{ V}$ .

A high performance poly-Si TFT should not only provides high on-state driving current but low off-state leakage current. High on-state driving current means the pixel capacitances could be charged more efficiently during a line access time. Sufficiently low off-state leakage current represents the charged capacitance could remain stable during the much longer frame time. Therefore, on/off current ratio is obviously a more appropriate evaluation parameter compared with on-state or off-state current alone.

#### 2.4.2 Electrical Characteristics of T-Gate TFTs with Vacuum Gaps

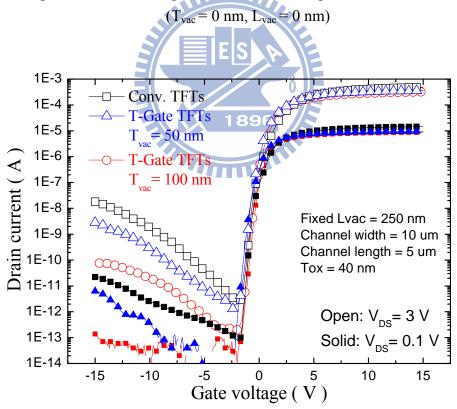

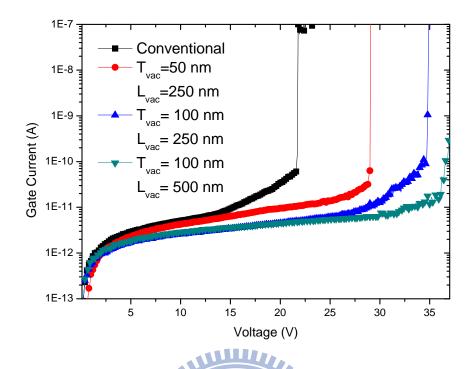

Fig. 2-7 shows the transfer characteristics of T-Gate LTPS TFTs with different  $T_{vac}$  and fixed  $L_{vac}$ ; while Fig. 2-8 shows those with different  $L_{vac}$  and fixed  $T_{vac}$ . All T-Gate LTPS TFTs are with channel length of 5 µm and channel width of 10 µm, and gate oxide thickness of 400 Å. It is shown that the leakage current of T-Gate LTPS TFTs could be remarkably suppressed without degrading on current significantly. It is attributed to the drain field relief via the offset region and vacuum gap to reduce the leakage current at the off state, and the low series resistance via field plate assistance to maintain the on current at the on state. The leakage current of T-Gate LTPS TFTs could also be further reduced by increasing the  $T_{vac}$  or  $L_{vac}$  due to the more vertical or lateral drain-field reduction, respectively, which is consistent with previous simulated results. For the T-Gate TFTs with  $T_{vac} = 100$  nm and  $L_{vac} = 500$  nm, the leakage current could be suppressed to below 1 pA at  $V_{DS} = 3V$  and  $V_{GS} = -15V$ , which is about three-order reduction as compared to conventional one, and the maximum on/off

current ratio could be promoted to beyond  $10^9$ . Table 2-2 lists the typical electrical characteristics of these devices.