# 國立交通大學

電子工程學系 電子研究所

博士論文

奈米點應用於先進非揮發性記憶體之製作與特性研究

Fabrication and Electrical Characterization of Advanced Nonvolatile Memories Based on Nanocrystals

研 究 生:林昭正

指導教授:曾俊元與張鼎張

中華民國九十八年七月

### 奈米點應用於先進非揮發性記憶體之製作與特性研究

## Fabrication and Electrical Characterization of Advanced Nonvolatile Memories Based on Nanocrystals

研究生:林昭正 Student: Chao-Cheng Lin

指導教授:曾俊元 Advisor: Dr. Tseung-Yuen Tseng

張鼎張

Dr. Ting-Chang Chang

國立交通大學

子工程學系電子研究所

博士論文

A Dissertation

Submitted to Department of Electronics Engineering and

Institute of Electronics

College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in

111

**Electronics Engineering**

May 2009 Hsinchu, Taiwan, Republic of China

中華民國 九十八年七月

### 奈米點應用於先進非揮發性記憶體之製作與特性研究

研究生: 林昭正 指導教授: 曾俊元與張鼎張

## 國立交通大學 電子工程學系電子研究所

#### 中文摘要

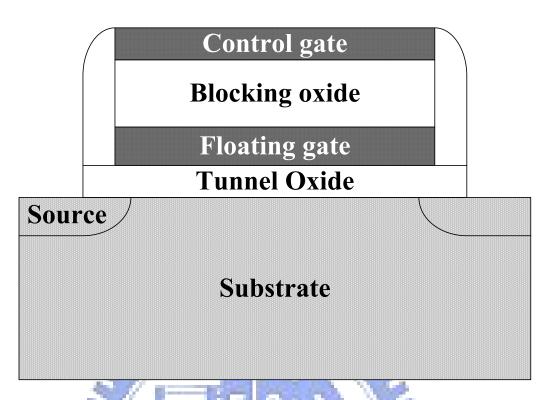

近年來,以傳統浮閘(Floating gate)記憶體為基本元件之非揮發性固態半導體記憶體已被廣泛的應用於各種電子產品。為獲得更高密度、低功率損耗與快速讀寫的操作驅使目前非揮發性記憶體在元件尺寸上持續的微縮。然而傳統浮閘記憶體在寫入與抹除的持續操作後,會在穿遂氧化層產生漏電路徑使得原本儲存的電荷全部流失回到矽基版,而且這個情形隨著尺寸的微縮而更加的嚴重。因此,在資料保存時間(Retention)和耐操度(Endurance)的考量下,微縮穿遂氧化層的厚度是非常困難的。具非揮發性的奈米點記憶體被提出並存有希望可取代傳統浮閘記憶體。由於以空間上與電性上分離的奈米點作為儲存中心,所以可以有效改善尺寸微縮時,記憶體元件在多次讀寫操作後的資料儲存能力。除了奈米點記憶體外,電阻式非揮發性記憶體(RRAM)近年來也成為學者與工業界的焦點。主要是由於其製程簡單且與動態隨機存取記憶體(DRAM)製程相似,可以被整合到半導體的後段製程。電阻式記憶體擁有高速、非揮發性與低電壓操作的特性等優點。

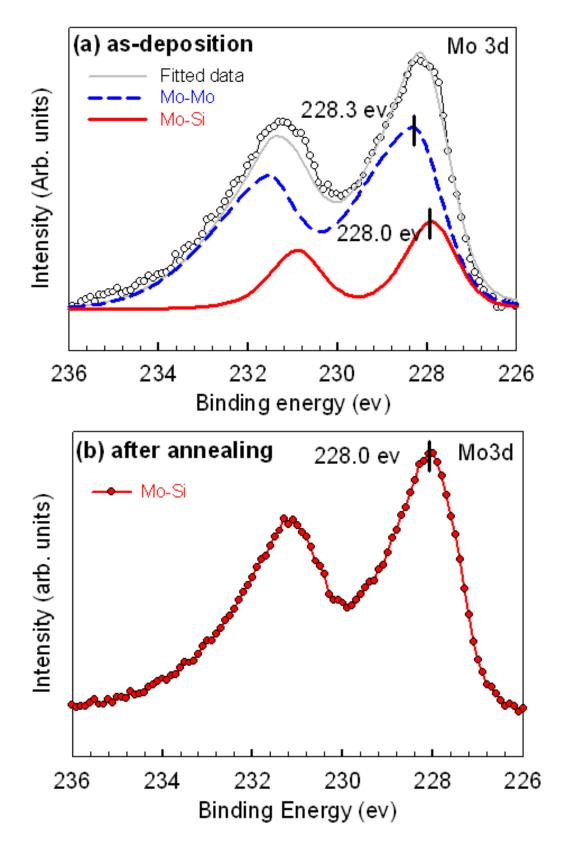

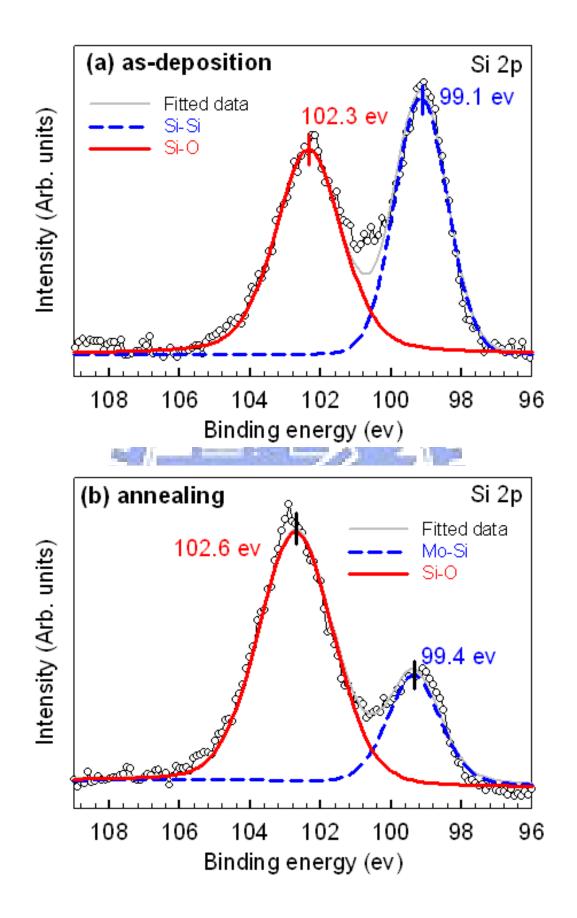

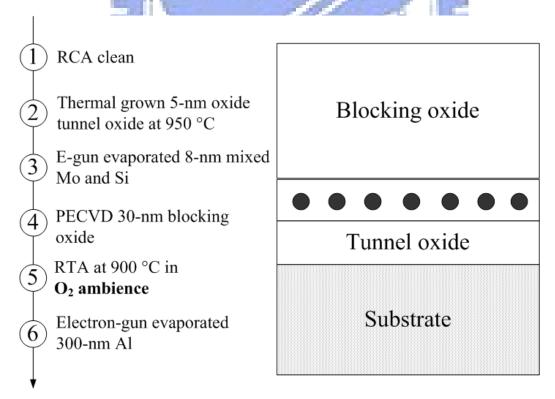

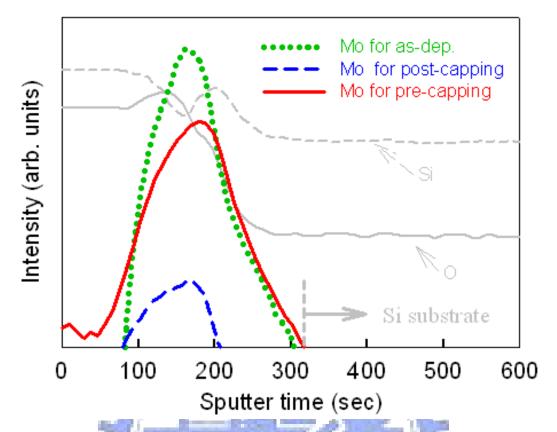

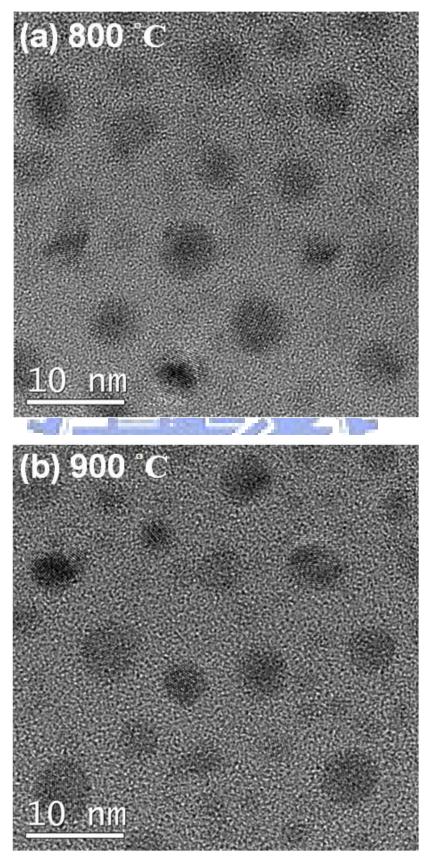

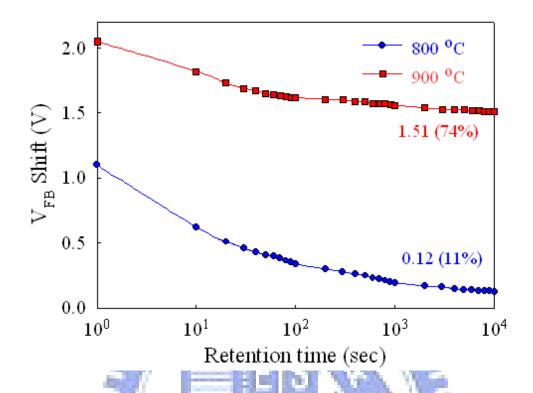

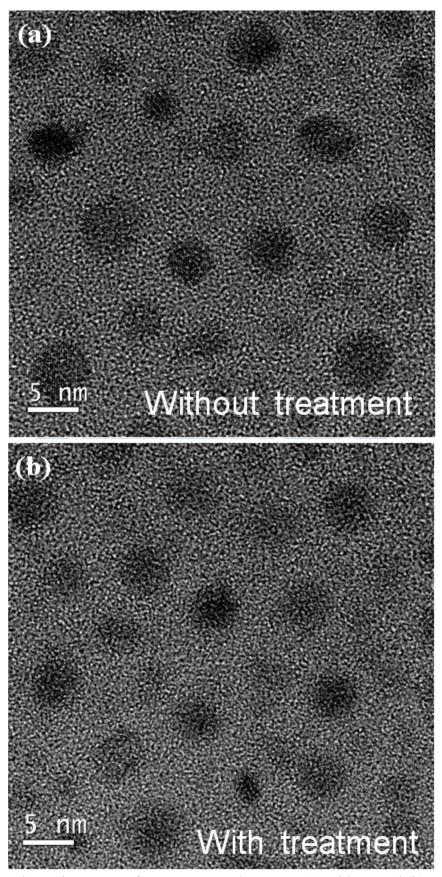

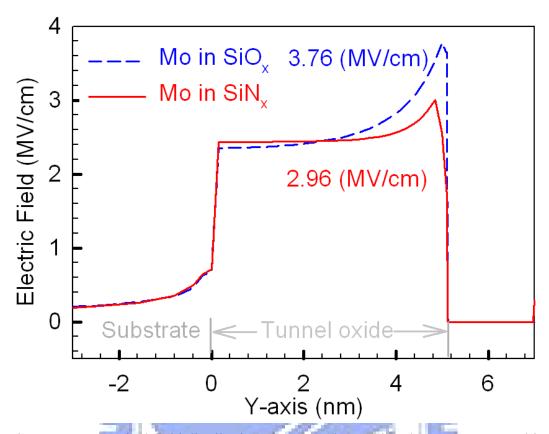

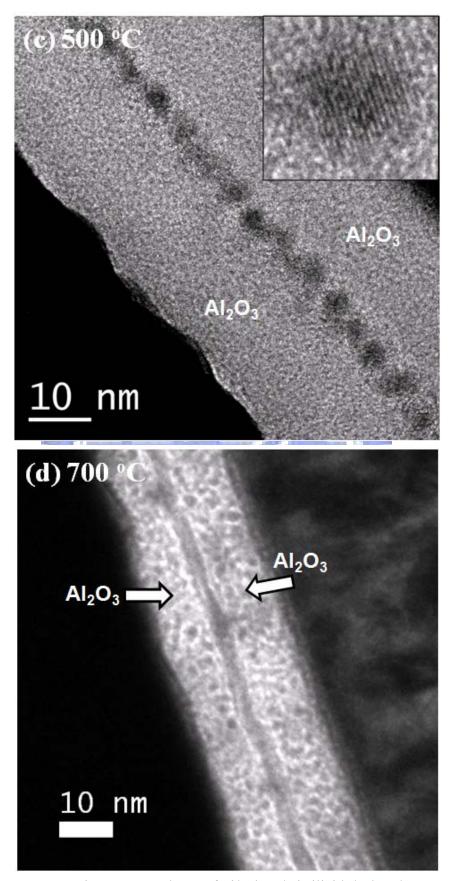

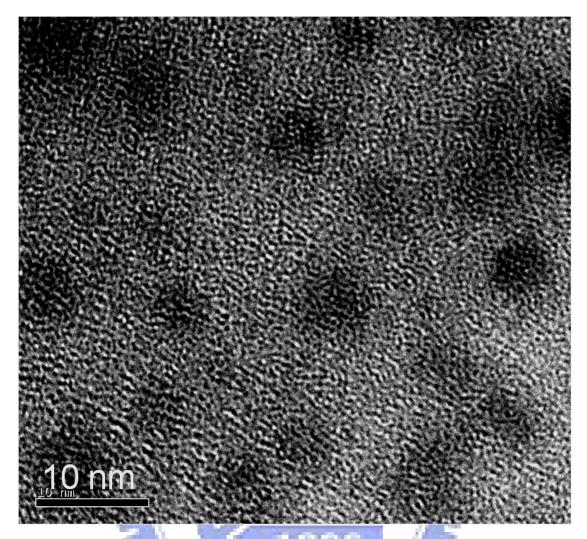

在本論文中,我們將研究鉬(Mo)與鉬化矽作為奈米點材料來克服傳統非揮發性記憶體在微縮過程中會遭遇到的困難。相較於其他金屬材料,鉬具有低價格,高溫熱穩定性,與高功函數等優點。我們首先提出對鉬化矽退火以形成鉬金屬奈米點,並應用在奈米點非揮發性記憶體上。在室溫環境中,利用雙電子槍(dual electron-gun)同時以一比三的比例蒸鍍矽與鉬(Si and Mo)的方式來形成奈米點自

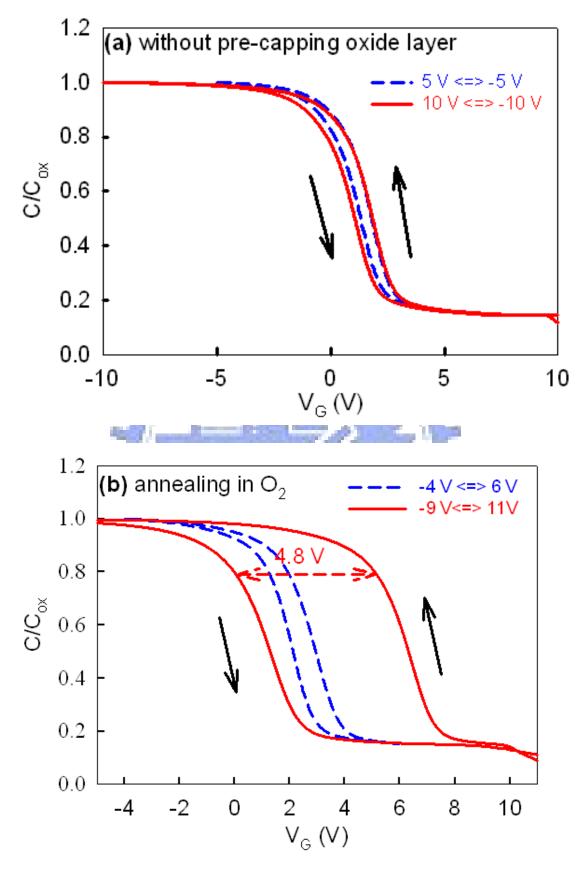

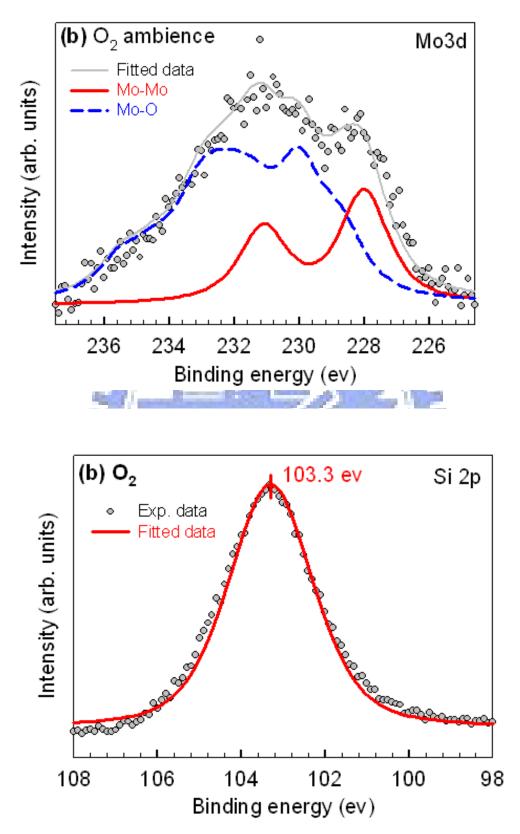

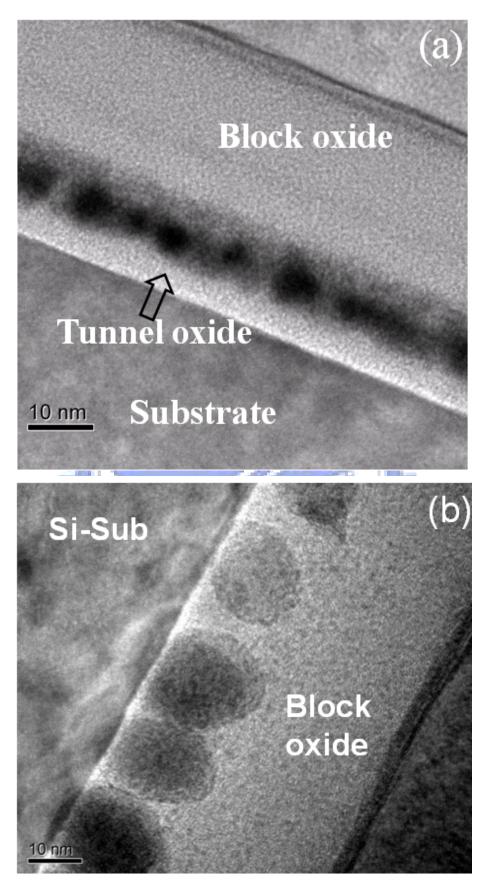

我形成層,再以退火的方式使奈米點形成。在我們的實驗中,我們發現奈米點的大小與組成的成分會因退火的氣氛(ambience)不同而有所差異。在氮氣熱退火下,可以發現所形成的奈米點大約5-nm且所組成的成分主要為矽化鉬(MoSi<sub>2</sub>),而在氧氣退火下,會使得所形成的奈米點大小約20-nm且組成成分以氧化鉬為主(Mo oxide)。除此之外,我們發現在氧氣退火前先疊一層氧化矽可阻擋氧化鉬揮發。此為形成氧化鉬奈米點的一個關鍵步驟。

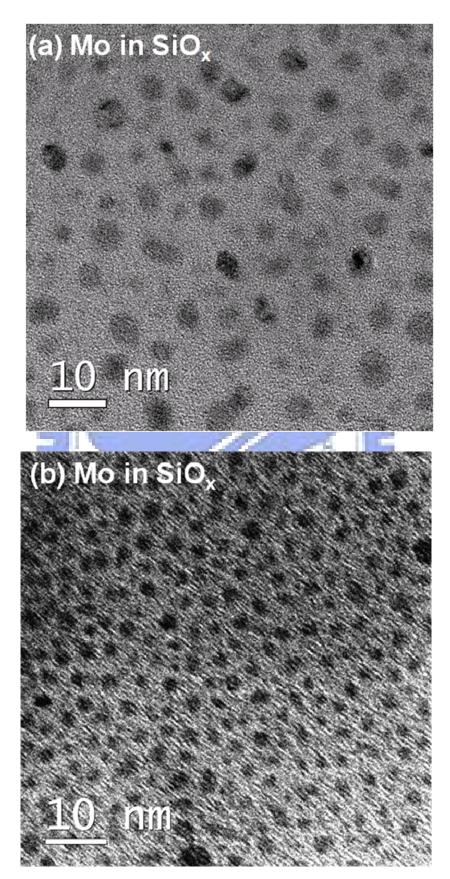

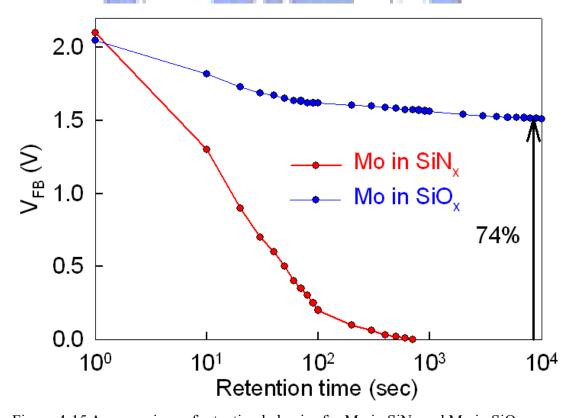

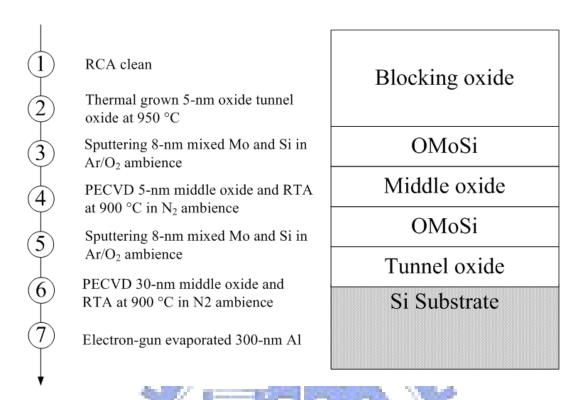

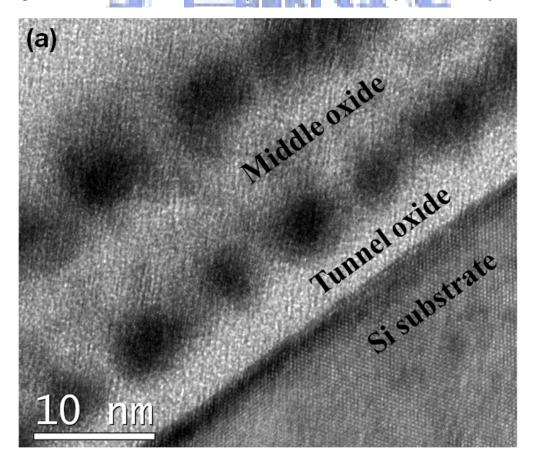

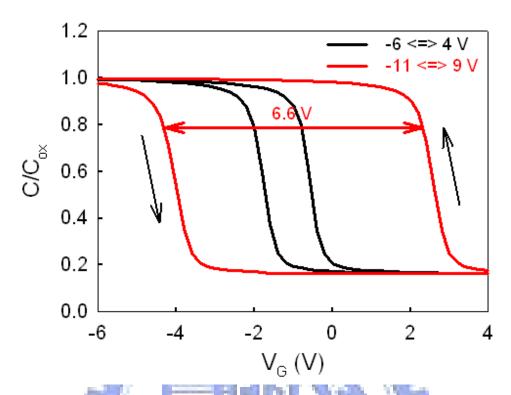

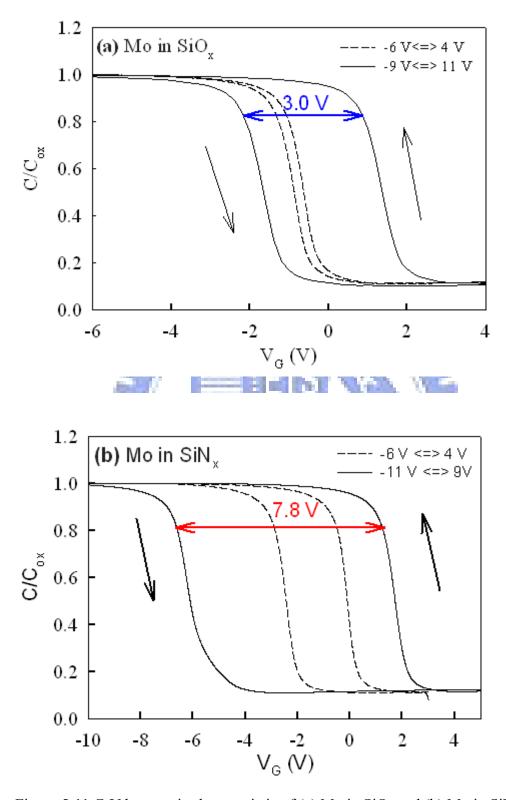

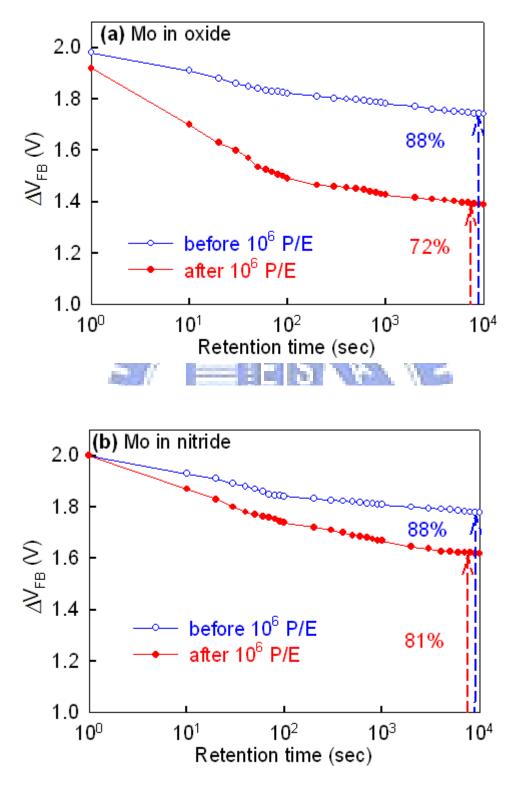

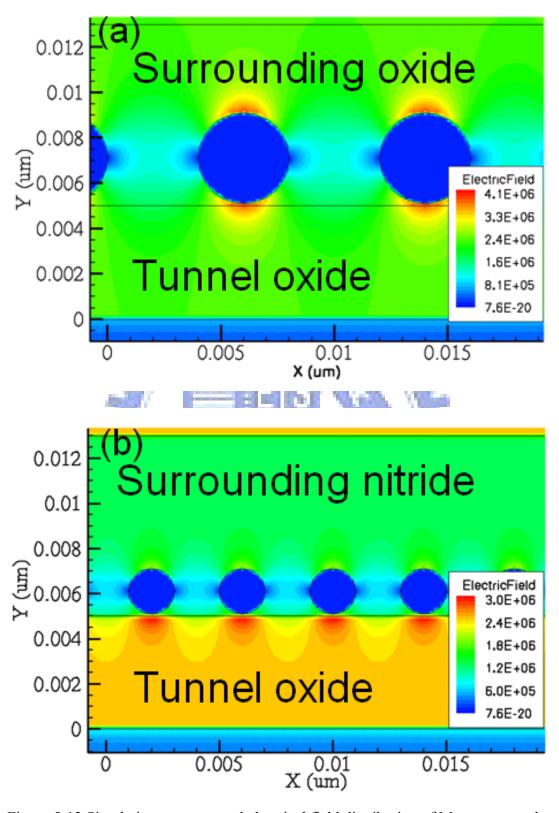

近年來已經發展了許多方法來形成金屬奈米點記憶體,一般而言,大多數的方法都需要長時間的熱退火製程在氣氣的環境下,這個步驟會影響現階段半導體製程中的熱預算和產能且同時造成金屬奈米點過氧化的現像。因此在本論文中,我們使用一個簡單且快速的製程方法來形成金屬鉬奈米點,並將其應用於非揮發性記憶體元件上。我們在氫氣和氧氣(Ar/O<sub>2</sub>)的環境中濺鍍鉬與矽的混合層,藉由熱退火於氮氣環境下來形成奈米點。利用形成氧化物時不同形成能(formation energy)的差異,可以在氦氣快速退火的過程中形成金屬奈米點。同樣的我們也利用此方法濺鍍鉬與矽的混合層在(Ar/N<sub>2</sub>)的環境中,我們發現,高密度(6×10<sup>12</sup> cm<sup>-2</sup>)的鉬金屬奈米點可以被形成於氮化矽(SiN<sub>x</sub>)中,這將有助於解決奈米點記憶體在元件尺寸微縮時可能造成記憶體元件參數變化的問題。最後我們製作雙層鉬奈米點記憶體結構並探討其特性。相較於單層奈米點,我們發現發現多層奈米點不僅在室溫下且在高溫下都擁有較好的電荷儲存能力和保存能力。

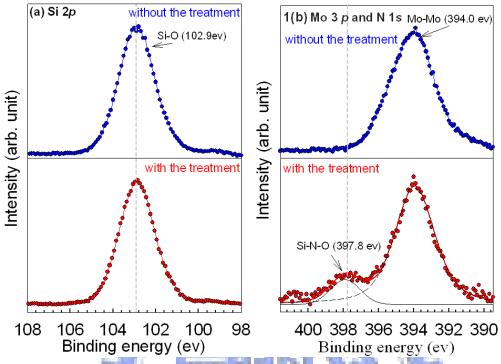

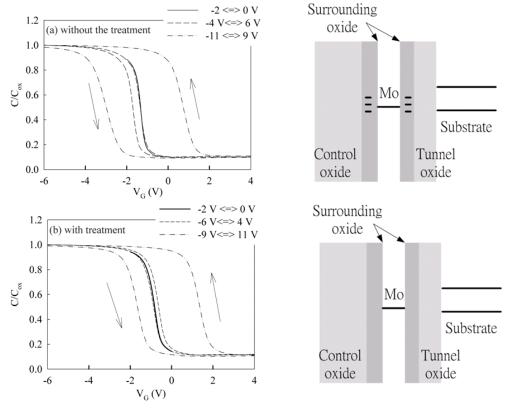

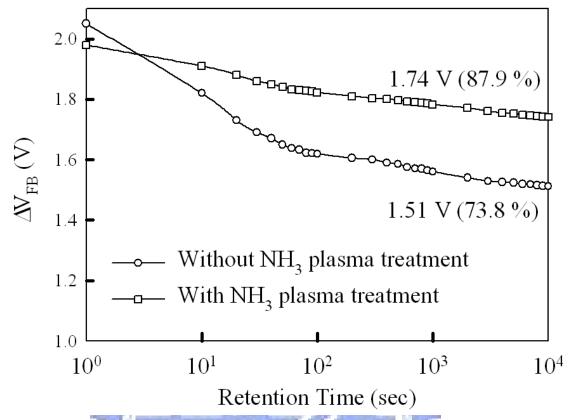

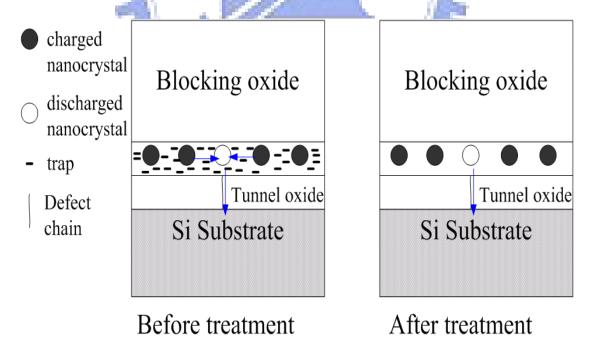

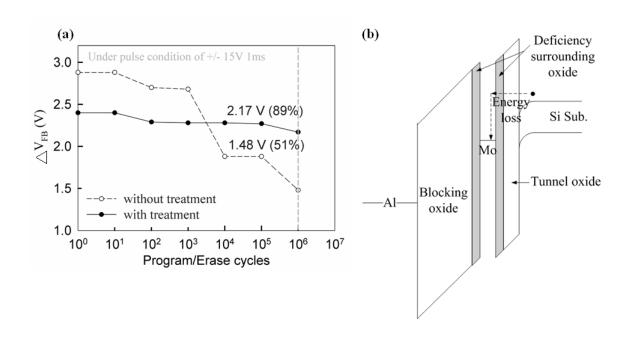

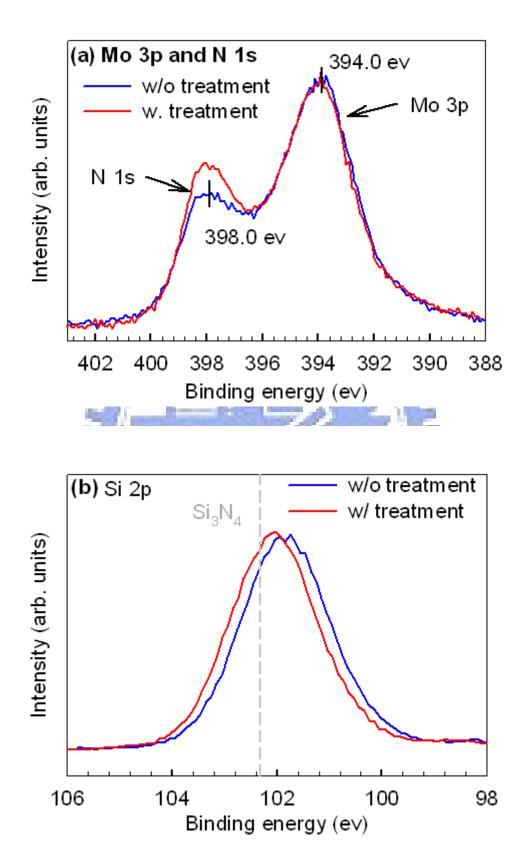

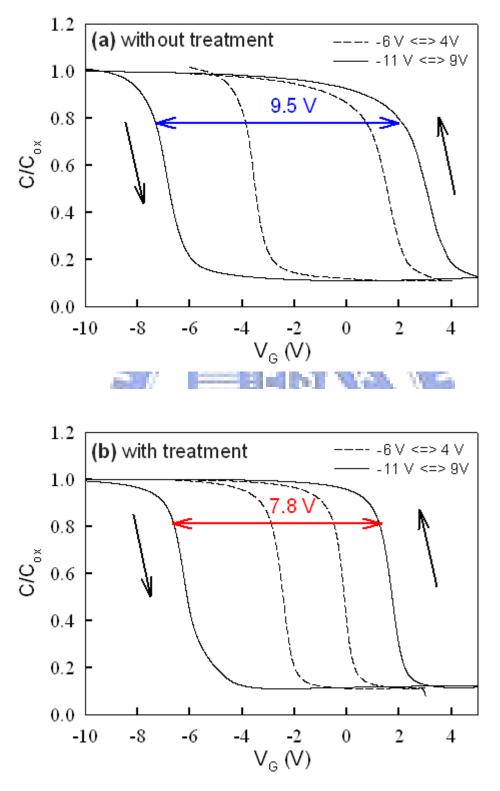

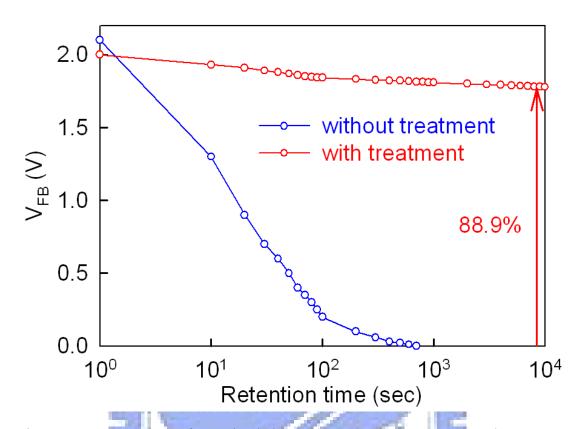

由於許多製作奈米點的方法,諸如離子佈植法(ion implantation)、氧化方法 (oxidation)與濺鍍法(sputtering)等都可能在形成奈米點的過程中造成奈米點周遭的介電質受到損害而影響記憶體的特性。因此,我們提出氨(NH<sub>3</sub>)電漿處理技術來改善奈米點周遭介電質的品質,以應用於非揮發性奈米點記憶體。氨電漿技術被廣泛的應用於半導體工業,由於它的低溫特性,可以降低製程的熱預算。我們在鉬奈米點嵌入氧化矽與氮化矽的記憶體元件上進行氨電漿的處理,研究中發現藉由氨電漿的處理可以引入氮鍵結於奈米點周遭的介電質。這些氮鍵結可以有效的鈍化介電質中的缺陷,並改善金屬奈米點的記憶體特性。

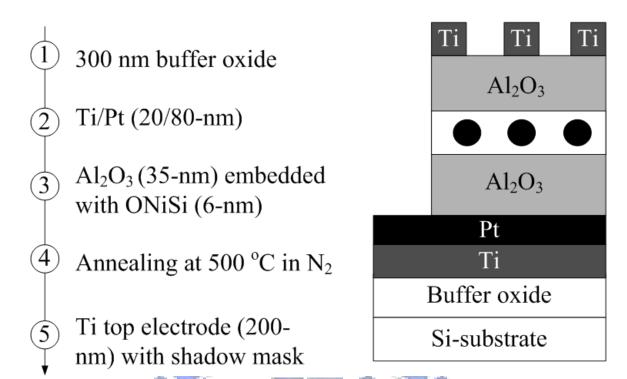

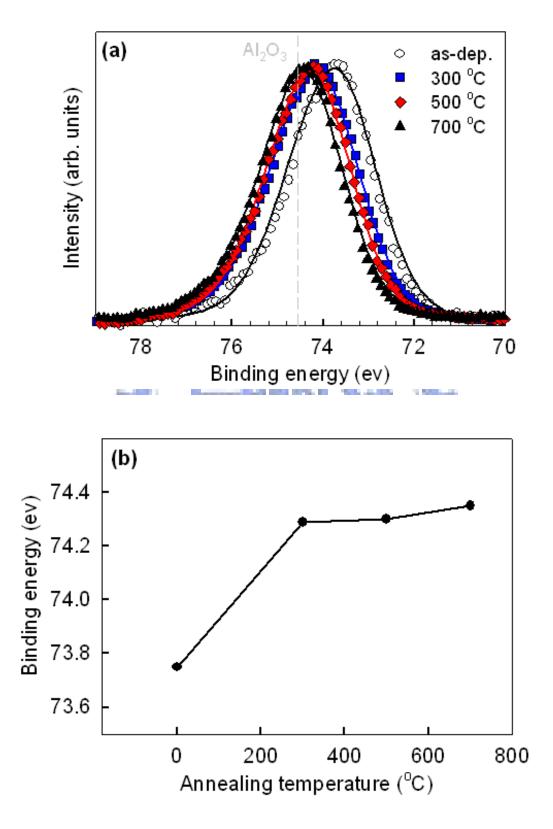

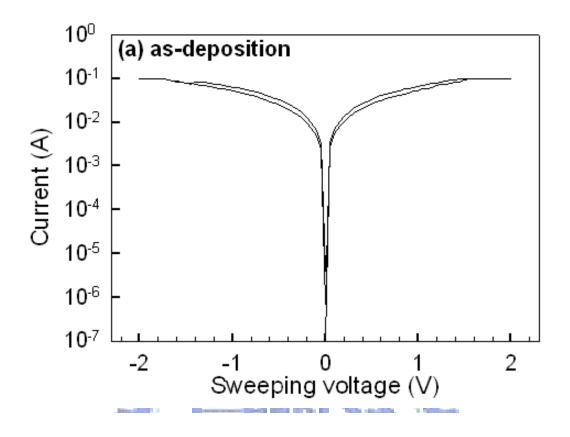

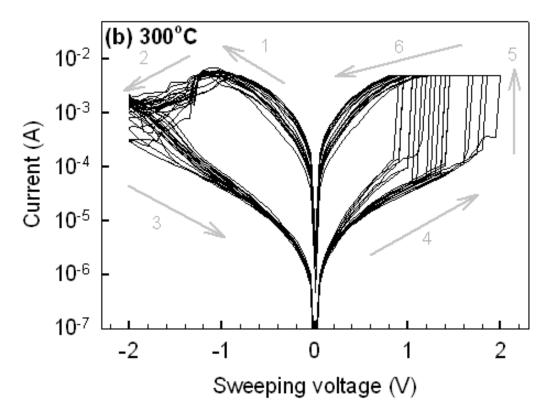

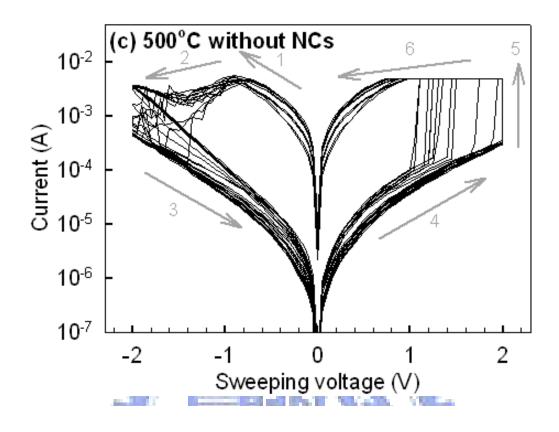

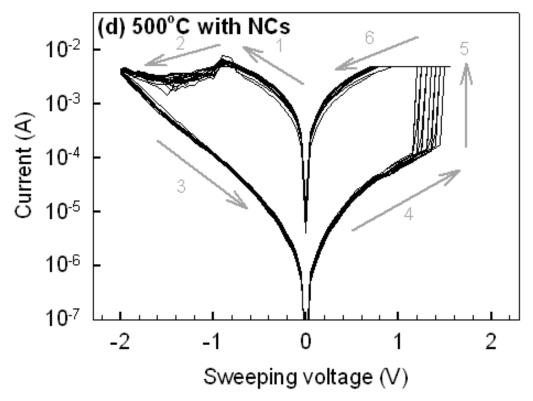

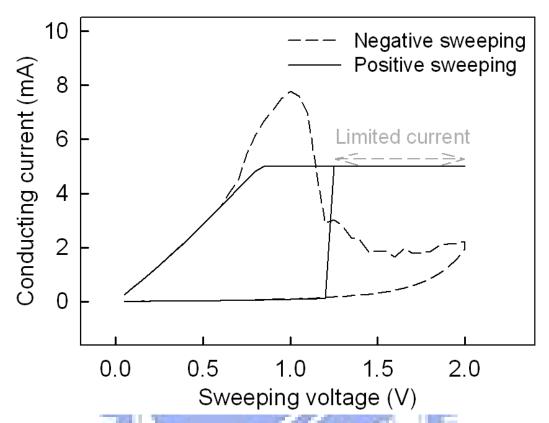

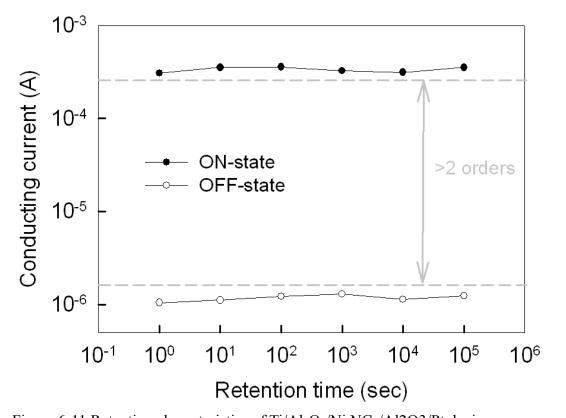

相較於浮閘金屬奈米點非揮發性記憶體,電阻式記憶體被廣泛的研究以期能整合於後段製程。在論文中,我們研究氧化鋁的電阻式記體特性在不同退火溫度下的影響。研究中發現,傳統金屬/絕緣層/金屬 (MIM)結構之電阻式記憶體元件

的特性會有很大的變化與不穩定性,這增加了元件在設計與操作上的複雜度。因此,我們提出金屬/絕緣層/奈米點/絕緣層/金屬的結構來改善電阻式記憶體的特性。實驗的結果發現,電阻式記憶體的電流不管在開啟(ON-state)或者關閉的狀態(OFF-state)會因為金屬奈米點的嵌入而穩定下來。除此之外,由關閉狀態至開啟狀態的起始電壓變化的範圍也會縮小。最後,我們將對我們的研究主題作一總結。

# Fabrication and Electrical Characterization of Advanced Nonvolatile Memories Based on Nanocrystals

Student: Chao-Cheng Lin Advisors: Prof. Tseung-Yuen Tseng

Prof. Ting-Chang Chang

Department of Electronics Engineering and Institute of Electronics

National Chiao Tung University, Hsinchu, Taiwan

#### **Abstract**

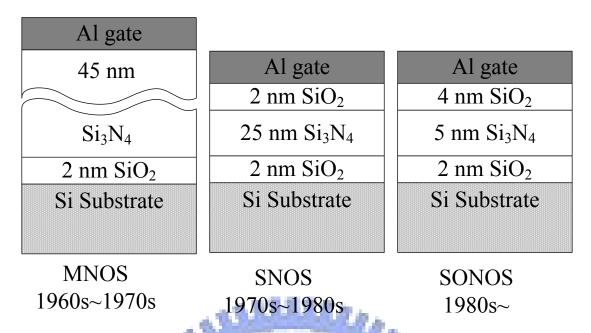

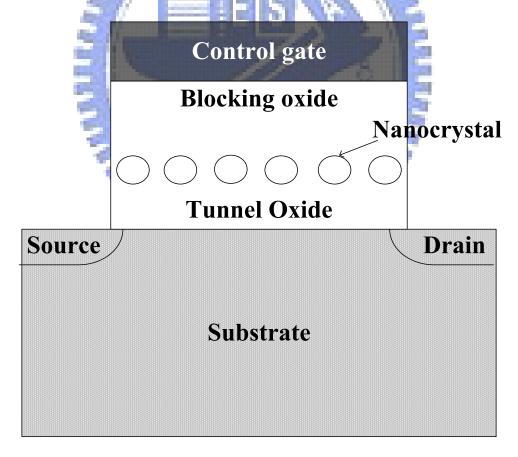

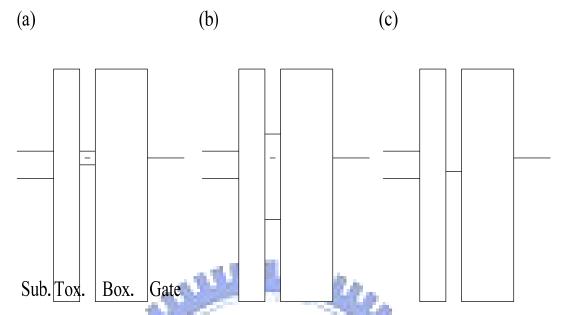

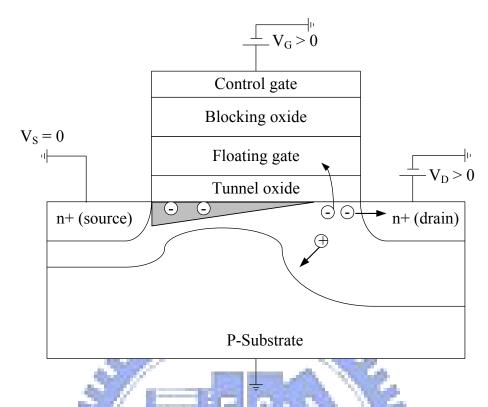

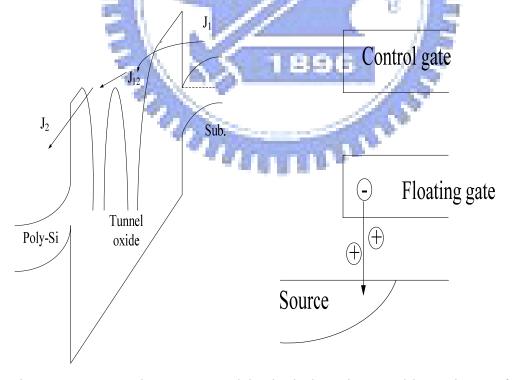

Floating gate composed nonvolatile memories (NVMs) have been widely application in electronic devices in recent years. Requirements of high density, low power consumption and high speed operation drive the memory device scaling down. However, all of the charges stored in the floating gate will leak into the substrate if the tunnel oxide has a leakage path in the conventional NVM during endurance test. Therefore, the tunnel oxide thickness is difficult to scale down without influence of retention and endurance characteristics. Nanocrystals (NCs) NVMs are one of promising candidates to substitute for conventional floating gate memory because the discrete NCs as charge storage centers instead of continuous floating gate can effectively improve data retention for the device scaling down. On the other hand,

resistive switching random access memories (RRAM) have recently received academic and industry's attention for its benefit of high density, high operation speed and simple structure. Furthermore, the fabrication process of RRAM is similar to that of DRAM, and therefore can be easily integrated into back-end process of memory device.

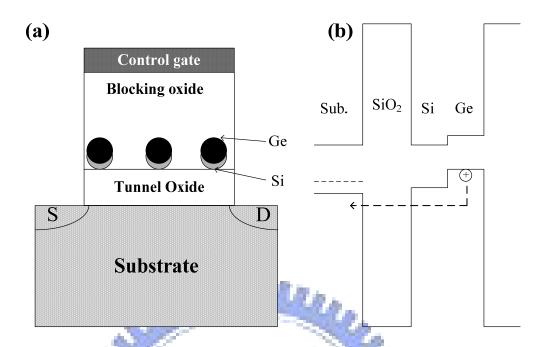

In this thesis, we propose Mo and Mo silicide as material for fabrication of nanocrystal to overcome the limitation in conventional NVMs during the scaling down process. Compared with other materials, Mo-based material has advantages of low cost, high thermal stability and high work function. Furthermore, Mo has been proposed for the metal gate, and is compatible with the MOSFET fabrication process. Besides, for back-end memory process, we embedded nanocrystal in RRAM to reduce variation of memory characteristics of RRAM.

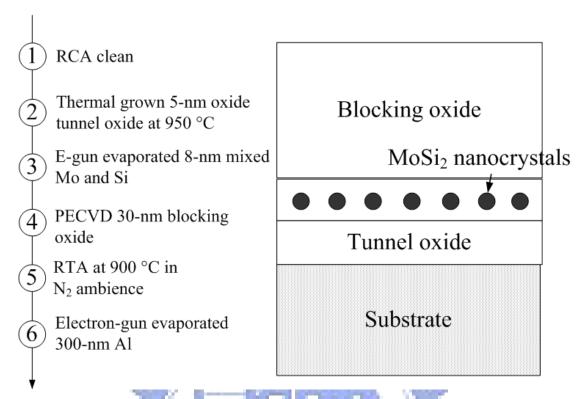

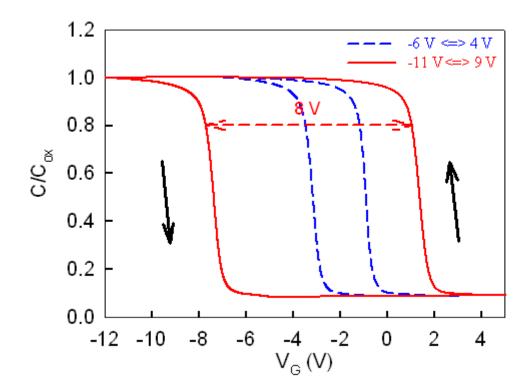

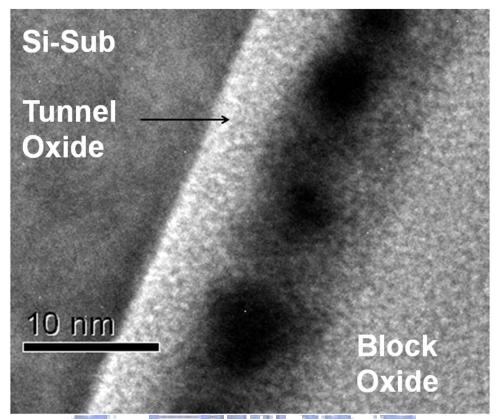

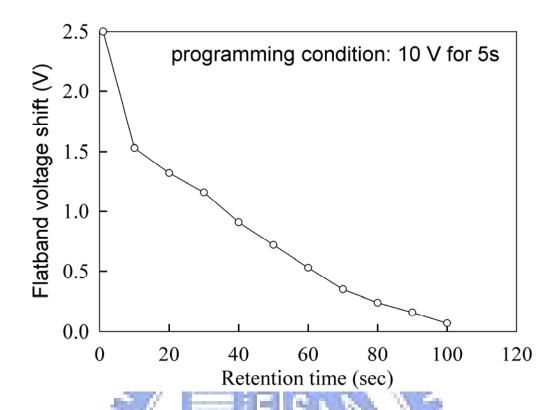

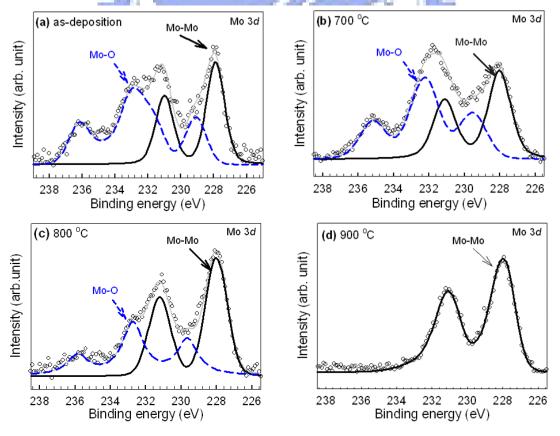

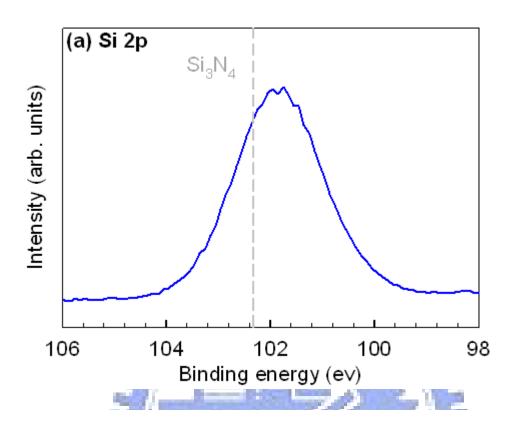

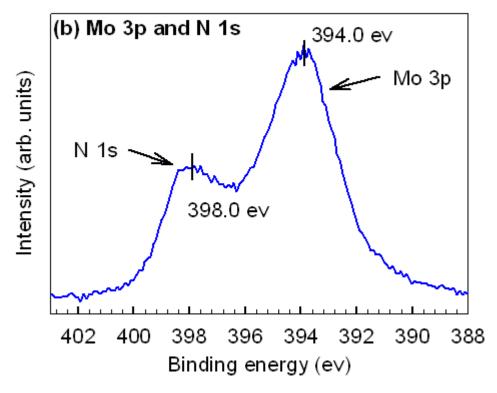

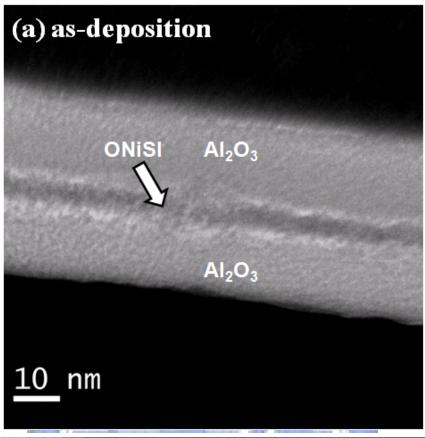

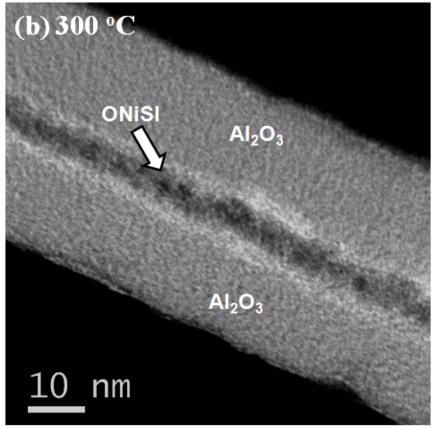

First, we proposed a Mo silicide serving as NCs self-assembling layer for application in NCs NVMs. Mo silicide layer was deposited by dual electron-gun evaporation of Mo and Si pellets at room temperature, and a post annealing was performed to form NCs. In our results, we found that annealing ambience can influence the size, density and composition of NCs. When Mo silicide layer annealing in N<sub>2</sub> ambience, the size of NCs is about 5-nm, and the composition of NCs is dominated by MoSi<sub>2</sub>. However, when annealing in O<sub>2</sub> ambience, Mo oxide NCs was formed and its size is about 20-nm. In addition, we found that a pre-annealing-capping oxide layer is a key process to form Mo oxide NCs.

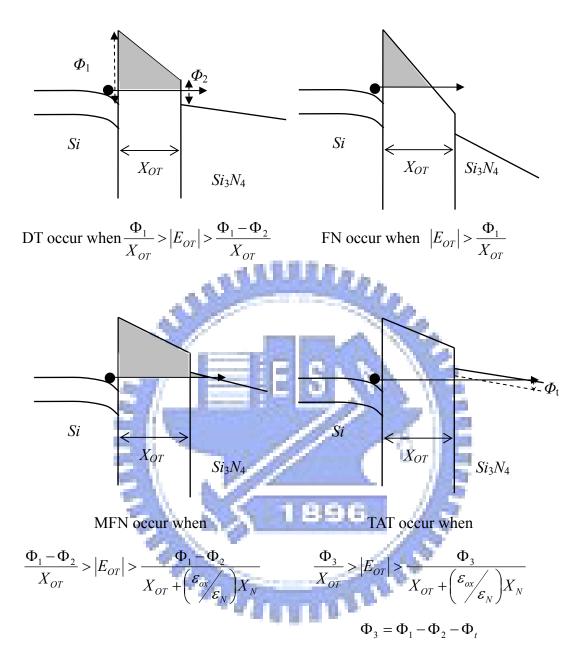

There are many methods have been develop to form nanocrystals for nonvolatile memory application. Most of the methods need long-term annealing in oxygen ambience. This procedure will influence thermal budget and throughput for the current manufacture technology of semiconductor industries. Hence, a simple and fast fabrication technique of Mo NCs was demonstrated for NVM application in this thesis.

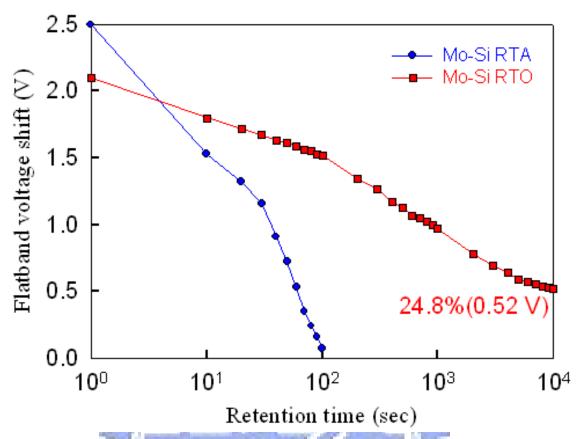

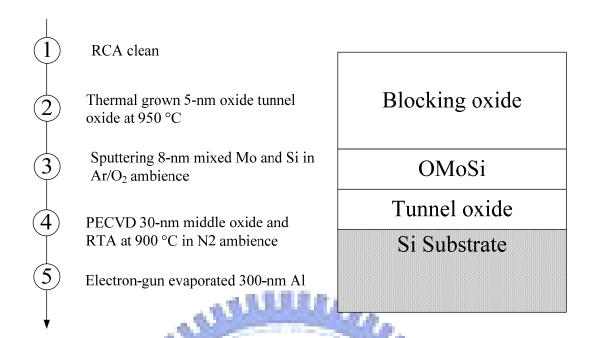

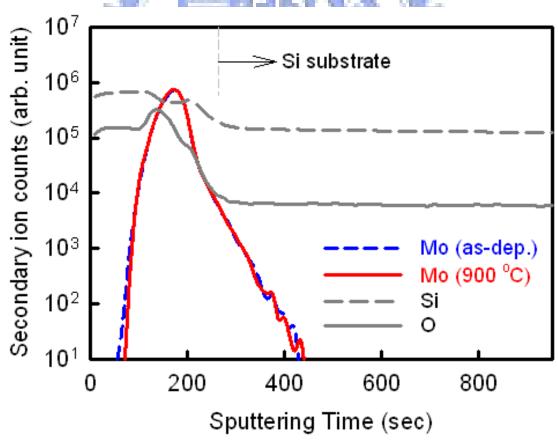

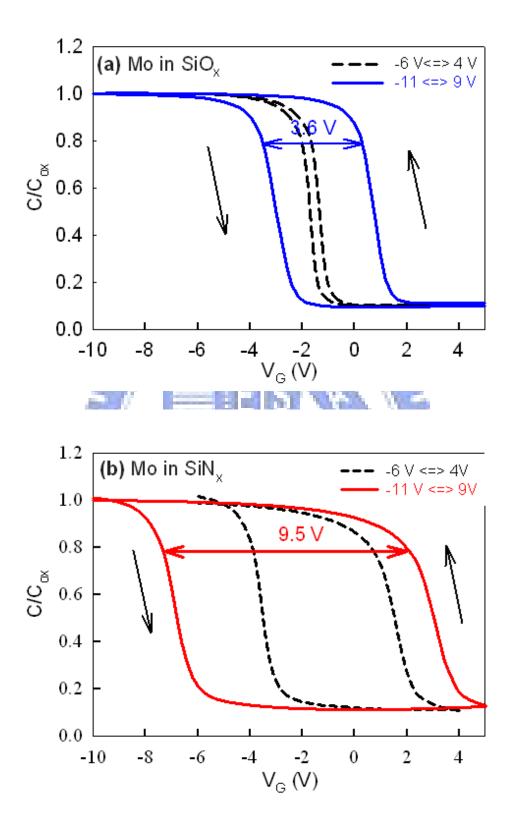

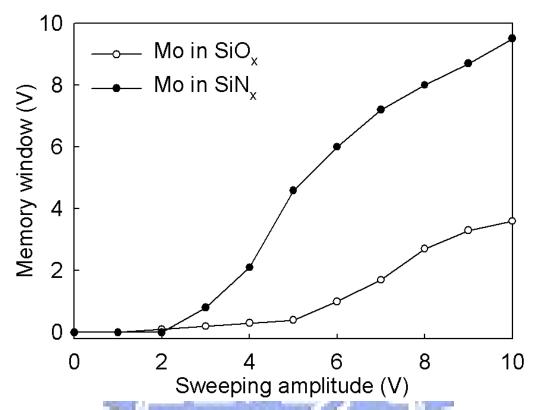

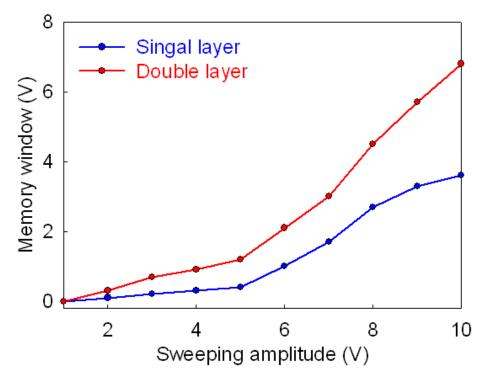

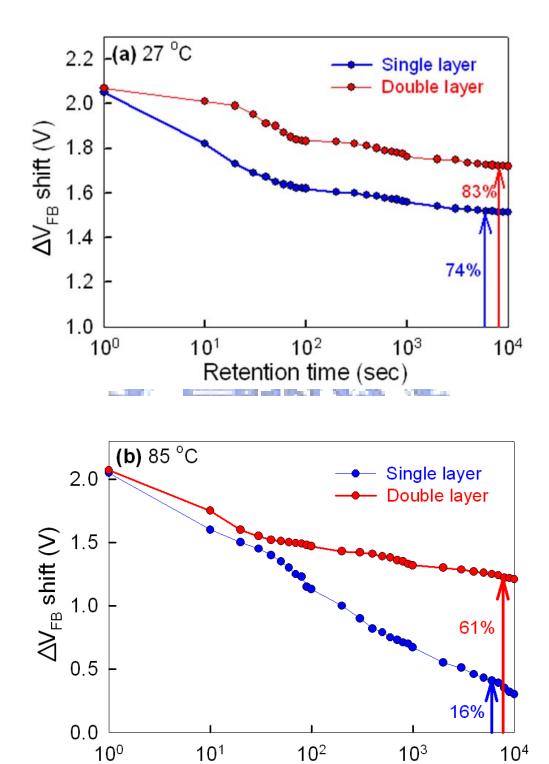

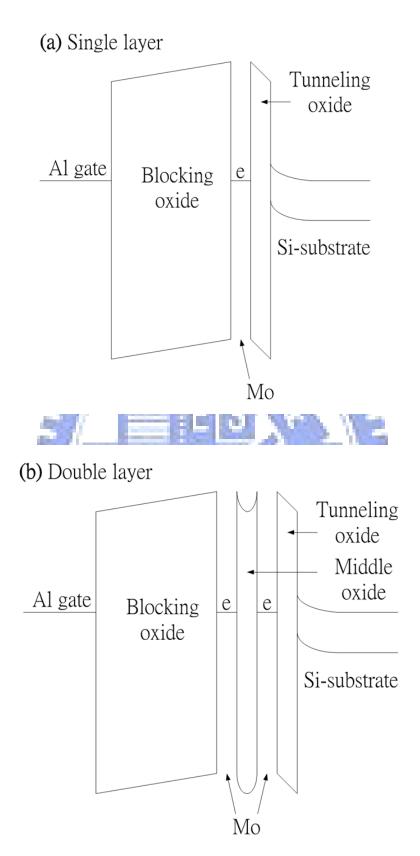

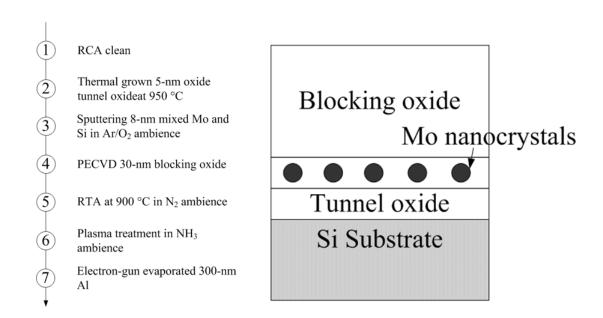

The NVM structure of Mo NCs embedded in the SiO<sub>x</sub> layer was fabricated by annealing Mo silicate, which was deposited by sputtering Mo and Si target in Ar and O<sub>2</sub> ambience. In the formation process, the oxygen plays a critical role for the NCs formation during sputter process. A high density (~10<sup>12</sup> cm<sup>-2</sup>) NCs also can be simply and uniformly fabricated in our study. We also proposed a formation of Mo NCs embedded in SiN<sub>x</sub> by replacing O<sub>2</sub> by N<sub>2</sub> ambience during the sputtering process. A high density Mo NCs was embedded in the silicon nitride (SiNx) which presented larger memory effect. Therefore, by using internal competition mechanism in charge trapping layer for these elements (Mo, Si, and O or N), we can obtain a metallic NCs NVM with low thermal budget process. Besides, double-layer NCs NVM structure was fabricated in this work. We found that double-layer NCs structure has better charge storage and retention over than single-layer one under high temperature test because of Coulomb blockade effect can be reduce by sharing the stored carriers into both the first layer and second NCs layer. Furthermore, carriers stored in the first layer can build-up Coulomb expulsion force to reduce the tunneling probability of carriers stored in the secondary NCs layer.

Many proposed methods for fabrication of NCs such as ion implantation, oxidation and sputtering are expect to induce defect in the dielectric around nanocrystals, and influence charge storage ability of memory device. Therefore, we used a post treatment of ammonia (NH<sub>3</sub>) plasma to improve the quality of the surrounding dielectric. Ammonia plasma treatment has been widely application in semiconductor industry for its low thermal budget. In this work, ammonia plasma treatment was performed on Mo NCs embedded in oxide or nitride. The results indicate that nitrogen bonding can be introduced into surrounding dielectric to passivate defects, and therefore improve the nonvolatile memory characteristics of the memory device.

In addition to floating gate device, we study the resistive switching random access memories (RRAM) for application in back-end nonvolatile memories. Aluminum oxide was employed as resistive switching layer in this work. We found that the variation of resistive switching characteristics in conventional structure, metal/insulator/metal structure, is large. This increases the complexity of designing and operation of the device. Therefore, we proposed metal/ insulator/nanocrystals/ insulator/metal to reduce variation of memory characteristics in RRAM device. In the final part of this dissertation, the conclusion is presented.

Key words: Nanocrystal, Nonvolatile memory, Mo, double layer, RRAM, resistive switching.

### Acknowledgement

歲月如梭,遙想當年進交大時,我仍是個少不經事的研究生,一路以來,碩士班畢業、念博士班、考資格考、做研究、寫論文與實驗室同仁一起生活的日子仍歷歷在眼前,如今六年來的研究生活已經告一段落了。回首這些日子來的點點 滴滴,因為有許多人、事、物的幫助與影響下,才得以完成我的博士生涯。

心中滿是說不盡的感激,因為有母校提供我理想與完整的求學環境與研究設備,讓我得以在研究生活中無所窒礙,盡情發揮。然而身處於這浩瀚無際的知識宇宙之中,我的指導教授曾俊元老師與張鼎張老師猶如日月般引領著我,邁向學術研究的光明之路。我要感謝曾俊元老師,老師淵博的知識付予我在研究上的創造力。在老師身上,學會許多待人處事的道理。老師總能在學生困頓疑惑之際給予學生正面的鼓勵,讓學生能堅持到底,得以完成今日的學業。我要感謝張鼎張老師,每當學生在研究上遭遇困難與問題的瓶頸時,老師總能教導學生如何思考問題以排除困難。總能給予學生一個明確的思考方向,循循善誘,讓學生不會迷失方向與目標。除此之外,老師平時也很親切的關心學生的生活狀況,造就了實驗室和諧的氣氛。

感謝志溢、俊豪、世青、致宏、群傑、文俊與沛勳學長們,有你們無私的經驗傳承,讓我得以順利的步入研究的軌道。感謝鍵賢、俊傑與富凱,有你們的陪伴,讓我在碩士班的生活多采多姿。感謝述穎與聖錡,這本論文是你們辛苦研究的結晶。感謝同學緯仁、立偉與志洋,與你們相互討論中讓我的論文更加精彩。感謝學弟,志瑋、仕承、勝凱、彥廷、睿龍、麗雯、俐婷、貴宇、成能、方方土、勝杰、侑廷、信淵、耀峰、介銘、陽東、宥豪、杜比、信賢、影帝、冠仲、小油條、俊興、松蒔、承幼、永昇、奕全與孟漢帶給我許多的歡樂。

在此特別感謝中山的夥伴們,有書瑋、崎峰、原瑞、柏均、佳盛、敏甄、正 杰、冠張、書慶、漢博與志豪等其他學弟妹,有你們大家的幫忙,我才能有順利 的實驗,來完成這本博士論文。 最後,要感謝我最愛的父母,從小到大給予我健全的教育與生活,讓我衣食無缺,總能在我困頓失意時,提供我最佳的避風港口。有你們的無私的支持,我才能心無旁騖的完成我的學業,謝謝父親與母親。

昭正 夏 2009年7月於新竹交大

## **Contents**

| Chinese Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| English Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IV             |

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | X              |

| Table Captions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | XIII           |

| Figure Captions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | XIV            |

| Chapter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1              |

| The state of the s | _              |

| 1.1.2 Nanocrystal Nonvolatile Memory Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5              |

| 1.1.3 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10             |

| 1.1.2 Nation  1.2 Motivation  1.3 Organization of This Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10             |

| 1.3 Organization of This Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| Chapter 2 Basic Principles of Nonvolatile Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| 2.1 Programming/Erasing mechanisms of nonvolatile memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 18             |

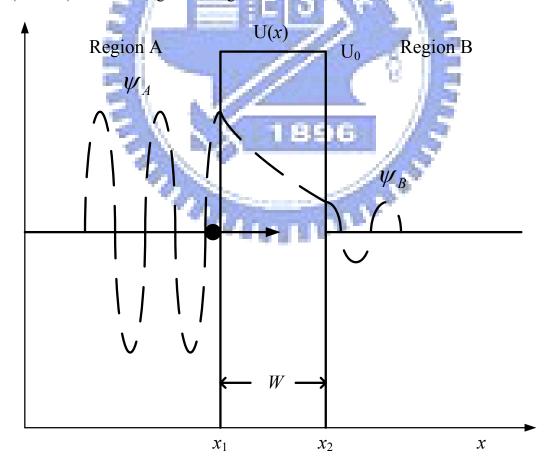

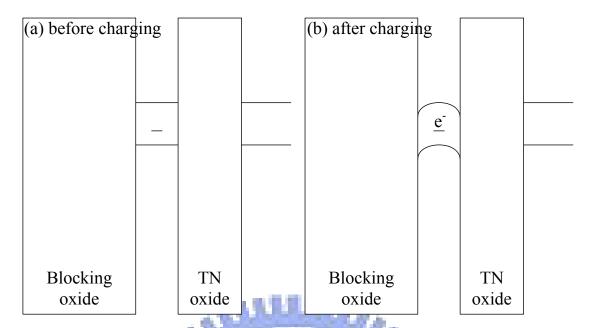

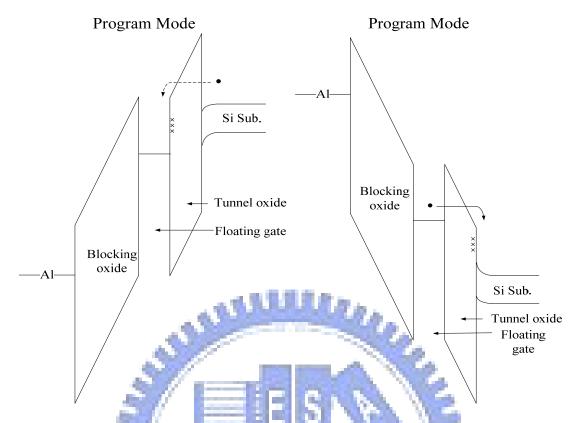

| 2.1.1 Tunneling effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19             |

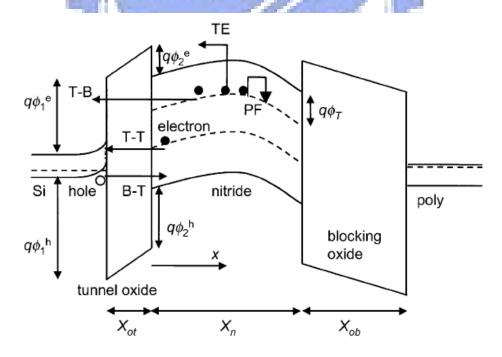

| 2.1.2 Channel Hot-Electron Injection (CHEI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                |

| 2.1.4 Channel Initiated Secondary Electron Injection (CHISEI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                |

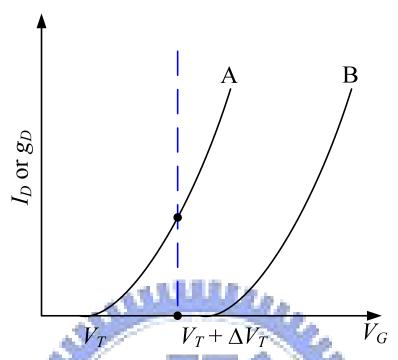

| 2.2 Basic Physical Characteristic of Nanocrystal Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 25             |

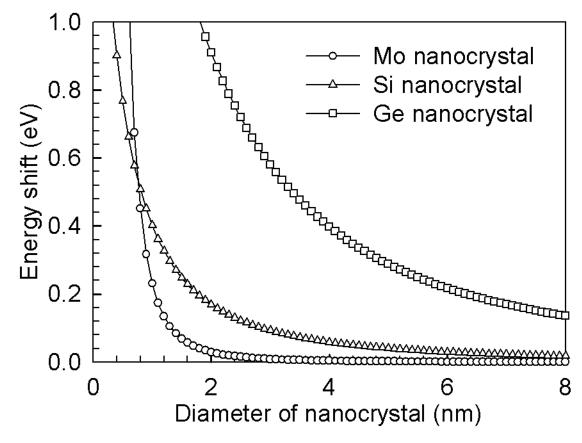

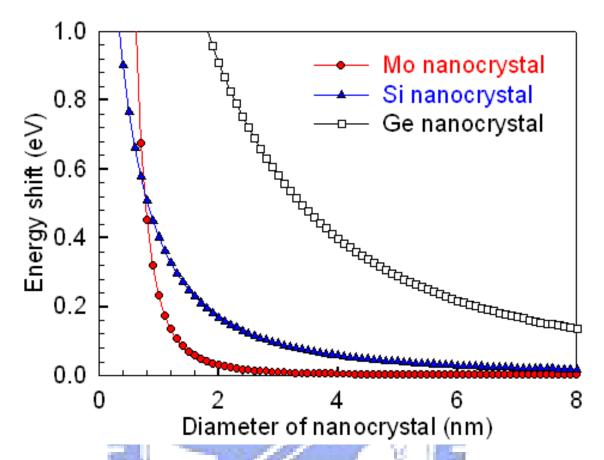

| 2.2.1 Quantum Confinement Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 25             |

| 2.2.2 Coulomb Blockade Effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 26             |

| 2.3 Reliability of Nonvolatile Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                |

| 2.4 Gibbs free energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29             |

| Chantan 2 Malyhdanum hagad nanaanyatal nanyalatila mam                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | a <b>wi</b> aa |

| Chapter 3 Molybdenum-based nanocrystal nonvolatile memo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                |

| 3.1. Formation and memory characteristics of molybednum nanocrystal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| 3.1.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                |

| 3.1.2 Experiment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

| 3.1.3 Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                |

| DITID INDUITED WITH MIDEMEDITOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.1            |

| 3.1.4 Conclusion                                             | 43                |

|--------------------------------------------------------------|-------------------|

| 3.2. Influence of post-annealing ambient on the memory of    | haracteristics of |

| molybdenum-based nanocrystal memory                          | 44                |

| 3.2.1 Introduction                                           |                   |

| 3.2.2 Experiment                                             | 44                |

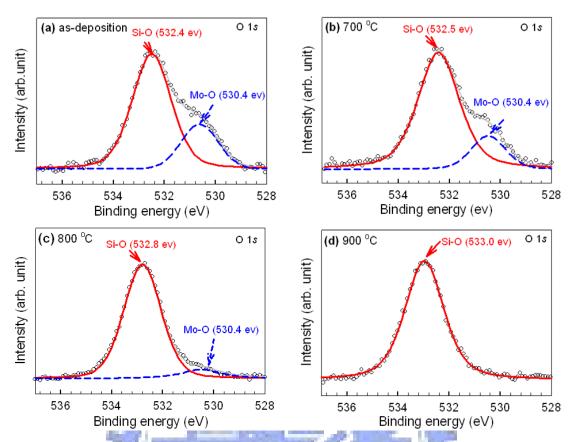

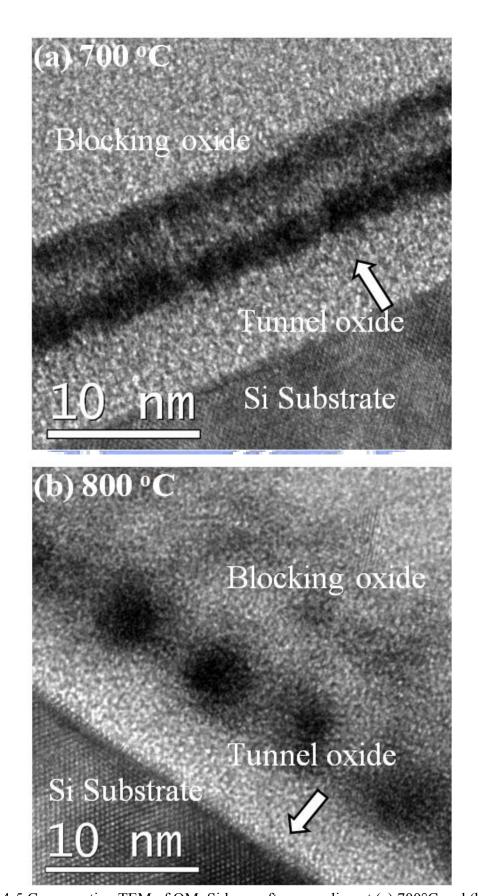

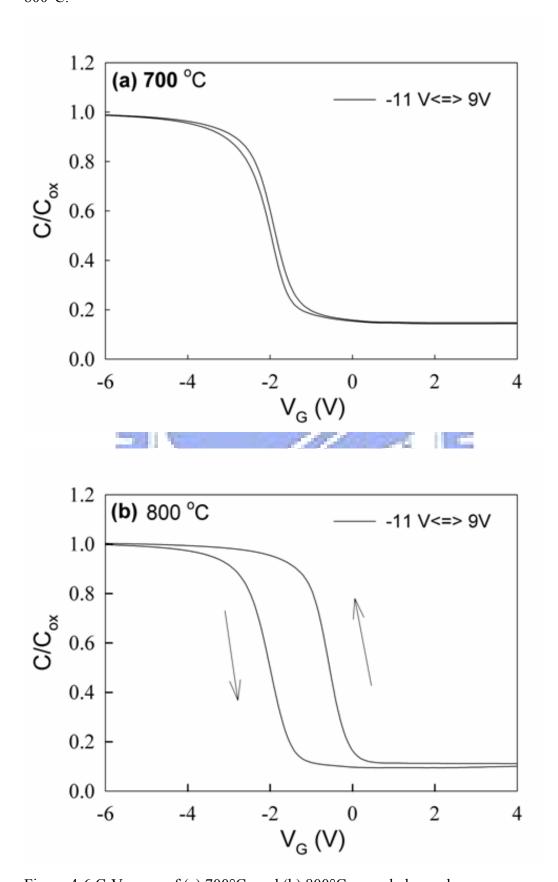

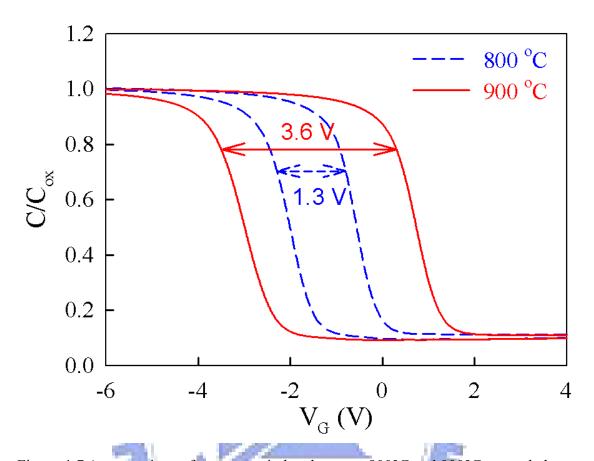

| 3.2.3 Results and discussion                                 | 45                |

| 3.2.4 Conclusion                                             | 48                |

|                                                              |                   |

| Chapter 4 Memory characteristics of Mo nanocrystal           | embedded in       |

| silicon oxide and silicon nitride                            |                   |

| 4.1 Formation and memory characteristics of Mo nanocrys      | tal embedded in   |

| silicon oxide                                                | 59                |

| 4.1.1 Introduction                                           | 59                |

| 4.1.2 Experiment                                             | 60                |

| 4.1.3 Results and discussion                                 | 61                |

| 4.1.4 Conclusion                                             | 64                |

| 4.2 Formation and memory characteristics of Mo nanocrys      | tal embedded in   |

| silicon nitride                                              | 64                |

| silicon nitride                                              | <b>6</b> 4        |

| COST CONTRACTOR OF CONTRACTOR OF COST                        |                   |

| 4.2.2 Experiment                                             | 66                |

| 4.2.4 Conclusion                                             | 67                |

| 4.3 Enhancement of Charge Storage Ability of Double la       |                   |

| memory structure of Mo embedded in oxide                     | 68                |

| 4.3.1 Introduction                                           | 68                |

| 4.3.2 Experiment                                             | 69                |

| 4.3.1 Introduction                                           | 69                |

| 4.3.4 Conclusion                                             |                   |

|                                                              |                   |

| <b>Chapter 5</b> Memory characteristics of Mo nanocrystal    | influenced by     |

| ammonia plasma treatment                                     | J                 |

| 5.1. Charge storage characteristics of Mo nanocrystal memory | ry influenced by  |

| ammonia plasma treatment                                     | 88                |

| 5.2.1 Introduction                                           |                   |

| 5.1.2 Experiment                                             | 89                |

| 5.1.3 Results and discussion                                 |                   |

| 5.1.4 Conclusion                                             | 93                |

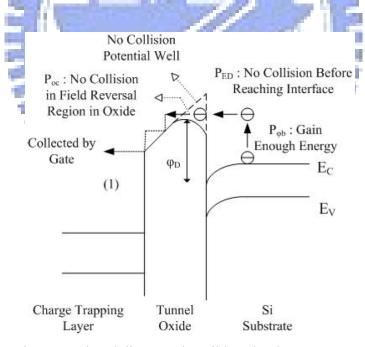

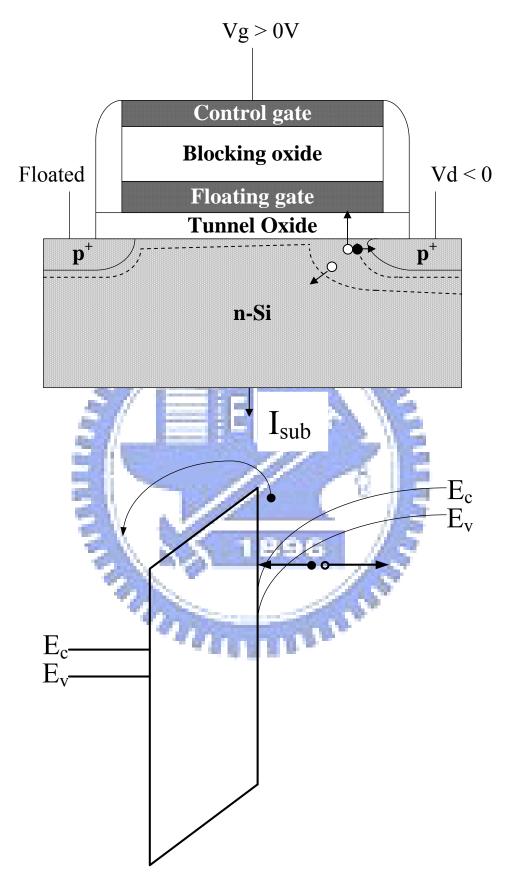

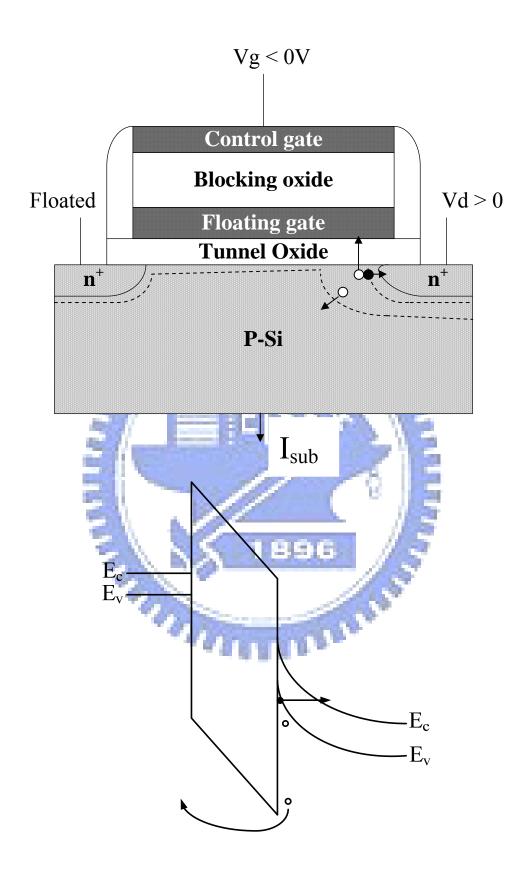

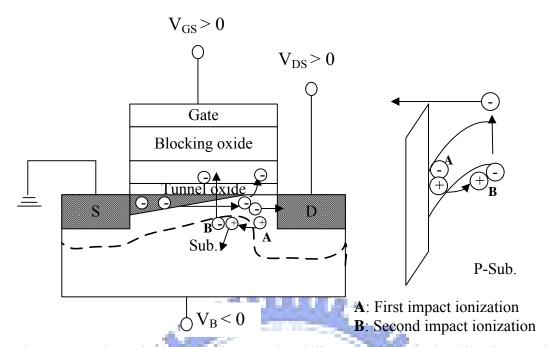

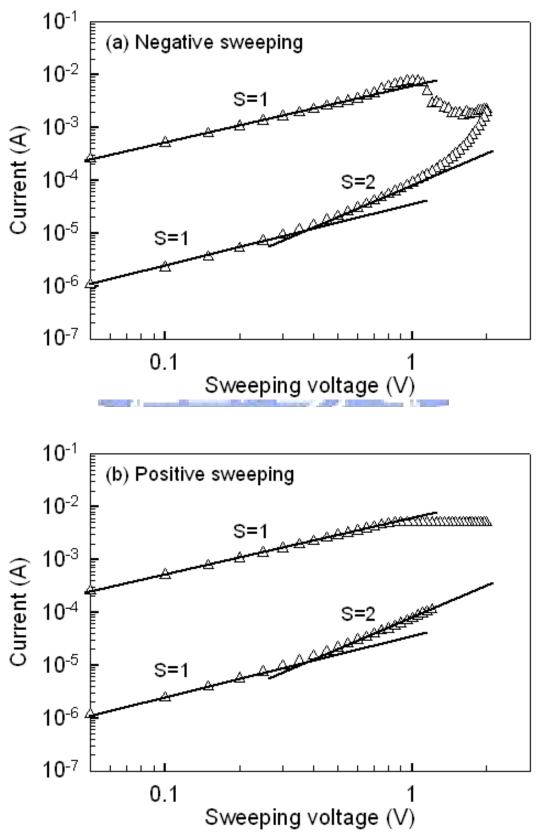

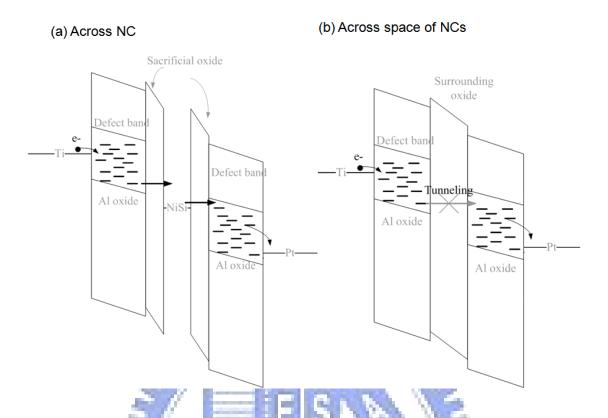

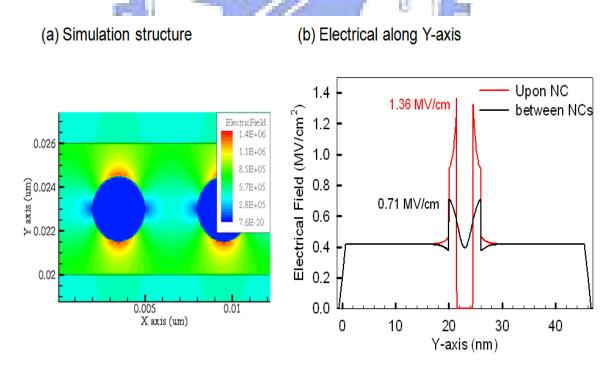

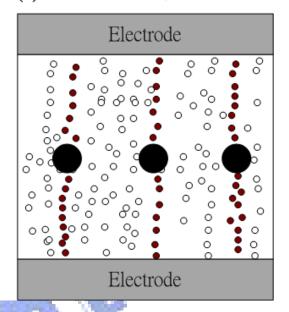

| 5.2. Influence of ammonia plasma treatment on the memory ch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | iaracteristics of |