# 國立交通大學電子工程學系電子研究所博士論文

# 互補式金氧半電晶體之金屬閘極材料與技術研究 A Study on the Metal Gate Materials and Technology for the CMOS Application

研究生: 黃誌鋒

指導教授 : 崔秉鉞 博士

中華民國 九十五 年 十 月

#### 互補式金氧半電晶體之金屬閘極材料與技術研究

# A Study on the Metal Gate Materials and Technology for the CMOS Application

研究生: 黃誌鋒 Student: Chih-Feng Huang

指導教授: 崔秉鉞 博士 Advisor: Dr. Bing-Yue Tsui

國立交通大學 電子工程學系 電子研究所 博士論文 A Dissertation

Submitted to Department of Electronics Engineering and Institute of Electronics

College of Electrical Engineering and Computer Science

National Chiao-Tung University

In Partial Fulfillment of the Requirements

for the Degree of

Doctor of Philosophy

in Electronics Engineering

2006

Hsinchu, Taiwan, Republic of China

中華民國 九十五 年 十 月

## 互補式金氧半電晶體之金屬閘極材料與技術研究

研究生: 黃誌鋒 指導教授: 崔秉鉞 博士

#### 國立交通大學

#### 電子工程學系電子研究所

#### 摘要

互補式金氧半電晶體(CMOS)進化至 45 奈米技術後,多晶矽閘極將遭遇其物理限制-多晶矽空乏、硼穿透和高電阻係數,尋找多晶矽閘極替代物變得更為迫切,解決這些物理限制,金屬閘極是一明確的選擇。整合金屬閘極於互補式金氧半電晶體將帶來新的挑戰,金屬閘極的採用需要提供元件有更好的效能與令人滿意的可靠度且金屬閘極須有適當的有效功函數(work function)使元件有適當的起始電壓(threshold voltage),本論文中,吾人將探討數種金屬閘極材料區分為金屬氮化物,二元金屬合金與全金屬矽化閘極。

首先,吾人將探討氮化鉬(MoN<sub>x</sub>)閘極,利用反應式濺鍍沉積氮化鉬薄膜,其 氮含量原子百分比為 46-59,主要晶相為 MoN,隨著氮含量的增加,其微結構趨 近非結晶且阻值增加,氮化鉬有效功函數亦隨氮含量增加且逐漸飽和於矽價帶, 在氧化鉿(HfO<sub>2</sub>)上沒有費米栓(Fermi-level pinning)效應,結果顯示氮化鉬閘極是 p-型金氧半場效電晶體很好的選擇。 其次,另一耐火金屬鷂經氮化後調變有效功函數,氮化鷂含氮元素高於原子百分比 44 其晶相為 WN 且此晶相穩定度高達 800 °C,縱使氮濃度高達原子百分比 61,並無更高晶相產生。氮化鷂中過多的氮元素在溫度低於 766 °C 便會析出,且 過多的氮會導致氮化鷂有效功函數下降,在氧化鉿上會有輕微的費米栓效應,這種情形下,氮化鷂可應用於 p-型全空乏絕緣層上矽(SOI)金氧半場效電晶體元件,但不適合當塊材(bulk) p-型金氧半場效電晶體閘極。

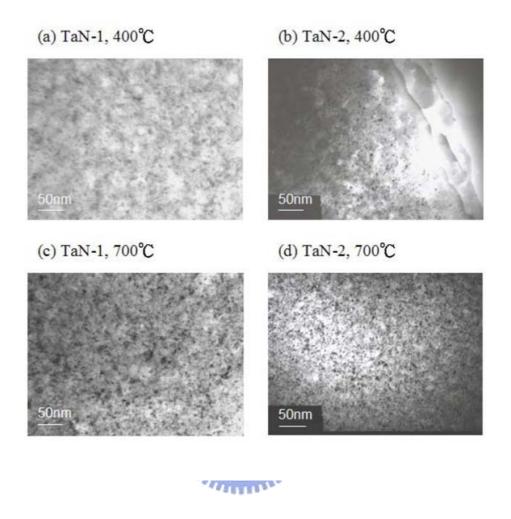

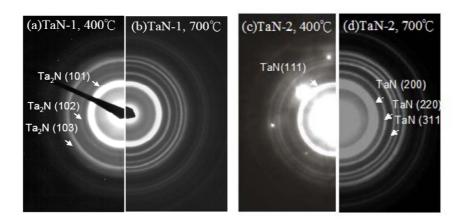

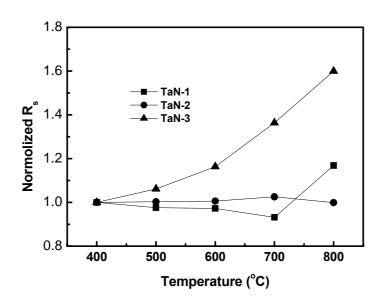

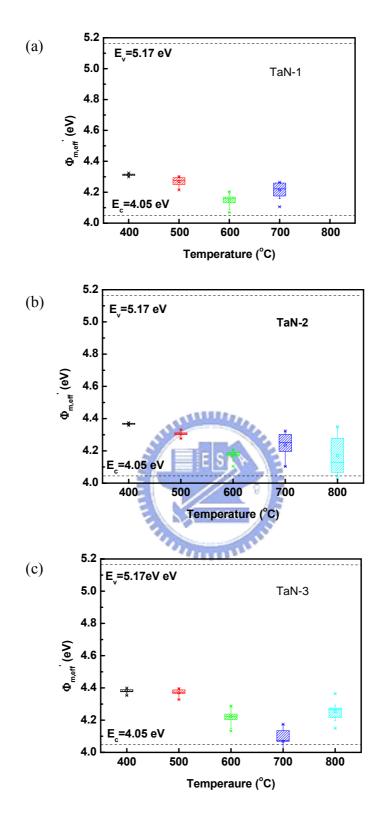

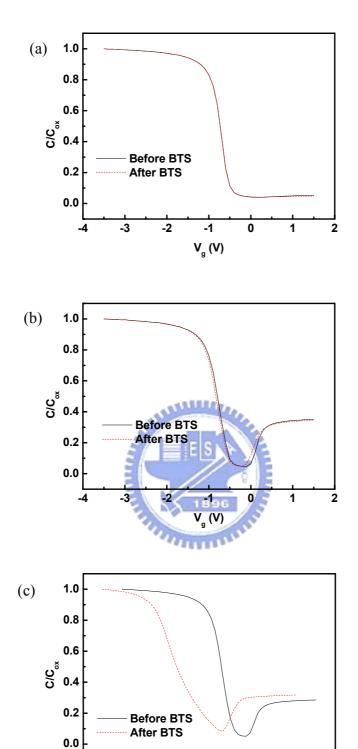

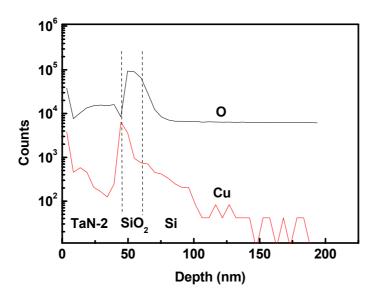

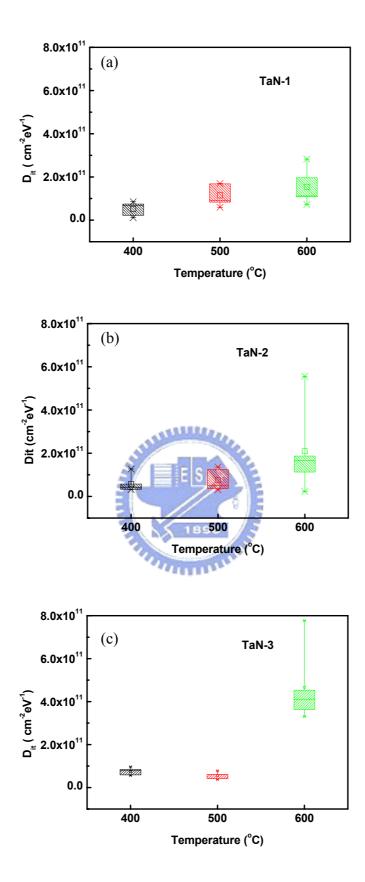

金屬氮化物的高阻值迫使吾人思考堆疊(stack)結構當閘極,探討銅/氮化鉭(Cu/TaN<sub>x</sub>)堆疊,其中低電阻值層(銅層)適合當主要的導電材料,底層(氮化鉭層)用以當起始電壓控制材料。氮化鉭中氮含量原子百分比為 23-39,且薄膜幾乎為非晶結構,熱穩定度高達 800°C,氮化鉭的有效功函數約為 4.31-4.38 eV,氮成分調變有效功函數能力低於 70 meV,元件平帶電壓均值隨著溫度增高而下降且平帶電壓標準差增大,雖然在高溫時晶相變化、晶粒成長與銅污染會貢獻平帶電壓不穩定性,在 600°C 熱應力致氧化層電荷主導平帶電壓下降與標準差,銅/氮化鉭堆疊閘極可使用於 n-型金氧半場效電晶體銅/氮化鉭,其製程最高溫度需控制在 500°C.

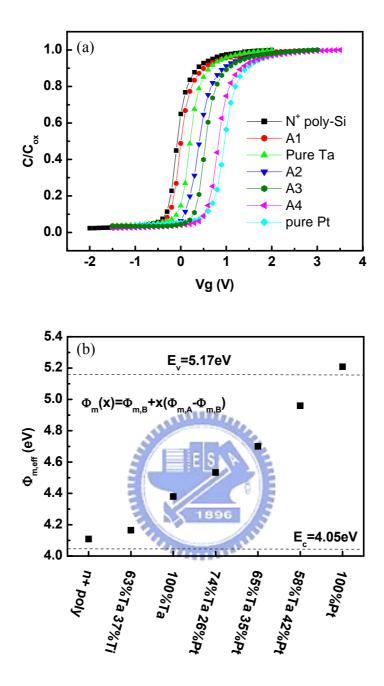

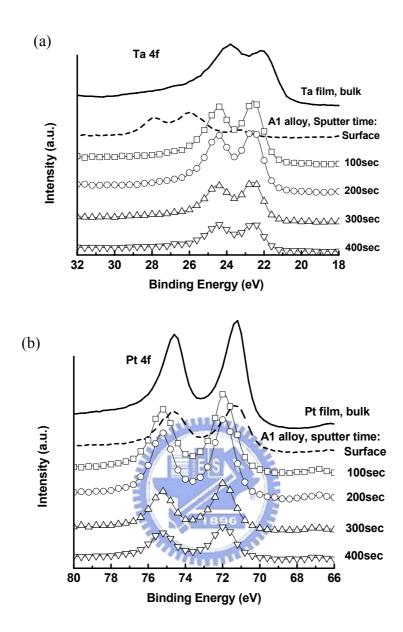

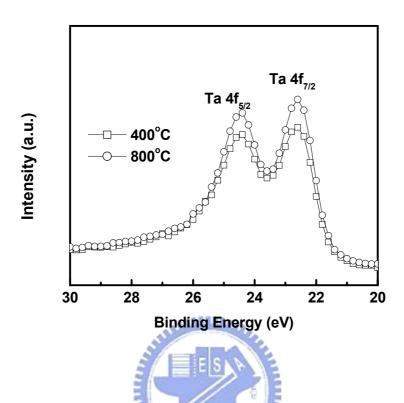

雖然金屬氮化物具高溫熱穩定性,但其有效功函數範圍並不夠大,吾人展示一種有效的功函數調變方法,利用二元金屬合金而非金屬半化物,選擇適當的金屬成分與組成,可獲得任意功函數之二元金屬合金。調變鉭基材合金(鉭-鈦和鉭-鉑)其有效功函數可連續分部於 4.16-5.2 eV ,如此大範圍功函數使得該金屬合金適用於互補式金氧半場效電晶體,鉭與鉑經混合後,其核心電子束縛能改變,佐證合金功函數可依金屬合金系統調整,而且鉭膜中混合鉑元素會造成結晶變差且形成合金晶相,經參透式電子顯微鏡確認鉭-鉑合金薄膜中晶粒為奈米尺寸。

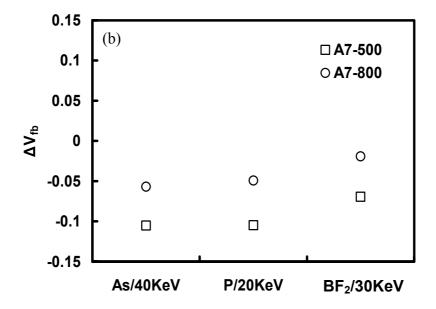

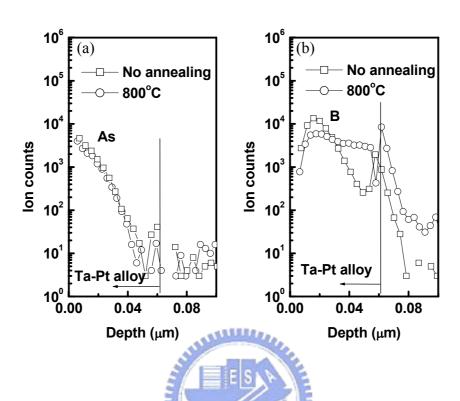

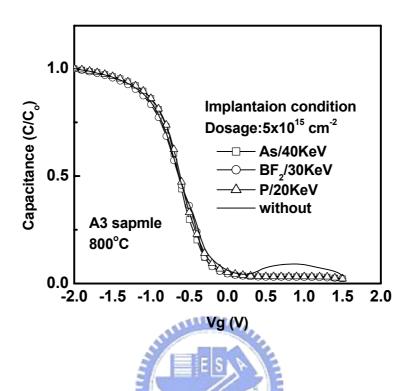

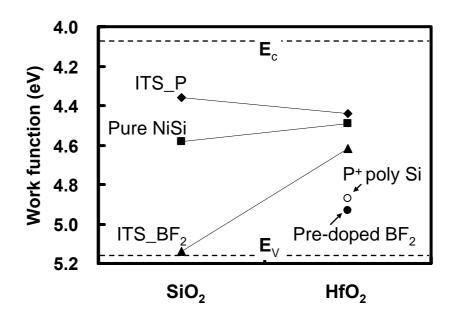

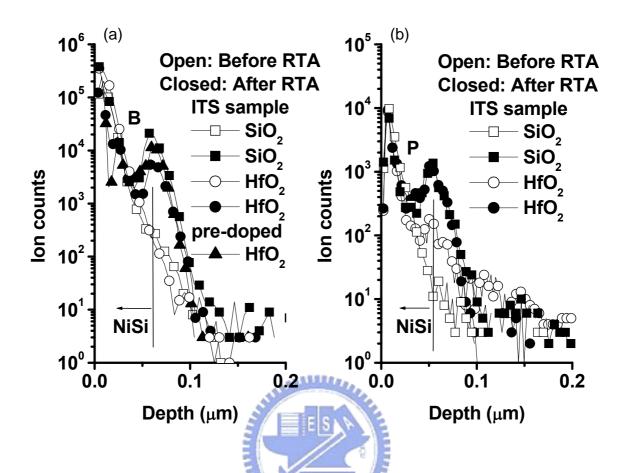

最後,一種新方法(雜質植入矽化物)用以實現全金屬矽化閘極有效功函數調

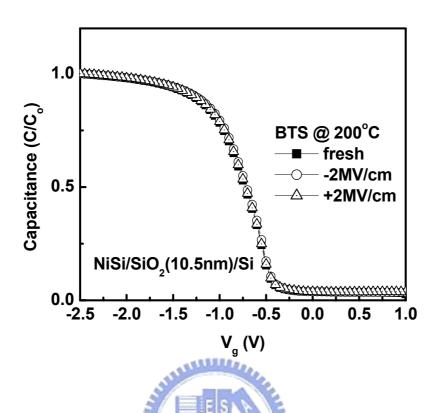

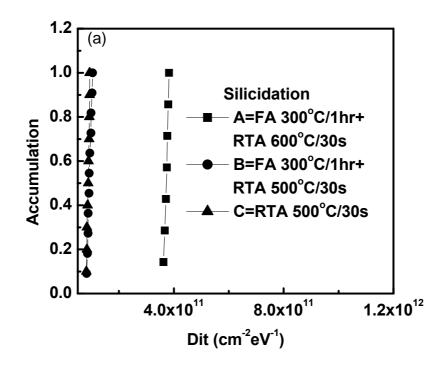

變,全金屬矽化閘極容易整合於傳統金氧半場效電晶體製程,且利用雜質推積於全矽化物與底層絕緣材料介面,擁有大範圍的有效功函數調變。半導體矽經全金屬矽化後,植入  $BF^{\dagger}$ 與  $P^{\dagger}$ 雜質接著作退火可有效調變全金屬矽化閘極功函數。但當底層絕緣層材料為氧化鉿,會產生費米栓效應,限制功函數調變,一層薄的二氧化矽介面層可減緩費米栓效應。雖然矽化鎳全矽化閘極在二氧化矽尚可穩定到 $600\,^{\circ}$ C,但長時間處於 $600\,^{\circ}$ C,熱應力與雜質擴散會導致氧化層劣化,全矽化後製程溫度建議低於 $500\,^{\circ}$ C 以緩和氧化層劣化。

總結,金屬氮化物由於功函數調變範圍過小,僅能使用於雙金屬閘極組合,儘管金屬合金擁有大範圍的功函數,但很難利用單一金屬閘極製程整合不同成份合金於互補式金氧半電晶體,經 N-型與 P-型參雜全金屬矽化閘極製程最有可能符合單金屬雙功函數組合,但金屬矽化前多晶矽與高介電材料反應產生費米栓效應限制了運用全金屬矽化閘極,到目前為止並沒有完美的金屬閘極材料與製程供選擇,標準互補式金氧半電晶體金屬閘極製程尚須詳細考慮雙金屬閘極或金屬全矽化閘極。

A study on the Metal Gate Materials and

**Technology for the CMOS Application**

**Student: Chih-Feng Huang**

**Advisor: Dr. Bing-Yue Tsui**

**Department of Electronics Engineering & Institute of Electronics**

**National Chiao-Tung University**

**Abstract**

As the evolution of the CMOS technology beyond the 45 nm technology node,

poly-silicon gate encounters several inherent limitations – poly-Si depletion, boron

penetration, and high resistivity. It becomes urgent to seek replacements for the

poly-silicon gate. Metal gate is an obvious choice to solve all of the limitations.

However, to integrate metal gates with CMOS process faces new process challenges.

The introduction of metal gates should provide devices better performance and

competent reliability, and the metal gates should have proper work functions to make

devices meet suitable threshold voltages. In this dissertation, several metal gate

materials including metal nitrides, binary metal alloys, and fully silicided gates were

investigatred.

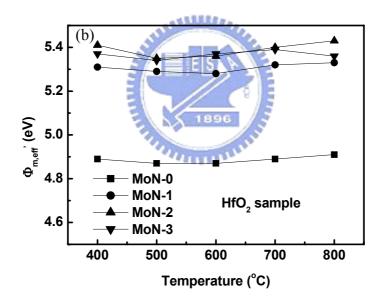

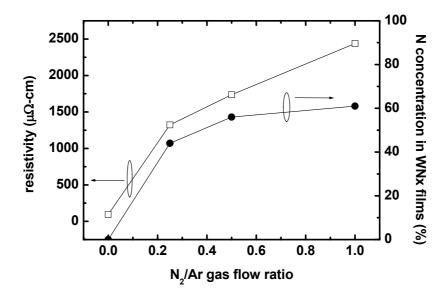

The MoN<sub>x</sub> gates were studied at first. The main phase of the MoN<sub>x</sub> films with the 46 -

59 at. % of nitrogen is MoN. As the N/Mo ratio increases, the microstructure of MoN<sub>x</sub>

film tends to be amorphous-like and the resistivity increases. The work function of MoN<sub>x</sub>

iv

increases with the increase of nitrogen content and tends to saturate at the valence band of Si. No Fermi-level pinning effect is observed on HfO<sub>2</sub> film. These results indicate that MoN is a good candidate of gate electrode for PMOSFETs.

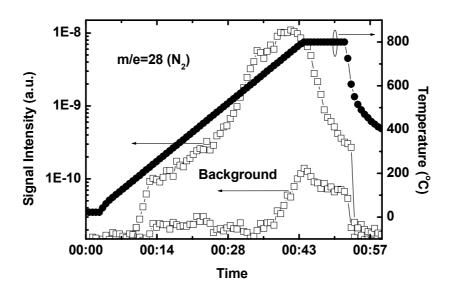

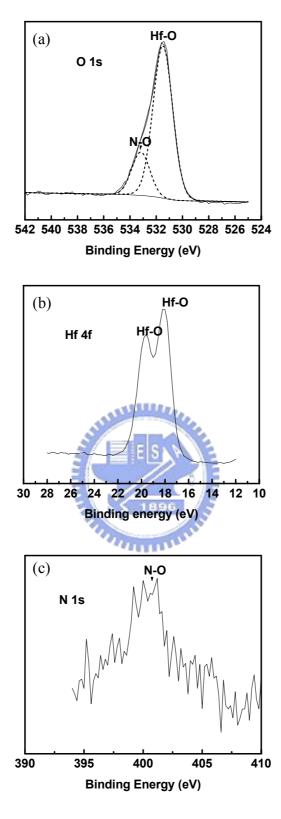

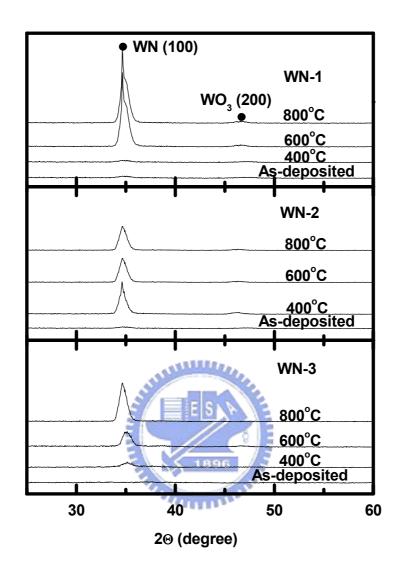

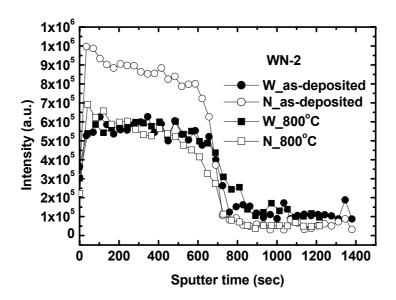

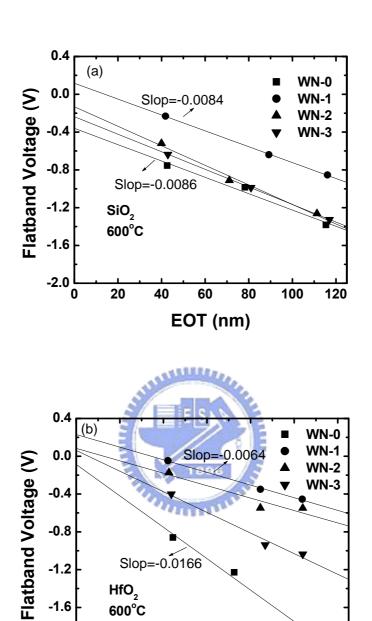

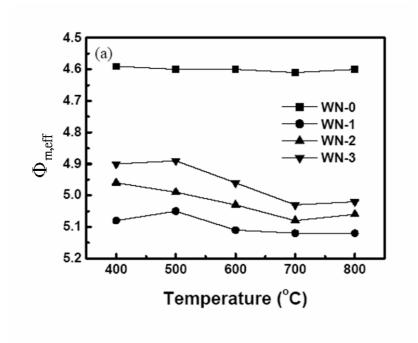

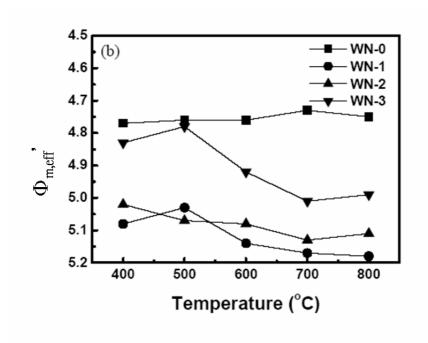

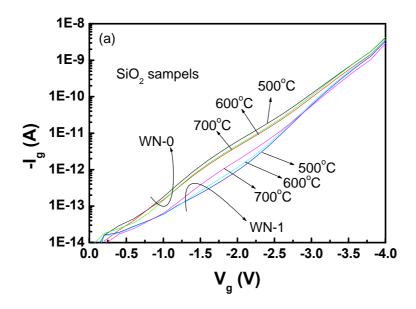

The WN<sub>x</sub> films with nitrogen higher than 44 % atomic ratio has a main phase of WN, and the WN phase is stable up to 800 °C. The higher order WN<sub>x</sub> phase does not form even if the nitrogen concentration is as high as 61%. The excess nitrogen atoms in WN<sub>x</sub> films desorbs at temperatures below 766 °C. The excess nitrogen in WN<sub>x</sub> films can cause the effective work function lowering. Weak Fermi-level pinning effect is observed on  $HfO_2$  film. In this case, WN<sub>x</sub>/HfO<sub>2</sub> gate stack can be applied to p-type fully-depletion SOI devices but WN<sub>x</sub> is not suitable to be meal gate of bulk p-type MOSFTEs.

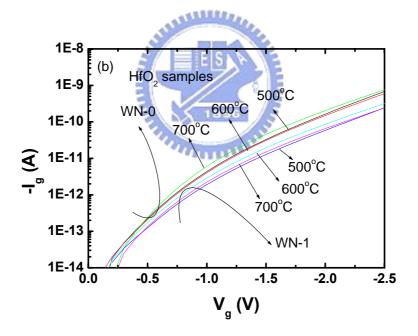

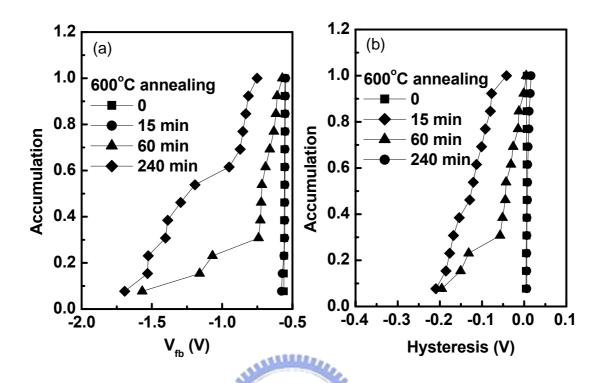

The high resistance of metal nitride forces us to consider the stack structure as gate electrodes. We investigate the Cu/TaN<sub>x</sub> stack of witch the Cu layer serves as the major conduction material and the TaN<sub>x</sub> layer serves as the threshold voltage control material. As the nitrogen content of TaN<sub>x</sub> varies in the range 23 – 39 at. %, TaN<sub>x</sub> films are almost amorphous and are thermally stable up to 800 °C. The work function of TaN<sub>x</sub> is about 4.31-4.38 eV and the modulation range is less than 70meV. The mean value of flatband voltage decreases and the deviation of the flatband voltage increases with the increase of the annealing temperature. Although phase change, grain growth, and Cu contamination contribute the instability of flat band voltage at high temperature, thermal stress-induced oxide charges dominate these thermal instability at 600 °C. The Therefore, Cu/TaN<sub>x</sub> stack gate electrode can be used for the nMOSFETs, and the maximum process temperature following gate electrode deposition should be 500 °C.

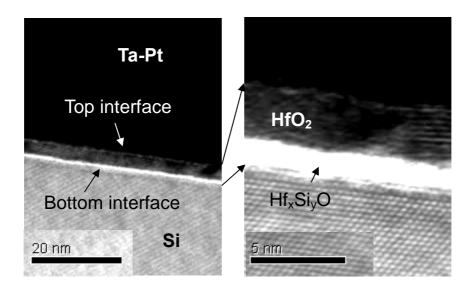

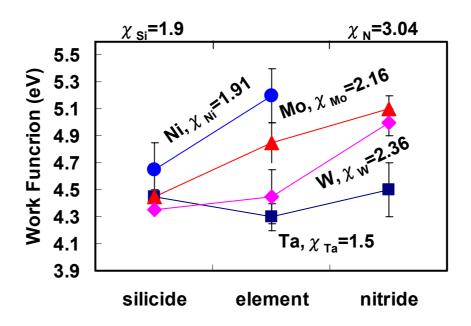

Although metal nitrides are thermally stable, the work function modulation range is not large enough. We demonstrate an effective method of work function modulation by the binary metal alloys instead of metal nitrides. Any work function can be obtained by the binary metallic alloy system with a proper composition of high and low work function metals. Binding energies of core level electrons of Ta and Pt change due to the intermixing of Ta and Pt, which is the mechanism that work function of alloys are adjusted in the metallic alloy systems. The work function of the Ta-based metal alloys (Ta-Ti and Ta-Pt) can be modulated from 4.16 eV to 5.2 eV continuously. Such a wide range work function modulation makes them suitable for CMOS applications. Moreover, incorporation of Pt in Ta film induces poor crystallization and a compound phase of Ta-Pt alloys. Transmission electron microscopy analysis confirmed that grain sizes of Ta-Pt alloys were nano-scale.

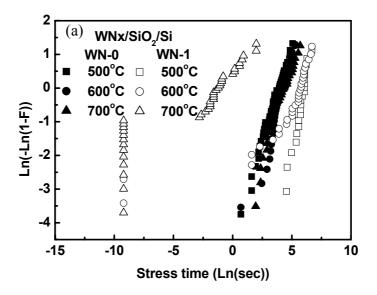

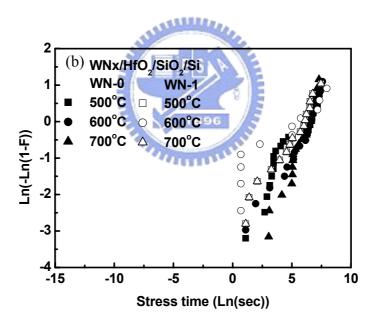

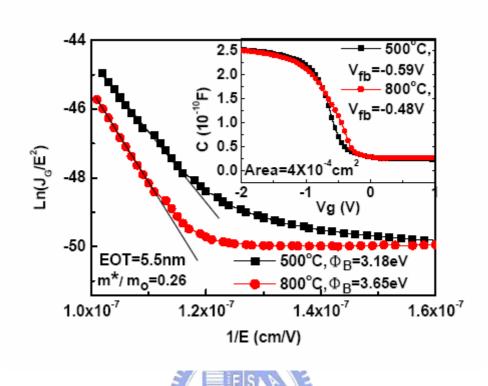

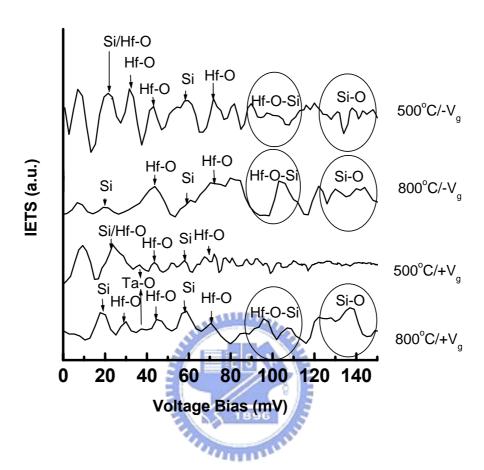

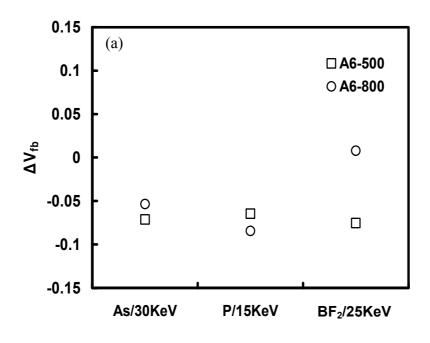

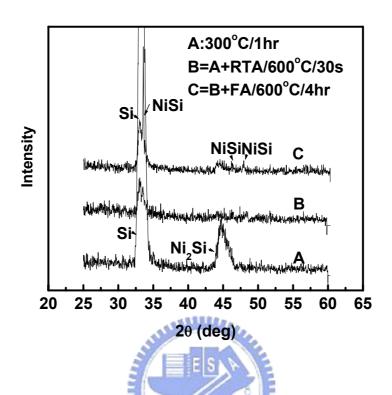

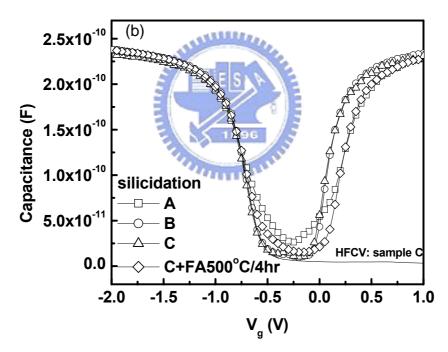

Finally, a new method, implant-to-silicide (ITS), is used to realize effective work function ( $\Phi_{m,eff}$ ) adjustments of fully silicided (FUSI) gates. FUSI gate is easily to integrate with the conventional CMOS process and have a wide range modulation of effective work function by impurities pile-up at the interface between silicide and gate dielectric. The  $\Phi_{m,eff}$  of NiSi FUSI gates on SiO<sub>2</sub> can be tuned by incorporating BF<sub>2</sub><sup>+</sup> or P<sup>+</sup> dopants after silicidation. Nevertheless, the Fermi-level pinning effect is observed in the NiSi/HfO<sub>2</sub> gate which limits the  $\Phi_{m,eff}$  adjustment. A thin SiO<sub>2</sub> interfacial layer between HfO<sub>2</sub> and FUSI gates can reduce the Fermi-level pinning effect. A NiSi FUSI gate on SiO<sub>2</sub> is thermally stable up to 600 °C. The thermal stress and impurity diffusion after a prolonged 600 °C annealing degrade the oxide integrity. The temperature of the post-silicidation process should be as low as 500 °C.

In summary, the small work function range of single metal nitrides restricts that the metal nitrides can only been used for the dual metal scheme. Although the metallic alloys reveal wide range of work function, the integration of different composition of metallic alloys in CMOS application is difficult by the single metal process. Fully silicided gates doped by the N-type and P-type impurities are the most promising process for the single

metal dual work function scheme. However, the interaction between poly-Si and high-k materials before silicidation induces Fermi-level pinning and will retard the application of fully silicided gates. Up to date, there are still no perfect choice of metal gate materials and processes. The standard metal gates for the CMOS are still under consideration to the dual metal scheme or fully silicided gates.

#### 誌謝

本論文能夠順利完成,首先要特別感謝我的指導教授 崔秉鉞博士。感謝老師在這幾年的博士生涯中給予實驗、研究與論文上充分且詳實的指導與教誨,並時時的鼓勵與支持,尤其在實驗上遭遇困難時老師的關懷讓學生在困境中生信心, 老師認真的研究態度與親切的處事風範,令學生受益良多。

其次感謝國家奈米實驗室與交通大學奈米中心提供優良研究設備,特別感謝奈米中心的 林素珠、徐秀鑾、黃月美與陳聯珠小姐在實驗上的幫忙,並感謝奈米實驗室中的工作同仁不厭其煩的給予幫助,使我得以順利完成實驗。諸位口試委員的指正與建議,也在此表示特別感謝。

衷心的感謝實驗室的學長以及一起參與實驗的學長們,特別是徐偉成、林成 利、吳振誠等學長於實驗上的指導及幫忙,另外要感謝實驗室同學們:國龍、家彬、 偉豪、修維、敏晟、鎮吉、志民、天才、旻達、堅立、建翔、智勛、逸璿、柏智、 立峰、宜澤、季霈、孟漢等。由於有了你們相伴,使我渡過此漫長研究生活。再 次感謝所有幫助過我、關心過我的學長及朋友們.....。

最後,我特別要感謝我的父母 黃資良先生與 李玉鳳女士以及我的兄弟姊妹 吉泉、水蓮、麗真、振卿,感謝你們多年來的栽培,默默付出與支持,使我得以 全心全力地投入學業。另外特別感謝女友 宜樺在研究生涯的最後年度裡,給我莫 大的照顧與關心。

# **Contents**

| Abstract (Chinese)            | i    |

|-------------------------------|------|

| Abstract (English)            | iv   |

| Acknowledgement (Chinese)     | viii |

| Contents                      | ix   |

| Table Captions                | xiii |

| Figure Captions               | xiv  |

| Chapter 1                     |      |

| Introduction                  | 1    |

| 1.1 Historical Perspective    | 1    |

| 1.2 Metal Gate Electrodes     | 5    |

| 1.2.1 Metal Gate Materials    | 5    |

| 1.2.2 Resistivity             | 7    |

| 1.2.3 Work Function           | 7    |

| 1.2.4 Metal-Gate Structures   | 8    |

| 1.3 Work Function Engineering | 9    |

| 1.3.1 Structure Modification  | 9    |

| 1.3.2 Interface Treatment     | 10   |

| 1.4 Fermi-Level Pinning       | 11   |

| 1.5 Process Integration       | 12   |

| 1.6 Overview of Dissertation  | 13   |

| References                    | 15   |

# Chapter 2

| Experimental Methods                                                   | 33 |

|------------------------------------------------------------------------|----|

| 2.1 Introduction                                                       | 33 |

| 2.2 Electrical Characterizations                                       | 34 |

| 2.2.1 Basic Electrical Characterizations and Parameters                | 34 |

| 2.2.2 Work Function Extraction                                         | 35 |

| 2.3 Inelastic Electron Tunneling Spectroscopy                          | 39 |

| 2.3.1 Basic Principle of IETS                                          | 39 |

| 2.3.2 Measurement Method                                               | 42 |

| 2.3.3 Signal Analysis                                                  | 43 |

| References                                                             | 45 |

| Chapter 3  Molybdenum Nitride Gates                                    | 57 |

| 3.1 Introduction                                                       | 57 |

| 3.2 Process Flow                                                       | 58 |

| 3.3 Results and Discussions                                            | 59 |

| 3.3.1 Physical Properties of MoN <sub>x</sub> films                    | 59 |

| 3.3.2 Effective Work Function on SiO <sub>2</sub> and HfO <sub>2</sub> | 60 |

| 3.3.3 Electrical Effect of Thermal Annealing                           | 63 |

| 3.4 Summaries and Conclusions                                          | 64 |

| References                                                             | 65 |

| Chapter 4                                                              |    |

| Tungsten Nitride Gates                                                 | 76 |

| 4.1 Introduction                                                       | 76 |

|                                                                        |    |

| 4.2 Process Flow                                                                    | 77  |

|-------------------------------------------------------------------------------------|-----|

| 4.3 Results and Discussions                                                         | 78  |

| 4.3.1 Physical Properties of N-rich WN <sub>x</sub> Films                           | 78  |

| 4.3.2 Effective Work Function on SiO <sub>2</sub> and HfO <sub>2</sub>              | 81  |

| 4.3.3 Electrical Effect of Thermal Annealing                                        | 85  |

| 4.4 Summaries and Conclusions                                                       | 86  |

| References                                                                          | 88  |

| Chapter 5                                                                           |     |

| Cu/Tantalum Nitride Stack Gates                                                     | 102 |

| 5.1 Introduction                                                                    | 102 |

| 5.2 Process Flow                                                                    | 103 |

| 5.3 Results and Discussions                                                         | 104 |

| 5.3.1 Physical Properties of TaN <sub>x</sub> Films                                 | 104 |

| 5.3.2 Effective Work Function on SiO <sub>2</sub>                                   | 106 |

| 5.3.3 Electrical Effect of Thermal Annealing                                        | 108 |

| 5.4 Summaries and Conclusions                                                       | 109 |

| References                                                                          | 111 |

| Chapter 6                                                                           |     |

| Ta-Pt Metallic Alloy Gates                                                          | 122 |

| 6.1 Introduction                                                                    | 122 |

| 6.2 Process Flow                                                                    | 123 |

| 6.3 Results and Discussions                                                         | 124 |

| 6.3.1 Work Function Modulation                                                      | 124 |

| 6.3.2 Physical Characteristic of Ta-rich Ta-Pt Alloys                               | 125 |

| 6.3.3 Thermal Stability of the Ta-Pt Alloy on SiO <sub>2</sub> and HfO <sub>2</sub> | 128 |

| 6.3.4 Effect of Impurity Incorporation to the Effective Work Func  | tion 131     |

|--------------------------------------------------------------------|--------------|

| 6.4 Summaries and Conclusions                                      | 133          |

| References                                                         | 135          |

| Chapter 7                                                          |              |

| Fully Ni-Silicided Gates                                           | 154          |

| 7.1 Introduction                                                   | 154          |

| 7.2 Process Flow                                                   | 155          |

| 7.3 Results and Discussions                                        | 156          |

| 7.3.1 Thermal Stability of the Fully-Silicided NiSi Gates          | 156          |

| 7.3.2 Effect of Work Function due to Impurity Redistribution       | 158          |

| 7.3.3 Effects of Silicidation and Post Annealing on Electrical Cha | racteristics |

|                                                                    | 159          |

| 7.4 Summaries and Conclusions                                      | 161          |

| References 1896                                                    | 163          |

| Chapter 8                                                          |              |

| Conclusions and Recommendations                                    | 178          |

| 8.1 Conclusions                                                    | 178          |

| 8.2 Recommendation for Future Works                                | 184          |

| References                                                         | 188          |

# **Table Captions**

| Chapter 1                                                                     |         |

|-------------------------------------------------------------------------------|---------|

| Table 1-1 Desired properties of the metal gates for CMOS                      | 22      |

| Table 1-2 The sheet resistance and thickness of gate electrodes predicted     | in ITRS |

| roadmap                                                                       | 23      |

| Table 1-3 Charge neutral level and S parameter for several dielecitrics       | 24      |

| Chapter 3                                                                     |         |

| Table 3-1 MoN <sub>x</sub> sample ID and some basic characteristics.          | 68      |

| Chapter 5                                                                     |         |

| Table 5-1 Mean values and standard deviations of retention time of Cu/Tal     | N-2 MOS |

| capacitors under transient capacitance measurement.                           | 113     |

| Chapter 6                                                                     |         |

| Table 6-1 Some conditions of binary metal alloy samples and their composition | ons139  |

| Table 6-2 Material characteristics of Ta, Ta-Pt (A2), and Pt films            | 140     |

| Chapter 6                                                                     |         |

| Table 7-1 Some conditions of the FUSI test samples                            | 167     |

| Chapter 8                                                                     |         |

| Table 8-1 Comparison of metal gates.                                          | 190     |

# **Figure Captions**

# Chapter 1

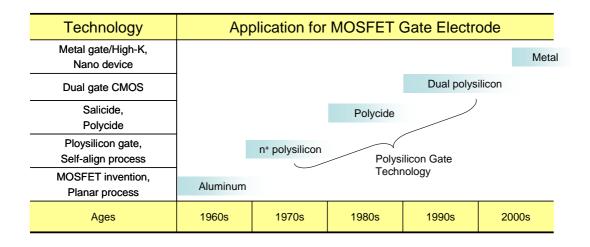

| Fig. 1-1 The evolution of MOSFET gate electrodes with the innovation of technologies.      |

|--------------------------------------------------------------------------------------------|

| 25                                                                                         |

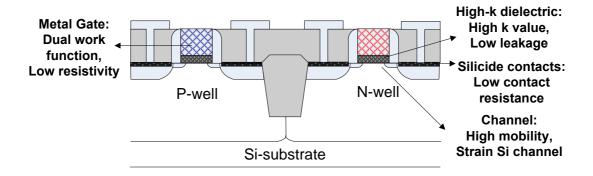

| Fig. 1-2 A schematic cross-section of a sub-45 nm metal gate CMOS structure, where         |

| the novel materials and process-integration solution are indicated                         |

| Fig. 1-3 The common metal elements in periodic table. The elements were marked as p,       |

| n, and m according to its work function near the valence band, conduction                  |

| band, and mid-gap of silicon energy band, respectively                                     |

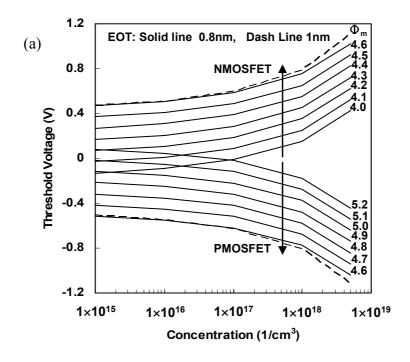

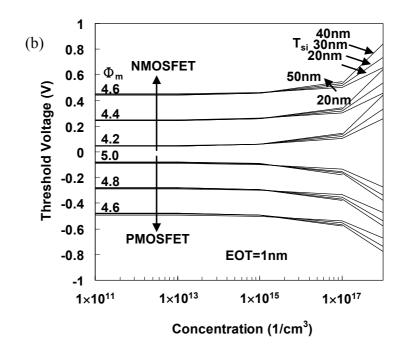

| Fig. 1-4 The threshold voltages of (a) bulk devices and (b) SOI devices versus channel     |

| concentrations. The estimation of threshold voltage was evaluated with the                 |

| simulation of long channel and uniform charnel dopant devices by Avant!                    |

| MEDICI. The dependence of oxide thickness or thickness of silicon body was                 |

| also taken an account                                                                      |

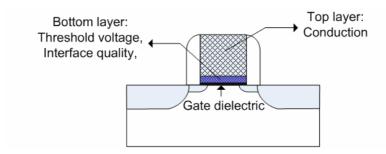

| Fig. 1-5 A structure of the stack metal-gate electrode. The bottom layer serves as         |

| threshold control and dielectric-contact layer; the top layer severs as                    |

| conduction layer connected with metallic interconnect                                      |

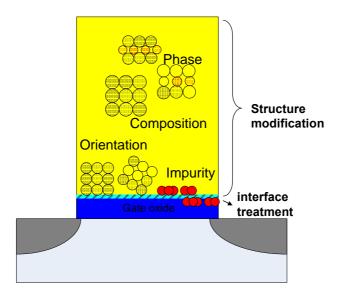

| Fig. 1-6 Schematic methods of work function modulation divided into two categories:        |

| structure modification and interface treatment                                             |

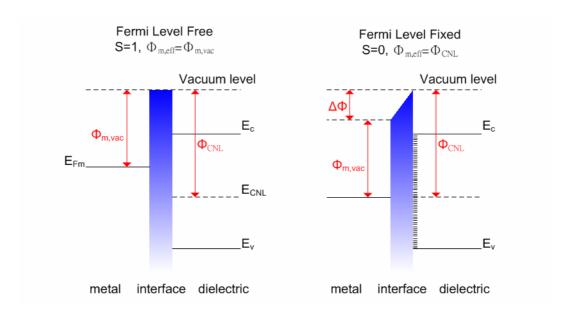

| Fig. 1-7 The critical Fermi level of metal gate on dielectric. The effective work function |

| of metal on dielectric is the same as in vacuum while the interface is perfect.            |

| The effective work function is fixed to the delectric-charge-neutral level while           |

| the interface-state density is high. The interface states are caused by both               |

| intrinsic states (MIGS, ViGS) and extrinsic states (defect levels)3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

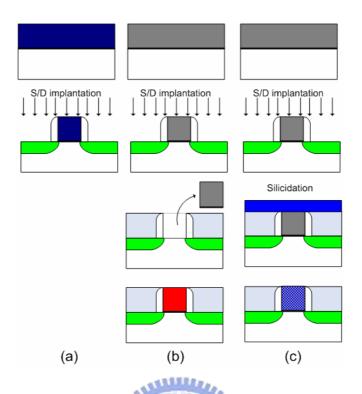

| Fig. 1-8 Schematic process flows of metal gate MOSFETs including (a) gate-first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| process; (b) gate-last process, and (c) fully-silicided process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

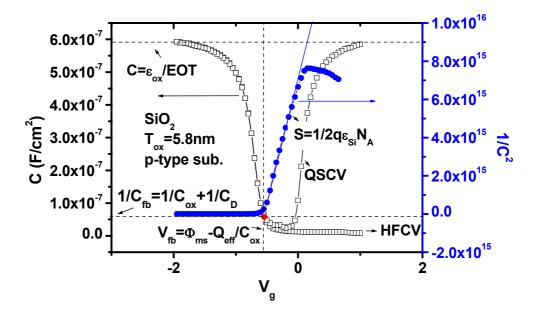

| Fig. 2-1 High-frequency (HF) and quasi-frequency (QS) capacitance-voltage (CV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| characteristic curves of metal-oxide-semiconductoe capacitance as well as th                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1/C <sup>2</sup> -V plot corresponding to the HFCV. Some basic parameters are extracte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| from these plots according to the described formula4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

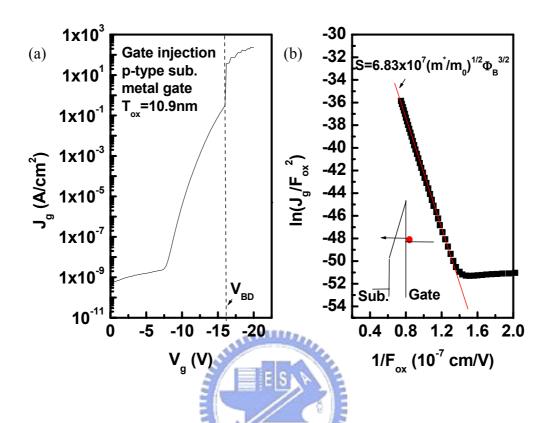

| Fig. 2-2 (a)The I-V characteristic curve, and (b) the relative Fowler-Nordheim plot a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| the electrons are injected from the gate electrode. The inset in (b) shows the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| band diagram. The abrupt jump at $V_{\text{BD}}$ is referred to oxide breakdown voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

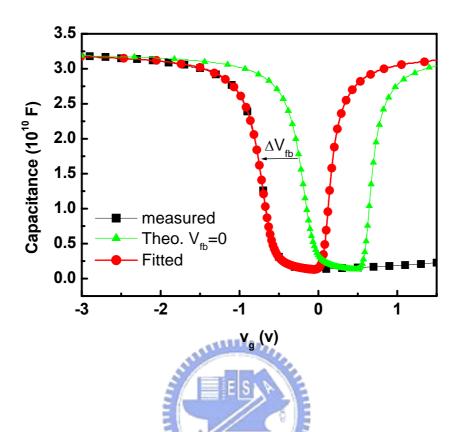

| Fig. 2-3 A example for the extraction of the effective work function by fitting the HFC with a theoretical curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| The state of the s |

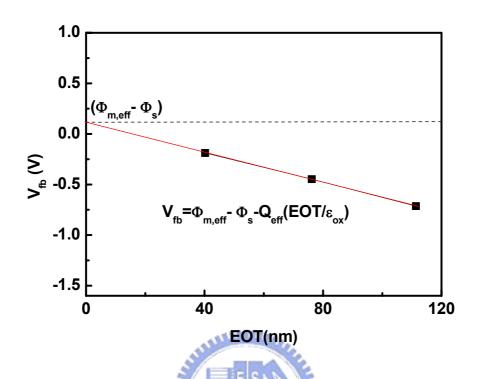

| Fig. 2-4 An example for the extraction of the effective work function by a $V_{fb}$ -EOT plo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| extrapolated at zero of EOT5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

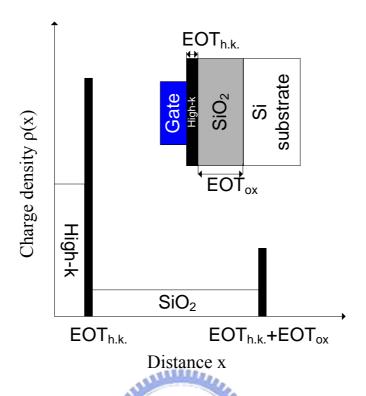

| Fig. 2-5 A schematic plot of charge distribution in the gate/HfO <sub>2</sub> /SiO <sub>2</sub> /Si structure. The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| bulk charges in SiO <sub>2</sub> and HfO <sub>2</sub> are assumed to be a uniform distribution5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

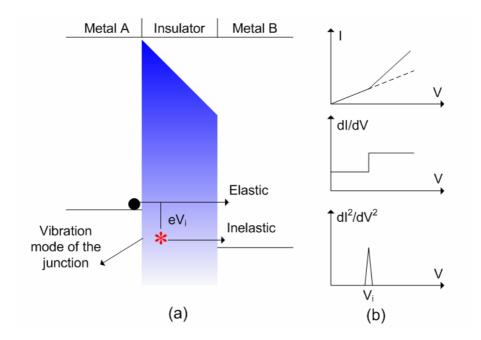

| Fig. 2-6 (a) A schematic energy diagram for tunneling between normal metals A and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| at a voltage bias V which is the threshold voltage to trigger the inelastic                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| tunneling due to the interaction of electron and vibration mode of energy eV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| (b) The relative tunneling current of metal A/insulator/metal B structure at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| K and the corresponding first derivative and second derivative plots5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

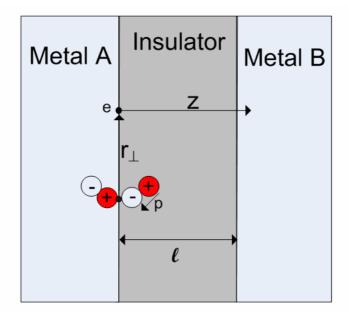

| Fig. 2-7 A schematic diagram of the coordinates used to determined interaction energies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| of a tunneling and a molecule positioned near an insulator-metal A interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 53                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------|

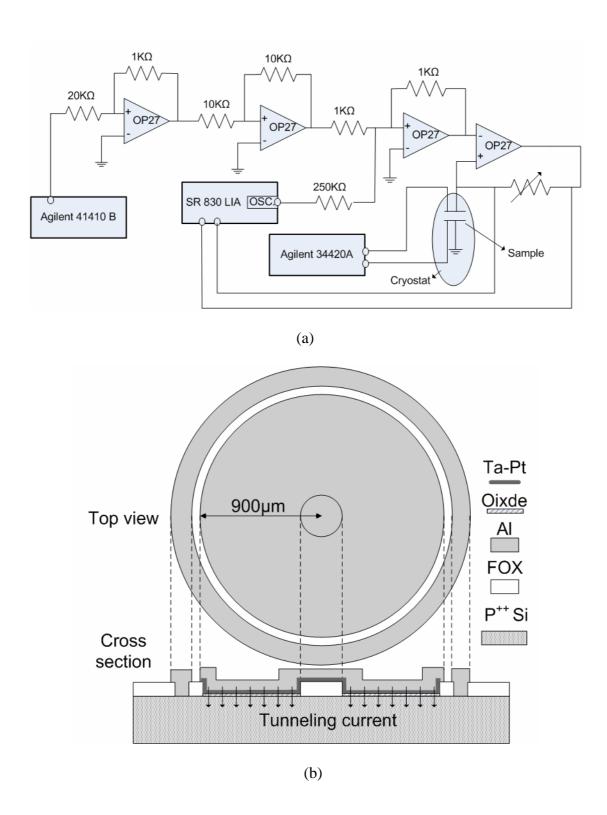

| Fig. 2-8 (a) A circuit schematic diagram of mixer in the IETS system; (b) the schematic                             |

| structure of the IETS test sample. 54                                                                               |

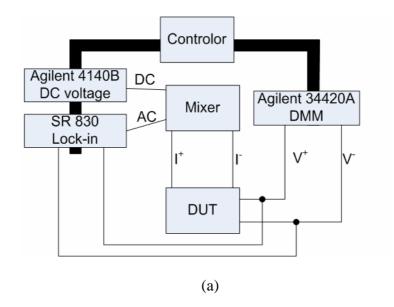

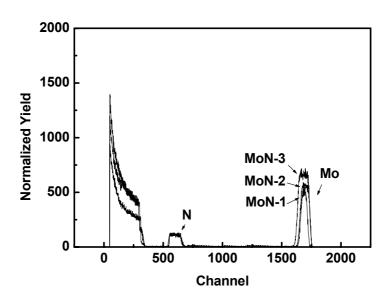

| Fig. 2-9 (a) Schematic diagram and (b) the configuration of the IETS system consisted                               |

| of a DC voltage source (Agilent 4140), a lock-in amplifier with an AC source                                        |

| (SR 830), DC voltage meter (Agilent 34420A), a mixer circuit, a cryostat and                                        |

| controller                                                                                                          |

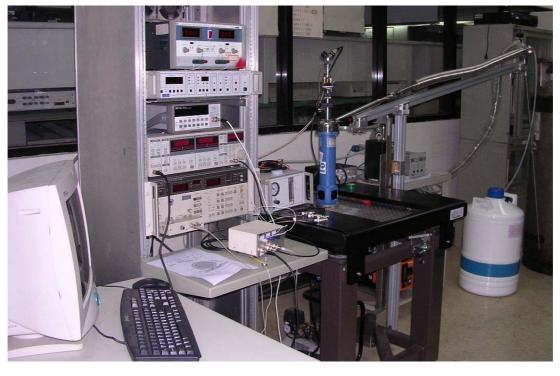

| Fig. 2-10 (a) The primary and smoothed $2\omega$ signal measured by the lock-in amplifier; (b                       |

| the IETS signal extracted from the smoothed $2\omega$ signal after subtraction of a                                 |

| polynomial background                                                                                               |

| Chapter 3                                                                                                           |

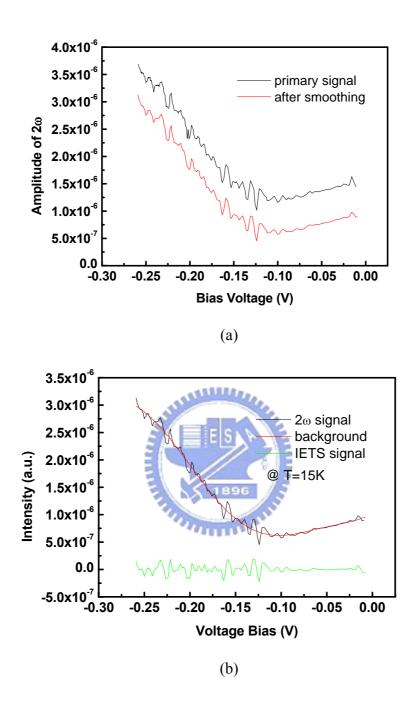

| Fig. 3-1 Rutherford-back-scattering (RBS) spectra of MoN <sub>x</sub> films on graphite substrate.                  |

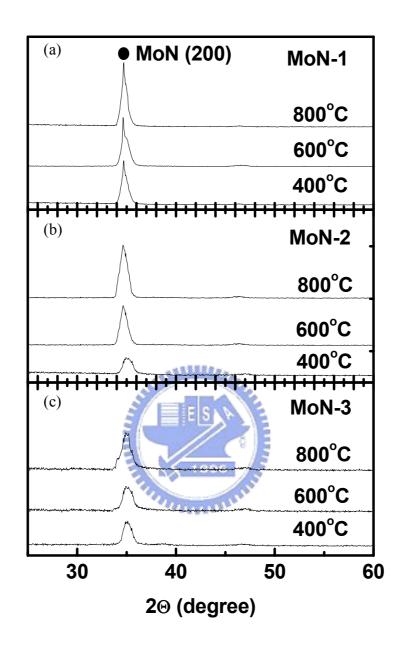

| Fig. 3-2 X-ray diffraction (XRD) spectra of (a) MoN-1, (b) MoN-2, and (c) MoN-3                                     |

| films after annealing at different temperatures70                                                                   |

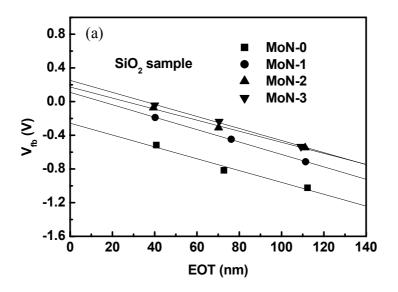

| Fig. 3-3 Flat-band voltage $(V_{fb})$ versus equivalent oxide thickness (EOT) plot of (a)                           |

| $MoN_x/SiO_2/Si\ structure\ and\ (b)\ MoN_x/HfO_2/SiO_2/Si\ structure\ after\ annealing$                            |

| at 500 °C71                                                                                                         |

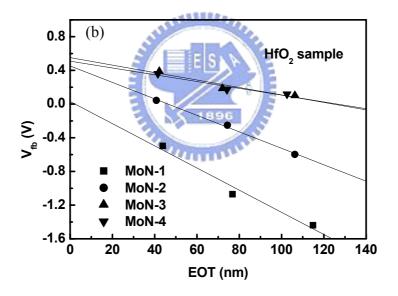

| Fig. 3-4 (a) Effective work function of $MoN_x$ film on $SiO_2$ layer and (b) quasi-effective                       |

| work function of MoN <sub>x</sub> film on HfO <sub>2</sub> layer versus annealing temperature72                     |

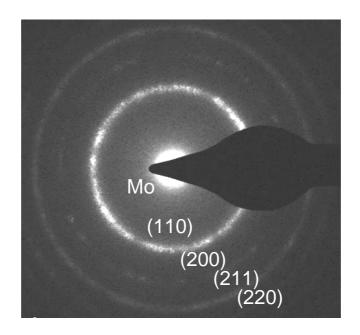

| Fig. 3-5 The electron diffraction pattern of the MoN-0 film after annealing at 600 °C.                              |

| 73                                                                                                                  |

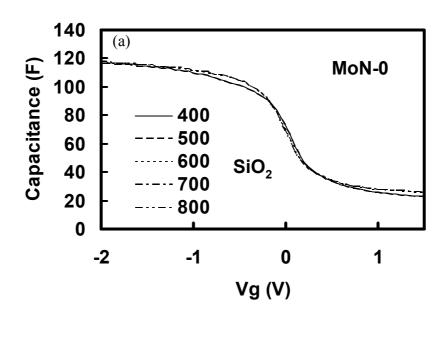

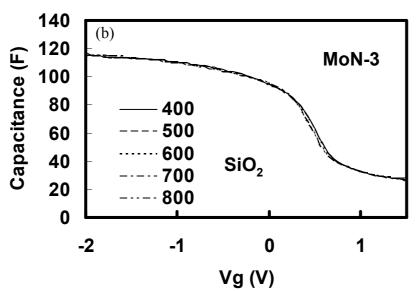

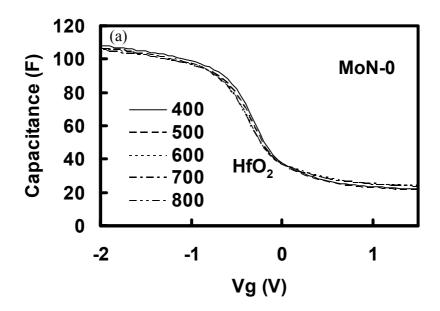

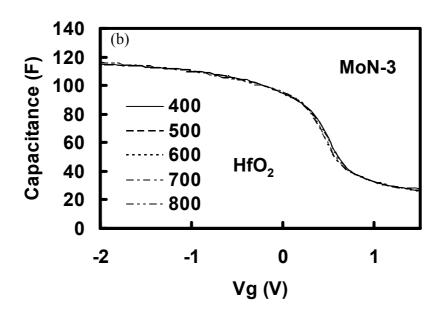

| Fig. 3-6 Capacitance-Voltage curves of $MoN_x$ (60 nm)/SiO <sub>2</sub> (40 nm)/Si structure of                     |

| (a)MoN-0 and (b) MoN-3 films after annealing at different temperatures74                                            |

| Fig. 3-7 Capacitance-voltage curves of MoN <sub>x</sub> (60 nm)/HfO <sub>2</sub> (5 nm)/SiO <sub>2</sub> (40 nm)/Si |

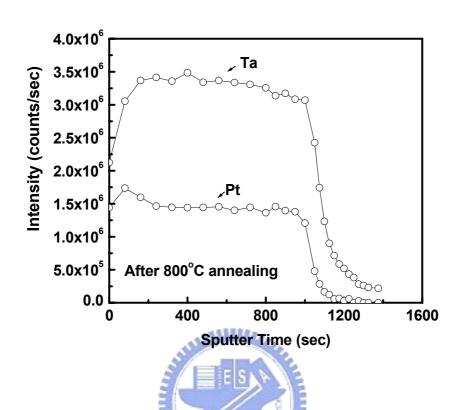

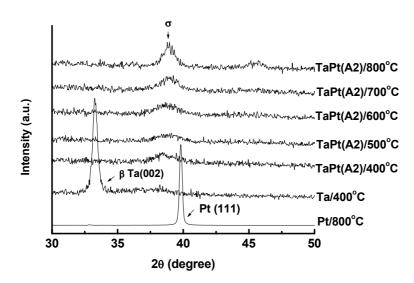

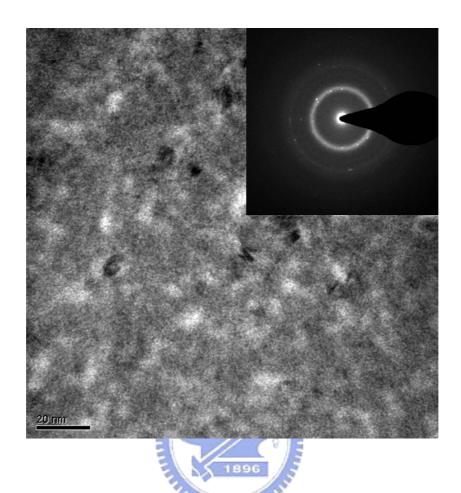

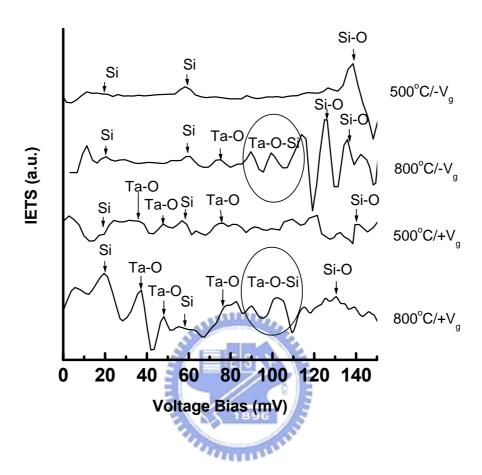

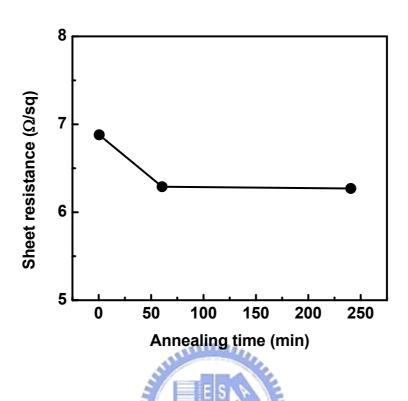

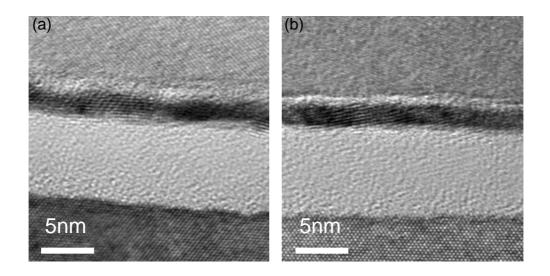

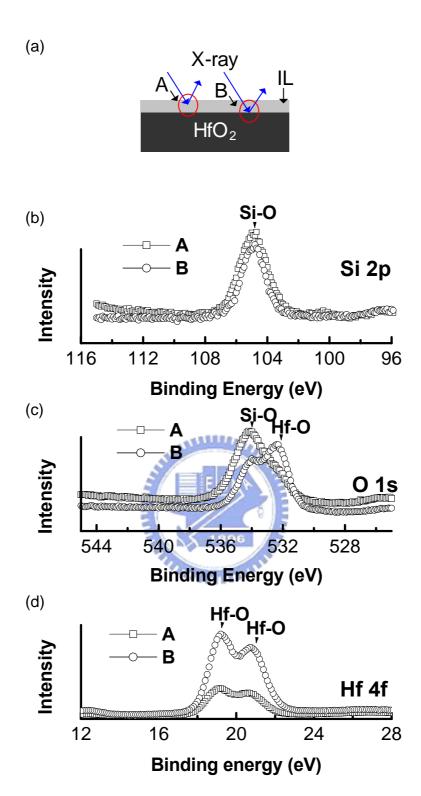

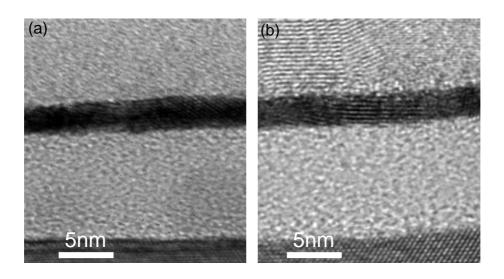

|           | structure of (a) MoN-0 and (b) MoN-3 films after annealing at different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |