# 國立交通大學

# 電機與控制工程學系

# 碩士論文

功率感知資料匯流排編碼解碼器設計

Design of Power Aware Data Bus Codec

研究生: 黃德瑋

指導教授:林進燈 教授

陳右穎 教授

中華民國九十六年七月

# 功率感知資料匯流排編碼解碼器設計 Design of Power Aware Data Bus Codec

研究生:黃德瑋 Student: De-Wei Huang

指導教授:林進燈 教授 Advisor: Dr. Chin-Teng Lin

陳右穎 教授 Dr. You-Yeng Chen

國立交通大學

電機與控制工程學系

碩士論文

## A Thesis

Submitted to Institute of Electrical and Control Engineering

College of Electrical and Computer Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical and Control Engineering

July 2007

Hsinchu, Taiwan, Republic of China 中華民國九十六年七月

# 功率感知資料匯流排編碼解碼器設計 Design of Power Aware Data Bus Codec

學生: 黃德瑋 指導教授: 林進燈 博士

陳右穎 博士

國立交通大學電機與控制工程研究所

## 中文摘要

本論文提出在匯流排傳輸上面,設計一個功率感知資料匯流排編碼解碼器,來降低 transition activity,進而達到降低功耗輸出的效果。在8位元寬度以及外部負載電容50 pF 環境下模擬結果,分別與編碼前及 RSH 方法相比較可降低23%和6%功率消耗,其設計特色在於:(1)編碼解碼端不需要花費龐大硬體成本以及處理時間,便可達到迅速傳輸資料以及有效率降低功耗的目的;(2)針對不同應用能自動挑選來做最合適的編碼處理。經由測試結果,只需要額外增加6%硬體成本,在多媒體資料傳輸,平均可降低20%左右動態功率;在DCT、FIR 程式中,平均可降低50~60%左右動態功率。

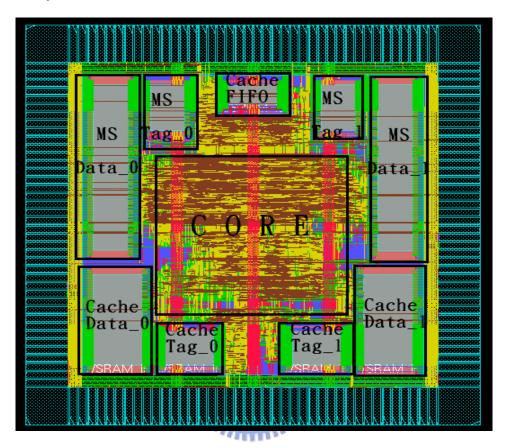

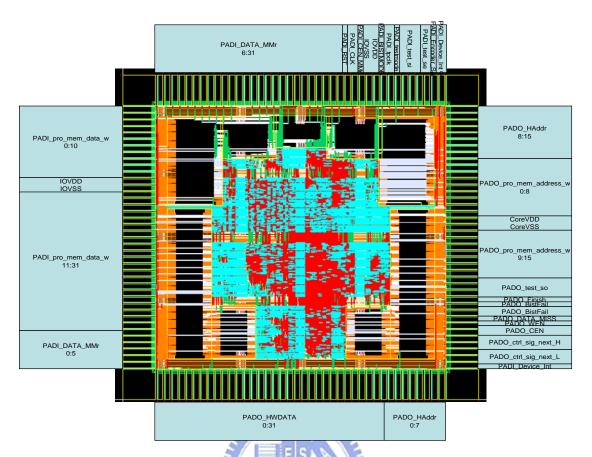

再者,我們將此低功耗匯流排整合至在已開發的嵌入式RISC/DSP單核心處理器內,針對處理器系統架構上面,加入數位低功耗設計,有效率的降低功率消耗,期望能在效能以及功耗上達到一個平衡點。此設計採用TSMC 0.18μm 製程,晶片製作面積約 2.11x2.11 mm²,預估最大操作頻率在 100MHz,功率消耗約 16mW。

Design of Power Aware Data Bus Codec

Student: De-Wei Huang Advisor: Dr. Chin-Teng Lin

Dr. You-Yeng Chen

Department of Electrical and Control Engineering

National Chiao-Tung University

**Abstract**

In this thesis, we propose a power-aware codec scheme to reduce transition

activity for data bus design. The low power data bus codec consisting of transparent,

inverter, XOR, and XNOR module can lead to 23 % & 6 % power reduction

compared with the un-coding and R-S-H's methods under the 8-bit width and the 50

pF capacitance loading. The main features of this codec design are: (1) codec can save

68% area overhead compared with R-S-H's design and (2) codec can adaptively

choose the optimal encoding scheme for different kinds of data types due to versatile

applications. From the FIR and DCT benchmark simulations, the power can be

reduced to 50%~60% on average.

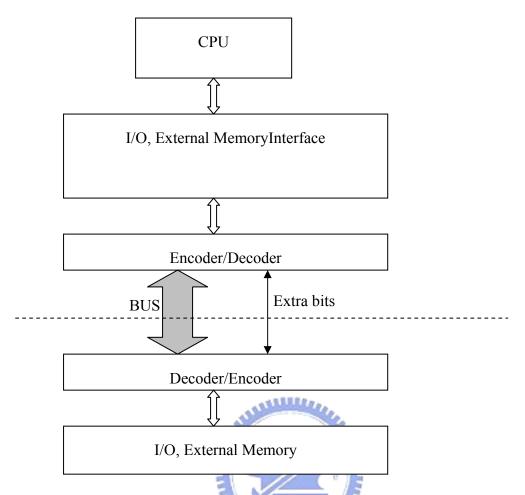

Furthermore, we integrate this data bus codec into a RISC/DSP unit-core

processor with the tradeoff between cost and power. The chip fabricated in TSMC

0.18μm CMOS technology process with the total area of 2.11×2.11mm<sup>2</sup> and has

power consumption of 16mW at 100MHz with 1.8V supply voltage.

iii

## 誌謝

兩年的研究所生涯隨著論文的完成劃上了句號,這兩年間,要感謝許多人的 鼓勵和幫忙,使我獲得充實的專業能力並順利完成研究所的學業。

首先要感謝的是我的指導教授-林進燈老師。林老師是國內十分傑出的一位 教授,在不同領域內都有相當好的研究成果。感謝老師提供了很理想的研究環境 及正確的引導,使我在研究上非常順利。在老師悉心的指導下,讓我學習到解決 問題的能力及做研究應有的態度。

另外,最感謝資工系范倫達教授及鐘仁峰學長的教導,尤其是面臨畢業主題方向模糊的壓力時,范教授在這上面給予我相當大的助力,而教授親切的態度及學識的也讓我在討論論文時感到輕鬆而無壓力,獲益良多。此外在實驗室中,不管大小疑難雜症,常常去請教仁峰學長,非常感謝學長不厭其煩地教導,使我增進了對積體電路設計上的專業知識,開拓了我的視野。也感謝實驗室所有的夥伴,經翔學長、紹航學長、峻谷學長、家昇學長、庭緯學長、有德學長、笑容甜美頭髮捲捲的美女靜瑩、酷酷運動全能的智文、開朗運動全能的俊傑、可愛熱情的正妹林玫、翰林大學士肇廷以及讓我論文不能早點寫完的學弟妹們等,感謝大家在研究上的互相扶持及鼓勵。

也感謝我的爸爸、媽媽、奶奶、哥哥,你們的支持一直是我最溫暖的後盾; 你們的鼓勵是我信心的來源。

# **Table of Contents**

## Table of Contents V

List of Figures V11

List of Table X

| Chapter 1 | Introduction                                                 | 1    |

|-----------|--------------------------------------------------------------|------|

| 1.1       | Brief Introduction                                           | 1    |

| 1.2       | Organization of the Thesis                                   | 3    |

| Chapter 2 | Power Aware Data Bus Codec                                   |      |

| 2.1       | MotivationRelated Works                                      | ∠    |

| 2.2       | Related Works                                                |      |

| 2.2.1     | Bus-Invert Bus Encoding                                      |      |

| 2.2.2     | Bus-Invert Bus EncodingZero-Transition Activity Encoding     | 9    |

| 2.2.3     | A Coding Framework for Low Power Address and Data Busses     |      |

| 2.3       | Power Aware Data Bus Codec                                   | 20   |

| 2.3.1     | Proposal of Codec                                            | 22   |

| 2.3.2     | Architecture of Codec                                        | 28   |

| 2.4       | Power Aware Data Bus Codec Simulator                         | 31   |

| 2.4.1     | 8 bits Power Aware Data Bus Codec Simulator                  | 31   |

| 2.4.2     | 16 bits Power Aware Data Bus Codec Simulator                 | 35   |

| 2.5       | Result and Analysis                                          |      |

| Chapter 3 | Low Power Embedded Processor Design                          | . 41 |

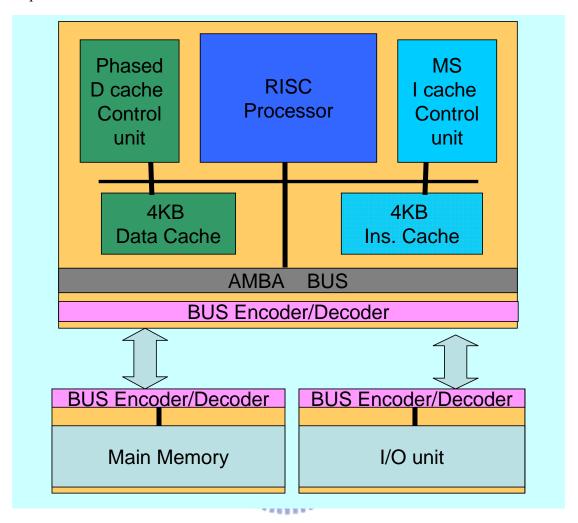

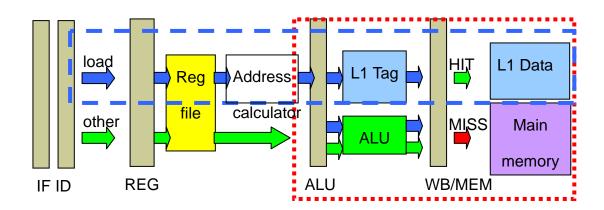

| 3.1       | Architecture of the Low Power Embedded Processor             | 41   |

| 3.1.1     | Low Power Embedded Processor Core                            | 41   |

| 3.1.2     | Low Power Embedded Processor Instruction Set                 | 45   |

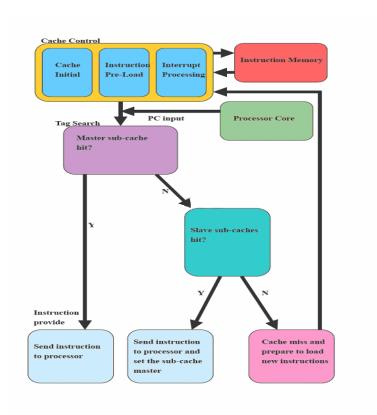

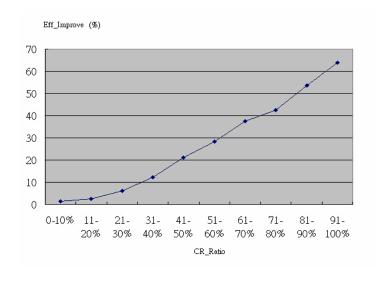

| 3.2       | Configurable Master-Slave I-Cache Controller                 | 49   |

| 3.2.1     | The Proposal of Configurable Master-Slave I-Cache Controller | 49   |

| 3.2.2     | The Performance of Configurable Master-Slave I-Cache         | 50   |

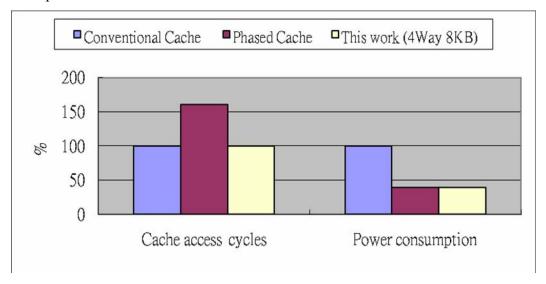

| 3.3       | High Performance Pipeline Design of Low Power Phased Cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51   |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.4       | Tool Chain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52   |

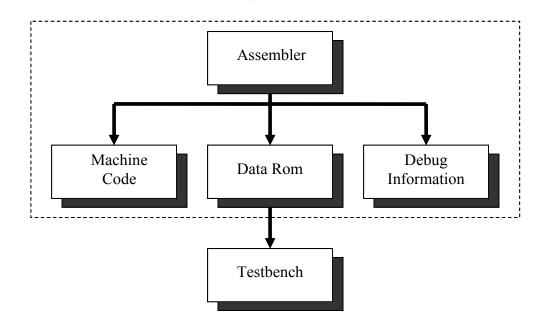

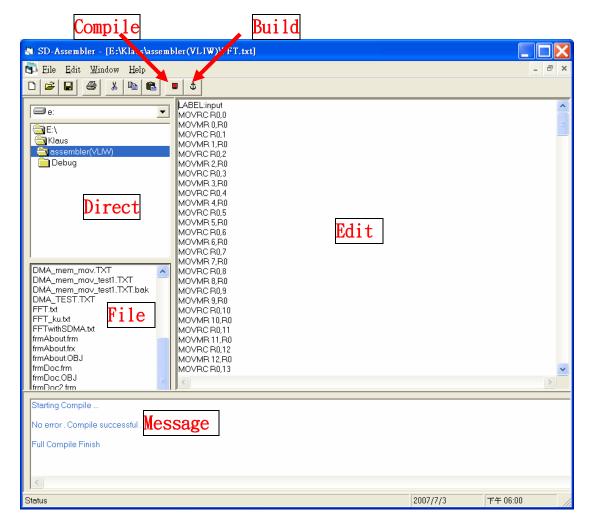

| 3.4.1     | Assembler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 52   |

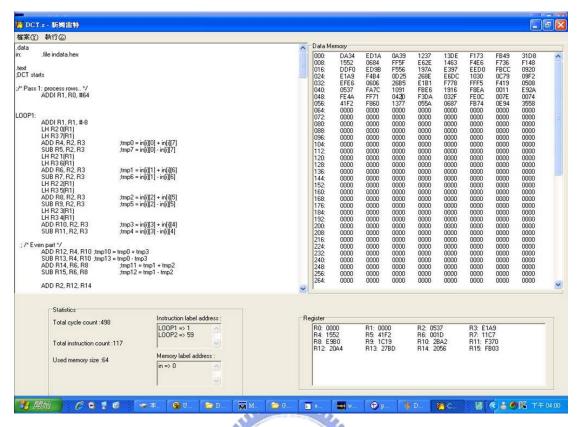

| 3.4.2     | Simulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 53   |

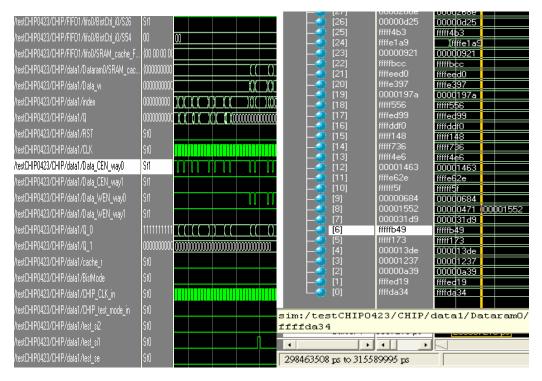

| 3.5       | Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 55   |

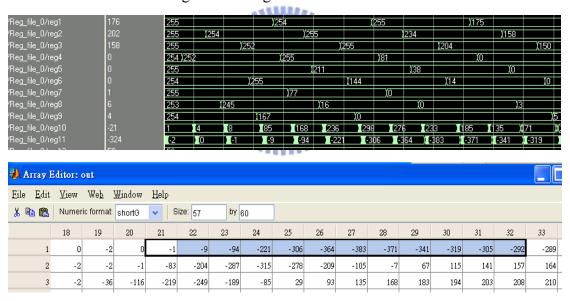

| 3.5.1     | Finite Impulse Response                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55   |

| 3.5.2     | Discrete Cosine Transform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57   |

| 3.5.3     | Sobel Operator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 58   |

| 3.6       | Field-Programmable Gate Array (FPGA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59   |

| 3.7       | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 60   |

| Chapter 4 | Chip Implemenation and Verification Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 61 |

| 4.1       | Chip Fabrication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 61   |

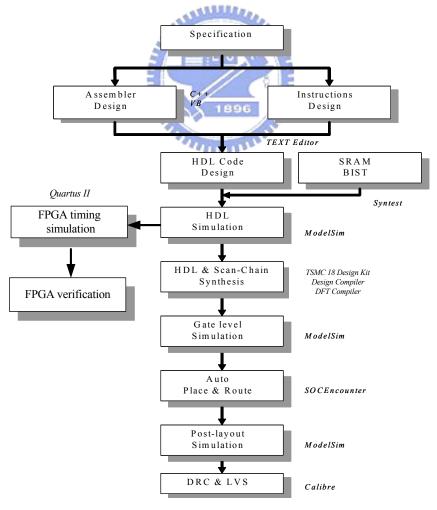

| 4.1.1.    | Chip Design Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 61   |

| 4.1.2.    | Synthesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62   |

| 4.1.3.    | Auto Placement and Routing (APR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62   |

| 4.2       | Power Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66   |

| Chapter 5 | Conclusions and Future works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

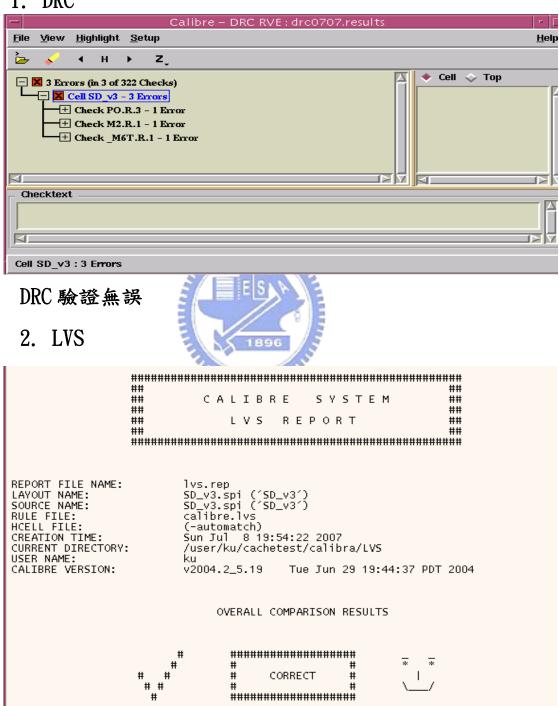

| Appendix  | THE THE PARTY OF T | . 73 |

| A. DRO    | C and LVS Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 73   |

| B. CIC    | Tapeout Review Form.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 74   |

# List of Figures

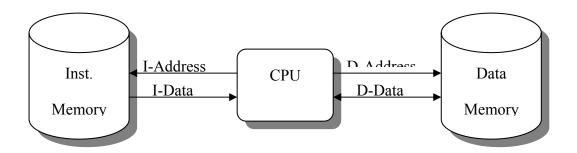

| Fig. 2-1. Harvard architecture with four busses                 | 6  |

|-----------------------------------------------------------------|----|

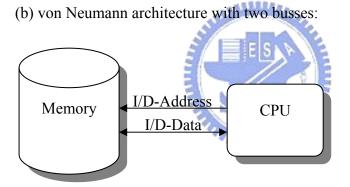

| Fig. 2-2. von Neumann architecture with two busses.             | 6  |

| Fig. 2-3 von Neumann architecture with one bus.                 | 7  |

| Fig. 2-4. Bus-Invert Encoding.                                  | 9  |

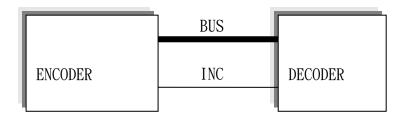

| Fig. 2-5. Zero-Transition Activity encoder/decoder              | 11 |

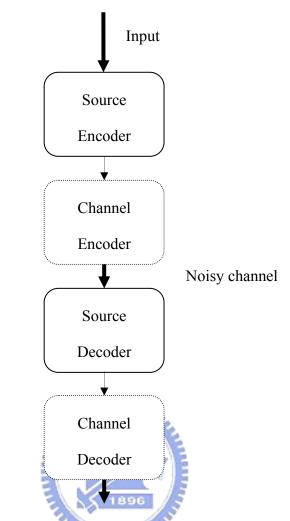

| Fig. 2-6. A general communication system.                       | 14 |

| Fig. 2-7. A general communication system of noiseless channel   | 15 |

| Fig. 2-8. A Practical communication system of noiseless channel | 15 |

| Fig. 2-9. Occurrence distribution for EEG data before dbm       | 18 |

| Fig. 2-10. Occurrence distribution for EEG data after dbm.      | 18 |

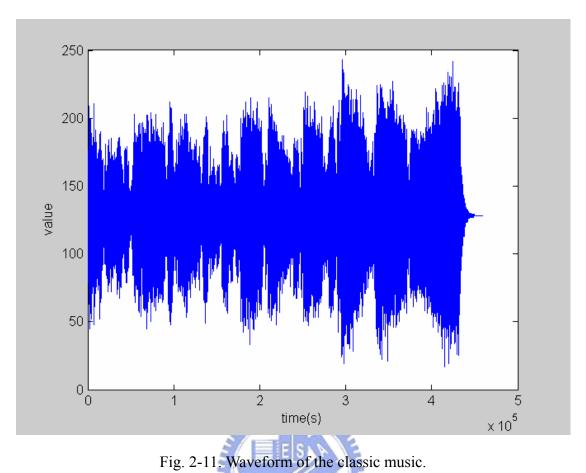

| Fig. 2-11. Waveform of the classic music                        | 21 |

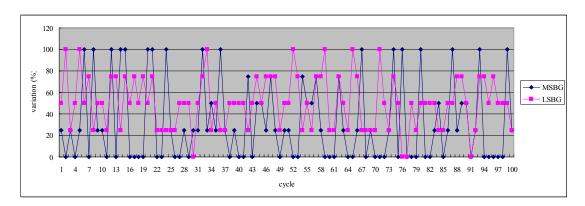

| Fig. 2-12. Data variation                                       | 22 |

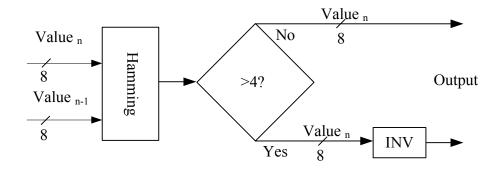

| Fig. 2-13. Block diagram of Invert coding.                      | 25 |

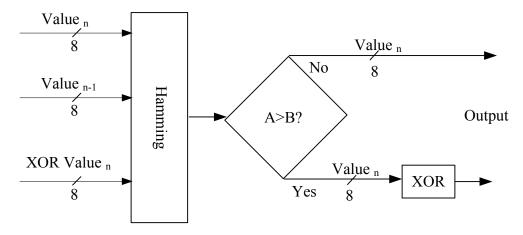

| Fig. 2-14. Block diagram of XOR coding.                         | 27 |

| Fig. 2-15. Block diagram of XNOR coding.                        | 28 |

| Fig. 2-16. System architecture.                                 | 29 |

| Fig. 2-17. Block diagram of encoder.                            | 29 |

| Fig. 2-18. Block diagram of decoder.                            | 30 |

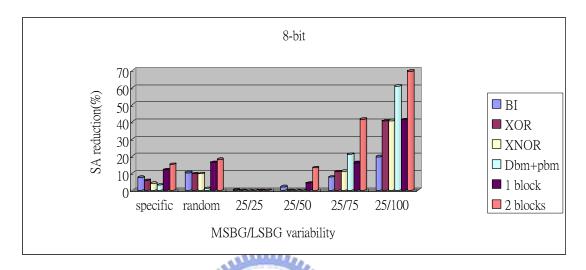

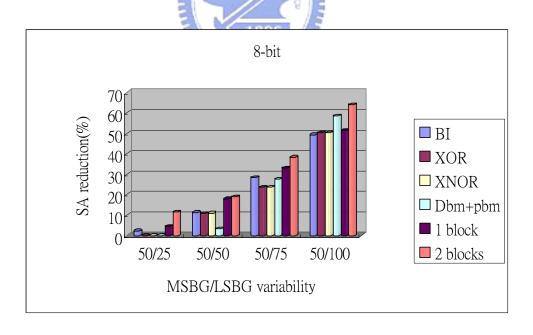

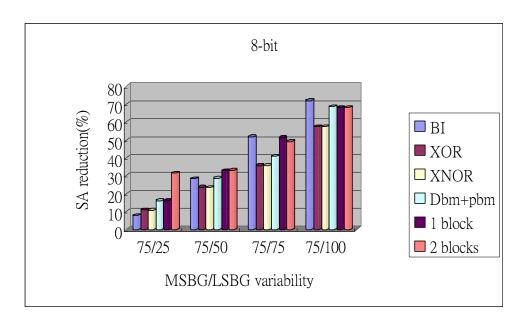

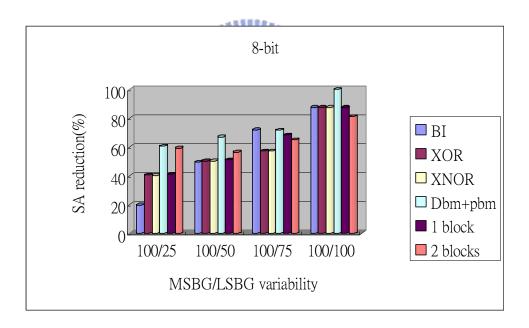

| Fig. 2-19. Switch activity reduction for 8-bit data             | 33 |

| Fig. 2-20. Switch activity reduction for 8-bit data             | 33 |

| Fig.2-21. Switch activity reduction for 8-bit data              | 34 |

| Fig. 2-22. Switch activity reduction for 8-bit data             | 34 |

| Fig. 2-23. The Data Distribution.                               | 35 |

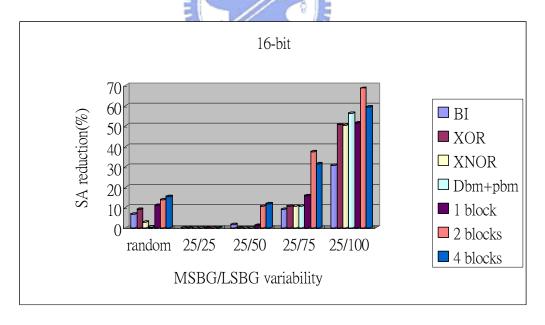

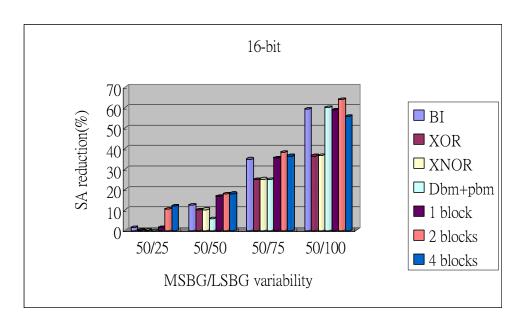

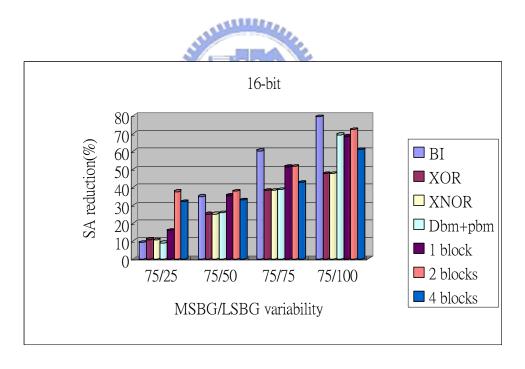

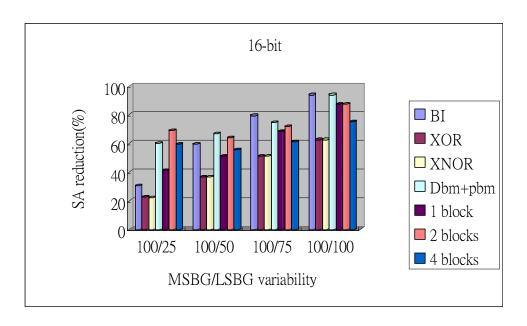

| Fig.2-24. Switch activity reduction for 16 bits data                   | 37   |

|------------------------------------------------------------------------|------|

| Fig.2-25. Switch activity reduction for 16 bits data                   | 38   |

| Fig.2-26. Switch activity reduction for 16 bits data                   | 38   |

| Fig.2-27. Switch activity reduction for 16 bits data                   | 39   |

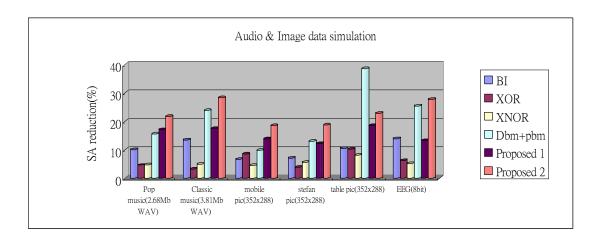

| Fig. 2-28. Simulation for Multi-Media data.                            | 39   |

| Fig. 3-1 The architecture of processor                                 | 42   |

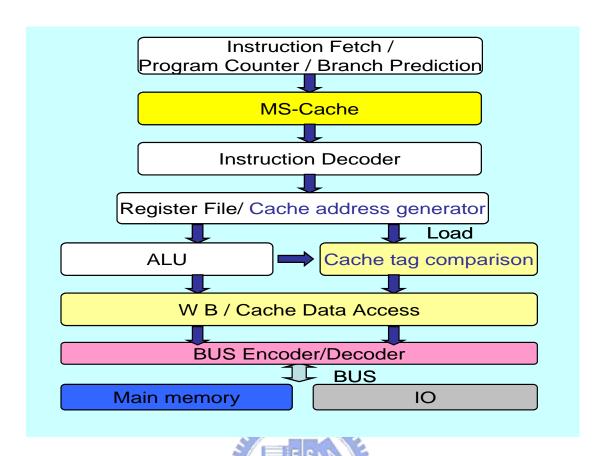

| Fig. 3-2 Pipeline processing flow                                      | 43   |

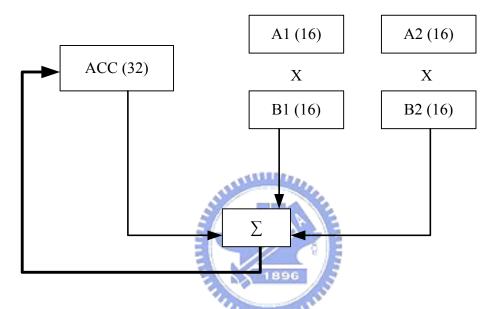

| Fig. 3-3 MACHR operation                                               | 48   |

| Fig. 3-4 The Configurable Master-Slave I-Cache controller algorithm    | 50   |

| Fig. 3-5 The improvement of MS-cache                                   | 50   |

| Fig. 3-6 The architecture of High performance pipeline design of low p | ower |

| phased cache                                                           | 51   |

| Fig. 3-7 Cache access cycles & Power consumption                       |      |

| Fig. 3-8 The assembler Figure                                          |      |

| Fig. 3-9 Assembler Interface                                           | 53   |

| Fig. 3-10 Software pipeline design flow                                | 54   |

| Fig. 3-11 The simulator interface                                      | 55   |

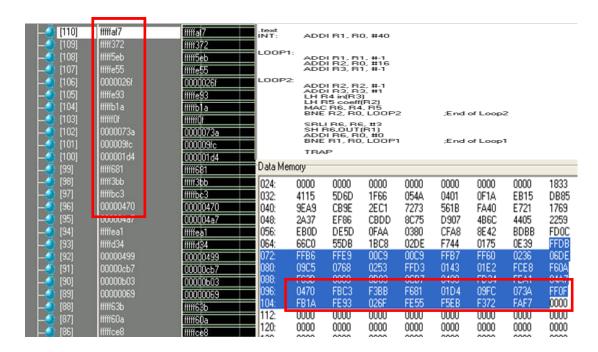

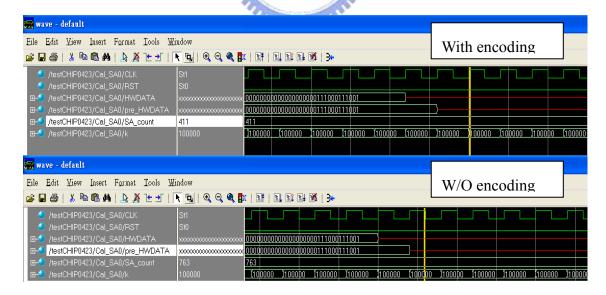

| Fig. 3-12 FIR RTL simulation and simulator result.                     | 56   |

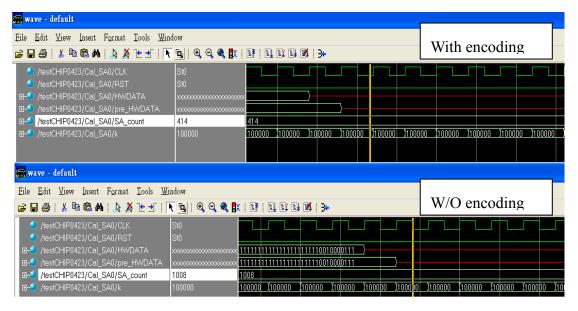

| Fig. 3-13 Switch activity for FIR                                      | 56   |

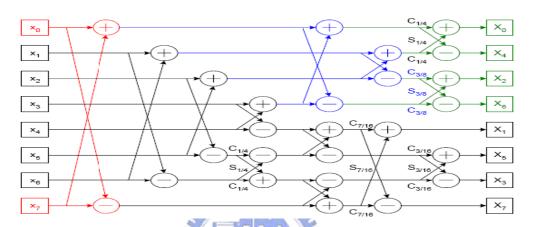

| Fig. 3-14 1 dimension 8 by 8 DCT                                       | 57   |

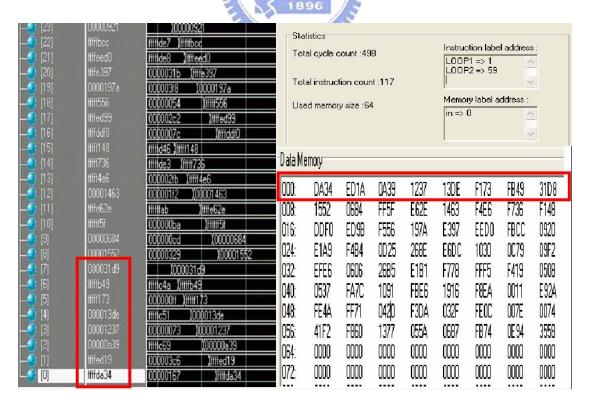

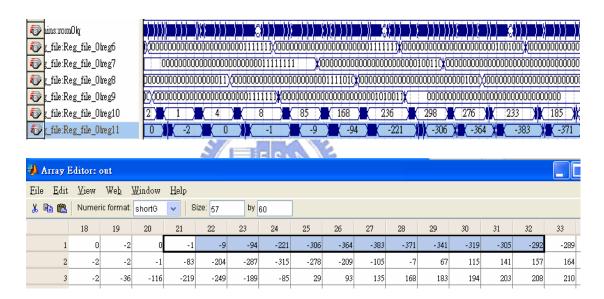

| Fig. 3-15 2 dimension 8-8 DCT RTL simulation and simulator result      | 57   |

| Fig. 3-16 Switch activity for DCT                                      | 58   |

| Fig. 3-17 Sobel Operator simulation.                                   | 59   |

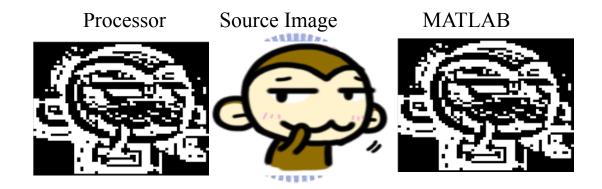

| Fig. 3-18 The Sobel operator result in FPGA and Matlab                 | 60   |

| Fig. 4-1 Chip Design Flow                                              | 61   |

| Fig. 4-2 Chip Layout Diagram                                           | 63   |

| Fig. 4-3 Chip Pin Description Diagram                | 64 |

|------------------------------------------------------|----|

| Fig. 4-4 160pin-CQFP Bounding Diagram                | 64 |

| Fig. 4-5 DCT gate-level simulation                   | 66 |

| Fig. 4-6 Sobel gate-level simulation                 | 66 |

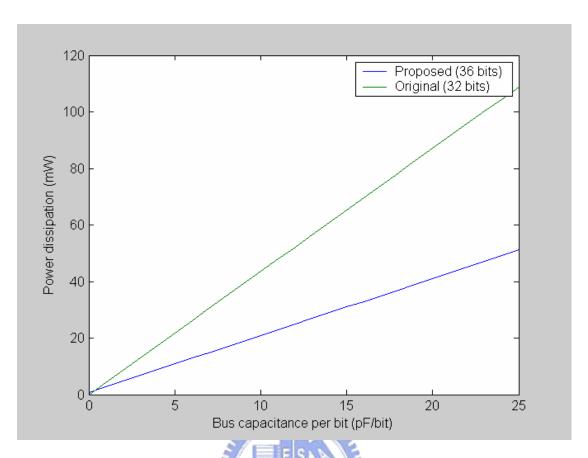

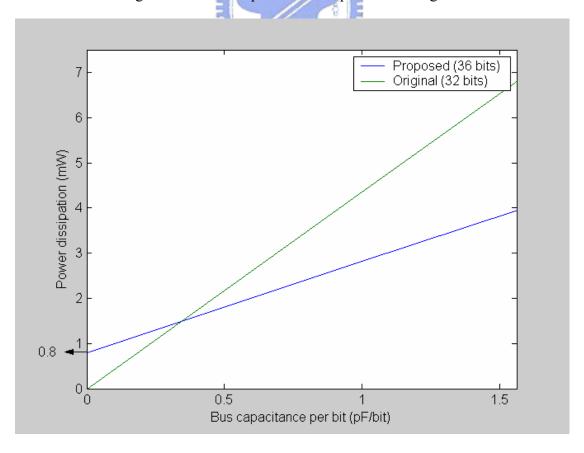

| Fig. 4-7 Power dissipation for Proposed and Original | 68 |

| Fig. 4-8 Power dissipation for Proposed and Original | 68 |

# List of Table

| Table 2-1 Without Zero-Transition Activity Encoding    | 11 |

|--------------------------------------------------------|----|

| Table 2-2 With Zero-Transition Activity Encoding       | 12 |

| Table 2-3 Example of Difference-Based Mapping ( dbm )  | 17 |

| Table 2-4 Example of Probability-Based Mapping ( pbm ) | 19 |

| Table 2-5 First Ten Data Sequences of Classic Music    | 21 |

| Table 2-6 Data Variation                               | 22 |

| Table 2-7 Example of Classic Music before Using Invert | 23 |

| Table 2-8 Example of Classic Music after Using Invert  | 24 |

| Table 2-9 Example of Classic Music before Using XOR    | 25 |

| Table 2-10 Example of Classic Music after Using XOR    | 26 |

| Table 3-1 Data Moving Instructions List                | 45 |

| Table 3-2 Arithmetic & Logic Instructions List         | 46 |

| Table 3-3 Branch/Jump Instructions List                | 46 |

| Table 3-4 SIMD Instructions List                       | 47 |

| Table 3-5 Other Instructions List                      | 48 |

| Table 4-1 Synthesis Report                             | 62 |

| Table 4-2 APR Report                                   | 62 |

| Table 4-3 Chip Specification                           | 65 |

# Chapter 1 Introduction

## 1.1 Brief Introduction

In 3C integration era, the mobile phone does not only communicate with people but also has various functions like digital camera, MP3 player, games, and etc. Therefore, the multi-functions mobile phone just can acquire favor of consumers in the information market.

However, when the demand of performance and functions of the mobile phone increases, the power consumption would be an important design issue. Most of companies not only seek for high performance and low cost, but also focus on low power design.

In other words, low power is a primary consideration to System on Chip (SOC) design, especially for handheld devices due to the limited battery life. In order to accomplish such challenging tasks, many design techniques such as multi-Vth design techniques [1][2], dynamic voltage scaling [3][4], gated clock [5], and low-power on-chip memory architecture [6] have been proposed to reduce both dynamic power and leakage power However, those design techniques require advanced design process to reach the low power goal.

In the processor, it becomes increasingly limited by memory performance and system power consumption [7]. The power associated with off-chip accesses can dominate the overall power budget. The memory power problem is even more acute for processors that possess memory intensive access patterns and require streaming serial memory access that tends to exhibit low temporal locality.

In terms of reducing memory power, one approach is to consider how optimally to schedule off-chip accesses. The capacitance associated with the external bus is much larger than the internal node capacitance inside a microprocessor. [7] For example, a low-power embedded microprocessor system like an Analog Devices ADSP-BF533 running at 500 MHz consumes about 374 mW on average during normal execution. Assuming a 3.65 V supply voltage and 133 MHz bus frequency, the average external power consumed is around 170 mW, which accounts for approximately 30% of the overall system power dissipation. One factor affecting the capacitance on external bus power is the bus width. For example, the power dissipation on 16-bit bus is larger than 30% on 8-bit bus. As a consequence, the design target like MP3 player, PDA and mobile phone always use low bit width bus instead of the high bit width bus.

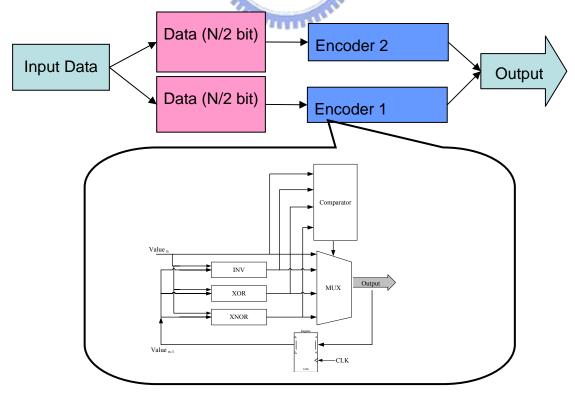

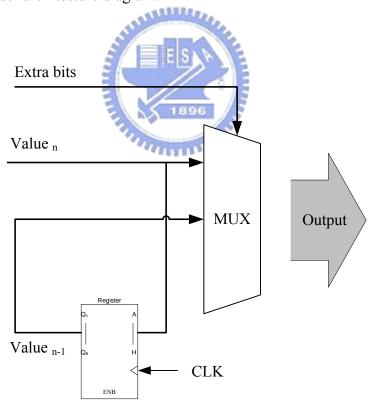

Recently, R-S-H proposed codec scheme to reduce power consumption for data and address buses. However, the table size is proportional to bit width in [16]. That means that while data width is larger, more power consumption certainly be induced. In this thesis, we are motivated to design a power-aware data bus codec which can reduce dynamic power for data transmission. This power-aware codec is composed of transparent, inverter, XOR, and XNOR modules. We use the audio, image, EEG,, random, and specific data to verify the codec characteristics via simulation results and compare with other encoding schemes. In terms of codec implementation, a RISC/DSP unit-core processor that integrates the proposed codec and low power cache controller design is used for verification. The chip has been fabricated in TSMC 0.18µm CMOS technology with the total area of 2.11×2.11mm². The maximum clock frequency runs at 100MHz with a single 1.8V supply voltage.

The proposed codec design has following features:

(1)Low cost

Codec does not need large hardware cost (just have 5% gate counts of total processor) and one cycle processing time penalty.

#### (2)Low power

In the result of 8-bit simulation, our proposal has 23 % dynamic power reduction in average on bus. For DSP function such as DCT and FIR, our proposal has 50-60% dynamic power reduction on bus. For power estimation, the proposed encoder and decoder only have 0.8mW in PrimePower simulation.

#### (3) Awareness

The general encoder is usually suitable for several specific data stream or data property. For instance, Bus-Invert encoding scheme can only be used to acute data variability. Our proposed method can compare the result of all encoding functions in encoder and adaptively choose the optimal encoding scheme for different kinds of data types due to versatile applications.

## 1.2 Organization of the Thesis

In this thesis, the organization is as follows. In Chapter 1, we give a brief introduction for low power design. In Chapter 2, we propose a new power-aware codec design for data bus. The integrated processor including our proposed bus codec, and tool chains will be demonstrated in Chapter 3. The processor layout and simulated result are shown in Chapter 4. Finally, conclusions and future work are remarked in the last Chapter.

# **Chapter 2 Power-Aware Data Bus Codec**

We would present an adaptive data bus codec including proposal, architecture, and performance comparison with the features of low power, low cost, and awareness.

## 2.1 Motivation

As we know, there are two major sources of power dissipation in digital CMOS circuits, which are summarized as follows[8][9]

$$P = a \times C \times V^2 \times f + I_{leakage} \times V, \qquad (2-1)$$

Where P, C,  $\alpha$ , V, f denote power consumption, capacitance, transition activity, supply voltage, and clock frequency, respectively. The first and second terms represent the dynamic power and leakage power, respectively. In the second term, leakage current that can be arisen from substrate injection and sub-threshold effects is primarily determined by the fabrication technology.

For the reduction of dynamic power, the main design principle is to minimize the values of V, C, f and  $\alpha$  in Eq. (2-1) [10]. Among the four parameters, supply voltage V that has a quadratic effect and capacitance C are very efficient ways of decreasing the power dissipation. However, for CMOS circuits, the designers usually decrease V and C in layout level. For larger digital circuits and systems, decreasing V and C is an annoying problem in cell-based design. On the other hand, lowering the transition activity is a very promising way to reduce the power consumption in cell-based design.

Generally speaking, the percentage of power dissipation on bus is in the range of 10% and 80% for microprocessor. The category of bus is external bus and internal bus. External bus includes external memory data transmission and I/O data transmission. Internal bus includes internal memory, cache, and IP data transmission. The power dissipation in external busses usually is larger than that of internal busses by hundred times [8]. Thus, we are motivated to solve this critical power problem of data bus in architecture and logic level. In this paper, we propose a power-aware encoder and decoder to compress the data transition activity  $\alpha$ , and thus the power can be saved.

There are four properties in bus stream [11] discussed as follows.

- (1) Instruction address stream: Instructions addresses are often consecutive. As a result, instruction address stream is very predictable.

- (2) Data address stream: Data access may be consecutive while accessing arrays; otherwise, the data address stream is random. Although data addresses are less predictable, they still follow the principles of spatial and temporal locality.

- (3) Instruction stream: Most ISAs (Instruction Set Architecture) exhibit some regularity and instructions can be partitioned into fixed-location fields. As a result, Instruction stream is predictable by fixed-location fields.

- (4) Data stream: The sequence is not predictable. The values vary irregularly with different kinds of applications and different kinds of algorithms.

The above properties in bus stream have been widely applied to three off-the-shelf computer architectures.

(a) Harvard architecture with four busses:

Fig. 2-1. Harvard architecture with four busses.

Harvard architecture is a computer architecture with physically separate storage and signal pathways for instructions and data. Each address bus and data bus is only for instruction memory or data memory. As a result, each stream has independent bus and been easily controlled.

Fig. 2-2. von Neumann architecture with two busses.

The von Neumann architecture is a computer architecture that uses a single storage structure to hold both instructions and data. Instruction address stream and Data address stream are set on the same bus. Instruction stream and Data stream is so on.

(c) von Neumann architecture with one bus:

Fig. 2-3 von Neumann architecture with one bus.

All streams are running on the same bus. On this bus, it needs more signals to control stream operations.

### 2.2 Related Works

In this section, we would introduce the relative researches of low power bus encoding. From the beginning, we will have a brief subsection about Bus-Invert encoding. Bus-Invert encoding [12] is a traditional encoding at the early low power designs. It has the advantage of low cost hardware implementation. In Section 2.2.2, we will introduce Zero-Transition Activity encoding [15]. In Section 2.2.3, we will show a coding framework for low power address and data busses [16].

# 2.2.1 Bus-Invert Bus Encoding

We will consider the activity on a typical data bus to be characterized by a random uniformly distributed sequence of values [13][14]. The assumption of random uniformly distributed inputs is also conveniently made by most of the statistical power estimation methods. With this assumption for any given time-slot the data on an n-bit wide bus can be any of  $2^n$  possible values with equal probability. The average number of transitions per time slot will be n/2. For example on an eight-bit bus there will be

an average of 4 transitions per time-slot or 0.5 transitions per bus-line per time-slot. When all the bus-lines toggle at the same time (the probability of this happening in any time-slot is  $1/2^n$ ) there will be a maximum of n transitions in a time-slot and thus the worst power dissipation is proportional with n.

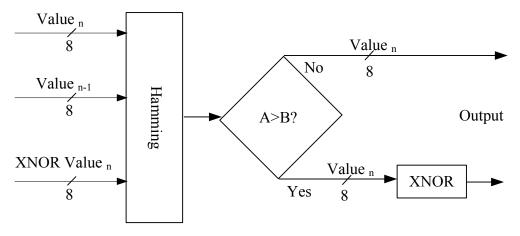

The Bus-Invert method [12] proposed here uses one extra control bit called invert. By convention then invert = 0 the bus value will equal the data value. When invert = 1 the bus value will be inverted. The worst power dissipation can then be decreased by half by coding the bus as follows (Bus-Invert method):

- (1) Compute the Hamming distance (the number of bits in which they differ) between the present bus value and the last data value.

- (2) If the Hamming distance is larger than n/2, set invert = 1 and make the present bus value equal to the inverted present data value.

- (3) Otherwise let invert = 0 and let the present bus value equal to the present data value.

- (4) At the decoder side, the contents of the bus must be conditionally inverted according to the invert line. In any case the value of invert must be transmitted over the bus (the method increases the number of bus lines from n to n + 1).

The Bus-Invert encoding has the advantage of that the maximum number of transitions per time-slot is reduced from n to n/2. Therefore the worst power dissipation for the bus is reduced by half. Fig. 2-4 shows the 16 bit data sequence using the Bus-Invert encoding in order to decrease the number of transitions.

Fig. 2-4. Bus-Invert Encoding.

We can see the Hamming distance between the data 0 and data 1 is smaller than 8, so invert =0. However the Hamming distance between the data 1 and data 2 is bigger than 8, so invert =1 and data 2 is inverted.

# 2.2.2 Zero-Transition Activity Encoding

The scheme we propose is related to the Bus-Invert encoding, both Bus-Invert encoding [12] and Zero-Transition Activity encoding [15] rely on the addition of a redundant line to reduce the total number of transitions that may happen when streams of patterns are transmitted over the bus. For example, Bus-Invert encoding use a redundant line INV that control data encoding for power reduction.

In Zero-Transition Activity encoding scheme, called the T0 code, is that of avoiding the transfer of consecutive addresses on the bus by using a redundant line, INC, to transfer to the receiving sub-system the information on the sequentially of the addresses. When two addresses in the stream to be transmitted are consecutive, the INC line is set to 1, the address bus lines are frozen (to avoid unnecessary switch activities), and the new address is computed directly by the receiver. On the other hand, when two addresses are not consecutive, the INC line is driven to 0 and the bus lines operate normally.

If all addresses of the ideal stream are consecutive, the INC line is always high, and the bus lines always have no transition. Consequently, the switch activity of our code is zero transitions per emitted consecutive address.

More formally, our Zero-Transition Activity encoding (T0 code) scheme can be described as follows Eq. (2-2):

$$(B(t), INC(t)) = \begin{cases} (B(t-1), 1) ; if \ t > 0 \ and \ b(t) = b(t-1) + S \\ (b(t), 0); \qquad otherwise \end{cases}, \tag{2-2}$$

where B(t) is the value on the encoded bus lines at time t JNC(t) is the additional bus line, b(t) is the address value at time t and S is a constant of increase, that we call stride. The corresponding decoding scheme can formally define as follows (2-3):

$$b(t) = \begin{cases} b(t-1) + S; & \text{if } INC = 1 \text{ and } t > 0 \\ B(t); & \text{if } INC = 0 \end{cases},$$

(2-3)

Notice that the T0 code retains its zero-transition property even if the addresses are incremented by a constant stride equal to a constant of two (as it is often the case for practical machines which are byte addressable, but that are able to access data or instructions aligned at word boundaries).

We take an example shows Zero-Transition Activity encoding following above equations (2-2) (2-3). Table 2-1 lists the switch activities with original data transfer, we can find the total transitions are 10 from cycle 0 to cycle 6. Table 2-2 lists the data transmission with Zero-Transition Activity encoding. At a given clock cycle t (t = [1,7] for table 2-2), the encoder computes the incremented address of cycle t and compares it to the address generated at cycle t - t . If the incremented old (t - t) address and the new (t) address are equal, the INC line is raised, and the old address is left on the bus. The encoder/decoder architecture is shown on Fig.2-5. The incrementer can be programmable, to be able to flexibly define the constant increment S. In Table 2-2, S is defined as 1.

The decoder architecture is simple. At any given clock cycle, the last cycle's

address is incremented. If the INC line is high, the old incremented value is used for addressing; otherwise, the value coming from the bus lines is selected. Finally, we can find the total transitions become 4. Zero-Transition Activity encoding make address value on bus be frozen when address is consecutive so that power dissipation will be reduced efficiently.

Fig. 2-5. Zero-Transition Activity encoder/decoder.

Table 2-1 Without Zero-Transition Activity Encoding

| Continuous bus address transition |                        |                |

|-----------------------------------|------------------------|----------------|

| cycle                             | Address to be transfer | Address on BUS |

| 0                                 | 00000000               | 00000000       |

| 1                                 | 00000001               | 00000001       |

| 2                                 | 00000010               | 00000010       |

| 3                                 | 00000011               | 00000011       |

| 4                                 | 00001000               | 00001000       |

| 5                                 | 00001001               | 00001001       |

| 6                                 | 00001010               | 00001010       |

| Тс                                | otal Transitions       | 10             |

Table 2-2 With Zero-Transition Activity Encoding

| Continuous bus address transition |                        |                |     |

|-----------------------------------|------------------------|----------------|-----|

| cycle                             | Address to be transfer | Address on BUS | INC |

| 0                                 | 00000000               | 00000000       | 0   |

| 1                                 | 00000001               | frozen         | 1   |

| 2                                 | 00000010               | frozen         | 1   |

| 3                                 | 00000011               | frozen         | 1   |

| 4                                 | 00001000               | 00001000       | 0   |

| 5                                 | 00001001               | frozen         | 1   |

| 6                                 | 00001010               | frozen         | 1   |

| То                                | Total Transitions 4    |                |     |

# 2.2.3 A Coding Framework for Low Power Address

## and Data Busses

In this section, we present a source-coding framework for describing low power encoding schemes and then employ the framework to develop new encoding schemes [16]. In the framework proposed here, a data source is processed first by a decorrelating function  $f_1$ . Next, a variant of entropy coding function  $f_2$  is employed, which reduces the transition activity.

Signal samples have higher probability of occurrence are assigned code words with fewer ON bits. This scheme is suited for the power dissipation depends on the number of ON bits. In VLSI systems, however, power dissipation depends on the number of transitions rather than thee number of ON bits.

A general communication system in Fig. 2-6 consists of a source coder, a channel coder, a noisy channel, a channel decoder, and a source decoder. The source coder (decoder) compresses (decompresses) the input data so that the number of bits required in the representation of the source is minimized. While the source coder removes redundancy, the channel coder adds just enough of it to combat errors that may arise due to the noise in the physical channel.

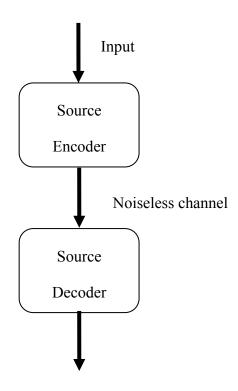

We consider the bus between two chips as the physical channel and the transmitter and receiver blocks to be a part of the pad circuitry, driving (in case of the transmitting chip) or detecting (in case of the receiving chip) the data signals. We will assume here that the signal levels are sufficiently high so that the channel can be considered as be noiseless. The noiseless channel assumption allows us to eliminate the channel coder resulting in the system shown in Fig. 2-7.

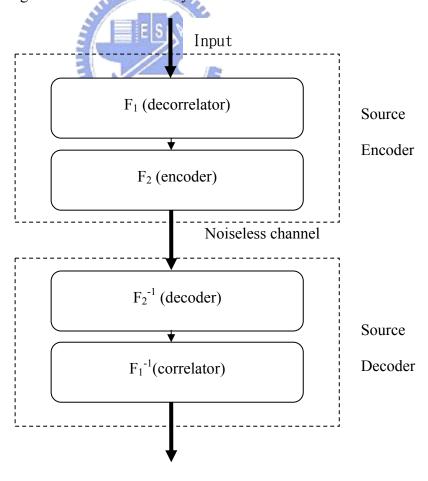

There have two functions  $f_1$ ,  $f_2$  in the source encoder shown in Fig. 2-8. The function  $f_1$  decorrelates the input so that all linear dependencies can been removed. The function  $f_2$  employs a variant of encoding whereby, instead of minimizing the average number of bits at the output, it reduces the average number of transitions.

Therefore, the function  $f_1$  decorrelates the input and adjusts the input probability distribution so that function  $f_2$  can reduce the transition activity by mapping encoding.

Fig. 2-6. A general communication system.

Fig. 2-7. A general communication system of noiseless channel.

Fig. 2-8. A Practical communication system of noiseless channel.

In this thesis, we choose the Difference-Based Mapping as the function  $f_1$ , the Probability-Based Mapping as the function  $f_2$ . In the later chapter, we will use this encoding method to compare with other encoding schemes including Bus-Invert, XOR, XNOR, proposed scheme.

The method of Difference-Based Mapping (dbm) is shown as follows Eq. 2-4. The x(n) is the input data, The prediction  $\hat{x}(n)$ , is a function of the past value of x(n). The dbm function returns the difference between x(n) and  $\hat{x}(n)$  properly adjusted so that the output fits in the available B bits.

if

$$(x(n) \ge \hat{x}(n) \& \& 2\hat{x}(n) \ge x(n))$$

$dbm = 2x(n) - 2\hat{x}(n);$

$else if (x(n) < \hat{x}(n) \& \& 2\hat{x}(n) - x(n) < 2^B)$

$dbm = 2x(n) - 2\hat{x}(n) - 1;$

$else if (\hat{x}(n) < 2^{B-1})$

$dbm = x(n);$

$else$

$dbm = 2^B - 1 - x(n);$

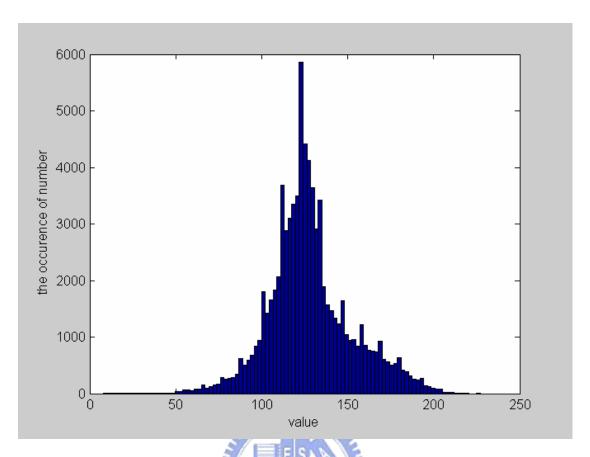

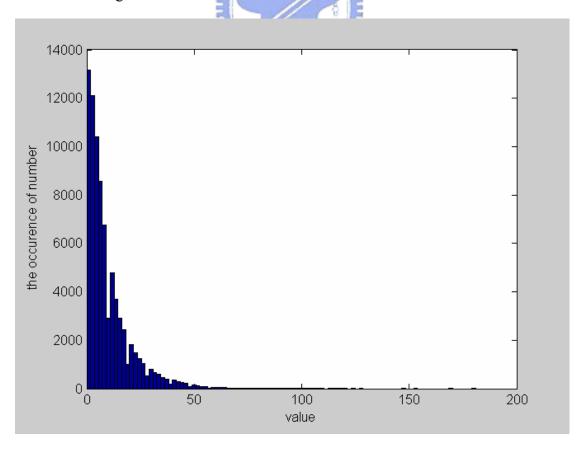

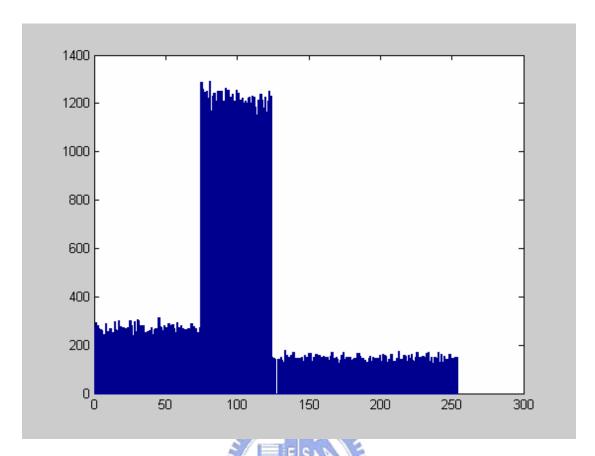

In the Difference-Based Mapping (dbm), we define four ranges for mapping,  $\{\hat{x}(n) < 2^{B-1}\}$ ,  $\{2\hat{x}(n) - 2^B \le x(n) \le \hat{x}(n)\}$ ,  $\{\hat{x}(n) < x(n) < 2\hat{x}(n)\}$ , and others. We can choose proper calculation according to four mapping ranges. For an example is listed in Table 2.3, we see that the dbm output is 0 when the current x(n) is equal to the previous  $\hat{x}(n)$  and the output value increases as the distance between the current x(n) and previous  $\hat{x}(n)$  increases. The goal of dbm is convert the total data distribution to close to 0 so that the number of transitions would be reduced. We see the occurrence distribution at the output of dbm for EEG 8 bits data is shown in

Fig. 2-9 and Fig. 2-10. The dbm skew the original distribution for most of the data sets and hence enable function f2, Probability-Based Mapping (pbm) to reduce the number of transitions even more.

Table 2-3 Example of Difference-Based Mapping (dbm)

| $\hat{\mathbf{x}}(\mathbf{n})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | X(n)    | $Dbm(x(n), \hat{x}(n))$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------------|