# 國 立 交 通 大 學 電子工程學系電子研究所

# 博士論文

以交連線為中心加強系統晶片可測試性及良率 之震盪環結構與演算法

## Interconnect-Centric Oscillation Ring Architectures and Algorithms for SoC Testability and Yield Enhancement

研究生:李淑敏 指導教授:李崇仁 博士

中華民國九十五 年 一 月

i

Copyright by KatherineShu-Min Li 2006

## INTERCONNECT-CENTRIC OSCILLATION RING ARCHITECTURES AND ALGORITHMS FOR SOC TESTABILITY AND YIELD ENHANCEMENT

by

Katherine Shu-Min Li, B.S., M.S.

DISSERTATION

Presented to the Faculty of the Graduate School of National Chiao Tung University in Partial Fulfillment of the Requirements for the Degree of

### **DOCTOR OF PHILOSOPHY**

#### NATIONAL CHIAO TUNG UNIVERSITY AT HSINCHU

January 2006

To my parents, Yoan-Jian Lee and Ru-Huai Xue.

### 摘要

交連線在深次微米及奈米技術中日益重要,因此,交連線的可測試性 及良率之問題引起眾多學者投入研究。本博士論文是以震盪環測試結構與 演算法(Oscillation Ring Architectures and Algorithms)來 解決交連線的可測試性及良率之問題。我們所提出的震盪環測試機制符合 IEEE1500標準並用以測試與診斷系統單晶片 (System on Chip, SoC)的交 連線。

我們面對兩項技術挑戰,第一項、設計複雜度使得交連線的可測試 性及良率之問題不可避免。第二項、串音雜訊使得交連線的訊號整合性及 延遲錯誤之問題受到重視。

為了面對第一項設計複雜度的挑戰,我們的作法是將震盪環測試機 制嵌入多接繞線器中以增進交連線的可測試性,並且提出以降低與平均繞 線壅塞度的方法來增進交連線的良率之問題。

為了面對第二項交連線的訊號整合性及延遲錯誤的挑戰,我們的作 法是進行一些基礎分析與研究,茲列舉如下。

- (1)為了建立交連線震盪環結構與演算法的分析架構,我們擴充 早先可在交連線上加入緩衝器的研究,所以我們所提出的震 盪環測試機制是可與常用的緩衝器加入技術(buffer insertion)相容。

- (2)為了測試交連線的訊號整合性及延遲錯誤,我們提出交連線 串音整合偵測機制,其作法是不直接測試延遲錯誤,而是利 用串音突波與串音延遲的關係來直接測試串音突波。為了證

v

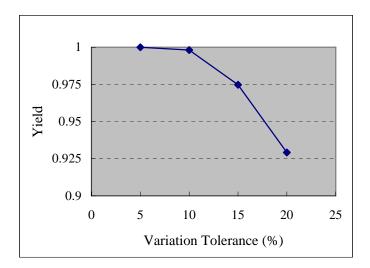

明此測試機制的有效性,我們以蒙地卡羅模擬來說明此機制 即使在百分之二十的製程飄移下仍達成百分之九十二以上 的測試良率。此處所發展的串音突波偵測器電路設計可用於 交連線震盪環測試結構中。

- (3)為了提高交連線的可測試性,提出交連線震盪環測試結構與 演算法。我們先提出基本的測試方法論,再進一步提出另一 個交連線診斷與最佳化的方法與技術。

- (4)最後我們將交連線震盪環結構與演算法加以修改應用到全 晶片繞線器上以及同步序向電路中。

本博士論文提出以交連線為中心加強系統晶片可測試性及良率之震盪 環結構與演算法來解決交連線的可測試性及良率之問題。綜結以上各觀 點,完成了五篇國際論文與提交了六篇期刊論文。

## INTERCONNECT-CENTRIC OSCILLATION RING ARCHITECTURES AND ALGORITHMS FOR SOC TESTABILITY AND YIELD ENHANCEMENT

Katherine Shu-Min Li, Ph.D.

National Chiao Tung University, 2006

Supervisor: Dr. Chung-Len Lee

Interconnects play a dominant role in deep-submicron and nanotechnologies. As a result, testability and yield problems of interconnects attract increasing attention.

The paradigm shift of the interconnect-related problems is indispensable to cope with two major challenges as technology advances into nanometer territory:

- The ever increasing design complexity of gigascale integration renders *testability* (*detection and diagnosability*) and *yield enhancement* inevitable.

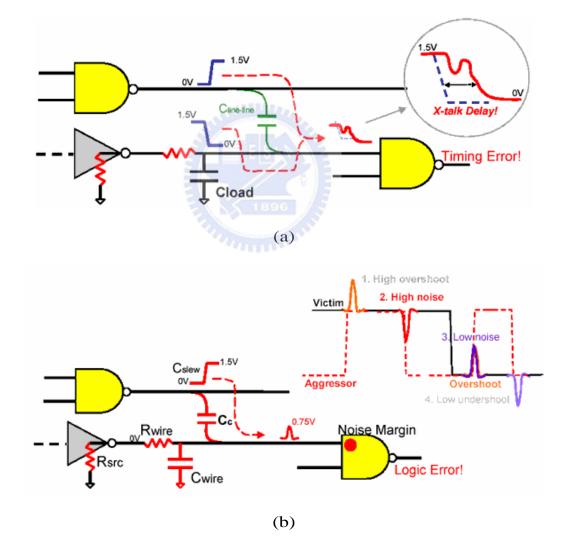

- The complicated physical effects inherent from the scaling effects in nanoscale technology make *crosstalk noise* (*crosstalk-induced glitch faults* and *crosstalk-induced delay*) inevitable, and thus *signal integrity* and *delay faults* can no long be ignored.

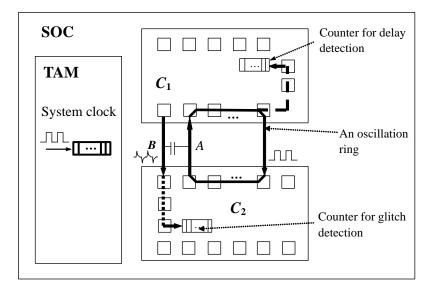

The motivation of this research is targeted at testability and yield enhancement with test time reduction at design stages by our proposed <u>O</u>scillation <u>R</u>ing (OR) test mechanism. These advantages of the oscillation ring test mechanism have made interconnects detectable and diagnosable through a systematic graph modeling approach. As a relatively novel methodology, OR mechanism for system-level interconnects should be compliant to IEEE Std. 1500. Thus, it is desirable to consider test architectures and algorithms for interconnect testing for System on Chip (SoC) under IEEE Std. 1500, and develop interconnect-centric computer-aided-design tools including design, detection, and diagnosis.

To handle the first challenge, the ever increasing design complexity of gigascale integration, we integrate our proposed oscillation ring test techniques into a signal-integrity-aware router. We propose an integrated multilevel full-chip routing algorithm that improves testability and diagnosability, manufacturability, and signal integrity for yield enhancement. Two major issues are addressed.

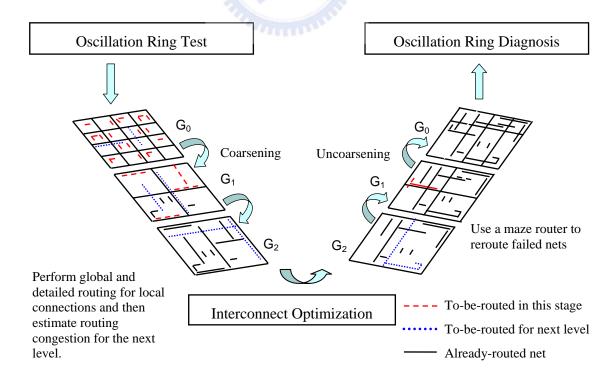

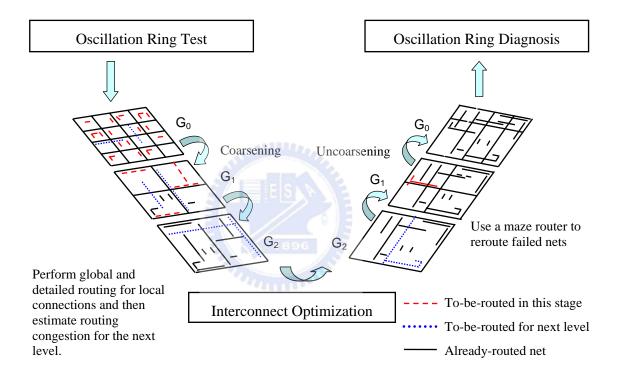

(1) An oscillation ring test and diagnosis scheme for interconnects, based on IEEE Std. 1500, is integrated into the multilevel routing framework to achieve testability enhancement. We augment the traditional multilevel framework by introducing a preprocessing stage of Interconnect Oscillation Ring Detection (*IORT*) that analyzes the oscillation ring structure for better resource estimation before the coarsening stage, and a postprocessing (final) stage of Interconnect Oscillation Ring Diagnosis (*IORD*) after uncoarsening that improves testability to achieve 100% interconnect fault coverage and maximal diagnosability.

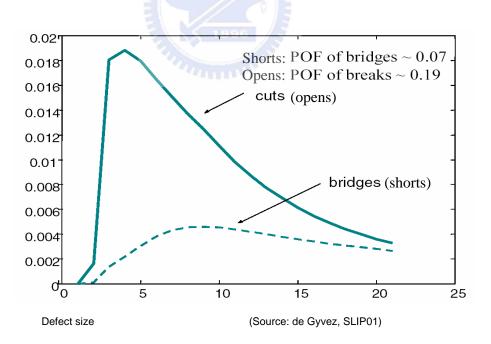

(2) We present a heuristic to balance routing congestion, and the goals of this router include minimizing multiple-fault probability, reducing crosstalk effects, and improving chemical-mechanical-polishing vield for both (CMP) and optical-proximity-correction (OPC) induced manufacturability problems. Experimental results on the MCNC benchmark circuits demonstrate that the proposed OR method achieves 100% fault coverage and the optimal diagnosis resolution for interconnects, and the multilevel congestion-driven routing algorithm effectively balances the routing density to achieve 100% routing completion. Experimental

viii

results show that our method significantly improves routing quality for testability and yield enhancement.

To deal with the second challenge for signal integrity problem, the crosstalk-induced faults have caused significant impact on interconnect performance as technology advances into nanometer era. The crosstalk is a phenomenon of parasitic capacitance caused by continuous scaling effects. It directly influences reliability, manufacturability and yield of VLSI circuits.

- (1) We present buffer planning techniques for designing and analyzing crosstalk noise together with performance during floorplanning, and show theoretically and experimentally that our interconnect-aware floorplanner outperforms currently available ones with simultaneously considering crosstalk and timing as our preliminary work which paves the base for *IORT* and *IORD*.

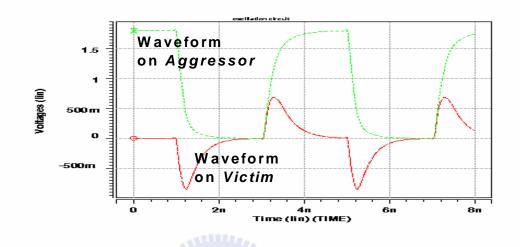

- (2) There are two types of crosstalk: crosstalk-induced glitch and crosstalk-induced delay. We analyze and design the detection of crosstalk faults for interconnect bus, and show experimentally that the unified detection scheme for crosstalk-induced glitch and crosstalk-induced delay is feasible and effectively. This scheme is based on a built-in pulse detector with an adjustable threshold voltage, and we show that this design works well under process variations.

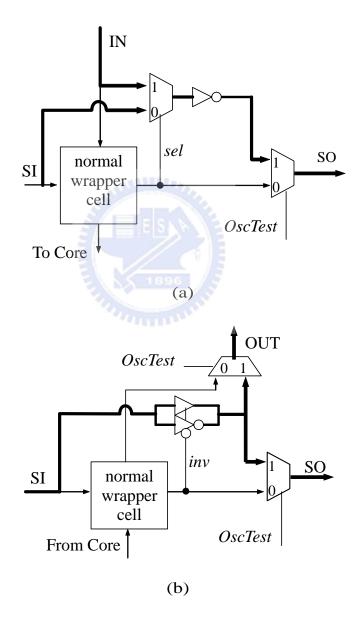

Furthermore, the pulse detector in the crosstalk unified detection scheme is embedded into IEEE Std. 1500 wrapper compliant cells so that oscillation ring test for the interconnect test can handle the delay fault, which poses challenges to system performance.

(3) We study interconnect detection and diagnosis problems for interconnects. We show a class of oscillation ring approximation algorithms for an interconnect detection and diagnosis problem and prove that oscillation ring mechanism with IEEE Std. 1500 compliant test architecture guarantees 100% fault detection (by *IORT*) and the optimal diagnosis resolution (by *IORD*) not only under the fault models of traditional stuck-at and open faults, but also delay and crosstalk glitch faults. Solutions to the interconnect problems by applying oscillation ring methodology pave the way for developing a novel integrated multilevel routing framework with a congestion metric for routing as mentioned above.

(4) Finally, the oscillation ring test method has been successfully modified and applied to synchronous sequential circuits to facilitate at-speed test for delay fault detectable in addition to traditional stuck-at and open fault models.

In summary, both testability and signal integrity issues have significant impact on interconnect design and test. In my PhD dissertation, an interconnect-centric oscillation ring architectures and algorithms targeted for SoC testability and yield enhancement is proposed to deal with system-level interconnect test and diagnosis, full-chip integrated multilevel router framework, and RTL (register transfer level) synchronous sequential circuits for at-speed testability.

## Acknowledgements

I am greatly indebted to my thesis advisor, Professor Chung Len Lee, for his tremendous support, encouragement, and guidance throughout my graduate study. Many discussions with him helped me progress in the right directions. I am also very grateful to him and Ms. Lee, also known as Prof. Hsu, for their help in many other matters, academically and socially. I would like to thank Professor Chauchin Su, Professor Yao-Wen Chang, for inviting me to join in their research groups and to be exposed to the bright research environments. They provided me with invaluable advice and encouragement. I wish to thank Professor Jwu E Chen in Department of Electrical Engineering of National Central University for his constant, immense encouragement and support, and inviting me to join multiple participation of EDA Forum between Academia and Industries.

I greatly appreciate the members of my dissertation committee. Professors Shih-Chieh Chang, Tsin-Yuan Chang, Yao-Wen Chang, Jwu E Chen, Chung-Len Lee, Jing-Yang Jou, Chauchin Su and Chen-Wen Wu for their interest in my work, for their invaluable comments and suggestions, and for their kind assistance in many occasions.

Thanks are due to all members of the SoC Testing & DFT group for providing a forum to discuss my research. Specifically, I wish to thank Dr. Wen-Ching Wu and Dr. Yeong-Jar Chang, Prof. Soon-Jyh Chang, Ming-Sheu Wu, Sheu Ping Lin. I especially appreciate Yoyo Chang at the department's Graduate Office for her professional assistance in all administrative and project matters.

Special thanks go to EDA Lab leading by Professor Yao-Wen Chang including Dr. Tsung-Yi Ho, Tai-Chen Chen, Tung-Chen Chen of National Taiwan University for their pioneering work on Routing and for providing me with the LEDA packages for my comparative studies.

Also special thanks go to Mixed-Signal Circuit Lab leading by Professor Chauchin Su for all the valuable discussion about circuit related characteristics with Hung Wen Lu, Hung Kai Chen, Ren-Qian Xu, Yu Hwai Tseng in Department of Electrical and Control Engineering of National Chiao Tung University.

Thanks also go to many wonderful friends who made my life in Hsin Chu so pleasant and unforgettable. Especially, I would like to express my appreciation to Prof. Pu Hsu for her assistance and support. Also, many thanks to my co-labs and classmates in SoC Testing & DFT Lab in Department of Electronics Engineering, National Chiao Tung University and EDA Lab in Department of Electrical Engineering, National Taiwan University (also previously known as VLSI&EDA Lab in Department of Computer and Information Science, Chiao Tung University).

My deepest appreciation goes to my parents, sisters and brothers for their unending love and support, and my uncle Yuan-Cai Lee and aunt Li-Zhou Gao, uncle Ru-Mao Xue and aunt Mei-Yun Zheng for their encouragement and help. Last, but not least. I am very grateful to the rest of my family: without their sacrifices and patience, the completion of this thesis would not have been possible.

> Katherine Shu-Min Li National Chiao Tung University January 2006

## **Table of Contents**

| Chi  | nese Al | ostract                                                                                                                                        |    | v    |

|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|----|------|

| Eng  | lish Ab | ostract                                                                                                                                        |    | vii  |

| Ack  | nowled  | lgements                                                                                                                                       |    | xi   |

| Tab  | le of C | ontents                                                                                                                                        |    | xiii |

| List | of Tab  | les                                                                                                                                            | X  | viii |

| List | of Fig  | ures                                                                                                                                           |    | xix  |

| Cha  | pter 1. | Introduction                                                                                                                                   |    | 1    |

| 1.1  | Interco | onnect-Centric Study vs. Oscillation Ring Test Methodology                                                                                     | 1  |      |

| 1.2  | Challe  | nges of Interconnect-Centric Research                                                                                                          | 4  |      |

| 1.3  | Interco | onnect Issues in Design and Test Process                                                                                                       | 8  |      |

| 1.4  | Overvi  | iew of the Dissertation                                                                                                                        | 11 |      |

|      | 1.4.1   | A unified approach to detecting and optimizing                                                                                                 | 12 |      |

|      | 1.4.2   | IEEE Standard 1500 Compatible Interconnect Delay and<br>Crosstalk Test Methodology                                                             | 12 |      |

|      | 1.4.3   | IEEE Standard 1500 Compilant Interconnect Diagnosis for<br>Delay and Crosstalk Glitch Faults                                                   | 14 |      |

|      | 1.4.4   | Oscillation Test for Synchronous Sequential Circuits (also<br>known as Finite State Machine Synthesis for At-Speed<br>Oscillation Testability) | 15 |      |

|      | 1.4.5   | Multilevel Full-Chip Routing with Testability and Yield<br>Enhancement                                                                         | 16 |      |

| 1.5  | Organ   | ization of the Dissertation                                                                                                                    | 18 |      |

| Cha  | pter 2. | Preliminaries                                                                                                                                  |    | 20   |

| 2.1  | Interco | onnect Models                                                                                                                                  | 20 |      |

|      | 2.1.1   | Interconnect Model for Detection                                                                                                               | 20 |      |

|      | 2.1.2   | Interconnect Model for Diagnosis                                                                                                               | 22 |      |

| 2.2  | Oscilla | ation Ring Test Methodology                                                                                                                    | 24 |      |

|      | 2.2.1   | Oscillation Ring Test Architecture & Operations                                                                                                | 24 |      |

|     | 2.2.2    | 2.1 Effectiveness for Delay Fault                                                           | 26 |    |

|-----|----------|---------------------------------------------------------------------------------------------|----|----|

|     | 2.2.2    | 2.2 Effectiveness for Crosstalk Faults                                                      | 27 |    |

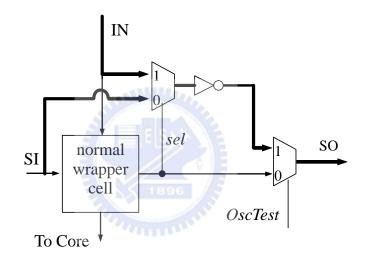

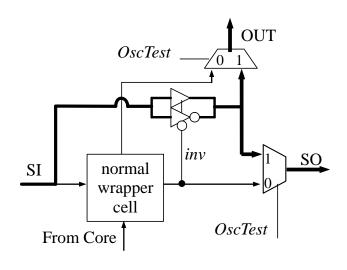

|     | 2.2.3    | IEEE 1500 Compliant Wrapper Cell Design                                                     | 30 |    |

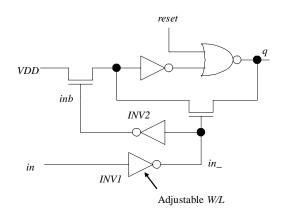

|     | 2.2.2    | 3.1 Pulse Detector                                                                          | 30 |    |

|     | 2.2.2    | 3.2 Wrapper Cell with Embedded Pulse Detector                                               | 31 |    |

|     | 2.2.4    | Delay Measurement Formula                                                                   | 34 |    |

| 2.3 | Interco  | onnect-driven Floorplanning                                                                 | 34 |    |

|     | 2.3.1    | Crosstalk Noise and Signal Integrity                                                        | 35 |    |

|     | 2.3.2    | System-Level Framework for Oscillation Ring Test                                            | 38 |    |

| 2.4 | Interco  | nnect-driven Routing                                                                        | 38 |    |

|     | 2.4.1    | Applications of the Oscillation Ring Test Methodology as a DFT technique                    | 39 |    |

|     | 2.4.2    | Congestion vs. Design for Yield                                                             | 40 |    |

|     | 2.4.3    | Multilevel Routing Framework                                                                | 40 |    |

|     | 2.4.4    | Our Integrated Multilevel Routing Framework                                                 | 42 |    |

| 2.5 | Assun    | ptions and Limitations                                                                      | 43 |    |

| 2.6 | Interco  | onnect-Centric Detection and Diagnosis Techniques                                           | 43 |    |

|     | 2.6.1    | Interconnect Detection Technology                                                           | 44 |    |

|     | 2.6.2    | Interconnect Diagnosis Technology                                                           | 45 |    |

|     | 2.6.3    | Summary of Interconnect Technologies.                                                       | 45 |    |

| 2.7 | Previo   | us Works                                                                                    | 46 |    |

|     | 2.7.1    | Interconnect Detection and Diagnosis Architectures & Algorithms                             | 46 |    |

|     | 2.7.2    | Oscillation Test Schemes                                                                    | 48 |    |

|     |          | 2.7.2.1 Analog and Mixed Signal Domain                                                      | 49 |    |

|     |          | 2.7.2.2 Digital Domain                                                                      | 49 |    |

| Cha | apter 3. | A Unified Approach to Detecting Crosstalk Faults of<br>Interconnects in Deep Submicron VLSI |    | 51 |

| 3.1 | Introd   | uction                                                                                      | 52 |    |

| 3.2 | The C    | rosstalk Detection Analysis Problem                                                         | 53 |    |

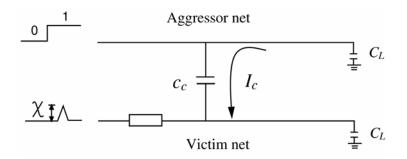

|     | 3.2.1 0  | Circuit Model for Crosstalk                                                                 | 53 |    |

|     | 3.2.2.   | Crosstalk Fault Effects                                                                     | 55 |    |

| 3.3 |          | sis to Relationships between Crosstalk-Induced Glitches and alk-Induced Delay               | 59 |    |

|     | 3.3.1 (                                                                                          | Glitch vs. Delay                                                                                               | 59  |    |

|-----|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|----|

| 3.4 | Pulse                                                                                            | Detector with Adjustable Detection Threshold                                                                   | 61  |    |

| 3.5 | Some                                                                                             | Considerations for Unified Detection Scheme                                                                    | 63  |    |

|     | 3.5.1                                                                                            | Glitch Amplitude and Width                                                                                     | 63  |    |

|     | 3.5.2                                                                                            | Effect of Skew between Aggressor and Victim Signals                                                            | 65  |    |

|     | 3.5.3                                                                                            | Process Variation Effect on Pulse Detector                                                                     | 66  |    |

| 3.6 | 1                                                                                                | imental Results of Monte Carlo Simulation on Unified<br>tion Scheme Considering Process Variations             | 67  |    |

| Cha | npter 4                                                                                          | . IEEE Standard 1500 Compatible Oscillation Ring<br>Based Interconnect Delay and Crosstalk Test<br>Methodology |     | 71 |

| 4.1 | Introd                                                                                           | uction                                                                                                         | 71  |    |

| 4.2 | Interc                                                                                           | onnect Test Architecture for Oscillation Ring Test                                                             | 75  |    |

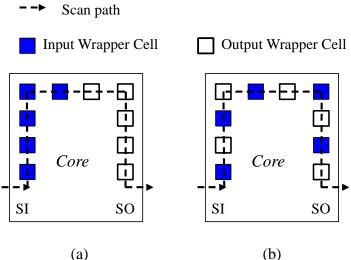

| 4.3 | IEEE                                                                                             | Standard 1500 Compliant Modified Wrapper Cell Design                                                           | 77  |    |

| 4.4 | Oscill                                                                                           | ation Ring Construction: Model and Analysis                                                                    | 80  |    |

|     | 4.4.1                                                                                            | Graph Model for Oscillation Ring Tests                                                                         | 82  |    |

|     | 4.4.2                                                                                            | Analysis of Rings and Test Cost                                                                                | 84  |    |

| 4.5 | Oscill                                                                                           | ation Ring Construction Algorithm                                                                              | 86  |    |

|     | 4.5.1                                                                                            | Exact Algorithm                                                                                                | 86  |    |

|     | 4.5.2                                                                                            | Ring Generation Algorithm: A Heuristic Algorithm                                                               | 87  |    |

| 4.6 | Exper                                                                                            | imental Results                                                                                                | 89  |    |

|     | 4.6.1                                                                                            | Simulated Results on HP benchmark circuit                                                                      | 90  |    |

|     | 4.6.2                                                                                            | Oscillation Ring Generation for Interconnect Detection<br>Algorithm                                            | 93  |    |

| Cha | Chapter 5. IEEE Standard 1500 Compliant Interconnect Diagnosis<br>for Delay and Crosstalk Faults |                                                                                                                |     | 99 |

| 5.1 | Introd                                                                                           | uction                                                                                                         | 100 |    |

| 5.2 | Oscill                                                                                           | ation Ring Test Scheme for Interconnect Diagnosis                                                              | 104 |    |

|     | 5.2.1                                                                                            | Oscillation Test Architecture                                                                                  | 104 |    |

|     | 5.2.2                                                                                            | Enhanced IEEE Standard 1500 Compliant Wrapper Cell<br>Design                                                   | 107 |    |

|     | 5.2.3                                                                                            | Crosstalk Glitch Detection                                                                                     | 108 |    |

|     | 5.2.4                                                                                            | Interconnect Graph Models                                                                                      | 110 |    |

|     | 5.2.5                                                                                            | Motivation and Problem Formulation                                                                             | 113 |    |

|                                   | 5.2.5.1 Problem Complexity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 113                                                  |

|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|                                   | 5.2.5.2 Problem Formulation and Constraints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 114                                                  |

| 5.3                               | Interconnect Diagnosability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 116                                                  |

|                                   | 5.3.1 Diagnosability Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 116                                                  |

|                                   | 5.3.2 Heuristic Diagnosability Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 119                                                  |

|                                   | 5.3.3 Number of Test                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 123                                                  |

| 5.4                               | Interconnect Diagnosis Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 125                                                  |

|                                   | 5.4.1 Fast Heuristic Diagnosability Check                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 125                                                  |

|                                   | 5.4.2 Interconnect Oscillation Ring Construction for Fault Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 126                                                  |

|                                   | 5.4.3 Interconnect Oscillation Ring Generation for Fault Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127                                                  |

| 5.5                               | Optimization Techniques for Interconnect Diagnosis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 129                                                  |

|                                   | 5.5.1 Concurrent Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 129                                                  |

|                                   | 5.5.2 Adaptive Tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 132                                                  |

| 5.6                               | Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133                                                  |

|                                   | 5.6.1 Comparison between Predetermined and Adaptive Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 133                                                  |

|                                   | 5.6.2 Comparison between Predetermined and Concurrent Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 136                                                  |

|                                   | 5.6.3 Comparison between Theoretical Bounds and Experimental                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                      |

|                                   | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137                                                  |

| Cha                               | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 137<br><b>140</b>                                    |

| <b>Cha</b><br>6.1                 | apter 6. Oscillation Test for Synchronous Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                      |

| 6.1                               | apter 6. Oscillation Test for Synchronous Sequential Circuits<br>Introduction to Finite State Machine Synthesis for At-Speed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 140                                                  |

| 6.1                               | apter 6. Oscillation Test for Synchronous Sequential Circuits<br>Introduction to Finite State Machine Synthesis for At-Speed<br>Oscillation Testability                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>140</b>                                           |

| 6.1                               | apter 6.Oscillation Test for Synchronous Sequential CircuitsIntroduction to Finite State Machine Synthesis for At-Speed<br>Oscillation TestabilityProblem Formulation: Oscillation Test for Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                                             | <b>140</b><br>140<br>143                             |

| 6.1                               | apter 6.Oscillation Test for Synchronous Sequential CircuitsIntroduction to Finite State Machine Synthesis for At-Speed<br>Oscillation TestabilityProblem Formulation: Oscillation Test for Sequential Circuits6.2.1Oscillation Ring Test Architecture at Logic Level                                                                                                                                                                                                                                                                                                                                                       | <b>140</b><br>143<br>143<br>146                      |

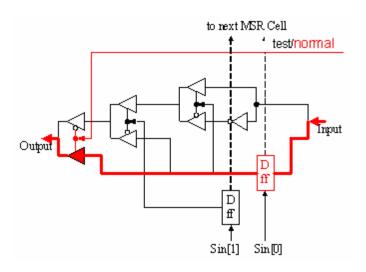

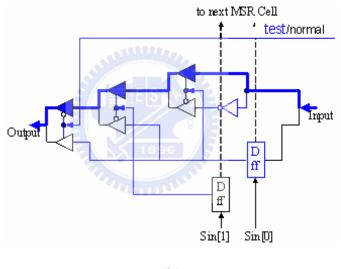

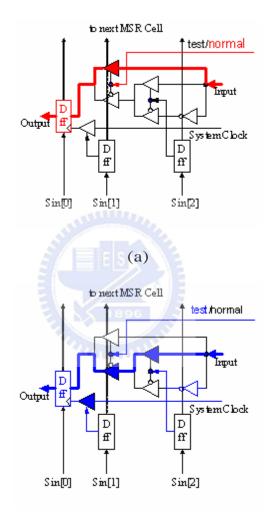

| 6.1                               | <ul> <li>apter 6. Oscillation Test for Synchronous Sequential Circuits</li> <li>Introduction to Finite State Machine Synthesis for At-Speed</li> <li>Oscillation Testability</li> <li>Problem Formulation: Oscillation Test for Sequential Circuits</li> <li>6.2.1 Oscillation Ring Test Architecture at Logic Level</li> <li>6.2.2 Modified State Register Design</li> <li>6.2.1 Modified State Register Design for Asynchronous</li> </ul>                                                                                                                                                                                | <b>140</b><br>143<br>143<br>146                      |

| 6.1                               | <ul> <li>apter 6. Oscillation Test for Synchronous Sequential Circuits</li> <li>Introduction to Finite State Machine Synthesis for At-Speed</li> <li>Oscillation Testability</li> <li>Problem Formulation: Oscillation Test for Sequential Circuits</li> <li>6.2.1 Oscillation Ring Test Architecture at Logic Level</li> <li>6.2.2 Modified State Register Design</li> <li>6.2.2.1 Modified State Register Design for Asynchronous Test.</li> <li>6.2.2.2 Modified State Register Design for Synchronous Circuits</li> </ul>                                                                                               | 140<br>143<br>143<br>146<br>146                      |

| <ul><li>6.1</li><li>6.2</li></ul> | <ul> <li>apter 6. Oscillation Test for Synchronous Sequential Circuits</li> <li>Introduction to Finite State Machine Synthesis for At-Speed</li> <li>Oscillation Testability</li> <li>Problem Formulation: Oscillation Test for Sequential Circuits</li> <li>6.2.1 Oscillation Ring Test Architecture at Logic Level</li> <li>6.2.2 Modified State Register Design</li> <li>6.2.2.1 Modified State Register Design for Asynchronous Test</li> <li>6.2.2.2 Modified State Register Design for Synchronous Circuits</li> </ul>                                                                                                | 140<br>143<br>143<br>146<br>146<br>148               |

| <ul><li>6.1</li><li>6.2</li></ul> | apter 6.       Oscillation Test for Synchronous Sequential Circuits         Introduction to Finite State Machine Synthesis for At-Speed       Oscillation Testability         Problem Formulation: Oscillation Test for Sequential Circuits       6.2.1         6.2.1       Oscillation Ring Test Architecture at Logic Level         6.2.2       Modified State Register Design         6.2.2.1       Modified State Register Design for Asynchronous Test         6.2.2.2       Modified State Register Design for Synchronous Circuits         Synchronous Oscillation Ring Test       Synchronous Oscillation Ring Test | 140<br>143<br>143<br>146<br>146<br>148<br>149        |

| <ul><li>6.1</li><li>6.2</li></ul> | apter 6.       Oscillation Test for Synchronous Sequential Circuits         Introduction to Finite State Machine Synthesis for At-Speed       Oscillation Testability         Problem Formulation: Oscillation Test for Sequential Circuits                                                                                                                                                                                                                                                                                                                                                                                 | 140<br>143<br>143<br>146<br>146<br>148<br>149<br>149 |

| Cha          | pter 7.                | Multilevel Full-Chip Routing with Testability and Yield<br>Enhancement                          | 160 |

|--------------|------------------------|-------------------------------------------------------------------------------------------------|-----|

| 7.1          | Introdu                | uction                                                                                          | 161 |

| 7.2          | Prelim                 | inaries                                                                                         | 168 |

|              | 7.2.1                  | OR Test Architecture for Interconnects                                                          | 168 |

|              | 7.2.2                  | Process Variation Effects on Oscillation Signals                                                | 170 |

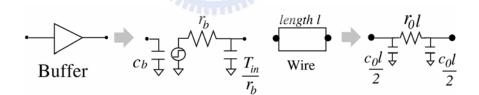

|              | 7.2.3                  | Interconnect Models in Oscillation Ring Test                                                    | 171 |

|              | 7.2.4                  | Interconnect Diagnosis Model with Oscillation Ring Tests                                        | 172 |

|              | 7.2.5                  | Chemical Mechanic Polishing Model                                                               | 173 |

|              | 7.2.6                  | Signal Integrity                                                                                | 174 |

| 7.3          | Multil                 | evel Routing Framework                                                                          | 176 |

|              | 7.3.1                  | Routing Model                                                                                   | 176 |

|              | 7.3.2                  | Testability-Aware Multilevel Routing                                                            | 178 |

|              | 7.3.3                  | Diagnosability-Aware Routing Structure                                                          | 178 |

|              | 7.3.4                  | Cost Metric for Routing Density Control                                                         | 181 |

| 7.4          | Experi                 | mental Results                                                                                  | 184 |

|              | 7.4.1                  | Testability Enhancement                                                                         | 184 |

|              | 7.4.2                  | Congestion Control for Multi-objective Optimization                                             | 187 |

| Cha          | Chapter 8. Conclusions |                                                                                                 |     |

| 8.1          |                        | Fied Approach to Detecting Crosstalk Faults of Interconnects in Submicron VLSI                  | 193 |

| 8.2          |                        | Standard 1500 Compatible Oscillation Ring Based Interconnect<br>and Crosstalk Test Methodology  | 194 |

| 8.3          |                        | Standard 1500 Compliant Oscillation Ring Based Interconnect osis for Delay and Crosstalk Faults | 195 |

| 8.4          | Oscilla                | tion Ring Test for Synchronous Sequential Circuits                                              | 195 |

| 8.5          |                        | evel Full-Chip Routing with Testability and Yield cement                                        | 196 |

| 8.6          | Future                 | Work                                                                                            | 196 |

| Bibliography |                        |                                                                                                 | 199 |

| Vita             | 208 |

|------------------|-----|

| Publication List | 209 |

## List of Tables

| 2.1 | Control signals for the modified input wrapper cell                                                                   | 3  |

|-----|-----------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Control signals for the modified output wrapper cell                                                                  | 3  |

| 4.1 | Control signals for the modified input wrapper cell (also same as Table 2.1)                                          | 7  |

| 4.2 | Control signals for the modified output wrapper cell (also same as Table 2.2)                                         | 7  |

| 4.3 | Comparison between the number of rings generated for experimental and theoretical results of Lower Bounds             | 9  |

| 4.4 | Analysis of Ring Length Characteristics                                                                               | 9  |

| 5.1 | Experimental results for Interconnect Diagnosis both for Predetermined and Adaptive Methods                           | 13 |

| 5.2 | Comparison between Predetermined and Concurrent Methods                                                               | 13 |

| 5.3 | Comparison of number of test rings between theoretical bounds and experimental results.                               | 13 |

| 6.1 | Statistics of benchmark circuits                                                                                      | 15 |

| 6.2 | Experimental comparison between our proposed oscillation test generation and pure scan methods.                       | 15 |

| 7.1 | Experimental Results based on the MCNC benchmarks for testability enhancement of interconnect detection and diagnosis | 18 |

| 7.2 | Routing benchmark circuits                                                                                            | 18 |

| 7.3 | Comparison of routing results of maximum density with both maximum delay and average delay                            | 19 |

| 7.4 | Comparison of routing results of statistical density with Lin's in ICCAD 2002                                         | 19 |

| 7.5 | Comparison of routing results of statistical density with Ho's in ICCAD 2003                                          | 19 |

## **List of Figures**

| 1.1  | Interconnect (a) Moore's Law, (b) Scaling effects on memory and microprocessor. ( <i>Source</i> : Intel for (a); <i>Source</i> : <i>Intel at ISSCC</i> -03 for (b))                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | For 90 nm technology, interconnect delay will account for <b>75%</b> of the overall delay. ( <i>Source: Cadence Design System</i> )                                                                                                                 |

| 1.3  | Important effects of global interconnects (Source: Tutorial of ICCAD'00)                                                                                                                                                                            |

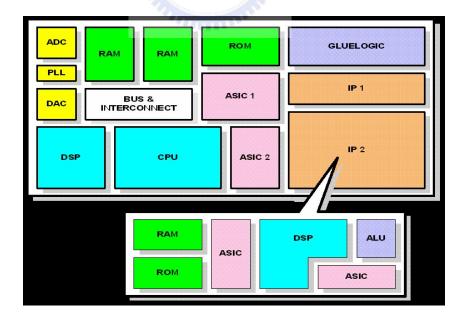

| 1.4  | An SoC circuit. (Source: on the courtesy of Prof. K. –J. Lee)                                                                                                                                                                                       |

| 1.5  | Crosstalk Effects (a) Crosstalk-induced Delay, (b) Crosstalk-induced Glitch. (Source: Magma Design Automation, Inc.)                                                                                                                                |

| 1.6  | Comparison of probability of faults between short and open faults (Source: de Gyvez, SLIP01)                                                                                                                                                        |

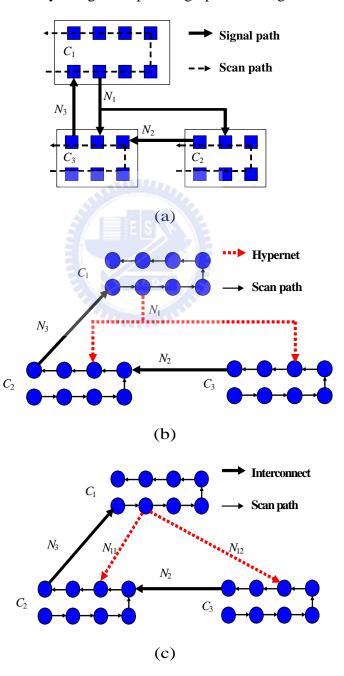

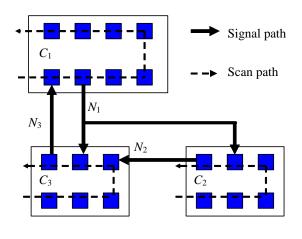

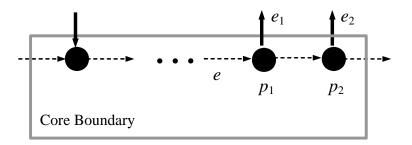

| 2.1  | (a) The interconnect diagram for SoC, (b) hypernet graph, (c) interconnect graph model with 2-pin nets for detection.                                                                                                                               |

| 2.2  | Graph model for delay faults.                                                                                                                                                                                                                       |

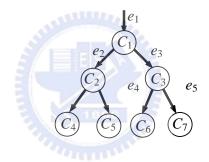

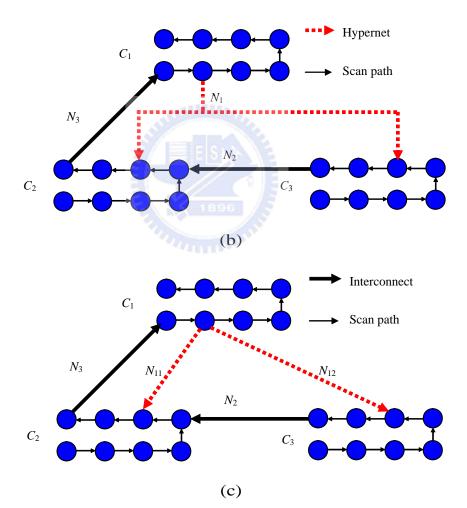

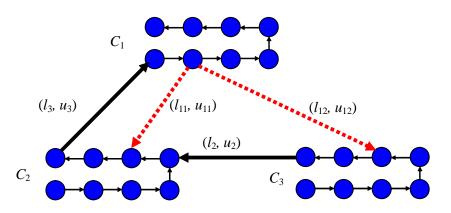

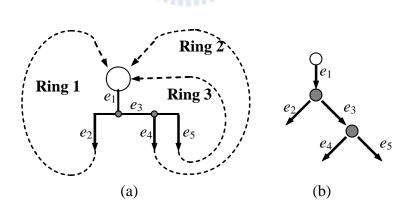

| 2.3  | (a) a multiple-sink hypernet, and (b) an interconnect diagnosis graph model.                                                                                                                                                                        |

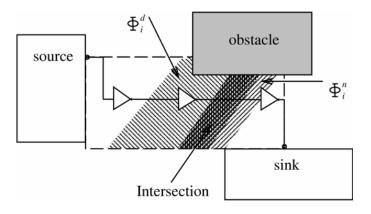

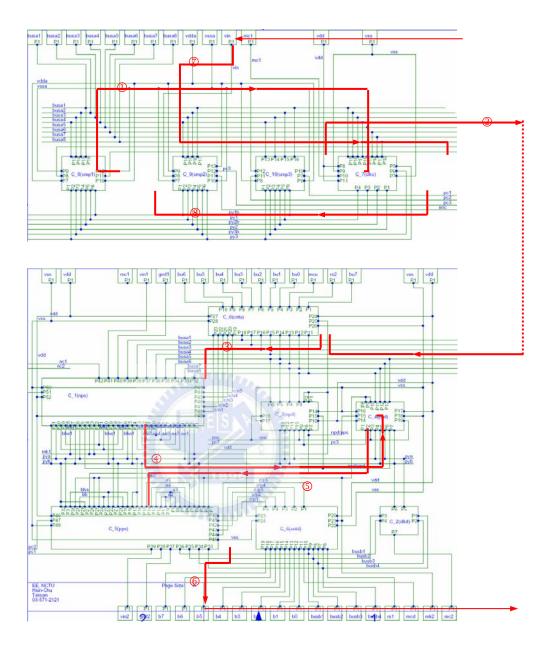

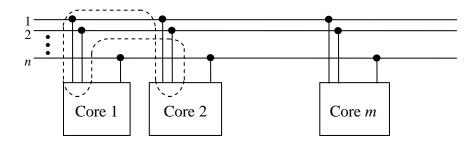

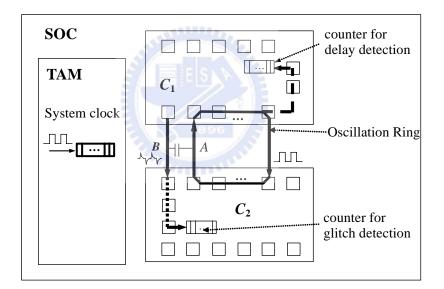

| 2.4  | Test architecture of system-level interconnect test for SoC ICs                                                                                                                                                                                     |

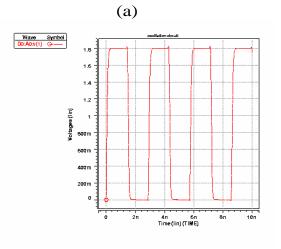

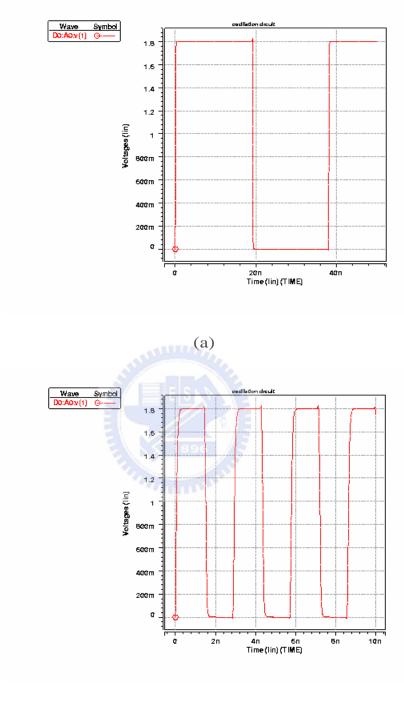

| 2.5  | Simulated waveforms of the longest (a) and shortest rings (b) of benchmark circuit hp.                                                                                                                                                              |

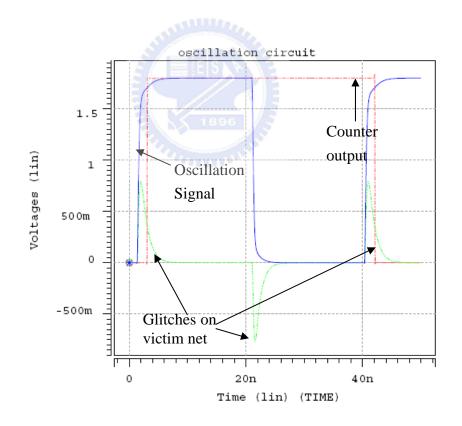

| 2.6  | Oscillation signal on the ring, induced glitches on the victim net, and counter output.                                                                                                                                                             |

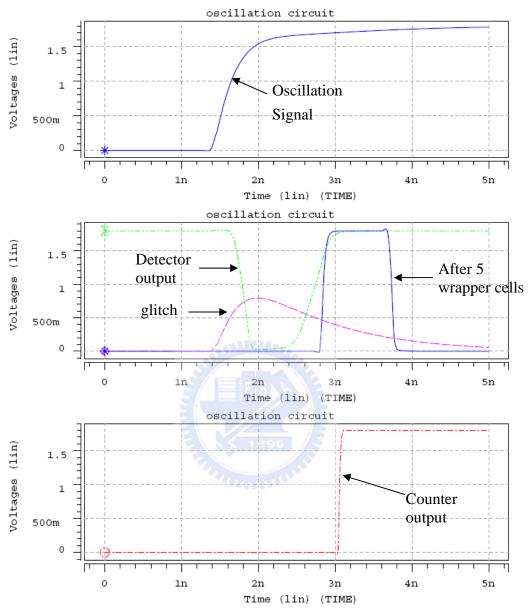

| 2.7  | Illustration on how the glitches are detected, an oscillation signal (top), the resulting crosstalk-induced glitch, the detector output, and the signal after 5 wrapper cells (middle), the counter output with the verified state change (bottom). |

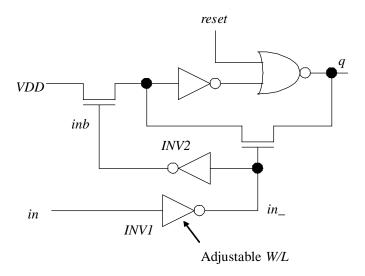

| 2.8  | A pulse detector (PD) with an adjustable threshold by W/L ratio of INV1                                                                                                                                                                             |

| 2.9  | Enhanced wrapper cells with forced inversion (a) input (b) output                                                                                                                                                                                   |

| 2.10 | Switch-level RC circuits for buffers and wires                                                                                                                                                                                                      |

| 2.11 | Noise due to crosstalk-induced current                                                                                                                                                                                                              |

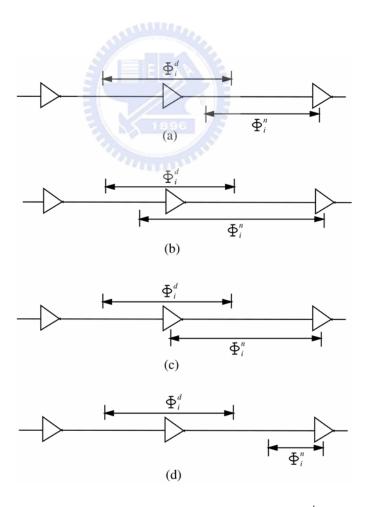

| 2.12 | The respective feasible regions $\Phi_i^n$ , $\Phi_i^d$ and $\Phi_i^n \cap \Phi_i^d$ for inserting a buffer that meet the delay, noise and both delay and noise constraints                                                                         |

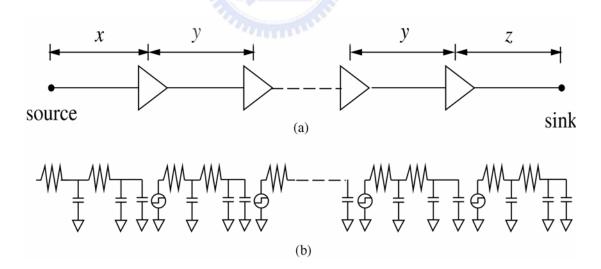

| 2.13 | (a) The buffer placement: $x$ is the optimized length between the source node and the first buffer, $y$ is the optimized length between every pair of neighboring buffers, and $z$ is the length between the last inserted buffer and the sink node. (b) The corresponding buffer model and wire $(\pi)$ model |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

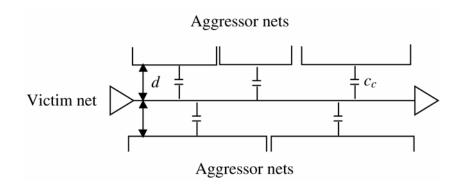

| 2.14 | The victim net suffers from multiple aggressor nets for the coupling capacitance                                                                                                                                                                                                                               |

| 2.15 | Four cases for the intersection of $\Phi_i^d$ and $\Phi_i^n$                                                                                                                                                                                                                                                   |

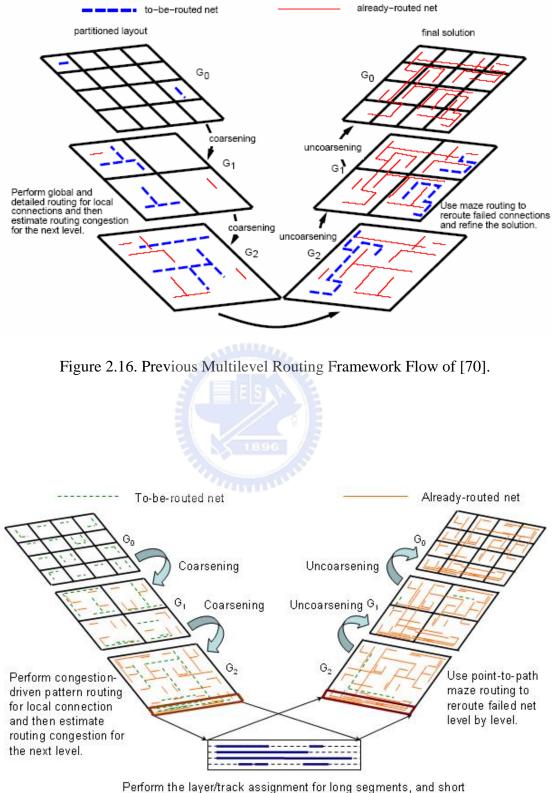

| 2.16 | Previous Multilevel Routing Framework Flow of [70]                                                                                                                                                                                                                                                             |

| 2.17 | Crosstalk-Driven Multilevel Routing Framework Flow [49]                                                                                                                                                                                                                                                        |

| 2.18 | Our Integrated Multilevel Routing Framework with Testability and Yield Enhancement                                                                                                                                                                                                                             |

| 2.19 | A worst-case scenario of interconnect structure or topology in SoC                                                                                                                                                                                                                                             |

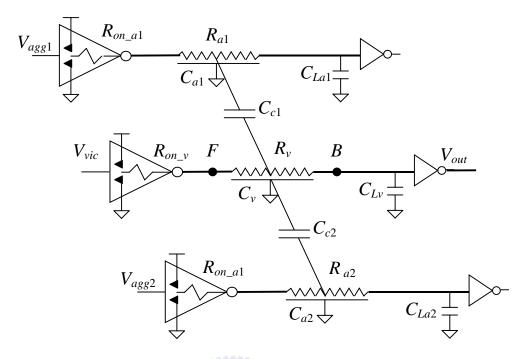

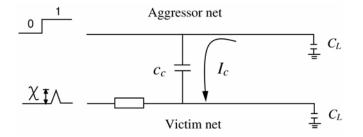

| 3.1  | Circuit model for the crosstalk analysis                                                                                                                                                                                                                                                                       |

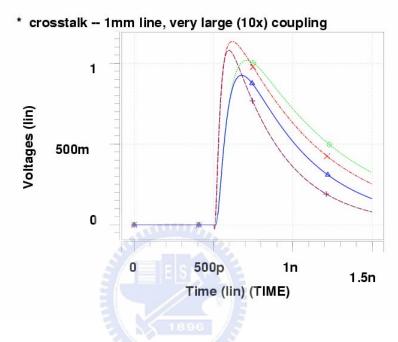

| 3.2  | Simulated crosstalk effects for <i>large</i> enough coupling capacitance, (a) the induced glitch and, (b) the induced delay                                                                                                                                                                                    |

| 3.3  | Simulated crosstalk effects for <i>smaller</i> coupling capacitance, (a) the induced glitch, and (b) the induced delay                                                                                                                                                                                         |

| 3.4  | Superposition of crosstalk-induced delay                                                                                                                                                                                                                                                                       |

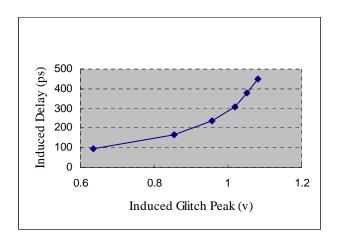

| 3.5  | Monotonic relationships between the peak of the induced glitch and the induced delay                                                                                                                                                                                                                           |

| 3.6  | A pulse detector (PD) with an adjustable threshold by W/L ratio of INV                                                                                                                                                                                                                                         |

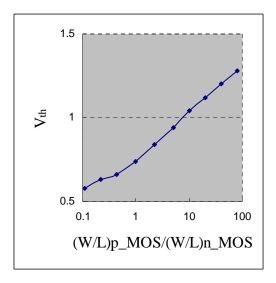

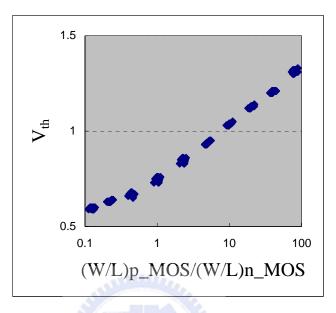

| 3.7  | Simulated relationships between the threshold of detected pulse amplitude $(V_{th})$ with respect to the W/L ratio of the pulse detector (PD)                                                                                                                                                                  |

| 3.8  | Glitch analysis with different resistances and coupling capacitances                                                                                                                                                                                                                                           |

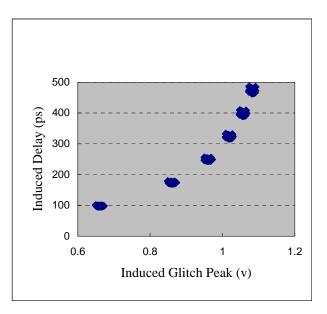

| 3.9  | Monte Carlo simulation of the induced delay vs. the induced glitch peak $(V_p)$                                                                                                                                                                                                                                |

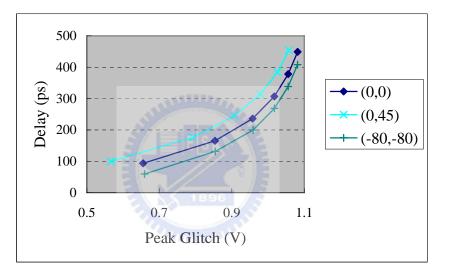

| 3.10 | The induced delay v.s. the peak of the induced glitch for three different cases: (1) $SK_1 = SK_2 = 0$ , (2) $SK_1 = SK_2 = -80$ ps, and (3) $SK_1 = 0$ , $SK_2 = 45$ ps                                                                                                                                       |

| 3.11 | Monte Carlo simulation of the threshold of detected pulse amplitude $(V_{th})$ with respect to the W/L ratio of the pulse detector                                                                                                                                                                             |

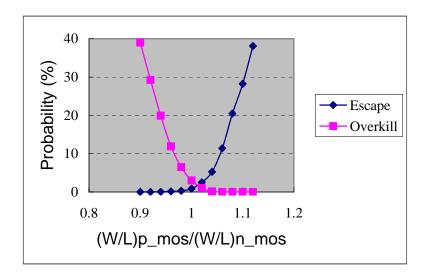

| 3.12 | Monte Carlo simulation of the Escape Probability and Overkill<br>Probability with respect to (W/L) ratio                                                                                                                                                                                                       |

| 3.13 | Monte Carlo simulation of the "Yield" with respect to process variation on parameter values                                                                                                                                                                                                                    |

| 4.1  | Test architecture for interconnect crosstalk detection and delay measurement (also known as Figure 2.4)                         |

|------|---------------------------------------------------------------------------------------------------------------------------------|

| 4.2  | The oscillation signal, A, on the oscillation ring and the induced glitches, B, on the victim interconnect                      |

| 4.3  | Modified wrapper cells: (a) input cell (b) output cell (also same as Figure 2.9)                                                |

| 4.4  | (a) The interconnect diagram, (b) hypernet graph, (c) graph model with 2-pin nets (also same as Figure 2.1)                     |

| 4.5  | Graph model for delay faults (also same as Figure 2.2)                                                                          |

| 4.6  | Hypernet branches and rings                                                                                                     |

| 4.7  | Rings for adjacent output pins                                                                                                  |

| 4.8  | Interconnect Oscillation Ring Test (IORT) Algorithm.                                                                            |

| 4.9  | The placement and routing of an illustrative example of the OR testing for a benchmark circuit $hp$                             |

| 4.10 | Simulated waveforms of the longest (a) and shortest rings (b) of benchmark circuit $hp$ (also same as Figure 2.5)               |

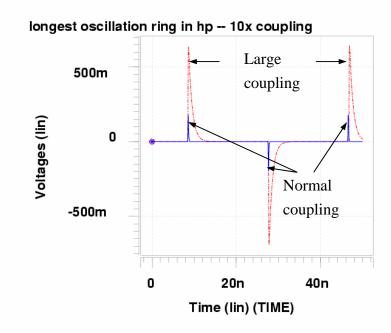

| 4.11 | Simulated waveforms of glitches induced by oscillation signals in the longest ring of " $hp$ " (also same as Figure 2.6)        |

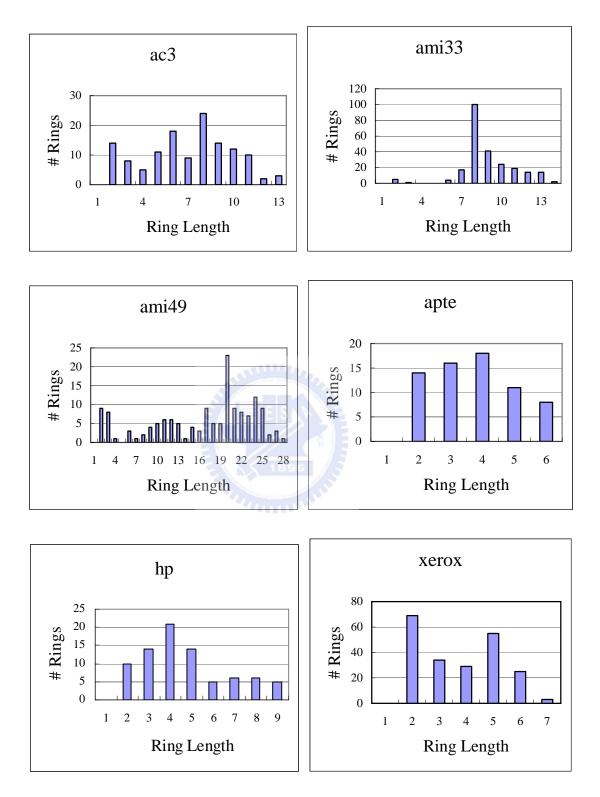

| 4.12 | Distribution of the ring lengths for the benchmark circuits by applying OR testing                                              |

| 4.13 | Relationship between fault coverage versus number of rings                                                                      |

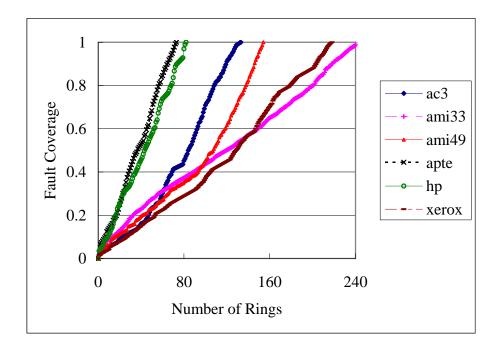

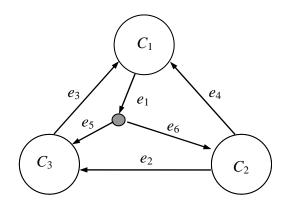

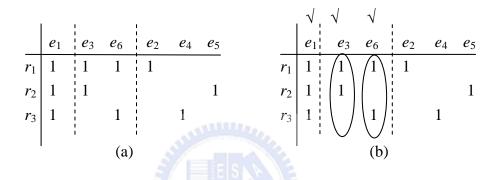

| 5.1  | An example SOC circuit: (a) a hypergragh and 3 hypernets in the interconnect structure, (b) labelling all net segments or edges |

| 5.2  | (a) a hypernet, and (b) the corresponding interconnect diagnosis graph model (Similar to Figure 2.3)                            |

| 5.3  | An illustration example for the complexity of the interconnect diagnosis problem for a bus-structure                            |

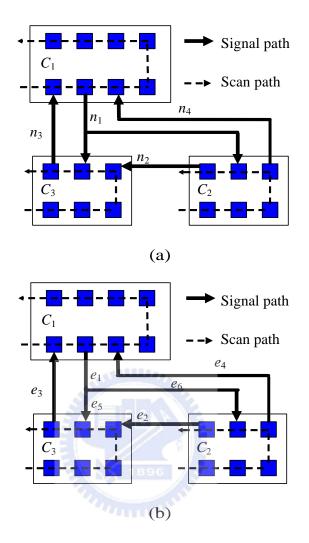

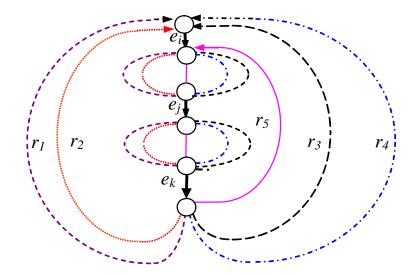

| 5.4  | An interconnect diagnosis graph example                                                                                         |

| 5.5  | Flow chart of the heuristic for diagnosability checking                                                                         |

| 5.6  | A diagnosability example for Figure 5.5(b)                                                                                      |

| 5.7  | Matrices for the heuristic diagnosability checking                                                                              |

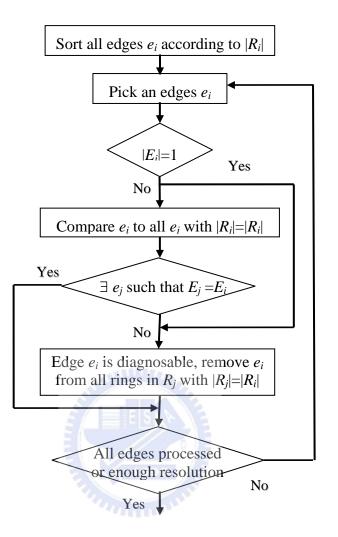

| 5.8  | The ring generation for interconnect fault detection algorithm (IORT)                                                           |

| 5.9  | The ring generation for interconnect fault diagnosis algorithm (IORD)                                                           |

| 5.10 | Diagnosis ring generation procedure                                                                                             |

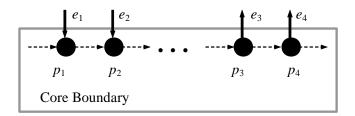

| 5.11 | Scan chain constraint                                                                                                           |

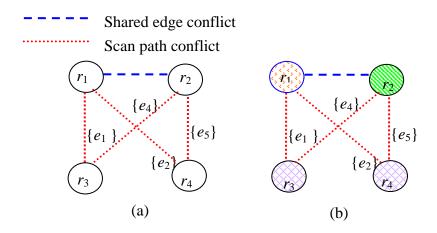

| 5.12 | (a) Conflict graph (b) Graph coloring                                                                                                                                                         | 131 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.13 | Pin reordering for interleaving configuration                                                                                                                                                 | 131 |

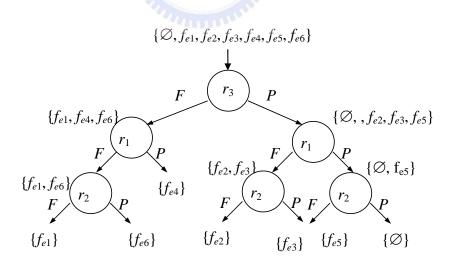

| 5.14 | An adaptive diagnosis tree                                                                                                                                                                    | 132 |

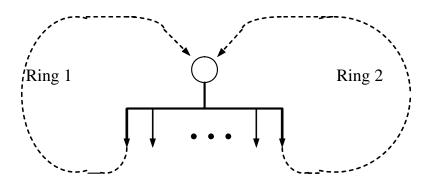

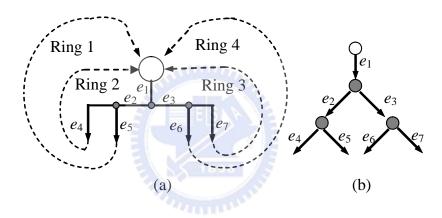

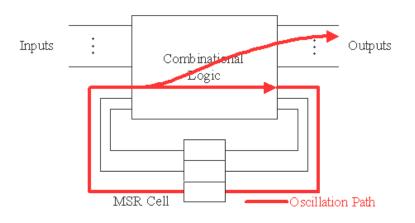

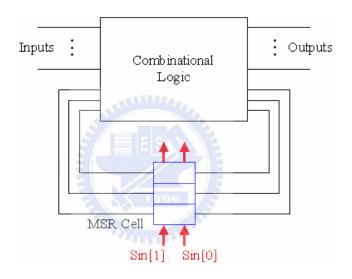

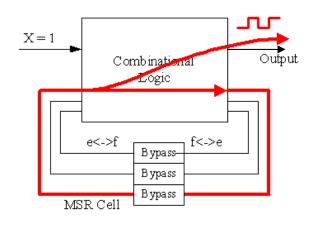

| 6.1  | Oscillation test architecture for sequential circuits: (a) Oscillation rings; (b) MSR states are controlled through scans, and (c) Oscillation test is controlled by system clock             | 145 |

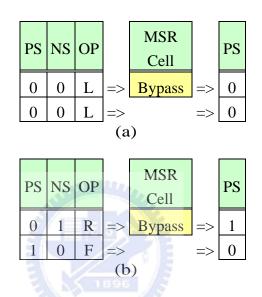

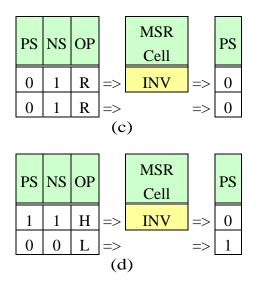

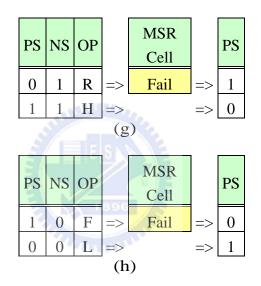

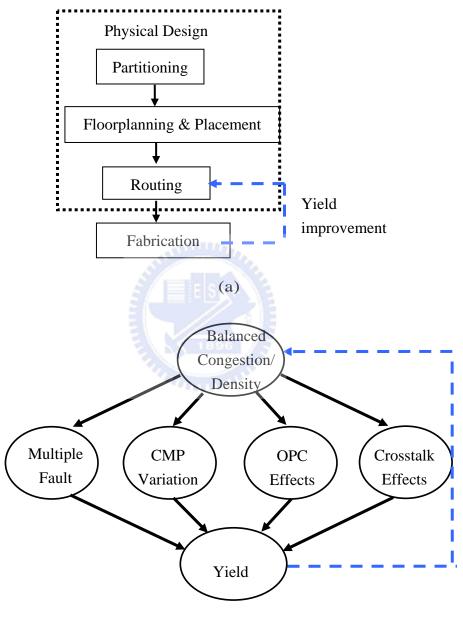

| 6.2  | MSR cell (a) normal mode, and (b) oscillation test mode                                                                                                                                       | 147 |

| 6.3  | Control state table of an MSR cell                                                                                                                                                            | 147 |

| 6.4  | MSR cell for synchronous oscillation test: (a) normal mode, (b) oscillation test mode                                                                                                         | 148 |

| 6.5  | Oscillation Test Pattern Generation (OTPG) Algorithm                                                                                                                                          | 149 |

| 6.6  | State transition and output table of an FSM                                                                                                                                                   | 150 |

| 6.7  | Modified State Transition Table                                                                                                                                                               | 151 |

| 6.8  | (a) Truth Table of a state bit, (b) Operation Table of the MSR cell state                                                                                                                     | 152 |

| 6.9  | Operation values of (a) $\{L, L\}$ , (b) $\{R, F\}$                                                                                                                                           | 153 |

| 6.9  | Operation values of (c) $\{R, R\}$ , (d) $\{H, L\}$                                                                                                                                           | 154 |

| 6.9  | Operation values of (e) $\{R, L\}$ , (f) $\{F, H\}$                                                                                                                                           | 154 |

| 6.9  | Operation values of (g) $\{R, H\}$ , (h) $\{F, L\}$                                                                                                                                           | 155 |

| 6.10 | Oscillation Test Pattern Generation (OTPG) Algorithm                                                                                                                                          | 156 |

| 6.11 | MSR cell state for state pair $(a, e)$                                                                                                                                                        | 156 |

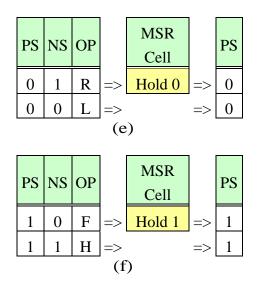

| 7.1  | (a) Yield enhancement in routing stage, and (b) Balancing routing congestion reduces multiple fault probability, CMP induced variation, OPC and crosstalk effects, all of which improve yield | 164 |

| 7.2  | Test architecture among IPs for delay and crosstalk detection, and delay measurement (same as Figure 2.4)                                                                                     | 169 |

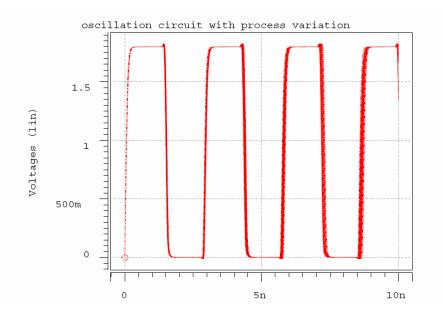

| 7.3  | Simulation waveform with process variation effects on the oscillation ring test scheme                                                                                                        | 172 |

| 7.4  | (a) hypernet, and (b) interconnect diagnosis graph model (Same as Figure 2.1)                                                                                                                 | 173 |

| 7.5  | Noise due to crosstalk-induced current                                                                                                                                                        | 175 |

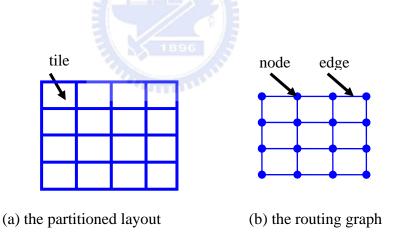

| 7.6  | Routing Graph (a) partitioned layout, (b) routing graph                                                                                                                                       | 177 |

| 7.7  | Integrated multilevel routing framework                                                                                                                                                       | 179 |

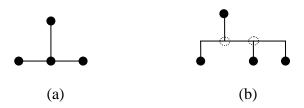

| 7.8  | Two routing trees: (a) a spanning tree with three segments (b) a<br>Steiner tree with the minimum number of intermediate nodes,                                                               |     |

|      | resulting in five segments                                                                                                                                                                    | 180 |

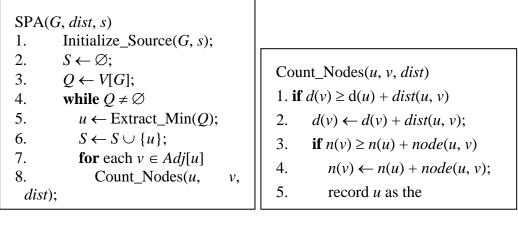

| 7.9  | (a) Shortest path algorithm, (b) $n(v)$ computation                                                                                                                                           | 181 |

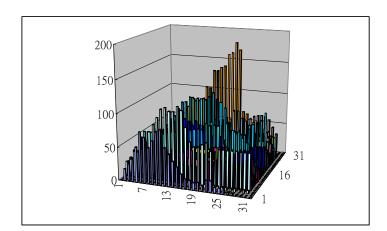

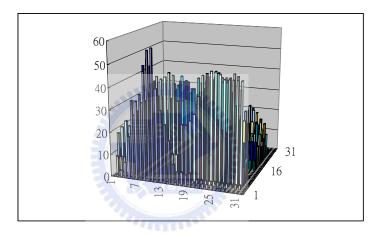

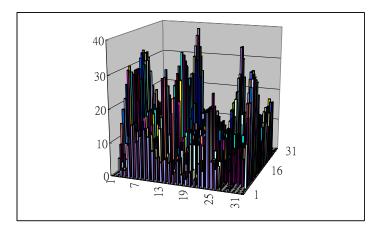

| 7.10 | Routing density distribution for mcc1 for (a) the performance-driven |     |

|------|----------------------------------------------------------------------|-----|

|      | MR, (b) the routability-driven MR, (c) and the proposed algorithm    | 190 |

## Chapter 1

## Introduction

Interconnect becomes the most critical concern in handling performance demand, design complexity and signal integrity, which are the most crucial challenges for designers in nanotechnology. However, to meet all the challenges in performance, complexity, cost, time-to-market, and nanotechnology related issues, the development of sophisticated testability methodology and Electronics Data Automation (EDA) tools for interconnects is essential. This thesis addresses issues on optimizing interconnect-centric oscillation testability and yield enhancement by architectural and algorithmic approaches.

#### **1.1 Interconnect-Centric Study**

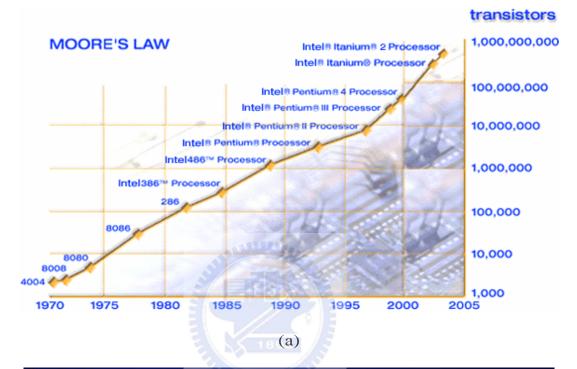

The motivation arises in dominant effects of interconnects (Figure 1.1), especially for square scaling effects in global interconnects (Figure 1.1(b)), and a more obvious trends appears with the nanotechnology in Figure 1.2 since for 90 nm technology, interconnect delay will account for 75% of the overall delay. A limitation of global interconnect routing (Figure 1.3) specially for SoC lies in their high complexity and density—due to the restricted nature of the interconnect structures, the complexity of the SoC ICs grow too quickly as the number of transistors increase due to Moore's Law (Figure 1.1(a)). One feasible approach to significantly improving chip capacities based on interconnect architectures is to incorporate testability and

diagnosability on an SoC chip with IEEE Std.1500 standards. To deal with a very high complexity and criticality of interconnect structure, it is desirable to develop a new technology and methodology for interconnect testing and diagnosis.

(b)

Figure 1.1 Interconnect (a) Moore's Law (b) Scaling effects on memory and microprocessor (*Source: Intel for* (a); *Intel at ISSCC*-03 for (b))

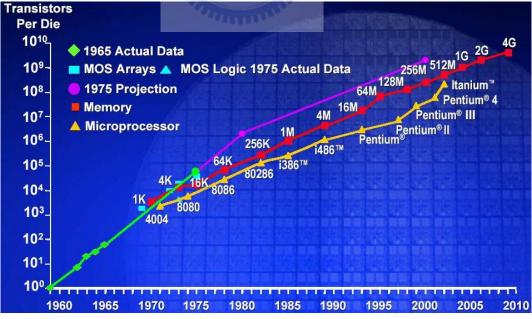

Figure 1.2 For 90 nm technology, interconnect delay will account for **75%** of the overall delay. (*Source: Cadence Design System*)

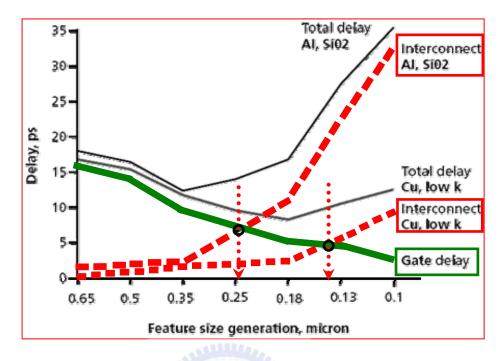

In Figure 1.3, by observing the relative relationship of the interconnect wirelength and device size (die size), the global wires dominates in nanometer process and SoC eras since intrinsic delay of device scales down by a factor of s, local interconnect delay remains the same, and the global interconnect delay increases by square of the scaling factors. The occurrence rates in both local and global wires of nanometer process are more than traditional process technology, with especially obvious difference in global wires.

Source: Tutorial of ICCAD '00

Figure 1.3 Important effects of global interconnects (Source: Tutorial of ICCAD '00).

### 1.2 Challenges of Interconnect-Centric Study

The challenges in interconnects are listed as follows:

- Design complexity, performance, and time-to-market (pull force): make interconnects critical in deciding performance.

- Testing and diagnosability (DfT): It combines the scalable interconnection structure in SoC with considerations of compliant IEEE Std.1500 for DfT (Design for Test), congestion for DfY (Design for Yield), and their applications in physical design including floorplanning and routing frameworks.

- > Testability and yield enhancement (DfM):

- Furthermore, testability and yield enhancement is important in dealing those CMP, OPC related issues in DfM. Thus, our approach is that interconnect congestion influences multiple fault probability, CMP and

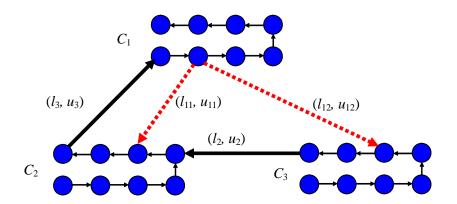

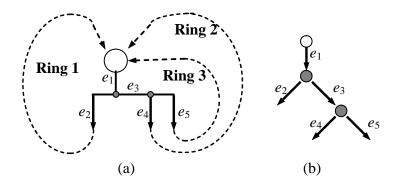

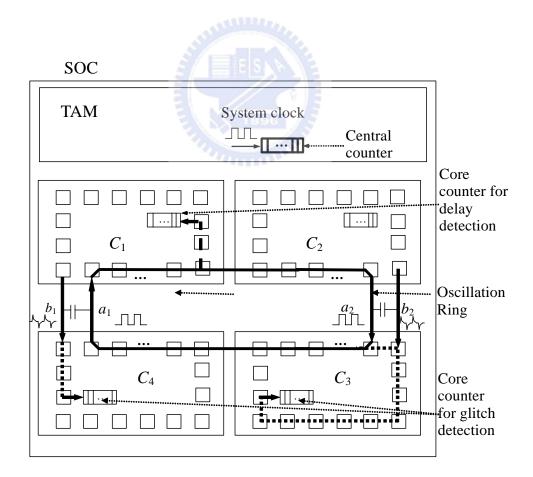

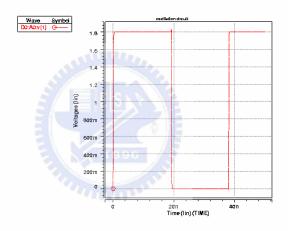

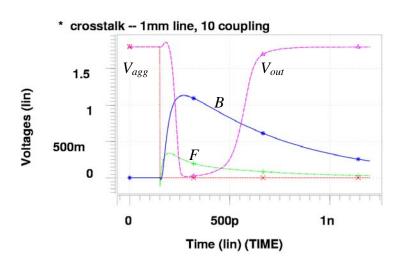

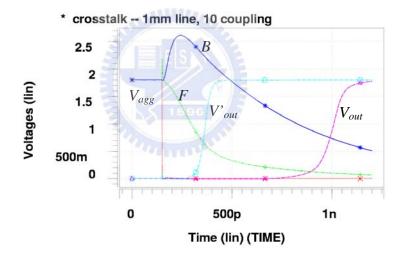

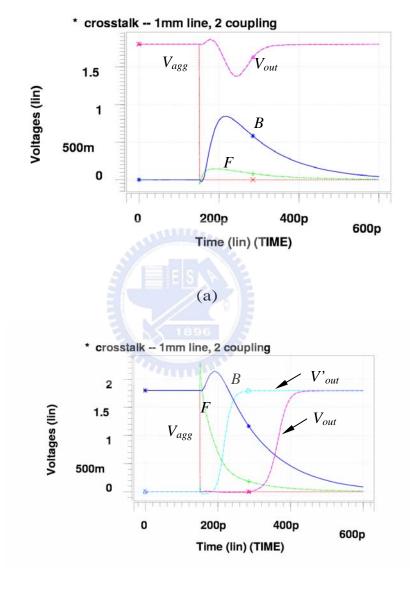

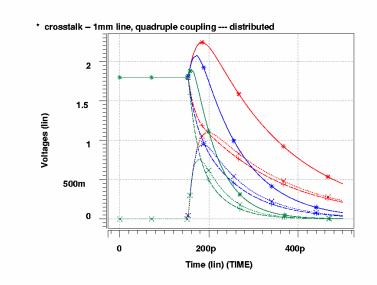

OPC issues, which could be optimized by testability and yield enhancement technologies [81-82].