## 國立交通大學

## 電機與控制工程系

## 碩士論文

離散時間單迴路積分三角類比數位轉換器之功率損耗模型建立與針對非對稱數位用戶迴路終 端機應用之電路設計

Building the power consumption model of discrete time single-loop multi-bit sigma-delta ADC and designing the circuit for ADSL-CO (central office) application

研 究 生:徐基恩

指導教授:陳福川 教授

中華民國九十六年八月

# 離散時間單迴路積分三角類比數位轉換器之功率損耗模型建立與針對非對稱數位用戶迴路終端機應用之電路設計

Building the power consumption model of discrete time single-loop multi-bit sigma-delta ADC and designing the circuit for ADSL-CO (central office) application

研究生:徐基恩 Student: Chi-En Hsu

指導教授:陳福川 Advisor: Fu-Chuang Chen

國立交通大學電機與控制工程系領士論文

A Thesis

Submitted to Department of Electrical and Control Engineering

College of Electrical Engineering and Computer Science

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Electrical and Control Engineering

August 2007

Hsinchu, Taiwan, Republic of China

中華民國九十六年八月

離散時間單迴路積分三角類比數位轉換器之功率損耗模型建立與針對非對稱數位用戶迴路終端機應用之電路設計

研究生:徐基恩 指導教授:陳福川 教授

國立交通大學 電機與控制工程研究所

### 摘要

在本篇論文中,我們建立了積分三角類比數位轉換器的功率消耗模型,而我們把功率 消耗模型分成類比功率消耗模型和數位功率消耗模型兩個部份,類比功率消耗模型包括 積分器功率消耗模型、量化器功率消耗模型、數位類比轉換器功率消耗模型;數位功率 消耗模型包括時脈產生器功率消耗模型和開關功率消耗模型。

我們針對非對稱數位用戶迴路終端機應用來做電路設計。我們選擇的電路架構為離散時間單迴路單一位元積分三角類比數位轉換器來實現非對稱數位用戶迴路終端機。

Building the power consumption model of discrete

time single-loop multi-bit sigma-delta ADC and

designing the circuit for ADSL-CO (central office)

application

Student: Chi-En Hsu

Advisor: Dr. Fu-Chuang Chen

Institute of Electrical and Control Engineering

Nation Chiao Tung University

**ABSTRACT**

In this work, we build the power consumption model of discrete time single-loop multi-bit

sigma-delta ADC, and the power consumption model of discrete time single-loop multi-bit

sigma-delta ADC can be divided into two parts. The one is the analog power consumption

model, and the other is the digital power consumption model. The analog power consumption

model includes the integrator power consumption model, the Quantizer power consumption

model and the DAC power consumption model. The digital power consumption model

includes the clock driver power consumption model and the switch power consumption

model.

We design the circuit for ADSL-CO (central office) application. And we used the discrete

time single-loop single -bit sigma-delta ADC architecture to simulate.

II

### 誌謝

首先感謝陳福川老師在我的研究論文方面的指導,使我的論文能夠更完善,並且在 ic 設計的領域建立的一定的基礎;接下來要感謝的是邱俊誠老師在微機電製程、8051 單晶片與 ZigBee 無線感測網路方面的指導,使我能夠在各方面都有一定的基礎,以後能有更完善的能力去應對工作上的需求。

接下來要感謝的是研究室的同窗好友孟學、哲安、一帆、嘉宏、亞書與建賢的陪伴, 使的我在研究的路上感到不孤單;也要感謝研究室的學弟們陪伴我度過研究所最後一 年,使研究所的生活能夠多采多姿;接下來要感謝的是 314 的室友們的陪伴,使的研究 以外的生活能夠完全放鬆。

最後要感謝的是我的父母親與我的家人,有他們在精神及物質方面的支持,我才有 半碼這麼無後顧之憂的完成學業,將來的我一定更加的懂事,也會盡一切努力讓你們覺 得驕傲。

### **List of Symbols**

N

gm1

### **Symbols** $V_{LSB}$ Quantizer step size **OSR** OverSampling Ratio Order of the Sigma-Delta modulator n Number of bits in the quantizer В Sampling Frequency $f_{s}$ Signal Bandwidth $f_{\scriptscriptstyle B}$ $V_{ref}$ Reference Voltage of the quantizer Gain of OTA A Frequency of the input signal $f_{in}$ ith phase of a nonoverlap clock $\phi_i$ Amplitude of input signal $A_{in}$ standard deviation of clock jitter $\sigma_{\scriptscriptstyle jit.}$ $C_{s}$ Sampling capacitor $C_{I}$ Integrating capacitor $C_{\scriptscriptstyle L}$ Load capacitor of OTA $V_{s}$ Input signal plus feedback DAC signal Time constant of input branch $\tau_1$ Standard deviation of $V_s$ $\sigma_{\scriptscriptstyle VS}$ Time constant of integrator output settling $\tau_2$ gain coefficient of i th integrator $a_i$ percentage of the bottom plate parasitic η TAbsolute temperature Switch ON resistance R

quantizer levels

Amplifier transconductance

## **Lists of Tables**

| Table 4.1 | Standard deviations of $V_s$ vs. different quantizer bit numbers                                 |       |

|-----------|--------------------------------------------------------------------------------------------------|-------|

|           |                                                                                                  | 55    |

| Table 5.1 | Minimum SR and GBW required w. r. t. OSR                                                         |       |

|           |                                                                                                  | 76    |

| Table 5.2 | Simulation results of standard deviation of capacitor mismatch vs. unin<br>number with $A_m = 1$ | t DAC |

|           |                                                                                                  | 90    |

## **Lists of Figures**

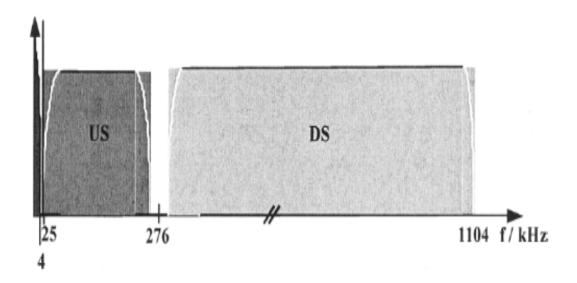

| Fig. 1.1 ADSL band allocation (DUS, FDD)                    | 2  |

|-------------------------------------------------------------|----|

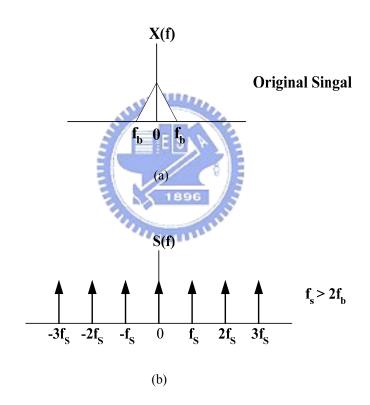

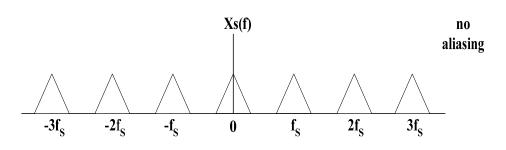

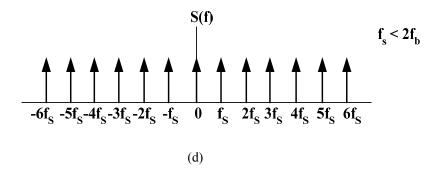

| Fig. 2.1 (a) Original signal spectrum                       |    |

| (b) Sample function when fs > 2fB                           |    |

| (c) Signal spectrum that is sampled by (b)                  |    |

| (d) Sample function when fs < 2fB                           |    |

| (e) Signal spectrum that is sampled by (d)                  | 5  |

| Fig. 2.2 Quantization process.                              | 6  |

| Fig. 2.3 Quantization error caused by A/D converter         | 6  |

| Fig. 2.4 Quantization error range.                          | 7  |

| Fig. 2.5 P.D.F of quantization error.                       | 7  |

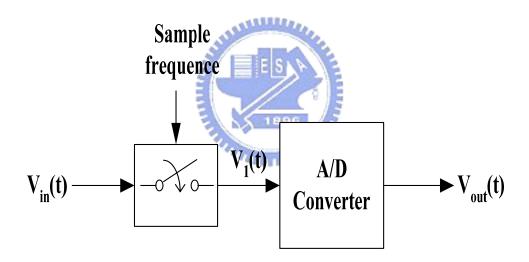

| Fig. 2.6 Sampling system.                                   | 9  |

| Fig. 2.7 Noise distribution after sampling.                 | 10 |

| Fig. 2.8 (a) General $\Sigma\Delta$ modulator               |    |

| (b) Linear model with quantization noise                    | 12 |

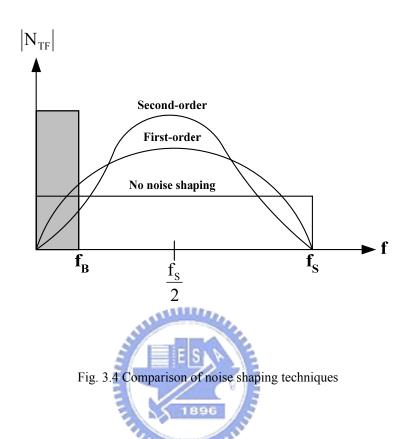

| Fig. 2.9 Noise shaping.                                     | 13 |

| Fig. 3.1 Block diagram of $\Sigma\Delta$ A/D converter      | 15 |

| Fig. 3.2 First-order $\Sigma\Delta$ modulator.              | 16 |

| Fig. 3.3 Single-loop second order $\Sigma\Delta$ modulator. | 18 |

| Fig. 3.4 Comparison of noise shaping techniques.            | 20 |

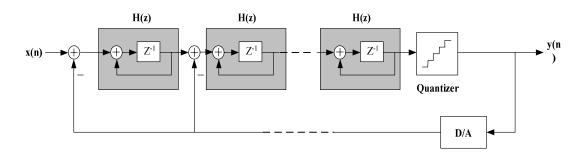

| Fig. 3.5 Single-loop high order $\Sigma\Delta$ modulator    | 21 |

| Fig. 3.6 Four-order interpolative architecture.             | 21 |

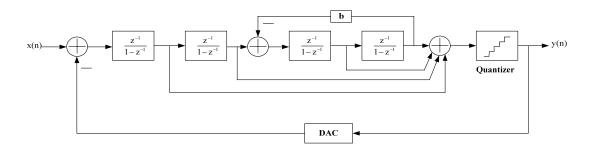

| Fig. 3.7 2-1 architecture MASH $\Sigma\Delta$ modulator     | 23 |

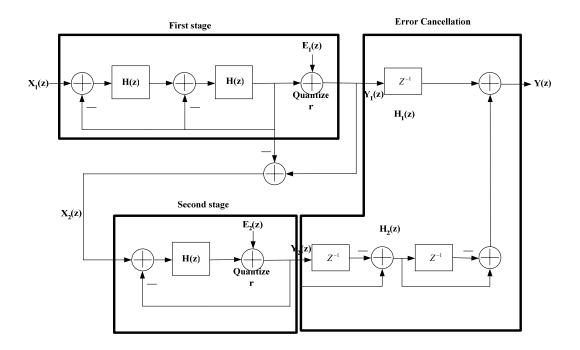

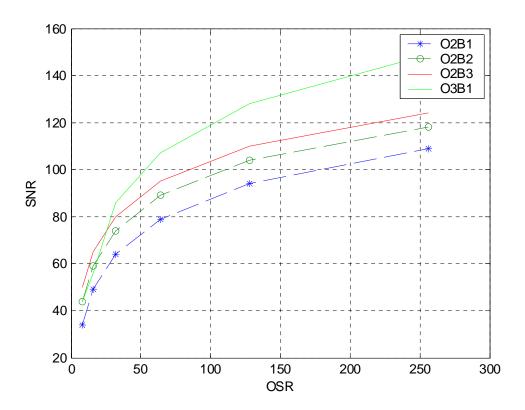

| Fig. 3.8 SNR vs. OSR with different quantizer bit number    | 25 |

| Fig. 3.9 Multi-bit architecture.                            | 26 |

| Fig. 3.10 A B-bit DAC with DEM technique                    | 27 |

| Fig. 3.11 Operation principle of the DWA algorithm                           | 28    |  |

|------------------------------------------------------------------------------|-------|--|

| Fig. 3.12 Output spectrum with three kinds of DAC                            | 29    |  |

| Fig. 3.13 Comparison of $\Sigma\Delta$ modulator architectures               | 30    |  |

| Fig. 3.14 Performance characteristic of a $\Sigma\Delta$ converter           | 33    |  |

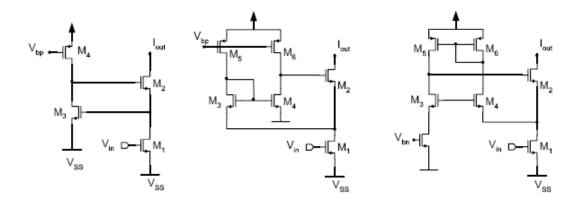

| Fig. 4.1 A single-stage telescopic OTA.                                      |       |  |

| Fig. 4.2 The folded cascode OTA.                                             |       |  |

| Fig. 4.3 The two-stage Miller-compensated OTA                                |       |  |

| Fig. 4.4 An overview of the obtained data points.                            | 45    |  |

| Fig. 4.5                                                                     |       |  |

| (a) Implementation of the integrator and the feedback DAC                    |       |  |

| (b) To charge the unit capacitance                                           |       |  |

| (c) To discharge the unit capacitance                                        | 47    |  |

| Fig. 4.6                                                                     |       |  |

| (a) an ideal inverter for logic level with a load capacitance                |       |  |

| (b) an ideal CMOS inverter for transistor level with a load capaci           | tance |  |

| (c) an ideal CMOS inverter for transistor level with a load                  |       |  |

| capacitance                                                                  | 51    |  |

| Fig. 4.7 The clock generator with non-overlapping clocks                     | 52    |  |

| Fig. 4.8 The CMOS switch.                                                    | 53    |  |

| Fig. 5.1 Fully differential switched-capacitor integrator and timing diagram | 60    |  |

| Fig. 5.2 Folded cascode op-amp.                                              | 63    |  |

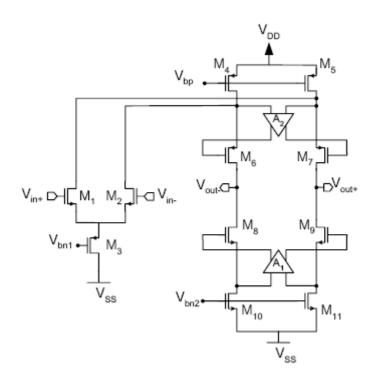

| Fig. 5.3 Regulated cascaded gain stage.                                      | 65    |  |

| Fig. 5.4 Gain boosting in cascode stage.                                     | 66    |  |

| Fig. 5.5 Gain boosting folded cascode op-amp.                                |       |  |

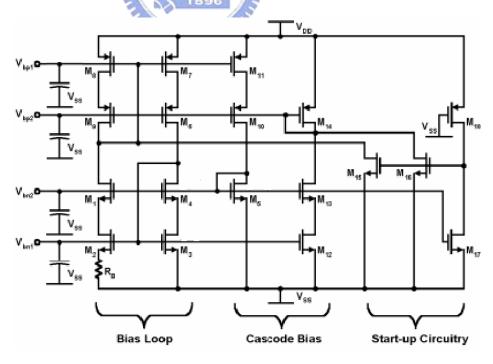

| Fig. 5.6 A wide-swing constant-transconductance bias circuit                 |       |  |

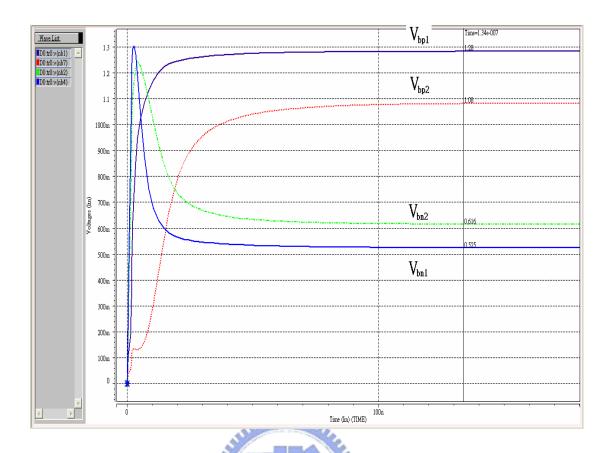

| Fig. 5.7 Simulated bias output voltages.                                     |       |  |

| Fig. 5.8 A switched-capacitor CMFR circuit                                   |       |  |

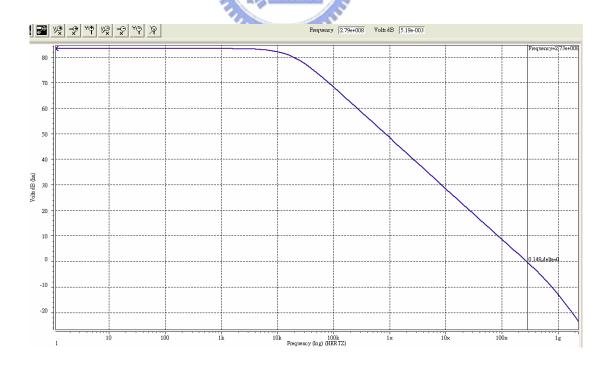

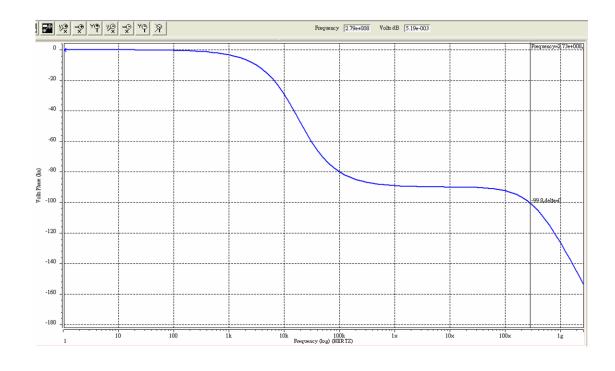

| Fig. 5.9 The gain-boosting folded-cascode OTA                     | 75 |

|-------------------------------------------------------------------|----|

| Fig. 5.10 Simulated frequency response of the amplifier           | 76 |

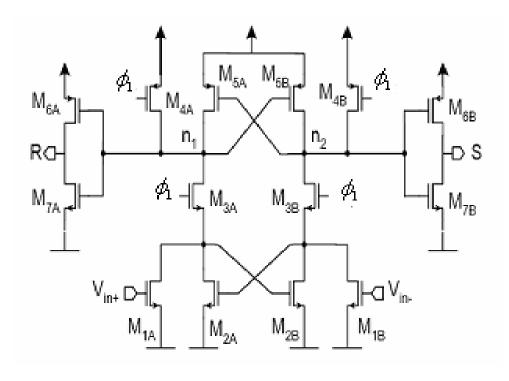

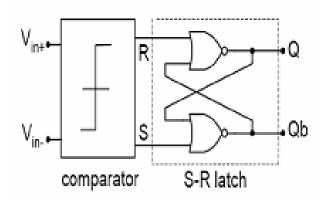

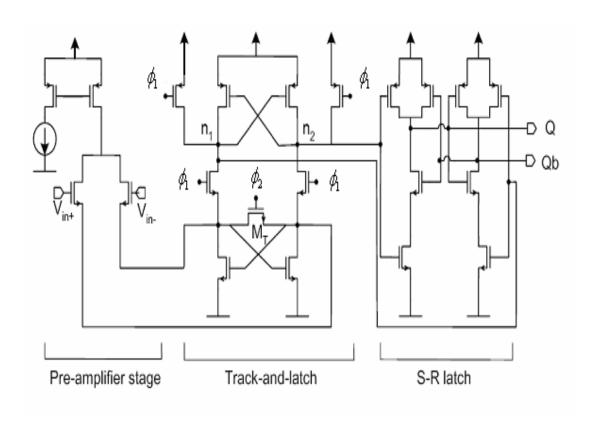

| Fig. 5.11 Regenerative latch comparator                           | 78 |

| Fig. 5.12 The dynamic comparator with a pre-amplifier input stage | 79 |

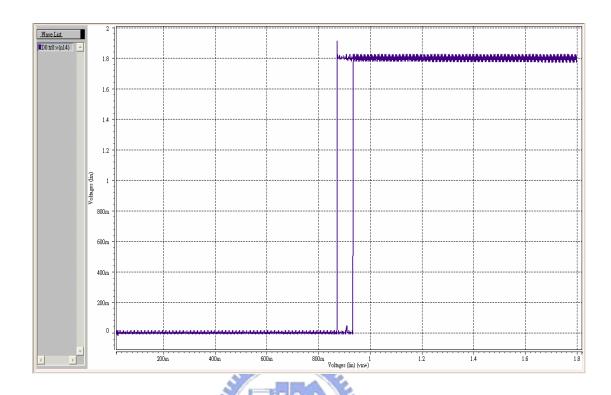

| Fig. 5.13 Simulated output vs. input voltage of the comparator    | 80 |

| Fig. 5.14 Input and output waveform of the comparator             | 80 |

| Fig. 5.15 Two-phase non-overlapping clock generator               | 81 |

| Fig. 5.16 Relationship of the simulated clock signals             | 83 |

| Fig. 5.17 (a) sampling mode for a switch-capacitors integrator    |    |

| (b) a sampling circuit,                                           |    |

| (c) a simplified sampling circuit                                 | 84 |

| Fig. 5.18 Definition of speed in a sampling circuit               | 85 |

| Fig. 5.19 Types of sampling switches.                             | 86 |

| Fig. 5.20 Simulated on-resistance of switches                     | 88 |

| Fig. 5.21 Schematic of modulator circuit.                         | 89 |

| Fig. 5.22 The output spectrum of –10dB input.                     | 90 |

## **Contents**

| 中文摘要                                                     | I   |

|----------------------------------------------------------|-----|

| English Abstract.                                        | II  |

| List of Symbols.                                         | III |

| Acknowledgment                                           | IV  |

| Lists of Tables.                                         | V   |

| Lists of Figures.                                        | VI  |

| Contents                                                 | IX  |

| Chapter 1 Introduction                                   | 1   |

| 1.1 Motivation                                           | 1   |

| 1.2 Organization                                         | 2   |

| Chapter 2 Fundamental Theorems of Sigma-Delta Modulators | 3   |

| 2.1 Nyquist Sampling Theorm                              | 3   |

| 2.2 Quantization Noise and Peak SNR                      | 5   |

| 2.3 Techniques of Sigma-Delta Modulator                  | 8   |

| 2.3.1 Oversampling Technique                             | 9   |

| 2.3.2 Noise shaping.                                     | 11  |

| Chapter 3 Architectures of Sigma-Delta Modulator         | 15  |

| 3.1 First-Order Sigma-Delta Modulator                    | 16  |

| 3.2 Single-Loop Second-Order Sigma-Delta Modulator       | 18  |

| 3.3 Single-Loop High Order Sigma-Delta Modulator         | 20  |

| 3.4 Interpolative Sigma-Delta Modulator                  | 21  |

| 3.5 MASH Architecture                                    | 22  |

| 3.6 Multi-bit Quantizer Sigma-Delta Modulator            | 24  |

| 3.7 Multi-bit Sigma-Delta Modulator use DEM Technique    | 26  |

| 3.7.1 Randomization Technique                                                 | 27       |  |

|-------------------------------------------------------------------------------|----------|--|

| 3.7.2 Data Weighted Averaging (DWA)                                           | 28       |  |

| 3.8 Decimator.                                                                | 30       |  |

| 3.9 Performance Metrics for a $\Sigma\Delta$ Modulator                        | 31       |  |

| Chapter 4 Models of Multi-Bit Sigma-Delta Modulator Power                     | 34       |  |

| 4.1 Integrator power                                                          | . 34     |  |

| 4.2 Quantizer power                                                           | 43       |  |

| 4.3 DAC Power.                                                                | 45       |  |

| 4.4 Clock driver power and switch power                                       | 47       |  |

| 4.5 Verification for the power consumption model                              | 56       |  |

| Chapter 5 Circuit Implementation for Second-order One-bit Sigma-Delta Modulat |          |  |

| 5.1 Switched-Capacitor Integrator Design                                      | 58<br>58 |  |

| 5.2 Operational Transconductance Amplifier                                    |          |  |

| 5.2.1 Folded Cascode OTA                                                      | 61       |  |

| 5.2.2 Gain Enhancement Technique                                              | 64       |  |

| 5.2.3 Bias circuit.                                                           | 67       |  |

| 5.2.4 Common-Mode Feedback                                                    | 72       |  |

| 5.2.5 Design of the Gain boosting folded cascode op-amp                       | 74       |  |

| 5.3 Comparator                                                                | 77       |  |

| 5.4 Clock generator.                                                          | 81       |  |

| 5.5 Switch                                                                    | 84       |  |

| 5.6 Simulation of System Circuit.                                             | 89       |  |

| Chapter 6 Conclusions and Future works.                                       | 91       |  |

| References                                                                    | 92       |  |

## Chapter 1

### Introduction

### 1.1 Motivation

Sigma-Delta A/D converters have become popular for high-resolution medium-to-low-speed applications such as digital audio [Bos 88][Nor 89], voice codec, and DSP chip. Recently,  $\Sigma\Delta$  ADCs have been applied to higher bandwidth signals, and low power designs are frequently emphasized. For example, in ×DSL [Gag 03][Rio 04] applications, signals up to several MHz must be handled.

The power consumption of the Sigma-Delta A/D converters is very important in all kinds of application. So it is very important that how to design can get the better power consumption. We propose an power consumption model to estimate the power consumption in the discrete time single-loop multi-bit  $\Sigma\Delta$  ADCs design.

As illustrated in Fig. 1.1, As illustrated in Fig. 1, in an ADSL modem the downstream data (DS) are transferred at higher frequencies in a wider band as compared to the upstream data (US). Flexible band allocations are standardized, such as frequency division (FDD), frequency overlapping, single upstream (SUS), and double upstream (DUS).1 The developed converter targets a central-office (CO) line-card application. For such transceivers, the analog-to-digital converter (ADC) typically requires 14-bit resolution over an analog signal bandwidth of 276 kHz.

Fig. 1.1 ADSL band allocation (DUS, FDD).

### 1.2 Organization

This work is organized as follows. In Chapter 2 and Chapter 3, systematic studies of fundamental theory and various architectures of  $\Sigma\Delta$  modulator are presented first. In Chapter 4, the power consumption model is derived and verified. In Chapter 5, design the circuit for ADSL-CO application. Conclusions and future works are presented in Chapter 6.

## **Chapter 2**

# Fundamental Theorems of Sigma-Delta Modulators

Before we establish the error models of  $\Sigma\Delta$  modulators, several important theorems and concepts must be known, such as Nyquist sampling theorem, quantization error and the two most critical techniques in a  $\Sigma\Delta$  modulator: oversampling and noise shaping. All topologies of  $\Sigma\Delta$  modulators are based on these two techniques. There also have some parameters we must to understand, such as OSR, SNR, and SNDR ...etc. This chapter starts from fundamental theorems, and introduces several topologies of  $\Sigma\Delta$  modulators.

We will illustrate quantization error and analyze quantization noise in an ideal A/D converter and then derives the peak signal-to-noise ratio. The resolution of an A/D converter is determined by signal-to-noise ratio, which is a very important specification in an A/D converter.

### 2.1 Nyquist Sampling Theorem

In an analog-to-digital converter, the analog signal from external environment must be converted to discrete-time signal by sampling. However, the sampling rate (fs) and signal bandwidth (fB) must follow the Nyquist sampling theorem in (2.1):

$$f_{S} \ge 2f_{B} \tag{2.1}$$

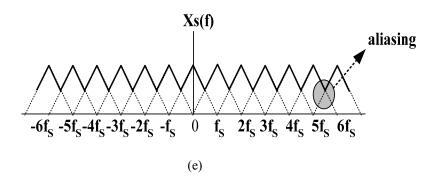

The sampling rate must be higher or equal to twice of signal bandwidth in order to prevent from aliasing. We will illustrate the phenomenon of aliasing by Fig. 2.1. Fig. 2.1(a) and (b) are the spectrums of signal and sample function respectively; from fig. 2.1(c), when sampling rate is twice higher than signal bandwidth, the signal after sampling has no aliasing and it can be perfectly reconstructed by using low pass filters. However, in Fig. 2.1(d), when the sampling rate is lower than twice of signal bandwidth, aliasing will appear in the signal after sampling. The signal having aliasing is difficult to reconstruct to original signal [Mach 96], like Fig. 2.1(e).

Fig. 2.1 (a) Original signal spectrum (b) Sample function when fs > 2fB (c) Signal spectrum that' sampled by (b) (d) Sample function when fs < 2fB (e) Signal spectrum that sampled by (d).

### 2.2 Quantization noise and Peak SNR

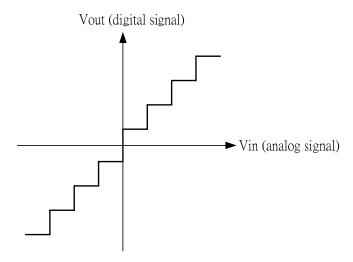

We can get a discrete-time signal by sampling a continuous-time signal, and this sampled signal can be converted to digital signal. Quantization will appear in this process, the basic concept of quantization is to classify the original signal to different levels according to its level to determine the bit number of this signal, as shown in Fig. 2.2.

Fig. 2.2 Quantization process

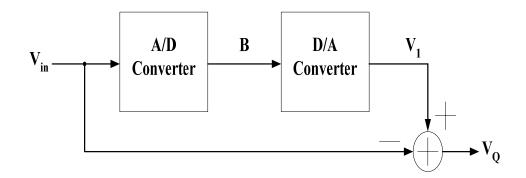

It will have quantization error even in an ideal analog-to-digital converter. As shown in Fig .2.3, we convert the digital signal B to analog signal V<sub>1</sub> by a D/A converter, and then the signal V<sub>1</sub> is subtracted by input signal Vin. The result is the quantization error V<sub>Q</sub>, as in (2.2) [Joh 97].

$$V_{Q} = V_{in} - V_{1} \tag{2.2}$$

Quantization noise  $V_Q = V_{in} - V_1$

Fig. 2.3 Quantization error caused by A/D converter

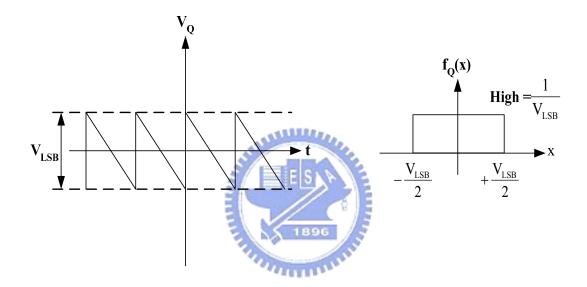

The range of quantization error is limited in  $\pm V_{LSB}/2$  (as in Fig. 2.4), and we assume the probability density function of quantization error is uniformly distributed between  $\pm V_{LSB}/2$  and its mean is zero, as shown in Fig. 2.5. From this assumption, we can easily get the quantization noise power  $V_{Q(rms)}^2$  in (2.3).

$$V_{Q(rms)}^{2} = \int_{-\infty}^{\infty} x^{2} \cdot f_{Q}(x) \cdot dx = \frac{1}{V_{LSB}} \int_{-VLSB/2}^{VLSB/2} x^{2} \cdot dx = \frac{V_{LSB}^{2}}{12}$$

(2.3)

Fig. 2.4 Quantization error range

Fig. 2.5 P.D.F of quantization error

From (2.3) we can know the quantization noise power is proportional to square of VLSB, and VLSB can be represented as in (2.4). Therefore, we can say that the quatization noise will reduce by increasing quantization bit number.

$$V_{LSB} = \frac{FS}{2^B} \tag{2.4}$$

FS=Full scale =  $V_{ref+} - V_{ref-}$  B: Quantization bit number

Assume that input signal is sinusoidal, expressed as  $V_{in}(t) = A \sin \omega t$ , so the input signal power

$V_{in(rms)}^2$  is as (2.5). In (2.5), we define the amplitude of input signal is the full scale of reference voltage, and from (2.3), (2.4) and (2.5), the peak SNR(Peak Signal-to-Noise Ratio) can be derived as in (2.6).

$$V_{\text{in(rms)}}^2 = \frac{1}{T} \int_{-T/2}^{T/2} (A \cdot \sin \omega t)^2 \cdot dt = \frac{A^2}{2} = \frac{(2A)^2}{8} = \frac{FS^2}{8}$$

(2.5)

PSNR = 10 log

$$\left(\frac{V_{\text{in(rms)}}^{2}}{V_{Q(\text{rms})}^{2}}\right) = 6.02B + 1.76 \text{ dB}$$

(2.6)

(2.6) is the result obtained by Nyquist sampling rate. From (2.6), we can know that each additional bit number in quantizer increases 6dB in SNR. In Nyquist A/D converters, increasing the resolution of quantizer (decrease  $V_{LSB}$ ) while reducing the quantization noise is a general method to reach higher SNR, but this method is sensitive to mismatches of analog device. Therefore, the general Nyquist A/D converter is not easily to implement with high resolution.

### 2.3 Techniques of Sigma-Delta Modulator

ΣΔ A/D converters are based on oversampling and noise shaping to reach high resolution. Oversampling means the sampling rate is much higher than Nyquist rate, about 8~512 times in general applications. The goal of oversampling is to expand quantization noise to wider range. It can reduce the quantization noise in signal bandwidth and increase the DR (Dynamic range) of input signal. Noise shaping is a technique that moves noise to high frequency, which is done by using discrete time filter and feedback technique. After noise shaping, the noise in high frequency can be filtered out by a digital filter [Nor 97].

### 2.3.1 Oversampling Technique

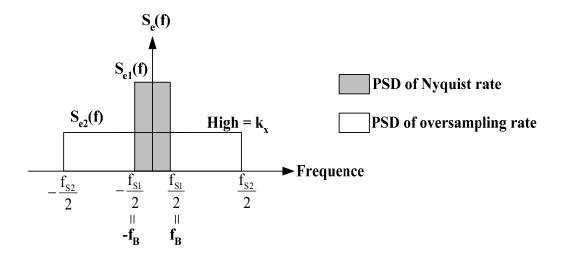

First, we made the assumption that quantization noise is a uniform distribution in sampling spectrum so its mean is zero and is a white noise [Raz 01]. The system in Fig. 2.6 just has oversampling function and does not have noise shaping effect. If a A/D converter is sampled in Nyquist rate, then the quantization noise is uniform distributed between  $\pm f_B$ ; if it is sampled by oversampling technique, then quantization noise is uniform distributed between  $\pm f_{S2}/2_s$ , which is much larger than  $f_B$ . As shown in Fig. 2.7, if the signal bandwidth is between  $\pm f_B$ , then quantization noise in this bandwidth will be reduced by using oversampling technique, which will raise PSNR significantly.

Fig. 2.6 Sampling system

Fig. 2.7 Noise distribution after sampling

In the condition of oversampling, the PSD (Power Spectrum Density) of quantization noise is as  $S_{e2}(f)$  in Fig. 2.7 and can be represented as:

$$k_x^2 = \frac{V_{LSB}^2}{12 \cdot f_s} = S_{e2}^2(f)$$

(2.7)

From (2.7) we can estimate the quantization noise in 2f<sub>B</sub> after oversampling

$$P_{Q} = \int_{-f_{B}}^{f_{B}} k_{x}^{2} \cdot df = \frac{2f_{B}}{f_{s}} \cdot \frac{V_{LSB}^{2}}{12} = \frac{FS^{2}}{12 \cdot 2^{2B} \cdot OSR}$$

(2.8)

In (2.8), we define a parameter OSR (Oversampling Ratio) as

$$OSR = \frac{f_s}{2f_R}$$

(2.9)

Finally, we can get PSNR from (2.5) and (2.8)

PSNR =

$$10 \log \left( \frac{P_{\text{signal}}}{P_{\text{Q}}} \right) = 6.02B + 1.76 + 10 \log (OSR)$$

(2.10)

From (2.10), we can find that doubling OSR will increase 3dB in PSNR, which is about 0.5 bit increase in resolution. Although oversampling can reduce quantization noise, it is difficult to reach high SNR when using a low bit quantizer. For example, if we need a 16bit A/D converter, then SNR must be equal to 98dB, if the signal bandwidth is 20KHz, then the sampling rate must equal to  $2 \times 10^9 \times 20$ KHz, it is impossible to implement. Because at such high frequency, quantization noise is no longer a white noise, it is correlated with input signal. So there is not only oversampling technique, we must add noise shaping technique also, if we want to achieve high resolution.

### 2.3.2 Noise Shaping

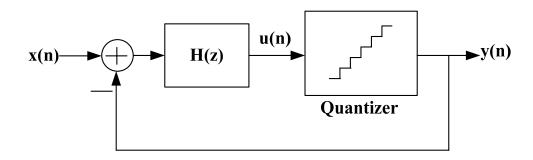

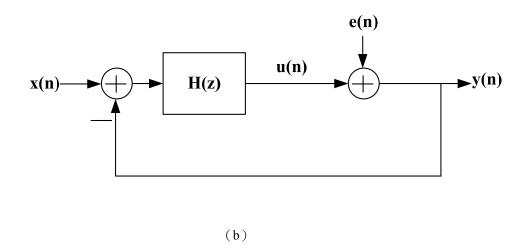

We can model a general  $\Sigma\Delta$  modulator and its linear model as shown in Fig. 2.8.

(a)

Fig. 2.8 (a) General  $\Sigma\Delta$  modulator (b) Linear model with quantization noise

From Fig. 2.8(a), we can derive output Y(z) as (2.11)

$$Y(z) = \frac{H(z)}{1 + H(z)} X(z) + \frac{1}{1 + H(z)} E(z)$$

(2.11)

and define Signal Transfer Function  $S_{\text{TF}}$  and Noise transfer function  $N_{\text{TF}}$  as

$$S_{TF}(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}$$

(2.12)

$$N_{TF}(z) = \frac{Y(z)}{E(z)} = \frac{1}{1 + H(z)}$$

(2.13)

where H(z) is the transfer function of a discrete time filter. There have two important meanings in (2.12), (2.13). If we want to obtain highest SNR,  $S_{TF}$  must be equal to 1, that means the input signal can transfer to output without attenuating; and  $N_{TF}$  (z) must be equal to 0, because the quantization noise will not affect output SNR.

In order to make  $N_{TF}(z)$  be a high pass filter, so at DC(z=1),  $N_{TF}$  must be 0, and z=1 is a pole of H(z), so the transfer function H(z) of the discrete filter is as

$$H(z) = \frac{1}{Z - 1} = \frac{Z^{-1}}{1 - Z^{-1}}$$

(2.14)

Substitute (2.14) into (2.12) and (2.13), we can get

$$S_{TF}(z) = \frac{1}{z} \tag{2.15}$$

$$N_{TF}(z) = 1 - \frac{1}{z}$$

(2.16)

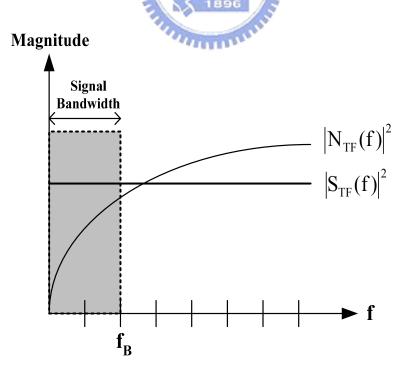

And we substitute z with  $e^{\frac{j^2\pi f}{fs}}$ , then we can plot  $|S_{TF}(f)|^2$  and  $|N_{TF}(f)|^2$  in frequency domain, as Fig. 2.9. We can find  $|N_{TF}(f)|^2$  also increases with frequency, and  $|S_{TF}(f)|^2$  is always equal to 1, if we choose signal bandwidth in low frequency, then we can get highest signal power and lowest noise power, from this figure we see that quantization noise is moved to higher frequency significantly, this is the noise shaping effect.

Fig. 2.9 Noise shaping

After noise shaping, we can filter out the noise in high frequency by using digital filter, and we will illustrate its architecture more detail in the next chapter.

## Chapter 3

## **Architectures of Sigma-Delta Modulator**

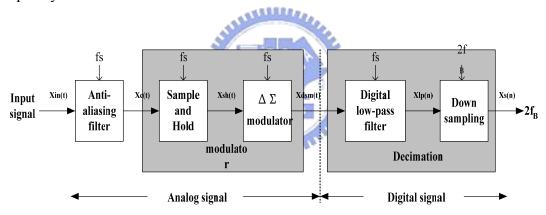

Before we introduce various architectures of  $\Sigma\Delta$  modulators, we must to realize the basic architecture of a general  $\Sigma\Delta$  A/D converter. Fig. 3.1 is a complete block diagram of a  $\Sigma\Delta$  A/D converter [Joh 97], and we can divide it into two different parts. First part is the  $\Sigma\Delta$  modulator. The main function of this part is doing oversampling and noise shaping to the input analog signal. Second part is the decimation filter. The main function of this part is to remove noise in high frequency and down sampling the sampling frequency to base band frequency.

Fig. 3.1 Block diagram of  $\Sigma\Delta$  A/D converter

First, the input signal Xin(t) pass an Anti-aliasing filter, the 3dB frequency of this filter is about few times of Nyquist frequency, so signal and noise out of Nyquist frequency is filtered roughly, and this signal goes into the  $\Sigma\Delta$  modulator after goes through a S/H circuit. However, in the circuits implement situation, the sample and hold function is included in the circuits of  $\Sigma\Delta$  modulator, so the signal Xc(t) will pass this modulator and produces a high speed data code Xdsm(n), because of noise shaping, the quantization noise will appear in high frequency. Finally, we must filter the noise in high frequency and reduce the sampling

frequency to Nyquist frequency by a decimator, and passes the digital signal to the output [Joh 97].

In this chapter, we will focus on the architectures of  $\Sigma\Delta$  modulator, because that the noise model and optimal method is focus on this part, we must understand the theorem, benefits and drawbacks of each kinds of  $\Sigma\Delta$  modulators. In addition, the implement of decimator is very typical [Ner 02][Mok 94]. In today's technology, DSP processors are also used to replace decimators, so we will introduce this part roughly.

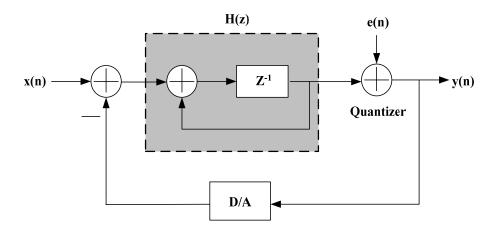

### 3.1 First-Order Sigma-Delta Modulator

We recall that H(z) in (2.14) is  $\frac{Z^{-1}}{1-Z^{-1}}$ , substitute it into Fig. 2.8, then we can get a first-order  $\Sigma\Delta$  modulator; Analyze transfer function H(z) from time-domain, it indicates that output signal m(t) is obtained by adding the delayed input signal n(t-1) and the delayed output signal m(t-1), so we can express a complete first-order  $\Sigma\Delta$  modulator as Fig. 3.2.

Fig. 3.2 First-order  $\Sigma\Delta$  modulator

H(z) in Fig. 3.2 is indicated the effects of delay and accumulation, this is equivalent with an integrator in circuit design, so the three circuits components of  $\Sigma\Delta$  modulator are integrator, quantizer and DAC in the feedback path.

A first order  $\Sigma\Delta$  modulator's output can represent as

$$Y(z) = z^{-1}X(z) + (1 - z^{-1})E(z)$$

(3.1)

From (3.1) we can find the signal transfer function is as a delay function, and noise transfer function is as a high pass filter, moves the noise to high frequency. In order to derive PSNR of first order  $\Sigma\Delta$  modulator, we must get the magnitude of NTF(z) and STF(z) in the frequency domain, so we substitute z with  $e^{j2\pi \cdot f/f_s}$ , and get  $\left|S_{TF}(f)\right|$  and  $\left|N_{TF}(f)\right|$  respectively as:

$$|S_{TF}(f)| = |z^{-1}| = |e^{-j2\pi \cdot f/f_s}| = 1$$

$$N_{TF}(f) = 1 - e^{-j2\pi \cdot f/f_s} = \sin(\frac{\pi f}{f_s}) \times 2j \times e^{-j\pi \cdot f/f_s}$$

(3.2)

$$\Rightarrow |N_{TF}(f)| = 2 \cdot \sin(\frac{\pi f}{f_c}) \tag{3.3}$$

So the quantization noise in base band  $\pm f_B$  can obtain by (2.7) and (3.3)

$$P_{Q} = \int_{-f_{B}}^{f_{B}} S_{e}^{2}(f) \cdot |N_{TF}(f)|^{2} df = \int_{-f_{B}}^{f_{B}} \frac{V_{LSB}^{2}}{12 \cdot f_{s}} \cdot \left[ 2 \sin \left( \frac{\pi f}{f_{s}} \right) \right]^{2} \cdot df$$

(3.4)

Because that fB is much lower than  $f_s$ , so  $\sin(\pi f/f_s)$  is approximate equal to  $(\pi f/f_s)$ , and  $P_Q$  is as

$$P_{Q} = \frac{V_{LSB}^{2} \pi^{2}}{36} \cdot (\frac{1}{OSR})^{3} = \frac{FS^{2} \cdot \pi^{2}}{36 \cdot 2^{2B} \cdot OSR^{3}}$$

(3.5)

From (2.5) and (3.5), if we have the maximum signal power, then PSNR is as (3.6)

$$PSNR = 10 \log(\frac{P_{signal}}{P_{Q}}) = 10 \log(\frac{3}{2}2^{2B}) + 10 \log[\frac{3}{\pi^{2}}(OSR)^{3}]$$

$$= 6.02B + 1.76 - 5.17 + 30 \log(OSR)$$

(3.6)

From (3.6), we find that each octave of OSR, PSNR will increase 9dB, increase 1.5 bit in resolution. Compare (3.6) with (2.10) that only has oversampling effect; we can find that  $1^{st}$  order noise shaping increases the performance of  $\Sigma\Delta$  modulator.

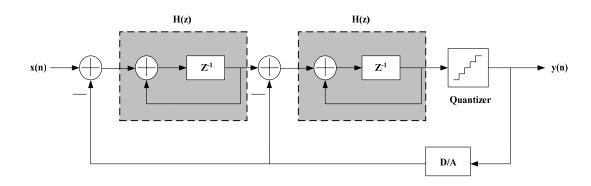

### 3.2 Single-Loop Second-Order Sigma-Delta Modulator

When the discrete time filter in Fig. 2.8 is replaced by two cascade integrator, then it is a second order  $\Sigma\Delta$  modulator, output of the first integrator is only connecting with the input of the second integrator, it is shown in Fig. 3.3

Fig. 3.3 Single loop second order  $\Sigma\Delta$  modulator

Then the output of it can easily be derived as

$$Y(z) = z^{-2}X(z) + (1 - z^{-1})^{2}E(z)$$

(3.7)

where S<sub>TF</sub> and N<sub>TF</sub> is as

$$S_{TF}(z) = z^{-2}$$

(3.8)

$$N_{TF}(z) = (1 - z^{-1})^2$$

(3.9)

Using the same method in (3.3) (3.4), we can obtain

$$\left|\mathbf{S}_{\mathrm{TF}}(\mathbf{f})\right| = 1\tag{3.10}$$

$$\left|N_{TF}(f)\right| = \left[2 \cdot \sin\left(\frac{\pi f}{f_s}\right)\right]^2 \tag{3.11}$$

$$P_{Q} = \frac{V_{LSB}^{2} \cdot \pi^{4}}{60 \cdot QSR^{5}} = \frac{FS^{2} \cdot \pi^{4}}{2^{2B} \cdot 60 \cdot QSR^{5}}$$

(3.12)

So finally, PSNR of the second order  $\Sigma\Delta$  modulator is as

PSNR =

$$10 \log(\frac{P_{\text{signal}}}{P_{\text{Q}}}) = 10 \log(\frac{3}{2}2^{2B}) + 10 \log[\frac{5}{\pi^4}(\text{OSR})^5]$$

$$= 6.02B + 1.76 - 12.9 + 50 \log(OSR)$$

(3.13)

In the single loop second order architecture, each octave of OSR can increase PSNR by 15 dB, it is equivalent to 2.5 bit in resolution. If we compare (3.13), (3.11) with |NTF(f)|=1 that without noise shaping, as Fig. 3.4, we can find that in our needed signal bandwidth, the

quantization noise is highest when |NTF(f)|=1, and that with second order noise shaping is smallest among this figure [Joh 97].

### 3.3 Single-Loop High Order Sigma-Delta Modulator

Fig. 3.5 is a single loop high order  $\Sigma\Delta$  modulator, from the derivation in Section 3.1 and Section 3.2, we can get the quantization noise PQ in signal bandwidth is as

$$P_{Q} = \frac{V_{LSB}^{2}}{12} \cdot \frac{\pi^{2L}}{2L+1} \cdot (\frac{1}{OSR})^{2L+1} , L : order$$

(3.14)

and its PSNR is

$$PSNR = 6.02B + 1.76 - 10 \log(\frac{\pi^{2L}}{2L+1}) + (20L+10) \log(OSR)$$

(3.15)

In the application of high order  $\Sigma\Delta$  modulator, (6L+3)dB increases in SNR when OSR is octave, so PSNR can be raised by increasing the order of the system, especially at large oversampling ratio. But sometimes in high order architecture, the performance will be worsen than result predicted by (3.13), because of the stability problem, it will make less effective noise shaping function, so the quantization noise will not be suppressed completely.

Fig 3.5 Single-loop high order  $\Sigma\Delta$  modulator

### 3.4 Interpolative Sigma-Delta Modulator

Interpolative is a kind of high order  $\Sigma\Delta$  modulator, it changes connection of some stages, adds some feedforward paths and feedback paths in order to suppose more aggressive noise shaping effect, Fig. 3.6 is a four-order interpolative architecture  $\Sigma\Delta$  modulator [Cha 90].

Fig. 3.6 Four-order interpolative architecture

This architecture also has stability problem, when the order L increases, each integrator produces one pole, and when the order is higher, poles of this system will also increase, and it will cause unstable situation, so the range of integrator gain will be limited; if the range of integrator gain is small, oscillation will appear in the circuits. Another is the considerations of clock control, when we use SC (switched-capacitor) to implement the integrator, each integrator needs two clocks to control its operation, and we will need more clock to control the integrator when the order of system increases, it will produce more problems.

#### 3.5 MASH Architecture

MASH (Multi-stage noise shaping) architecture is also called cascade architecture, which is a method that cascades several low order loops modulator in order to get high order noise shaping effect. The fundamental ideal of MASH is delivering quantization noise of front stage to input of next stage, and combining the digital outputs of all the stages with proper transfer function in digital domain, only the quantization noise of last stage will appear at the output, and the orders of  $N_{TF}$  is the same with total orders in the cascade  $\Sigma\Delta$  modulator. Fig 3.7 is a three-order cascade  $\Sigma\Delta$  modulator, its is the combination of a second-order and first-order  $\Sigma\Delta$  modulator, so also called 2-1 cascade architecture [Wil 94].

Fig. 3.7 2-1 architecture MASH  $\Sigma\Delta$  modulator

From Fig. 3.7, we can derive the first stage output  $Y_1(z)$  can be represented as

$$Y_1(z) = z^{-2}X_1(z) + (1-z^{-1})^2E_1(z)$$

(3.16)

Output of second stage  $Y_2(z)$  is as

$$Y_2(z) = z^{-1}X_2(z) + (1 - z^{-1})E_2(z)$$

(3.17)

and overall output of MASH Y(z) is as

$$Y(z) = H_1(z)Y_1(z) + H_2(z)Y_2(z)$$

(3.18)

and we can say that second stage input  $X_2(z)$  is almost the same with  $E_1(z)$ , in order to eliminate first stage quantization noise  $E_1(z)$ , from (3.16) ~ (3.18), we can define the error cancellation functions  $H_1(z)$  and  $H_2(z)$  as

$$H_1(z) = z^{-1}$$

(3.19)

$$H_2(z) = (1-z^{-1})^2$$

(3.20)

From (3.16)~(3.20),  $E_1(z)$  can be eliminated, and second stage quantization noise  $E_2(z)$  is shaped by third-order noise shaping function, and the MASH output Y(z) is as

$$Y(z) = z^{-3}X_1(z) + (1 - z^{-1})^3 E_2(z)$$

(3.21)

The most significant advantage of this architecture is that stability is not an issue, because it is composed by several low-order systems, and the quantization noise will not be amplified stage by stage, so its stability is good. Most important, the noise shaping function is equivalent as high order  $\Sigma\Delta$  modulator, so it is popular in recent publications [Rio 04][Vle 01]. However, there also have some drawbacks of this topology; it is sensitive to the circuits' imperfections, such as finite DC gain of OTA, variance of integrator gain due to capacitor mismatch and non-zero switch resistance. These are all practical considerations when we design a MASH architecture  $\Sigma\Delta$  modulator [Gag 03].

### 3.6 Multi-bit Quantizer Sigma-Delta Modulator

The demands of high resolution and high bandwidth ADC are more and more in recent years. In a high signal bandwidth, OSR of  $\Sigma\Delta$  ADC can't be too high, and the peak SNR of a  $\Sigma\Delta$  modulator with such limited OSR can't satisfy of high resolution applications, if we use higher order architecture, then the performance will degrade due to instability. So the most general method to increase performance is to use multibit quantizer. The most obvious advantage of using multibit quantizer is that the distance between quantizer level VLSB in (2.4)

is much smaller due to increasing of B, and according to (2.3), the power of quantization noise is attenuated. Fig. 3.8 is the results of theoretical peak SNR of  $\Sigma\Delta$  modulator versus oversampling ratio, with different order and quantizer bits, it is noted that peak SNR of the same OSR is increase 6 dB with each additional bit number in quantizer, and at low OSR, low order higher bit number architecture has equivalent performance as high order architecture. This result is usable for high bandwidth applications, and the power consumption of digital circuit in  $\Sigma\Delta$  modulator is reduced due to lower sampling rate [Pel 99].

Fig. 3.8 SNR vs. OSR with different quantizer bit number

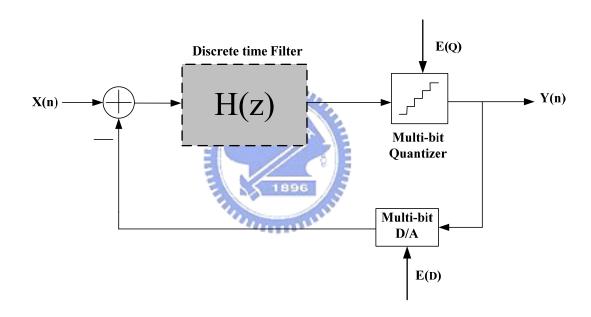

Because of using multi-bit quantizer, so we also need to use multi-bit DAC(Digital-to Analog Converter) to transfer the digital output to analog signal, and feed it back to integrator. The most significant disadvantage is the non-linearities introduced by multi-bit DAC can degrade the performance of  $\Sigma\Delta$  converter, like Fig. 3.9. It is a linear model of multi-bit  $\Sigma\Delta$

modulator, where E(Q) and E(D) represent the quantization noise and feedback DAC noise respectively. The values of these capacitor elements in DAC will not equal to ideal values that we need, it is due to process variation, typical value of mismatch in modern CMOS technology is about 0.05% ~ 0.5%. In recent years, so many researches are make efforts on reduce DAC noise due to mismatch, such as trimming [Nor97], Dynamic element matching(DEM)[Mil 03][Reb 90], although trimming is effective, but it has a expensive production step. So, DEM becomes more and more popular because of its efficiency and cheaper cost.

Fig. 3.9 Multi-bit architecture

#### 3.7 Multi-bit Sigma-Delta Modulator use DEM Technique

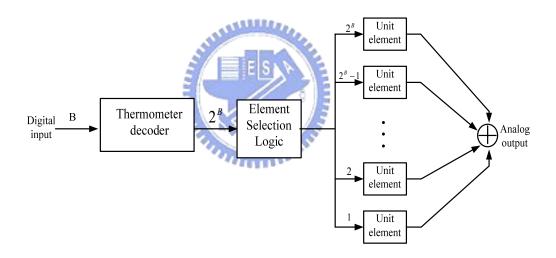

Dynamic element matching is a different approach to decrease the DAC noise, it is used to improve the linearity of pure DACs [Pla 79], but now it is most used in inner DAC of multi-bit  $\Sigma\Delta$  modulator. A DAC with DEM technique is illustrated in Fig. 3.10,  $2^B$  bits

thermometer code is put into the element selection logic block, and the function of element selection logic is try to select DAC elements in such way let the errors introduced by DAC average to zero for several operation periods. Because the DEM block is located in feedback loop, so its delay must be very small prevent to degrade the performance of  $\Sigma\Delta$  converter, therefore the algorithm used in the DEM block must be simple. There are several techniques of DEM, such as Randomization [Car 89], Clocked Averaging (CLA) [Pla 79], Individual Level Averaging (ILA) [Che 95], Data Weighted Averaging (DWA) [Bai 95], Randomization is the first approach to use DEM technique in  $\Sigma\Delta$  ADC, and DWA offers a good performance to reduce DAC error, in this section, an overview introduction of these two algorithms will be presented, and the operation principle of them will be explained.

Fig. 3.10 A B-bit DAC with DEM technique

#### 3.7.1 Randomization Technique

The main operation principle of randomization is that the element selection logic performs as a randomizer. In each clock period, the randomizer selects DAC elements randomly to generate the output of DAC. If the randomizer is ideal, then the DAC noise will become uncorrelated with each other. Simulation results show that randomization DEM

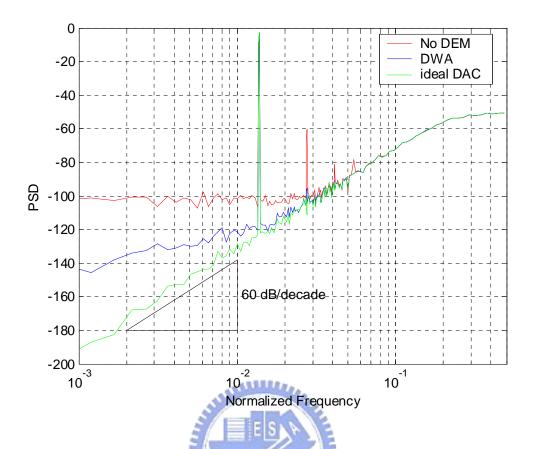

technique reduces the noise floor from DAC error by several dB, but it still be a white noise in low frequency. Fig. 3.12 is the output spectrum of a second-order  $\Sigma\Delta$  modulator with a 0.1% capacitor mismatch, it is notable that the noise floor of randomization DEM is lower than that without any calibration technique in the feedback DAC.

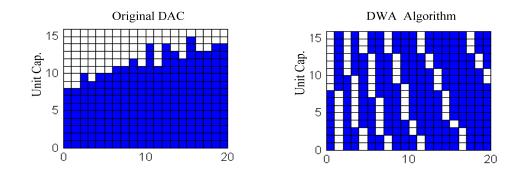

#### 3.7.2 Data Weighted Averaging (DWA)

DWA is a efficiently method to reduce DAC mismatch noise, it uses one register to remember the capacitor last time used, and always points to the first unused unit capacitor in this clock, so DWA rotates through all the unit capacitors such that all capacitors are used at the maximum possible rate. From this algorithm, each elements is used the same number of times in long interval, this ensures that the errors caused by the DAC average to zero quickly. In Fig. 3.11, it is a 4-bit DAC and the shaded boxes are the number of 1's in the thermometer code. Assumes that the input codes sequence is 8, 8, 10, 9, 10, 10, 11, 11, 12, 11, 14, 11, 14, 13, 12, 15... Fig. 3.12 is the simulation results of a third order  $\Sigma\Delta$  modulator, we can see that without DEM has highest noise floor and DWA works as a first order noise shaping function of DAC noise, ideal DAC only with quantization noise has third-order noise shaping.

Fig. 3.11 Operation principle of the DWA algorithm

Fig. 3.12 Output spectrum with three kinds of DAC

Another consideration is the sub-ADC(quantizer) of the  $\Sigma\Delta$  modulator, we usually use Flash A/D as the multi-bit quantizer because of its high speed, but Flash A/D has a significant disadvantage is that the number of comparators of it is proportional to  $2^B$ . That means a 6 bit quantizer needs 64 comparators, the occupied area of comparator may not much, but in modern SOC applications, the problems of power and area are important, so it becomes one limitation of multi-bit quantization.

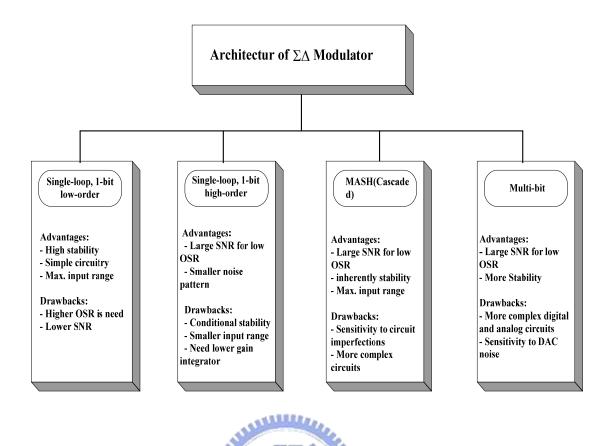

$\Sigma\Delta$  A/D converter is attractive for high resolution application, for higher signal bandwidth, we increase system order to raise SNR, but it still have stability problem. So people develop MASH and multi-bit architecture to improve its performance. Finally, we classify they into low order, high order, MASH and multi-bit four kinds of architecture, and compare their advantage and disadvantage as Fig. 3.13 [Med 99]

Fig. 3.13 Comparison of  $\Sigma\Delta$  modulator architectures

#### 3.8 Decimator

In  $\Sigma\Delta$  A/D converter, digital decimator is used to process digital signal of the quantizer output, the high speed data word after oversampling modulation can't be used directly. Because there have original signal and quantization noise among it, so the main function of decimator is to convert the oversampled B-bit output words of the quantizer at a sampling rate of fs to N-bit words at Nyquist rate of input, and removes the noise out of signal band. In order to prevent the noise introduced by other frequency, the decimator filter must have very flat signal pass-band, and sharp transition region and enough signal attenuation in stop band. Two-stage decimator is used in a general situation, because that single stage decimator is difficult to convert sampling rate to Nyquist rate in 1 time and without degrading SNR. In the

first stage, we can down-sample the sample frequency to 2~4 times of Nyquist frequency, and in the second stage, we can use IIR or FIR filter that have high linearity [Nor 97]. For a large OSR, multi-stage decimator is used.

#### **3.9 Performance Metrics for a** ΣΔ **Modulator**

In order to understand the performance merits used to specify the behavior of  $\Sigma\Delta$  modulator, several specifications concerning the performance are discussed [Gee 02].

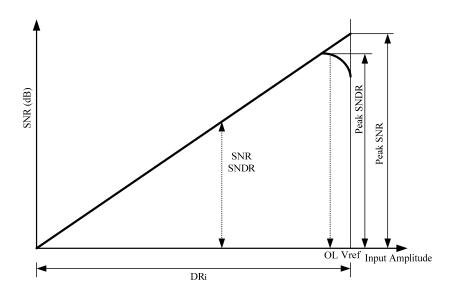

- **Signal to Noise Ratio:** The SNR of a data converter is the ratio of the signal power to the noise power, measured at the output of the converter for a certain input amplitude. The maximum SNR that a converter can achieve is called the peak SNR.

- **Signal to Noise and Distortion Ratio:** The SNDR of a converter is the ratio of the signal power to the power of the noise and the distortion components, measured at the output of the converter for a certain input amplitude. The maximum SNDR that a converter can achieve is called the peak SNDR.

- Dynamic Range at the input: The DRi is the ratio between the power of the largest input signal that can be applied without significantly degrading the performance of the converter, and the power of the smallest detectable input signal. The level of significantly degrading the performance is defined as the point where the SNDR is 6 dB bellow the peak SNDR. The smallest detectable input signal is determined by the noise floor of the converter.

- Dynamic Range at the output: The dynamic range can also be considered at the output of the converter. The ratio between maximum and minimum output power is the dynamic

range at the output DRo, which is exactly equal to peak SNR.

• Effective Number of Bits: ENOB gives an indication of how many bits would be required in an ideal quantizer to get the same performance as the converter. This numbers also includes the distortion components and can be calculated from (2.6) as

$$ENOB = \frac{SNR - 1.76}{6.02}$$

(3.22)

• Overload Level: OL is defined as the relative input amplitude where the SNDR is decreased by 6dB compared to peak SNDR

Typically, these specifications are reported using plots like Fig. 3.14. This figure shows the SNR and SNDR of the  $\Sigma\Delta$  converter versus the amplitude of the sinusoidal wave applied to the input of the converter. For small input levels, the distortion components are submerged in the noise floor of the converter. Consequently, the SNDR and SNR curves coincide for small input levels. When the input level increases, the distortion components start to degrade the modulator performance. Therefore, the SNDR will be smaller than the SNR for large input signals. Note that these specifications are dependent on the frequency of the input signal and the clock frequency of the converter. Fig. 3.14 also shows that SNDR curves drop very fast once the overload point is achieved. This is due to the overloading effect of the quantizer which results in instabilities.

Fig. 3.14 Performance characteristic of a  $\Sigma\Delta$  converter

## **Chapter 4**

# Models of Multi-Bit Sigma-Delta Modulator Power

The power estimation is presented for a sigma-delta converter with a certain accuracy and bandwidth specification. The influence of several design choices on the power-bandwidth-resolution trade-off will be discussed. This leads to some general design considerations.

The power estimation can be derived into the analog power consumption and the digital power consumption. The analog power consumption mainly includes the OTA of the integrator, the comparator of the quantizer, and the DAC from the quantizer to the integrator. The digital power consumption mainly includes the logic in the quantizer, the dynamic element matching algorithm, the CMOS switch and the clock generator. But in this paper, the digital power consumption only considers the CMOS switch and the clock generator.

### 4.1 Integrator power

The first considered power consumption is the integrator of the analog power consumption. The most power consumption is the OTA in the integrator. So, the total power consumption of the OTA can be written as

$$P_{OTA} = I_{OTA} \cdot V_{DD}$$

$$= k_{OTA} \cdot I_R \cdot V_{DD} \tag{4.1}$$

where  $I_{OTA}$  represents the total current of the OTA,  $I_B$  represents the bias current of the OTA,  $k_{OTA}$  represents the ratio of the total current of the OTA to this bias current and  $V_{DD}$  represents the supply voltage of the OTA. The factor  $k_{OTA}$  which depends on the number of current branches and the relative amount of current in each of them.

The ratio of the total current of the OTA to this bias current is represented by

$$I_B = \frac{1}{2} \cdot \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot V_{eff}^2 \tag{4.2}$$

Where  $V_{eff} = V_{GS} - V_{TH}$

For CMOS implementations, the OTA transconductance is related to the transconductance of a MOS transistor used in a differential input pair. The transconductance of the OTA to current relationship for a differential input pair is given by

$$g_m = \mu \cdot C_{OX} \cdot \frac{W}{L} \cdot V_{eff} = \frac{2I_B}{V_{eff}}.$$

(4.3)

So  $I_B$  can be written as

$$I_B = \frac{1}{2} \cdot g_m \cdot V_{eff} \tag{4.4}$$

where  $I_{\it B}$  represents the bias current of each transistor of the differential pair and  $V_{\it eff}$  represents the overdrive voltage.

The effective closed-loop load capacitance can be written as

$$C_{eq,cl} = C_S \cdot \left( 1 + \frac{C_P}{C_S} + \frac{C_L}{C_S} \left( 1 + \frac{C_S}{C_I} \left( 1 + \frac{C_P}{C_S} \right) \right) \right)$$

$$=k_{Cea.cl} \cdot C_S \tag{4.5}$$

where  $k_{Ceq,cl}$  represents the ratio between the effective closed-loop load capacitance and the sampling capacitance. It depends on the relative size of  $C_P$  and  $C_L$  compared to  $C_S$ . These sizes can only be determined when the OTA is designed since they depend on parasitic capacitances. The ratio of  $C_S$  to  $C_I$  is determined by loop-coefficient  $a_1$  of the sigma-delta converter[Gee 02].

The gain-bandwidth product of operational amplifier of the first integrator is a function of the equivalent load capacitor  $C_{eq,cl}$  and of the transconductance  $g_m$ , according to

$$f_{cl2} = \frac{g_m}{2\pi \cdot C_{eq,cl}} = \frac{g_m}{2\pi \cdot k_{Ceq,cl} \cdot C_S}.$$

(4.6)

The bias current of each transistor of the differential pair combined the gain-bandwidth product of operational amplifier with the equivalent load capacitor, so  $I_B$  can be written as

$$I_{B} = \frac{1}{2} g_{m} \cdot V_{eff}$$

$$= \frac{1}{2} \cdot f_{cl2} \cdot (2\pi \cdot k_{Ceq,cl} \cdot C_{S}) \cdot V_{eff}$$

$$= \pi \cdot k_{Ceq,cl} \cdot C_{S} \cdot V_{eff} \cdot f_{cl2}$$

$$(4.7)$$

It may be stated from the above results that the total power consumption of first OTA can

be written as

$$P_{OTA} = I_{OTA} \cdot V_{DD}$$

$$= k_{OTA} \cdot I_B \cdot V_{DD}$$

$$= k_{OTA} \cdot \left(\pi \cdot k_{Ceq,cl} \cdot C_S \cdot V_{eff} \cdot f_{cl2}\right) \cdot V_{DD}$$

$$= \pi \cdot k_{OTA} \cdot k_{Ceq,cl} \cdot C_S \cdot f_{cl2} \cdot V_{eff} \cdot V_{DD}$$

$$(4.8)$$

The power consumption of the first integrator is almost consumed in the first OTA. So this equation can be extended to the total analog power consumption of all the integrators in a sigma-delta converter by introducing the factor  $k_{\Delta\Sigma}$  which represents the ratio between the total current consumption of all the OTAs and the first OTA. The total analog power consumption of the integrators in a sigma-delta converter is given by

$$\begin{split} P_{an} &= I_{\Delta\Sigma} \cdot V_{DD} \\ &= k_{\Delta\Sigma} \cdot I_{OTA} \cdot V_{DD} \\ &= \pi \cdot k_{\Delta\Sigma} \cdot k_{OTA} \cdot k_{Ceq,cl} \cdot C_S \cdot f_{cl2} \cdot V_{eff} \cdot V_{DD} \end{split} \tag{4.9}$$

The analog power consumption is not included the power consumption of the quantizer yet.

$k_{OTA}$  indicates how much current the OTA consumes, relative to the bias current of one transistor of the differential input pair. This depends on the chosen OTA architecture. Three different alternatives are now briefly compared.

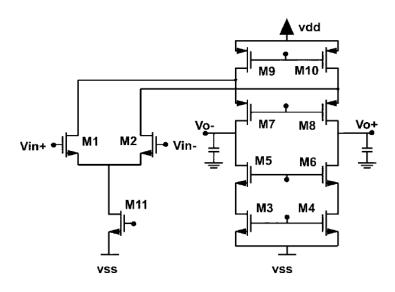

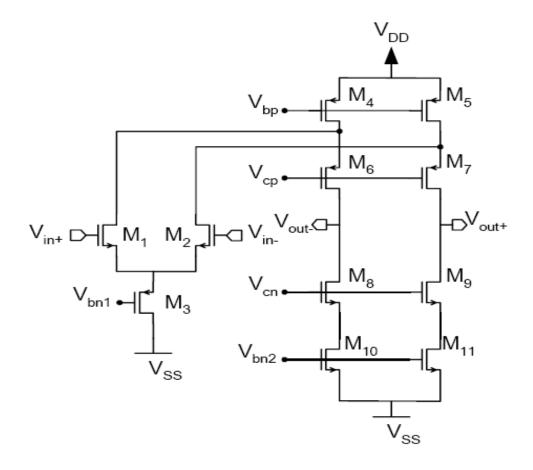

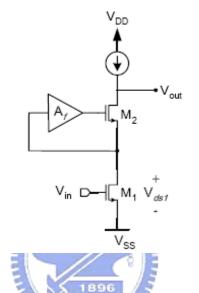

A single-stage telescopic OTA is shown in the Figure 1[Kus 98]. It can provide a large gain, has an excellent frequency performance and has only two current branches. This means  $k_{OTA}$  is only two. The mean drawback is the small output swing since it has five stacked transistors which have to remain in saturation region. Furthermore, it becomes difficult to employ the same common-mode levels at the input and the output of the OTA.

Figure 4.1 A single-stage telescopic OTA

The folded cascode OTA is shown in the Figure 2[Kus 98]. It can provide a large gain, and has an excellent frequency performance. The frequency performance of the folded cascade OTA is worse than the frequency performance of the telescopic OTA because more parasitic capacitances are associated with the non-dominant pole. The folded cascode OTA has two current branches that resulting in a value of four for  $k_{OTA}$ .

Compared with the telescopic OTA, the main advantages of the folded cascade OTA are the large output swing and the larger range for the input common-mode level. Because the folded cascode OTA only has four transistors need to remain in saturation.

Figure 4,2 The folded cascode OTA

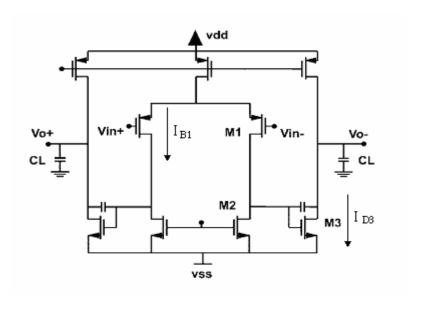

The two-stage Miller-compensated OTA is shown in the Figure 3[Kus 98]. It also can provide a large gain, but the frequency performance is worse. The dominant pole is determined by the compensation capacitance. The non-dominant pole is determined by the ratio of the transconductance of the output stage to the load capacitance. Compared with the telescopic OTA and the folded cascade OTA, the  $k_{OTA}$  of the two-stage Miller-compensated OTA is difficult to get it. Because the two-stage Miller-compensated OTA must improve the frequency performance by the compensation capacitance. The transconductance of the two-stage Miller-compensated OTA to current relationship for a differential input pair is

$$g_{m1} = \frac{2I_{B1}}{V_{GS1} - V_T} \,. \tag{4.10}$$

And, the bandwidth of the two-stage Miller-compensated OTA to transconductance relationship for a differential input pair is

$$\frac{g_{m1}}{C_M} = 2\pi \cdot f_{cl2} \tag{4.11}$$

where  $C_{\scriptscriptstyle M}$  is the Miller compensation capacitance.

So, the bandwidth of the two-stage Miller-compensated OTA to current relationship for a differential input pair is

$$I_{B1} = \frac{1}{2} g_{m1} \cdot (V_{GS1} - V_T)$$

$$= \frac{1}{2} \cdot 2\pi \cdot f_{cl2} \cdot C_M \cdot (V_{GS1} - V_T)$$

$$= \pi \cdot f_{cl2} \cdot C_M \cdot (V_{GS1} - V_T). \tag{4.12}$$

The non-dominant pole, which is created by the load capacitance, should be placed beyond the three times of the  $f_{cl2}$ [Lib 04]. This criterion is shown as

$$\frac{g_{m3}}{C_M + C_{eq,cl}} = 3 \cdot 2\pi \cdot f_{cl2}$$

$$= 6\pi \cdot f_{cl2}.$$

(4.13)

So, the bandwidth of the two-stage Miller-compensated OTA to the branch current relationship is

$$I_{D3} = \frac{1}{2} g_{m3} \cdot (V_{GS3} - V_T)$$

$$= \frac{1}{2} \cdot 6\pi \cdot f_{cl2} \cdot (C_M + C_{eq,cl}) \cdot (V_{GS3} - V_T)$$

$$= \pi \cdot f_{cl2} \cdot (3C_M + 3C_{eq,cl}) \cdot (V_{GS3} - V_T). \tag{4.14}$$

In general design of the operational amplifier, the phase margin usually is about  $60^{\circ}$ . Assuming that a  $60^{\circ}$  phase margin is required, the following relationships apply[Phi 02]:

$$C_M \ge 0.22C_{eq.cl}$$

(4.15)

Let

$$V_{GS3} - V_T = V_{GS1} - V_T. (4.16)$$

Therefore, the bandwidth of the two-stage Miller-compensated OTA to current relationship for a differential input pair is also written as

$$I_{B1} = \pi \cdot f_{cl2} \cdot C_M \cdot (V_{GS1} - V_T)$$

$$= 0.22\pi \cdot f_{cl2} \cdot C_{eq,cl} \cdot (V_{GS1} - V_T).$$

(4.17)

And, the bandwidth of the two-stage Miller-compensated OTA to the branch current relationship is also written as

$$I_{D3} = \pi \cdot f_{cl2} \cdot (3C_M + 3C_{eq,cl}) \cdot (V_{GS3} - V_T)$$

$$= \pi \cdot f_{cl2} \cdot (3 \cdot 0.22C_{eq,cl} + 3C_{eq,cl}) \cdot (V_{GS1} - V_T)$$

$$= 3.66\pi \cdot f_{cl2} \cdot C_{eq,cl} \cdot (V_{GS1} - V_T). \tag{4.18}$$

Consequently, the total currents of the two-stage Miller-compensated OTA can be written as

$$I_{Miller} = 2I_{B1} + 2I_{D3}$$

$$= 2 \cdot \left[ \pi \cdot f_{cl2} \cdot C_M \cdot (V_{GS1} - V_T) \right] + 2 \cdot \left[ \pi \cdot f_{cl2} \cdot (3C_M + 3C_{eq,cl}) \cdot (V_{GS3} - V_T) \right]$$

$$= 2 \cdot \left[ 0.22\pi \cdot f_{cl2} \cdot C_{eq,cl} \cdot (V_{GS1} - V_T) \right] + 2 \cdot \left[ 3.66\pi \cdot f_{cl2} \cdot C_{eq,cl} \cdot (V_{GS1} - V_T) \right]$$

$$= 7.76\pi \cdot f_{cl2} \cdot C_{eq,cl} \cdot (V_{GS1} - V_T). \tag{4.19}$$

This means  $k_{OTA}$  is only 7.76 for the two-stage Miller-compensated OTA.

Figure 4.3 The two-stage Miller-compensated OTA

$k_{\Delta\Sigma}$  represents the ratio between the total current consumption of all the OTAs and the first OTA. At first sight, one would expect that it increases significantly as the order of the converter increases since an extra OTA is required.

$k_{\textit{Ceq,cl}}$  represents the ratio between the effective closed-loop load capacitance and the sampling capacitance.

#### 4.2 Quantizer power

A multi-bit quantizer is used to quantize the analog signal to multi-level digital output signal in the implementation of a multi-bit sigma-delta modulator. The multi-bit quantizer is implemented by Nyquist-rate analog to digital converter. In the multi-bit sigma-delta modulator, the power estimation for the quantizer can be as the power estimation for the Nyquist-rate ADC. There are many parameters to be considered for the quantizer (Nyquist-rate ADC) like the speed and the accuracy.

The power is proportional to the supply voltage, the frequency and a charge. And, the power can be wrote as

$$P = V_{DD} \cdot I = V_{DD} \cdot f \cdot \text{Charge}. \tag{4.20}$$

From the equation (20), we can find a question. The question is what frequency should be considered for the multi-bit quantizer and then which charge is being transferred. The quantizer has two parts, comparators and processing circuitry. The comparator is clocked at frequency of the sample and the processing circuitry varies at the frequency of the input signal. So the equation (1) can be wrote as [Eri 02]

$$P = P_{comparator, fs} + P_{processing\ circuit, fb}. \tag{4.21}$$

and

$$P = V_{DD} \cdot f \cdot (Voltage \ swing) \cdot C \ . \tag{4.22}$$

The voltage swing for the comparators is always the full supply voltage. So the equation (22) can be wrote as

$$P = V_{DD}^{2} \cdot C \cdot f . \tag{4.23}$$

About the capacitances is not easy to estimate in the quantizer. Therefore, the equality is replaced by a proportionality and the capacitance is taken proportional to the technology's minimal channel length. So the following equation for the total power estimator is [Eri 02]

$$P \propto V_{DD}^{2} \cdot L_{\min} \cdot (fs + fb). \tag{4.24}$$

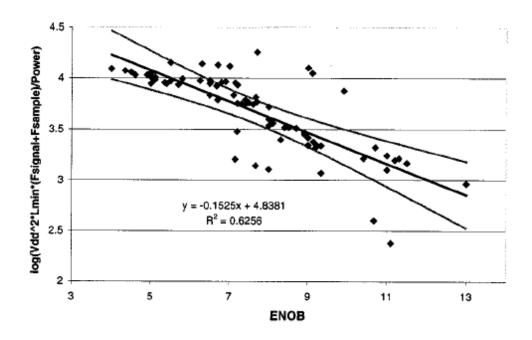

The accuracy is expressed as the effective number of bits (ENOB), which is defined as shown in the well-known [Eri 02]

$$ENOB = \frac{20 \cdot \log(SNDR) - 1.76}{6.02}.$$

(4.25)

where SNDR represents the signal-to-noise-and-distortion ratio. The accuracy expressed in (6) is related to the size of the devices and in this way to the power (5): this correlation has been investigated for 75 data points as show in Figure 4 [Eri 02]. From the Figure 4, we can get the following regression relation[Eri 02]

$$\log\left(\frac{V_{DD}^{2} \cdot L_{\min} \cdot (fs + fb)}{P_{Q}}\right) = -0.1525 \cdot ENOB + 4.8381. \tag{4.26}$$

So the final power estimator for the complete CMOS Nyquist-rate ADC can be written as [Eri 02]

$$P_{Q} = \frac{V_{DD}^{2} \cdot L_{\min} \cdot (fs + fb)}{10^{(-0.1525 \cdot ENOB + 4.8381)}}.$$

(4.27)

Figure 4.4.An overview of the obtained data points. The ENOB are given as a function of the input signal

#### **4.3 DAC Power**

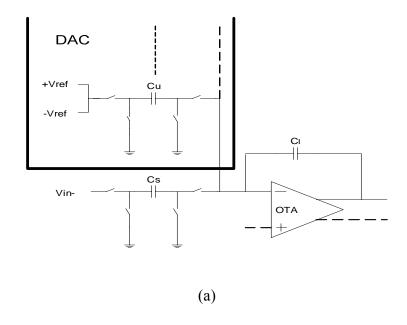

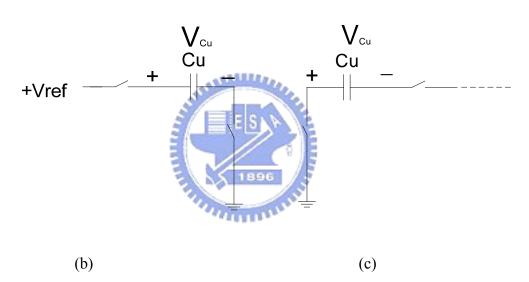

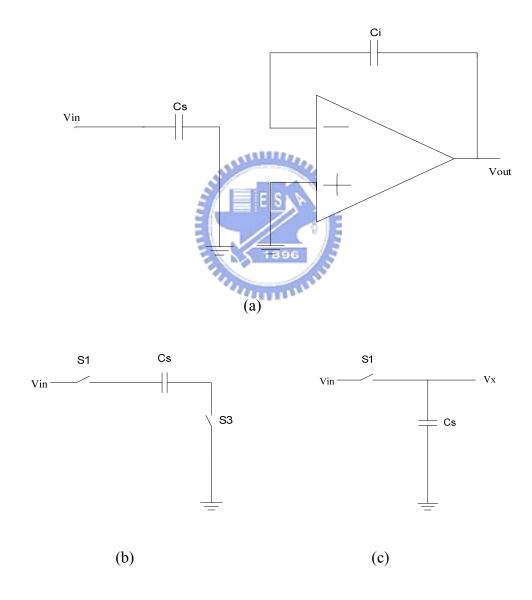

We estimate the power consumption of multi-bit DAC in the single-loop multi-bit sigma-delta converter. The multi-bit DAC is shown in Figure 5 (a) [Gag 03]. It is composed of switches and unit capacitors. At first, we consider charge and discharge for an unit capacitor in the multi-bit DAC. The operations of a unit capacitor are illustrated in Figure 5 (b) and Figure 5 (c) respectively. We assumed that the periods of charge and discharge both are T/2, the power consumption of a unit capacitor in the multi-bit DAC is

$$P_{u} = \frac{1}{T} \int_{0}^{T/2} V_{Cu} \cdot I_{u} dt + \frac{1}{T} \int_{T/2}^{T} (0 - V_{Cu}) \cdot I_{u} dt .$$

(4.28)

To employ charge conservation law, we can obtain (29):

$$I_{u} = Cu \frac{dV_{Cu}}{dt}. \tag{4.29}$$

When (29) substitutes for  $I_u$  in (29), (28) can be derived as

$$P_{u} = \frac{1}{T} \int_{0}^{T/2} V_{Cu} \cdot Cu \frac{dV_{Cu}}{dt} dt + \frac{1}{T} \int_{T/2}^{T} (0 - V_{Cu}) \cdot Cu \frac{dV_{Cu}}{dt} dt$$

$$= \frac{1}{T} \int_{0}^{Vref} V_{Cu} \cdot Cu \, dV_{Cu} + \frac{1}{T} \int_{Vref}^{0} (0 - V_{Cu}) \cdot Cu \, dV_{Cu}$$

$$= \frac{1}{T} \left( \frac{1}{2} \cdot V_{Cu}^{2} \cdot Cu \right) \begin{vmatrix} Vref \\ 0 \end{vmatrix} + \frac{1}{T} \left( 0 - \frac{1}{2} \cdot V_{Cu}^{2} \cdot Cu \right) \begin{vmatrix} 0 \\ Vref \end{vmatrix}$$

$$= \frac{1}{T} \left( \frac{1}{2} \cdot Vref^{2} \cdot Cu \right) + \frac{1}{T} \left[ 0 - \left( -\frac{1}{2} \cdot Vref^{2} \cdot Cu \right) \right]$$

$$= \frac{1}{T} Vref^{2} \cdot Cu = Vref^{2} \cdot Cu \cdot f_{s}$$

(4.30)

We can get the power estimation of a unit capacitor from (30), so the total power estimation for a multi-bit DAC is

$$P_{DAC} = 2 \cdot 2^{B} \cdot Cu \cdot Vref^{2} \cdot f_{s}$$

$$= 2 \cdot 2^{B} \cdot \frac{1}{2^{B}} Cs \cdot Vref^{2} \cdot f_{s}$$

$$= 2 \cdot Cs \cdot Vref^{2} \cdot f_{s}. \tag{4.31}$$

Figure 4.5 (a) Implementation of the integrator and the feedback DAC. (b) To charge the unit capacitance. (c) To discharge the unit capacitance.

## 4.4 Clock driver power and switch power

Static CMOS logic gates are very power-efficient because they dissipate nearly zero power while idle, so the primary dissipation component is the dynamic dissipation component.

And, the primary dynamic dissipation component is charging and discharging the load capacitance. For much of the history of CMOS design, power was a secondary consideration behind speed and area for many chips. As transistor counts and clock frequencies have increased, power consumption has skyrocketed and now is a primary design constraint.

Begin to review some definitions first. The instantaneous power P(t) drawn from the power supply is proportional to the supply current  $i_{DD}(t)$  and the supply voltage  $V_{DD}$

$$P(t) = i_{DD}(t) \cdot V_{DD}$$

(4.32)

The energy consumed over some time interval T is the integral of the instantaneous power. And, the energy can be wrote as

$$E = \int_{0}^{T} i_{DD}(t) \cdot V_{DD} dt . \tag{4.33}$$

The average power over this interval is

$$P_{avg} = \frac{E}{T} = \frac{1}{T} \int_{0}^{T} i_{DD}(t) \cdot V_{DD} dt.$$

(4.34)

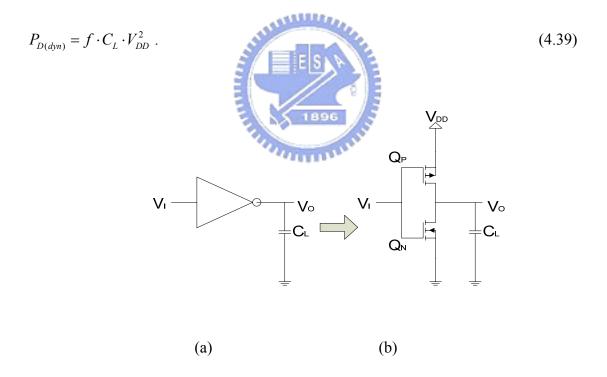

Considering an ideal inverter and a CMOS inverter with the load capacitor  $C_L$  are shown in Figure 6 (a) and Figure 6 (b) respectively. Giving a periodic square-wave from the input point is shown in Figure 6 (c). The associated NMOS transistor is ON and the PMOS transistor is OFF when the input signal approach high level voltage at  $t = 0^-$ . At the same time, the output voltage is 0 volts (GND).

Further, the associated NMOS transistor is OFF and the PMOS transistor is ON when the input signal voltage is changed from high level voltage to low level voltage at t=0. At the same time, the charging current pours into the load capacitor through the channel PMOS transistor, and the output voltage is going to approach high level voltage. At first, the energy of computation is  $E_S$  provided by the power supply is

$$E_{S} = \int V_{DD} \cdot i(t)dt = V_{DD} \cdot \int i(t)dt$$

$$=V_{DD} \cdot Q = V_{DD} \cdot (C_L \cdot V_{DD})$$

$$=C_L \cdot V_{DD}^2 . (4.35)$$

However, the energy  $E_{C}$  which stored up on the load capacitor is

$$E_C = \int V_{DD}(t) \cdot i(t) dt = \int V_{DD}(t) \cdot (C_L \cdot \frac{dv}{dt}) dt$$

$$= C_L \cdot \int V_{DD}(t) dv = \frac{1}{2} C_L \cdot V_{DD}^2.$$

(4.36)

Therefore, the energy  $E_P$  which dissipated on the PMOS transistor should be equal to the energy  $E_S$  provided by the power supply to subtract the energy  $E_C$  stored up on the load capacitance, also is

$$E_P = E_S - E_C$$

$$= C_L \cdot V_{DD}^2 - \frac{1}{2} C_L \cdot V_{DD}^2 = \frac{1}{2} C_L \cdot V_{DD}^2.$$

(4.37)

When  $t = T_1$ , the input signal  $V_I$  returns to the higher state once again so that the NMOS

transistor is ON and the PMOS transistor is OFF. After transformation, the load capacitor will be discharged through the channel of NMOS transistor, and leads to the power dissipation on the NMOS transistor. Consequently, the energy  $E_N$  which dissipated on the NMOS should be equal to the energy  $E_C$  stored up on the load capacitor, also is

$$E_N = E_C = \frac{1}{2} C_L \cdot V_{DD}^2. \tag{4.38}$$

For this reason, the total energy consumed by the logic gate in one cycle is  $(E_P + E_N) = C_L \cdot V_{DD}^2$ . If the input signal frequency of the CMOS inverter is f ,so the dynamic power dissipation  $P_{D(dyn)}$  is

Figure 4.6 (a) an ideal inverter for logic level with a load capacitance (b) an ideal CMOS inverter for transistor level with a load capacitance (c) a periodic square-wave for the input.

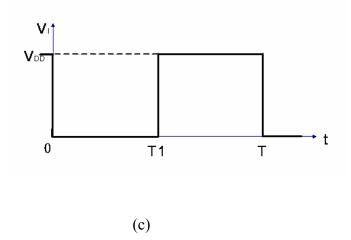

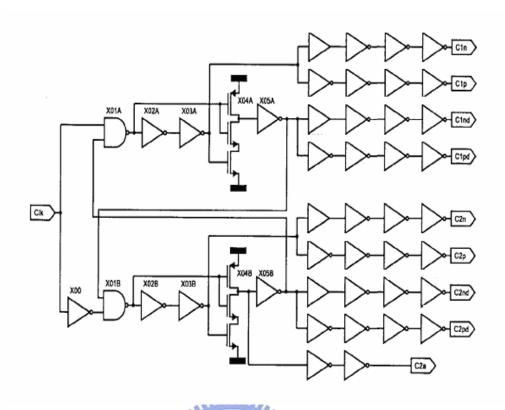

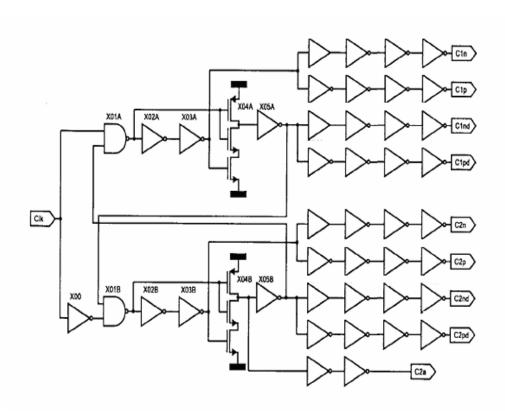

The switched-capacitor circuits and quantizers require various clock signals. These signals are generated on chip from one external clock signal. The switched-capacitor circuit requires two non-overlapping clocks for sampling and the integration phase. The clock generator with non-overlapping clocks is shown in Figure 2[Gee 02]. From Figure 7, it shows that the clock generator is composed of the logic gates. The primary logic gates which compose of the clock generator are inverters and the NAND gates. Assuming the clock generator has  $N_C$  logic gates, and the capacitance of one capacitor is  $C_{\mathrm{logic}}$ . Under these assumptions the power dissipation of the clock generator can be wrote as

$$P_{clock} = f \cdot C_{clock} \cdot V_{DD}^{2}$$

$$= N_{C} \cdot f \cdot C_{logic} \cdot V_{DD}^{2}. \tag{4.40}$$

Figure 4.7 the clock generator with non-overlapping clocks.

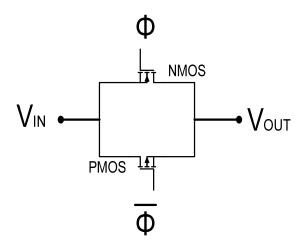

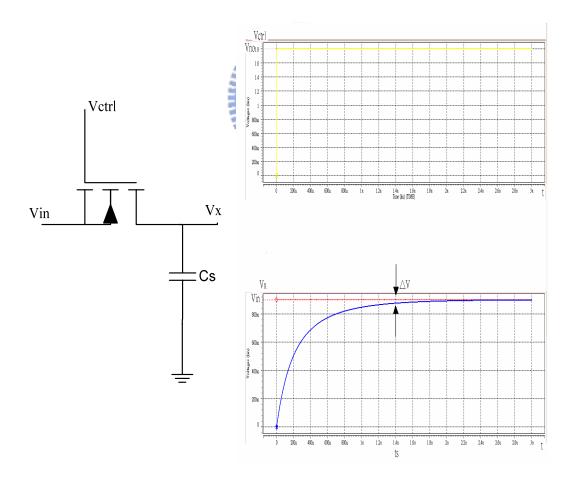

Another important component for the power dissipation is offered by CMOS transmitters in the switched-capacitor circuits. The output of the clock generator is connected to the gate of the CMOS switches in the switched-capacitor circuits. The CMOS switch is shown in Figure 4.8. Assuming that the number of the CMOS transmission gate in Sigma-Delta modulator is  $N_s$  and the gate capacitances of all CMOS transmission gates are  $C_{gate}$ . Under these assumptions the power dissipation of the CMOS switch can be wrote as

$$P_{switch} = f \cdot C_{switch} \cdot V_{DD}^2$$

$$=N_S \cdot f \cdot C_{gate} \cdot V_{DD}^2. \tag{4.41}$$

Figure 4.8 the CMOS switch

$C_{\rm gate}$  is the capacitance of the gate capacitor in one CMOS switch. The gate of an MOS transistor is a good capacitor. Indeed, its capacitance is necessary to attract charge to invert the channel of the transistor. The gate capacitor can be viewed as a parallel plate capacitor with the gate on top and channel on bottom with the thin oxide dielectric between. From the Table 1[Nei 05], it is clearly to observe that to get the approximation of intrinsic MOS gate capacitance with the CMOS switch. Because the voltage of the gate varies in  $V_{\rm DD}$  and GND, the status of the CMOS switch is either cut-off or linear. Consequently, the value of the gate capacitance  $C_{\rm gate}$  can be wrote as

$$C_{gate} = C_0$$

$$= C_{OV} \cdot W \cdot L . \tag{4.42}$$

where  $C_{OX}$  is the capacitance per unit area of the gate oxide, L is length of the gate, and W is width of the gate.  $C_{OX}$  can be wrote as

$$C_{OX} = \frac{\varepsilon_{OX}}{t_{OX}} \tag{4.43}$$

where the permittivity  $\varepsilon_{OX} = 3.9\varepsilon_0$  for  $SiO_2$  and  $\varepsilon_0$  is the permittivity of free space,  $8.85 \times 10^{-14}$  F/cm.

Besides,  $R_{CMOS}$  is the parallel resistance with  $R_N$  and  $R_P$ . Consequently,  $R_{CMOS}$  can be wrote as

$$R_{CMOS} = R_N // R_P$$

$$= \frac{1}{\mu_n \cdot C_{OX} \cdot \left(\frac{W}{L}\right)_n \cdot \left(V_{DD} - V_{tn} - \left|V_{tp}\right|\right)}.$$

(4.44)

Let  $R_{CMOS}$  be remained constant with the input signal level (44) employs the supposition that can be wrote as

$$\mu_n \cdot C_{OX} \cdot \left(\frac{W}{L}\right)_n = \mu_p \cdot C_{OX} \cdot \left(\frac{W}{L}\right)_p. \tag{4.45}$$

After combining the equation (42) with the equation (44), one may derive the results for the gate capacitance  $C_{\rm gate}$  so the gate capacitance  $C_{\rm gate}$  can be wrote as

$$C_{gate} = \frac{L_{\min}^{2}}{\mu_{n} \cdot R_{CMOS} \cdot (V_{DD} - V_{tn} - |V_{tp}|)}.$$

(4.46)

where  $L_{\min}$  represents the minimum manufacturable length because this results in greatest speed and lowest power consumption.

$C_{\log ic}$  is the value of the gate capacitance in one logic gate. Because the voltage of the

gate varies in  $V_{DD}$  and GND with the most logic gates, the status of the MOS of the logic gate is either cut-off or linear. Consequently, the value of the gate capacitance  $C_{\log ic}$  can be wrote as

$$C_{\log ic} = 2C_0$$

$$= 2C_{OV} \cdot W \cdot L . \tag{4.47}$$

Table 4.1 Approximation of intrinsic MOS gate capacitance

| Approximation of intrinsic MOS gate capacitance $(C_0 = C_{\it ox} {}^*\!W {}^*\!L)$ |         |                 |                                          |

|--------------------------------------------------------------------------------------|---------|-----------------|------------------------------------------|

| Parameter                                                                            | Cut-off | Linear          | Saturation                               |

| $C_{g_0}$                                                                            | $C_0$   | 0               | 0                                        |

| $C_{\mathfrak{g}}$                                                                   | 0       | $\frac{C_0}{2}$ | <sup>2C<sub>0</sub></sup> / <sub>3</sub> |

| $C_{\it gi}$                                                                         | 0       | C,/2            | 0                                        |

| $C_{\rm g} = C_{\rm gb} + C_{\rm go} + C_{\rm gd}$                                   | $C_0$   | $C_0$           | 2C <sub>0</sub> / <sub>3</sub>           |

It may be stated from the above result that the digital power consumption  $P_{\it dig}$  can be wrote as

$$P_{dig} = P_{clock} + P_{switch}$$

$$= N_C \cdot f \cdot C_{\log ic} \cdot V_{DD}^2 + N_S \cdot f \cdot C_{gate} \cdot V_{DD}^2$$

$$= N_C \cdot f \cdot \left(2C_{OX} \cdot W_{avg} \cdot L_{avg}\right) \cdot V_{DD}^2$$

$$+N_{S} \cdot f \cdot \left[ \frac{L_{\min}^{2}}{\mu_{n} \cdot R_{CMOS} \cdot \left(V_{DD} - V_{tn} - \left|V_{tp}\right|\right)} \right] \cdot V_{DD}^{2}. \tag{4.48}$$

where  $L_{avg}$  is average length and  $W_{avg}$  is average width of the logic gates in the clock generator.

The digital power consumption  $P_{dig}$  doesn't include the logic gates in the quantizer, and the dynamic element matching algorithm.

## 4.5 Verification for the power consumption model

By adding up all the contribution, the power dissipation of the sigma-delta modulator can be estimated as

$$Power \cong P_{an} + P_{Q} + P_{DAC} + P_{clock} + P_{switch}$$

$$= \pi \cdot k_{\Delta \Sigma} \cdot k_{\mathit{OTA}} \cdot k_{\mathit{Ceq,cl}} \cdot C_{\mathit{S}} \cdot f_{\mathit{cl2}} \cdot V_{\mathit{eff}} \cdot V_{\mathit{DD}}$$

$$+ \frac{{V_{\scriptscriptstyle DD}}^2 \cdot L_{\scriptscriptstyle \min} \cdot \left(fs + fb\right)}{10^{(-0.1525 \cdot ENOB + 4.8381)}}$$

$$+2 \cdot Cs \cdot Vref^2 \cdot f_s + N_C \cdot f_s \cdot (2C_{OX} \cdot W_{avg} \cdot L_{avg}) \cdot V_{DD}^2$$

$$+N_{S} \cdot f_{s} \cdot \left[ \frac{L_{\min}^{2}}{\mu_{n} \cdot R_{CMOS} \cdot \left(V_{DD} - V_{tn} - \left|V_{tp}\right|\right)} \right] \cdot V_{DD}^{2}$$

$$(4.49)$$

We used the second-order single-bit sigma-delta modulator of the Chapter 5 to verify the power consumption model. The total power consumption of the circuit is 16.96mW. The power consumption of the OTA is 7.95mW. So we know that the  $P_Q + P_{clock} + P_{switch}$  of the circuit is 1.06mW and the  $P_{an}$  of the circuit is 15.9mW.

The power consumption  $P_{an}$  of our power consumption model is 12.2mW and the power consumption  $P_{Q} + P_{clock} + P_{switch}$  of our power consumption model is 1.11mW. So we know that the power consumption of our power consumption model is 13.31mW.

The accuracy of our power consumption model is about 78.5%. So we have 21.5% inaccuracy for the power consumption model because the power consumption of the gain-boosting technique and bias circuit for OTA is not consider in our power consumption model.

Now we know that the gain-boosting technique for OTA can increase 25% power consumption of the OTA by Hspice simulation. So we can get the power consumption of the OTA is  $6.1 \times 1.25 = 7.625 mW$ . The total power consumption of our power consumption model is 16.36 mW. The accuracy of our power consumption model is about 96.5%.

## Chapter 5

# Circuit Implementation for Second-order One-bit Sigma-Delta Modulators

This chapter describes the detail circuit design for Second-order sigma-delta modulators.

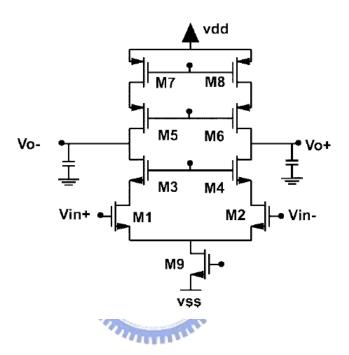

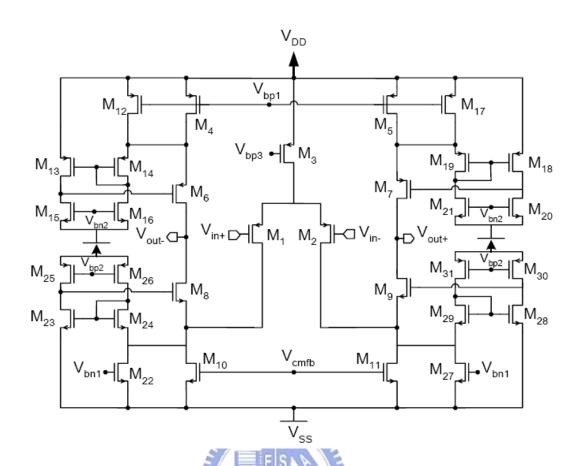

These circuit components include switched-capacitor integrators, operational transconductance amplifiers, bias network, comparators, quantizers, and digital networks.

Fully differential architectures are usually used in the analog circuits for the following reasons. First, a fully differential topology provides for high rejection of common-mode disturbance such as supply and substrate noise. It has the additional advantage that that if each single-ended signal is distorted symmetrically around the common-mode voltage, the differential signal will have only odd-order distortion terms. Second, a fully differential signal has twice amplitude as single-ended signal. Thus there is a net increase in dynamic range of 3dB for fully differential circuits.

### 5.1 Switched-Capacitor Integrator Design

Sigma-delta Modulators can be implemented by using either the discrete-time architectures, e.g. switched-capacitor (SC) and switched-current (SI) circuits, or continuous-time architectures, e.g. active-RC and transconductance-C (Gm-C) circuits. In general, most integrated circuits (IC) of sigma-delta A/D converters are implemented using SC circuits, because of easily simulation and compatible with VLSI CMOS process. Additionally, SC circuits provide better immunity to clock jitter than continuous-time circuits

and more preferable accuracy than SI circuits. Therefore, the SC circuit is a better choice for high-resolution applications. In our design, the integrator is implemented in a fully differential configuration. This improves the signal to thermal noise ratio  $SNR_{KT/C}$  by 3dB compared with the single-ended structure. If considering the same  $SNR_{KT/C}$ , the total values of sampling capacitors can be reduced by a factor of two and the capacitive load of the op-amp also can be decreased by reducing the sampling capacitance. This means the power dissipation of the amplifier is also reduced.

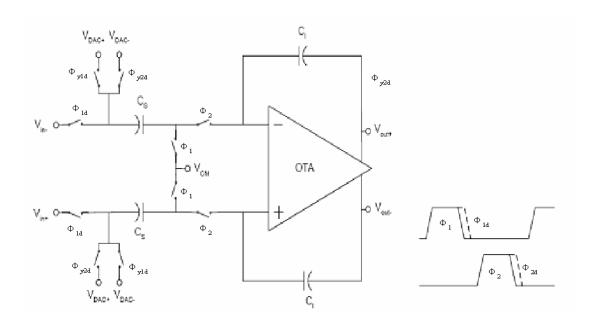

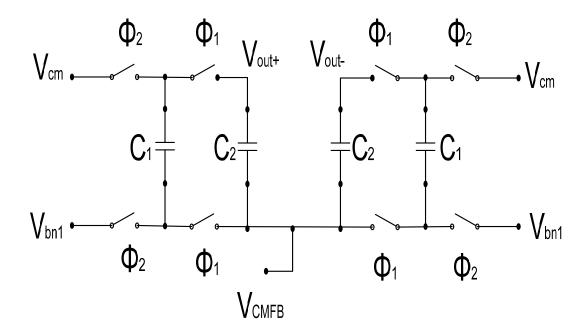

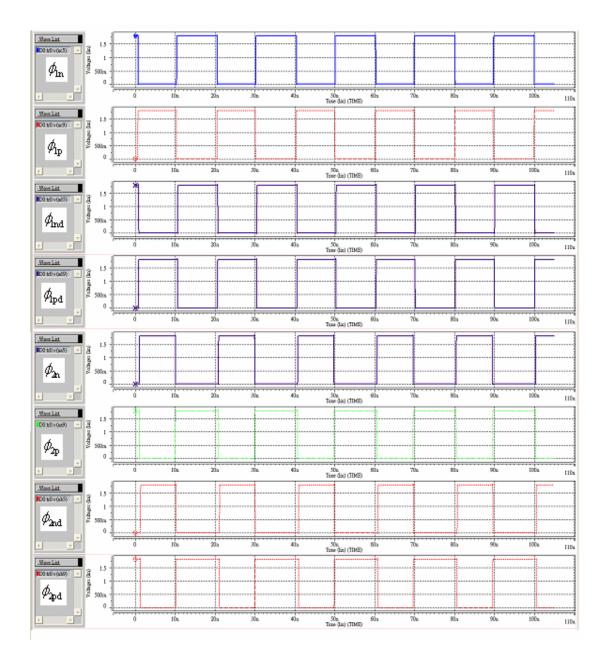

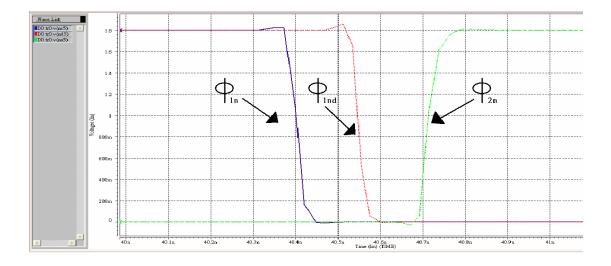

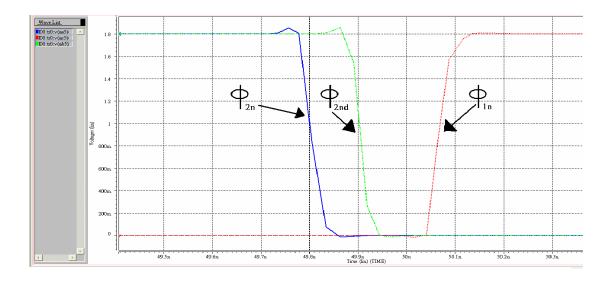

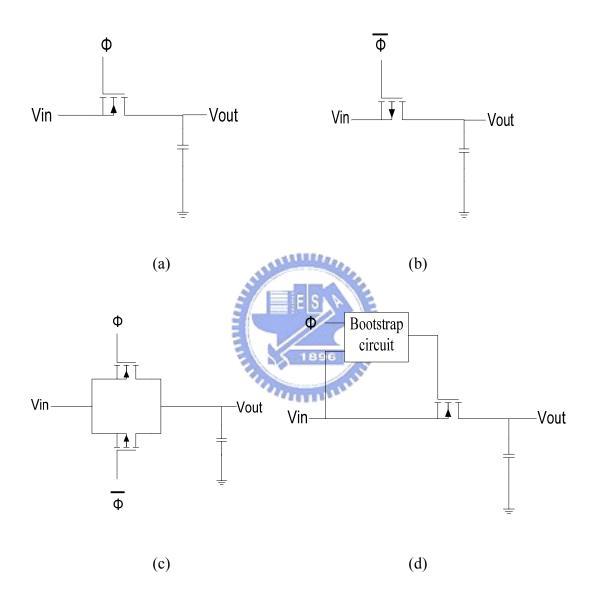

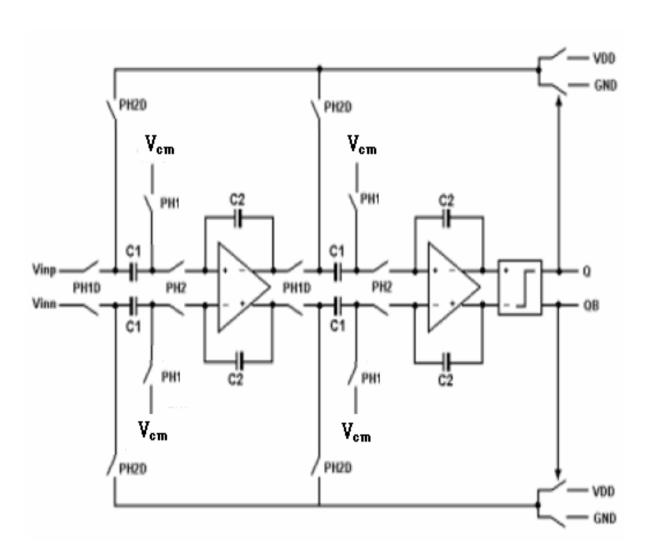

The timing phases used in the switched-capacitor integrator are two-phase non-overlapping clocks,  $\phi_1$  and  $\phi_2$ , and delayed clock phases,  $\phi_{1d}$  and  $\phi_{2d}$ . Fig. 5.1 shows the first integrator and timing diagram in the cascaded modulators. The input signal is sampled during phase 1 ( $\phi_1$  and  $\phi_{1d}$ ). During phase 2, the charge is transferred from sampling capacitor ( $C_s$ ) to the integrating capacitor ( $C_t$ ). At the same time, depending on the output value, the appropriate DAC reference voltage is applied to the sampling capacitor by the switches labeled  $\phi_{1,yd}$  and  $\phi_{2,yd}$ . The integrator employs the bottom-plate sampling technique to minimize the parasitic capacitance to the substrate [Fel 98]. The capacitors should be connected such that the bottom plate is driven either directly or through a switch by a voltage source or the output of the op-amp. This arrangement causes the parasitic capacitances to have the least effect on the operation of circuit, and the substrate noise coupling is also reduced by this arrangement.

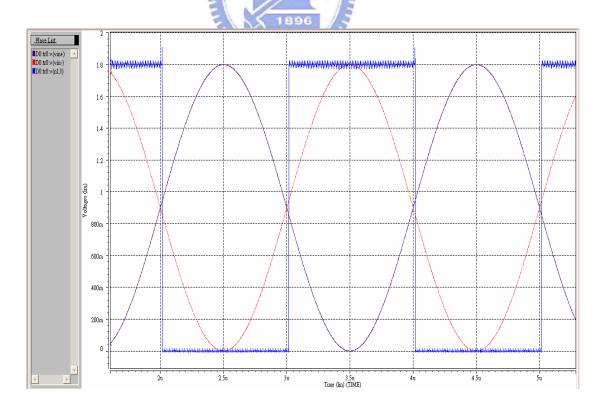

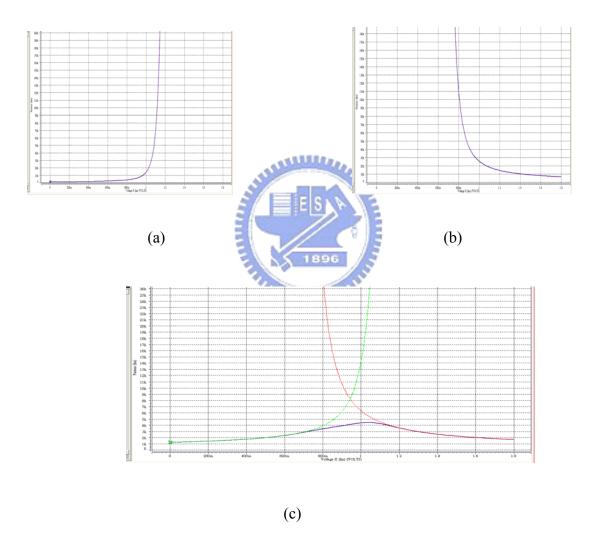

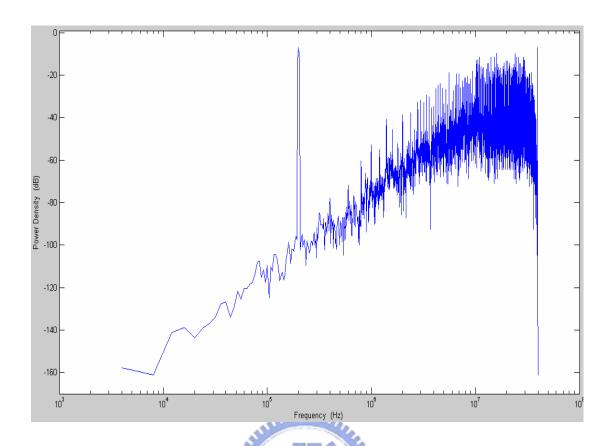

Fig. 5.1: Fully differential switched-capacitor integrator and timing diagram.