# 第一章

## 緒論

### 1.1 研究動機與目的

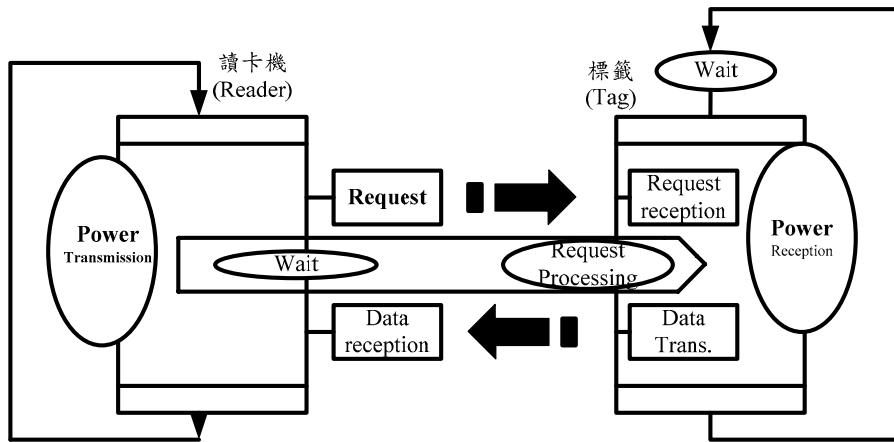

RFID(Radio Frequency Identification)是無線非接觸式具備辨識能力之元件，可藉由無線非接觸式讀取裝置核對儲存在元件內的辨識碼，最近幾年進行各種不同的廣泛應用[1-5]。在概念上和智慧卡、IC 卡近似，但儲存容量較大、外型尺寸也小很多，且具備無線通訊辨識能力。相較於條碼(Barcode)有著許多優點。下圖 1.1 為 RFID 系統圖，如圖 1.1 所示 RFID 系統主要包括了讀卡機(Reader or Interrogator)端與標籤端(Tag or Transponder)，而在被動式標籤中，能量(power)與指令(command)皆來自讀卡機所示，而在 RFID system 輕薄短小的優點下，近年 RFID 系統已廣泛應用在學界商界，因此也產生許多 RFID 在電路相關之研究，包括了

1. [6]中低耗功率 RFID 標籤研究。

2. [7][8]針對 RFID 標籤前端電路做 AC/DC 充電泵研究

3. [9][10]針對 RFID 低功耗整流電路研究

4. [11][12]針對 13.56MHz 作 RFID 標籤前端電路研究

5. [13]針對 RFID 標籤檢波器的研究

然而，基於以上 1~5 研究之下，本篇論文研究以在 RFID 系統在 UHF 頻段 915MHz(美國用)較少出現高整合功能性與低耗功率的標籤前端電路，所以本篇論文要針對 UHF 915MHz RFID 高整合功能性與低耗功率標籤前端電路做研究。

圖 1.1 RFID 系統圖

### ■ 1.1.1 RFID 系統與條碼系統比較

本節將其 RFID(Radio Frequency Identification)與條碼系統(Barcode)做以下的比較，並且列表示之

- 資料可更新:RFID Transponder 則可不限制次數的新增、修改、刪除儲存的資料。較條碼印刷後無法修改為佳。

- 方便資料辨讀:條碼需要近距離，使掃描光照在條碼上，transponder 只要在無線電波範圍內，即可傳遞訊號。

- 儲存資料的容量大:RFID Transponder 可達數 Megabytes，較二維條碼 2 至 3000 字元多。

- 可重複使用:RFID transponder 因本身資料更新，可重複使用

- 可同時讀取數個資料:條碼只侷限於一次讀取一個速度緩慢，而 RFID reader 可以同時辨讀多個 Transponder。

- 安全性:RFID transponder 可以利用後端資料加密或者 modulation 的方式以保證資料的安全性。

將 RFID(Radio frequency identification)與條碼系統(Barcode system)比較優缺點整理成下

表 1.1[1]

表 1.1 射頻辨識系統與條碼辨識系統比較

|                                      | RFID | 條碼 |                                                | RFID | 條碼 |

|--------------------------------------|------|----|------------------------------------------------|------|----|

| 非接觸式讀取                               | V    |    | 被動式<br><i>transponder</i>                      | V    | V  |

| 資料數位化                                | V    | V  | <i>Transponder</i><br>體積小                      | V    | V  |

| 資料具加密，<br>保密功能                       | V    |    | 抗污性、<br>耐候性                                    | V    |    |

| 讀取快速                                 | V    |    | 可整合設計<br><i>GPS、IC card</i><br>及 <i>sensor</i> | V    |    |

| 沒有固定度、<br>方向之要求                      | V    |    | 儲存大容量<br>資料                                    | V    |    |

| 可同時讀取多個<br><i>Transponder</i> 目<br>標 | V    |    |                                                |      |    |

| 價格                                   |      | V  |                                                |      |    |

### ■ 1.1.2 RFID 系統國內外發展現況

RFID 具有物品獨一辨識性、即時資訊傳遞性及可讀寫資訊等功能，使得 RFID 可應用於食衣住行育樂等各種生活面，創造社會大眾均能享受一種無所不在既快速又安全的優質生活，從世界的角度著眼[2]，RFID 技術已在零售業掀起一股風潮，全球前

十大零售業者包括 Wal-Mart、Carrefour、Home Depot、METRO、TESCO、Kroger、Costco 等九家業者都計畫以 RFID 技術建構更便利的消費環境，或將 RFID 導入物流中心以提升管理效率。從歐美日對於 RFID 技術應用的情況，不難發現 RFID 技術對於零售業的服務模式將帶來革命性的改變，背後商機更是無限，應用實例可見附錄 A.1。而將亞太國家發展應用比較整理如下表 1.2[4]

表 1.2 亞太鄰近國家發展與應用比較[4]

| 中國                                                                                                                                                                                                                                                    | 日本                                                                                                                                                                                                                                                                                   | 韓國                                                                                                                                                                                                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul style="list-style-type: none"> <li>■ 草擬跨部會整合”RFID 白皮書” 2005~2008 年完成 9 億張 RFID 身分證換發</li> <li>■ 學生電子購票專案 1000 萬張</li> <li>■ 壓力氣瓶導入 RFID 測試計劃</li> <li>■ 各類證照每年簽發 5000 萬件以上</li> <li>■ 上海強制性植入寵物晶片 9 萬個電子標籤</li> <li>■ 南京大學生運動會將使用 RFID</li> </ul> | <ul style="list-style-type: none"> <li>■ u-Japan 政策，目標逾 2010 年成為全球 ICT 最先進國家</li> <li>■ Hibiki(Low cost)兩年計畫投入 18 億日圓</li> <li>■ 2003 年推動家電/服飾/CD/建設機械/醫藥/物流</li> <li>■ 2004 年 20 億日圓推動家電/書籍/服飾/CD/建設機械/醫藥/物流</li> <li>■ 2005 投入 31 億組織 Airport/服飾/食品等應用聯盟或 working group</li> </ul> | <ul style="list-style-type: none"> <li>■ u-korea 政策 + IT839 先導計畫，目標為建立 RFID Based 服務產業</li> <li>■ RFID 研發實地測試經費投入：2004:美金七百萬 2005:美金 2100 萬 2005 選擇 433MHz 標準+移動式 RFID 為發展應用重點，應用領域包括武器、進口牛肉、航空行李、海運貨櫃等。</li> <li>■ 2007 年完成諸如 RFID 晶片等核心技術發展</li> </ul> |

台灣是全球重要的高科技產業製造中心，必須不斷應用創新科技，應積極發展 RFID 技術，以保持位居全球供應鏈的競爭優勢，而現今國內已投入或將投入 RFID 的上市櫃個股目前不多，除宏碁已投入 RFID 網絡系統的建置，國內最大的紙箱供應商永豐餘將是最大的 RFID power user，精技、欣技、台揚則是硬體面的廠商，伍豐、飛捷、振樺的 POS 也都會整合 RFID 介面，還有 Benq 已開發出國內第一款 NFC 手機。此外最近幾年國內應用 RFID 的計畫如附錄 A.2。

基於以上資料所顯示RFID效應已在全世界發酵，在業界學術領域都有許多案例可

循，所以本篇論文著重於發展RFID系統中的RFID標籤端作為本篇論文的研究重點。

### ■ 1.1.3 RFID 系統使用頻率

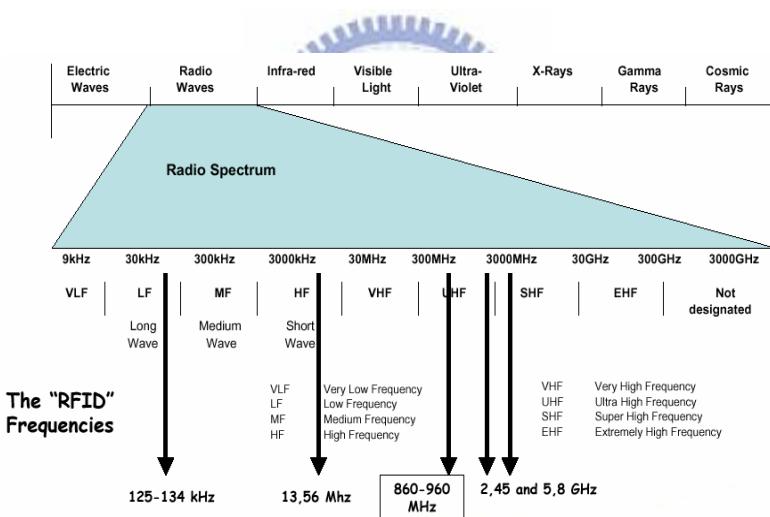

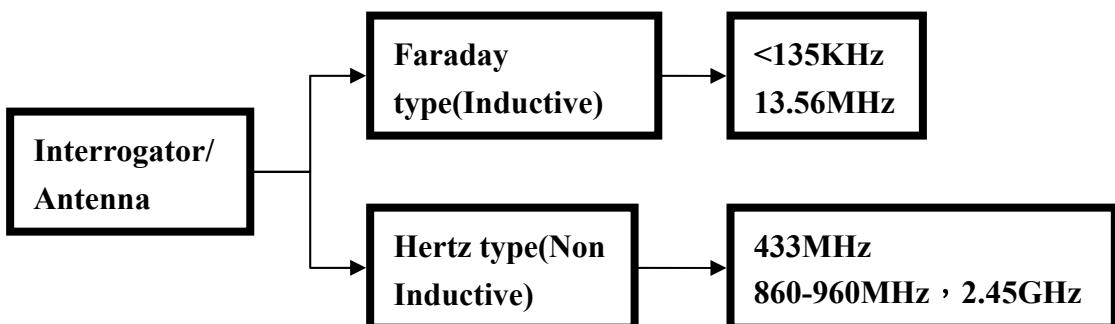

基於表 1.1 以上之優點，於是我們將 RFID 列為我們研究的重點。圖 1.2 列出目前 RFID 使用的頻率。本篇論文 RFID 標籤是設計工作在 UHF 的美國所使用的主流頻段 (915Mhz)。由圖 1.2 RFID 使用頻段我們可以將其利用頻率以及感應範圍將其所對應應用範圍簡單分類如下表 1.4[1]。對本篇論文所使用的美國頻段 915MHz 而言，RFID 系統必須符合 FCC Part 15[19]所制定出來的規範，主要是對於低功率的電磁場與電磁干擾做出規範，表 1.3 列出 FCC Part 15 對 RFID 系統在不同的頻段所限制的最大磁場強度

圖 1.2 RFID 使用頻段[1]

表 1.3 FCC Part 15 對 RFID 其頻率範圍相對應於磁場強度的規範[14]

| Frequency range/MHz | Maximum E-field | Measuring distance | Section |

|---------------------|-----------------|--------------------|---------|

| 1. 705~10. 000      | 100uV/m         | 30m                | 15. 223 |

| 13. 553~13. 567     | 10mV/m          | 30m                | 15. 225 |

|               |         |     |        |

|---------------|---------|-----|--------|

| 26.960~27.280 | 10mV/m  | 30m | 15.227 |

| 40.660~40.700 | 1mV/m   | 3m  | 15.229 |

| 49.820~49.900 | 10mV/m  | 3m  | 15.235 |

| 902.0~928.0   | 50mV/m  | 3m  | 15.249 |

| 2435~2465     | 50mV/m  | 3m  | 15.249 |

| 5785~5815     | 50mV/m  | 3m  | 15.249 |

| 24075~24175   | 250mV/m | 3m  | 15.249 |

表 1.4 依頻段區分的 RFID 應用範圍

| 頻率範圍             | 應用範圍                                                      |

|------------------|-----------------------------------------------------------|

| <b>LF</b>        | 通常使用在特殊用途:動物晶片                                            |

| <b>HF</b>        | 使用較為頻繁以及成熟。例:5cm 的 ISO14443 悠遊卡以及 1-1.5m 的 ISO15693 的巡檢系統 |

| <b>UHF</b>       | 長距離 3-30m 例:EPC Gen2 Standard                             |

| <b>Microwave</b> | 偵測距離最長通常用在軍事等特殊用途                                         |

可以從上表 1.4 看出低頻的應用範圍受限於頻率較低所以應用範圍也局限於近距離的應用，而在 UHF(ultra high frequency)就可利用其較大的感應距離，所有的應用範圍也比較廣泛，所以基於此理由，本篇論文也是將 RFID 標籤設計在 UHF 的頻段(915MHz)。

表 1.5[3]為依應用範圍所定義的 ISO 與 IEC 的標準，所以依據其標準 ISO18000-6 Air Interface 去設計本篇論文的 915MHz RFID 標籤的前端電路。

表 1.5 標準與應用

| RFID standard                          |                   |                                 |                           |

|----------------------------------------|-------------------|---------------------------------|---------------------------|

| Application                            | Number of STD     | Name                            | Deliberation Organization |

| <i>For Animal</i>                      | ISO11784          | Code Structure                  | ISO TC23 /SC19/WG3        |

|                                        | ISO11785          | Technical Concept               |                           |

|                                        | ISO14223          | Expand code & Encoding          |                           |

| <i>For Marine Container</i>            | ISO10374          | 915 Mhz & 2.45GHz System        | ISO TC104/SC4/WG2         |

|                                        | ISO18185          | Electronic seals for security   |                           |

| <i>For Management of things</i>        | ISO/IEC 18000-1   | General Parameter               | ISO JTC1/SC31/WG4         |

|                                        | ISO/IEC 18000-2~7 | Air Interface                   |                           |

|                                        | ISO/IEC 15961     | Application Command             |                           |

|                                        | ISO/IEC 15962     | Encoding Rule, Logical Memory   |                           |

|                                        | ISO/IEC 15963     | Unique ID                       |                           |

|                                        | TR 18001          | Application Requirements        |                           |

|                                        | TR 18046          | Performance Test Method         | ISO/IEC JTC1/SC31/WG3     |

|                                        | TR 18047          | Conformance Test Method         |                           |

| <i>Identification Proximity “card”</i> | ISO/IEC 14443-1   | Physical Characteristics        | ISO/IEC JTC1/SC17         |

|                                        | ISO/IEC 14443-2   | Radio Frequency & power         |                           |

|                                        | ISO/IEC 14443-3   | Initialization & Anti-collision |                           |

|                                        | ISO/IEC 14443-4   | Transmission Proto cal          |                           |

| <i>Identification Vicinity “card”</i>  | ISO/IEC 15693-1   | Physical Characteristics        | ISO/IEC JTC1/SC17         |

|                                        | ISO/IEC 15693-2   | Air Interface & Initialization  |                           |

|                                        | ISO/IEC 15693-3   | Anti-Collision & Protocol       |                           |

| <i>Near Field Communication</i>        | ISO/IEC 18092     | Interface & Protocol            | ISO/IEC JTC1/SC6          |

表 1.6[4]為由 EPC global 所定義之 RFID 標籤依其功能性分成五個 class，而 class 4 以及 class 5 雖功能較強但需要外掛電池，卻失去了原本 RFID 輕薄短小的優點，所以本篇論文所設計標籤是相容於 EPC class 2，class 3 的前端電路為設計目標。

表 1.6 EPC CLASS 標準與應用

| <i>EPC class</i><br>[SRI Consulting Business Intelligence<br>(SRIC-BI)] | <i>feature</i>                                                                 |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| <i>Class 0/1</i>                                                        | read only 被動式辨別標籤                                                              |

| <i>Class 2</i>                                                          | 被動式標籤可能具備基本功能例如<br>memory 或者加密                                                 |

| <i>Class 3</i>                                                          | 是半被動 RFID tags 可能支援長距離通訊                                                       |

| <i>Class 4</i>                                                          | 主動式標籤相容於寬頻且點對點通訊<br>並且能與其他同頻的主動式標籤或者<br>讀取器溝通                                  |

| <i>Class 5</i>                                                          | 主要定義 reader 必須具有提供其他<br>class1/2/3 Tag power 的能力並且同時都可<br>以相容與其他 class0~4 都能通訊 |

## 1.2 架構探討與選擇

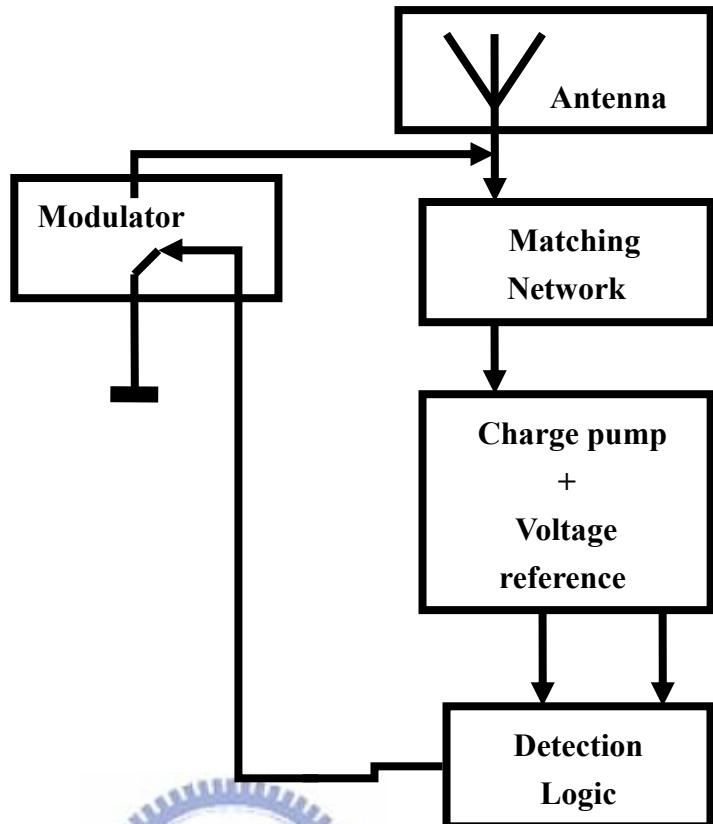

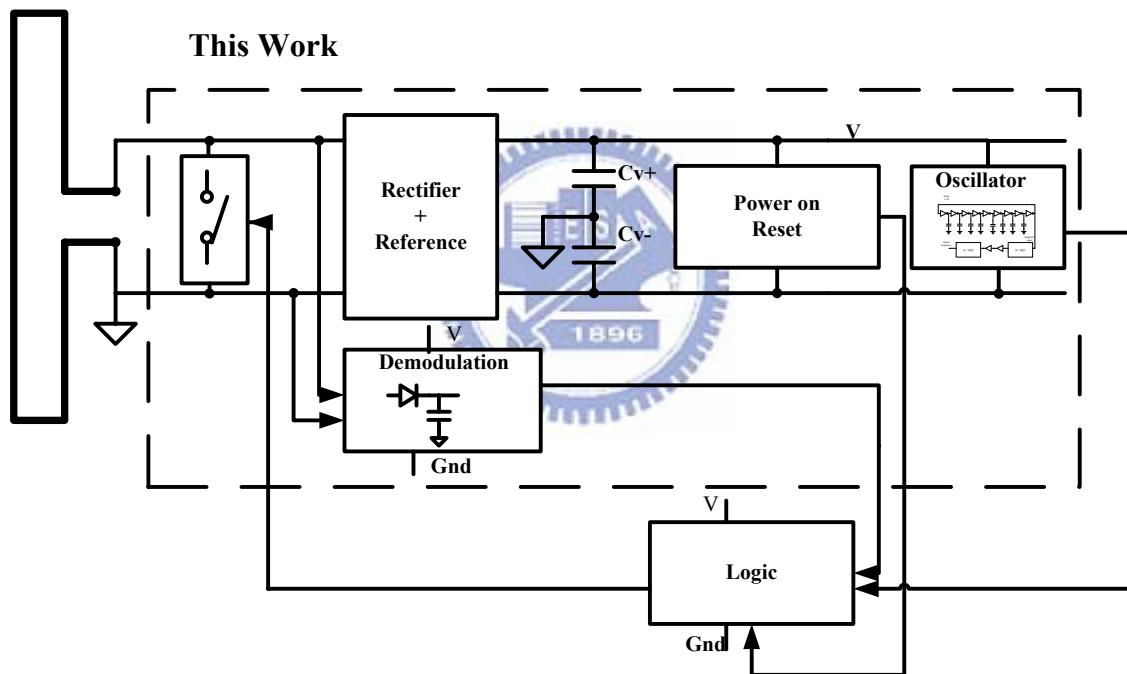

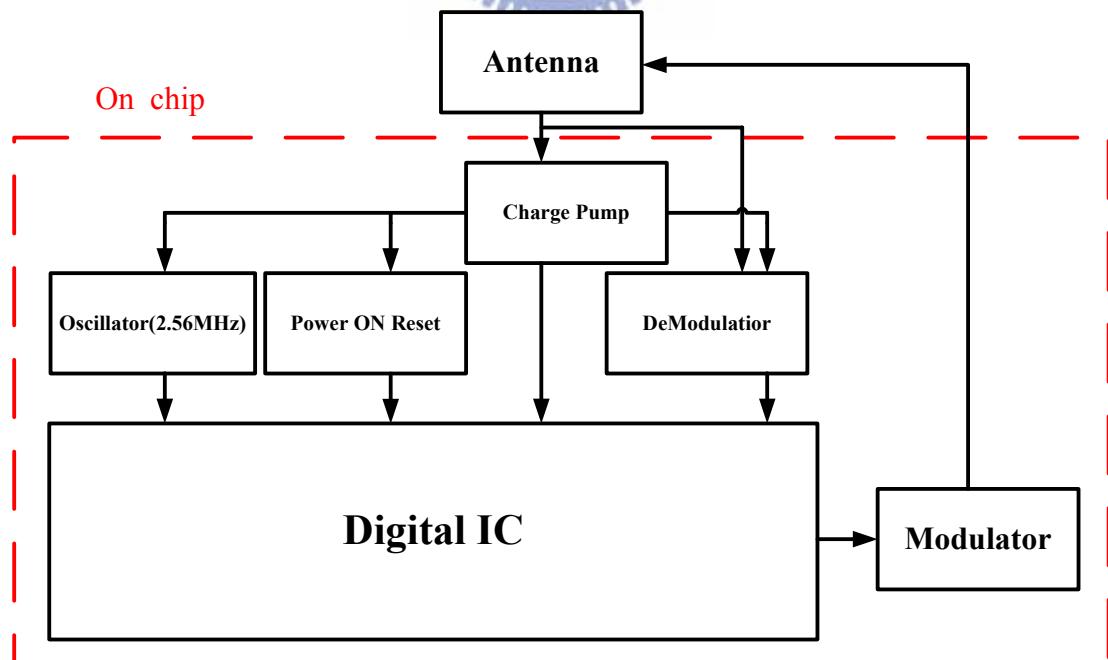

經由 1.1 所討論目前主要應用成熟階段 LF 和 HF 的頻段，所以目前我們著重的研究頻段是下一個較長距離應用的 UHF(Ultra High Frequency)，藉由較高的頻段提升我們的傳輸距離。此篇論文 RFID 標籤的設計目標也是架構在此頻段上，透過射頻前端電路以及基頻的數位訊號處理以實現更高的傳輸距離以及更高的標籤的辨識率。基本的 RFID 標籤方塊圖如下圖 1.2 所示，主要分為天線端(Antenna)以及匹配電路(Matching network)、充電泵(Charge pump)和穩壓電路(voltage reference)，偵測電路(Detector)和數位邏輯(logic)的部份，以及調變電路(Modulator)。

圖 1.3 標籤(transponder)方塊圖

由於市場成熟度而言，基本上國內大部分國產標籤 IC 為 13.56MHz，但相較於 UHF 而言因 13.56MHz 頻率較低便有感應距離不夠的限制因其感應原理也是有相當的差距，以下圖 1.4 表示其工作頻率與其能量產生方式。

圖 1.4 能量感應方式

國內大部分應用於 LF 和 HF 是利用電磁偶合(coupling)的方式獲取能量，所以我們著重較具傳輸優勢的 UHF 的頻段 915MHz 也配合國內交通部傾向的頻段範圍區間內 (~928MHz)。而在國內 RFID 標籤 IC 化過程中顯少見到使用 UHF 頻段的 IC 出現，而在高頻率頻段能量效率的轉換也是影響感應距離的重要因素，如能提高能量轉換效率，便能延長感應距離。同時也缺少具有高頻完整功能的前端電路實現的 RFID 標籤 IC 出現，所以此篇論文便著重於提高能量轉換效率(power conversion efficiency)以提供後端數位訊號處理有足夠能量工作以及完整的前端電路功能以提高辨識率與讀取率。其前端電路方塊圖如圖 1.5 所示。

圖 1.5 RFID 標籤前端電路方塊圖

國內現階段研究分析發現，極少 UHF RFID 標籤 IC 全部整合前端電路功能於 915MHz 的頻段的 RFID 標籤 IC，就如圖 1.5 方塊圖所示，此篇文章著重於 RF 轉成 DC 的充電泵(charge pump)以及穩壓電路(voltage reference)以及振盪器電路(Oscillator)、解調變電路(Demodulation)，啟動重設電路(Power On reset)，調變電路(Modulator)的部份，整合於一顆 RFID 標籤前端電路 IC 內，能夠達到目標:1.透過高效率匹配電路提升能量轉

換效率(RF to DC)，提供後端數位電路有足夠的能量工作，以延長有效感應距離。2. 利用較佳的解調變與調變電路能讓標籤(Tag)與讀卡機(Reader)能夠清楚辨別訊號，進而降低錯誤率(Error rate)3. 提供較高的敏感性(sensitivity)以降低對應讀卡機設計複雜程度。

所以此篇論文將針對使用高感度、高辨識率以及長距離整合型超高頻 RFID 標籤 IC 來作詳細的分析及探討，試圖找到一個較佳且有效的方式來解決其感應範圍不大以及低辨識率與高錯誤率的問題，由於國內晶圓代工業者於互補式金氧半(CMOS)製程環境的提供相當完善，所以此篇論文以研發相容於 CMOS 製程為主要方向。

## 1.3 電路規格制訂

本節內容主要模擬並訂定 RFID 標籤前端電路中所需各電路之規格方式與架構，使此篇論文所提出的 UHF RFID 標籤 IC 符合 UHF ISO18000-6 RFID 標籤前端電路之規定，以及提供後端數位訊號處理電路規格考量包括：載波頻率(Frequency of carrier)、能量轉換效率(Power Conversion Efficiency)、RF 輸入能量工作區間(range of RF input power)、工作電壓位準(Voltage Level)、振盪器頻率(Oscillator Frequency)、重載驅動能力(Heavy Load Driving)、解調變方式(Demodulation Voltage Level)、調變方式(Modulation)、上升時間(Rising time)、下降時間(Falling Time)、及消耗功率大小(Power)。

### 1.3.1 系統規格

首先在載波頻率的選擇上(frequency of carrier)在 1.2 節中提過，頻率小於 135KHz 易受發光設備所干擾，而 13.56MHz 目前應用最普遍，但由於其感應距離太短而限制其應用範圍，而在 2.45GHz 的頻段與水共振頻率相同也容易被水所吸收，所以此篇論文將載波頻率設計在 915MHz，同時也避免了 WIFI 無線網路以及微波以及藍芽大眾應用的頻段。但 RFID 在 RF 方面仍有許多限制，例如 Radio wave 易被金屬擋住以及包括標籤

位置重疊以及標籤天線位置方向都會影響其辨識度，這些地方可以利用讀卡機與標籤間的溝通機制，能有效加以改善其辨識度，例如 coding method[3]有(MILLER, EXTENDED MILLER, FM0, NRZ, MACHESTER, DBF, 以及 MFM 等)，而在 Access Method[3] 有(READ ONLY, WRITE ONCE READ MANY, READ WRITE 等)可以在數位訊號處理利用這些溝通方式提高辨識度，由於此篇論文主要專注於標籤前端電路，不在此詳述，但在前端電路也可以利用一些改善方式，由於 UHF 被動標籤前端電路主要是利用 Backscattering 的方式在連續發射的連續波，透過標籤將標籤資料(data)載在載波上面，當射頻波回傳到讀卡機端便可解調變回來將標籤所有的資料解調回來，所以在 RFID 標籤電路上在調變方式便有許多選擇的方式 例如 OOK, ASK, FSK, PSK, FHSS 等方式雖然 FHSS 和 FSK 以及 PSK 可能較 ASK 對其他頻率 interference 有較佳的抵抗力，但可能必須在標籤前端電路加上 subcarrier，造成可能多餘的能量損耗，對被動式標籤而言，是較為不利的，所以此篇論文利用 OOK(On off Keying)也就是 100% ASK 為 Modulator 電路，當 Backscattering 時控制天線輸入兩端的短路(Short)或是開路(Open)造成  $\Gamma$  值的不同，造成阻抗不同，當讀卡機接收到訊號時便可分辨出標籤資料是 0 或者是 1。

### 1.3.2 子電路架構

經由 1.3.1 訂定系統規格後，再細部訂定內部電路規格，就依照 1.2 圖 1.5 RFID 標籤前端電路一共分成整流電路( Rectifier )，限流電路( Limiter )，穩壓電路( Voltage Reference circuit )，電源啟動重置電路 ( Power On Reset circuit )，振盪電路 ( Oscillator circuit )，調變電路 ( Modulator )，解調變電路 ( Demodulator circuit )。將整個 RFID 標籤前端電路設計目的與架構的使用整理表列成如下表 1.7

表 1.7 子電路架構

| Part                     | structure          | feature               |

|--------------------------|--------------------|-----------------------|

| <b>Rectifier</b>         | Voltage multiplier | 倍數高短上升時間<br>長下降時間     |

| <b>Limiter</b>           | Serial diodes      | 提高限流避免晶片燒毀            |

| <b>Voltage reference</b> | Cascade and op Amp | 提供約 850mV 穩壓<br>高驅動能力 |

| <b>Power On Reset</b>    | Digital circuit    | 短 Reset 數位電路時間        |

| <b>Demodulator</b>       | Envelop detector   | 將資料正確解調               |

| <b>Oscillator</b>        | Ring Oscillator    | 提供數位電路<br>2.56MHz 振盪源 |

| <b>Modulator</b>         | Switch             | 利用 OOK 方式<br>提高阻抗改變量  |

基於以上表 1.7 RFID 標籤前端子電路基本架構下，本篇論文目標規格架構依照以上表 1.7 所示另外目標也以能做到小面積、低耗功率，高轉換能量效率、以及高功能性整合度前端電路晶片為目標，將在之後章節分述之。

## 1.4 論文組織架構

本論文重點將放在超高頻 RFID 標籤前端電路的製作，並以 TSMC 0.18μm 1P6M RF CMOS 製程實現，各章摘要如下：

第二章 RFID 標籤前端電路系統架構設計與模擬，將先分別探討整流電路 (Rectifier)，限流電路 (Limiter)，穩壓電路 (Voltage reference circuit)，電源啟動重置電路 (Power On reset circuit)，振盪電路 (Oscillator circuit)，調變電路 (Modulator)，解調變電路 (Demodulator circuit) 各子電路架構設計原理與工作方式以及設計目標，接著為整流電路，限流電路，穩壓電路，電源啟動重置電路，振盪電路，調變電路，解調變電路各子電路的合成設計與模擬，並研究子電路模擬結果討論。

第三章為 RFID 標籤前端電路量測結果與討論，先將 T18-95E 所下線的 915MHz RFID 標籤前端充電泵電路做模擬與量測的比較，其中包含整流電路（Rectifier）和限流電路（limiter）以及穩壓源（Voltage Reference）電路的量測結果。最後將其 915MHz UHF RFID 標籤前端電路合成做標籤前端電路（T18-96B）做系統模擬。

第四章為本篇論文做總結與將來發展。

## 第二章

# 915MHz UHF RFID 標籤前端電路架構與模擬

### 2.1 架構介紹

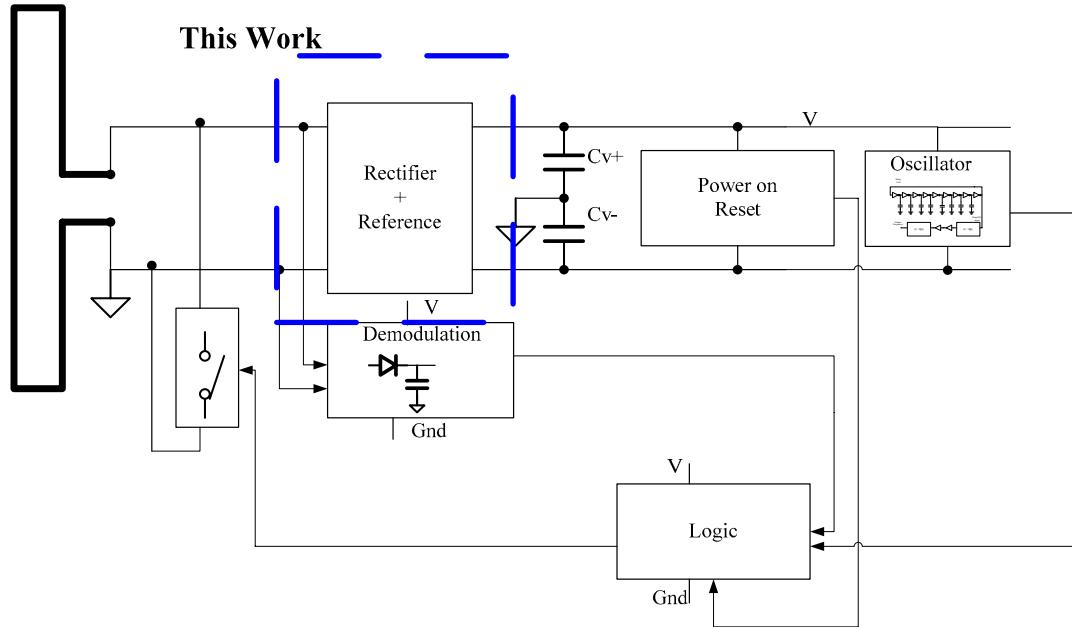

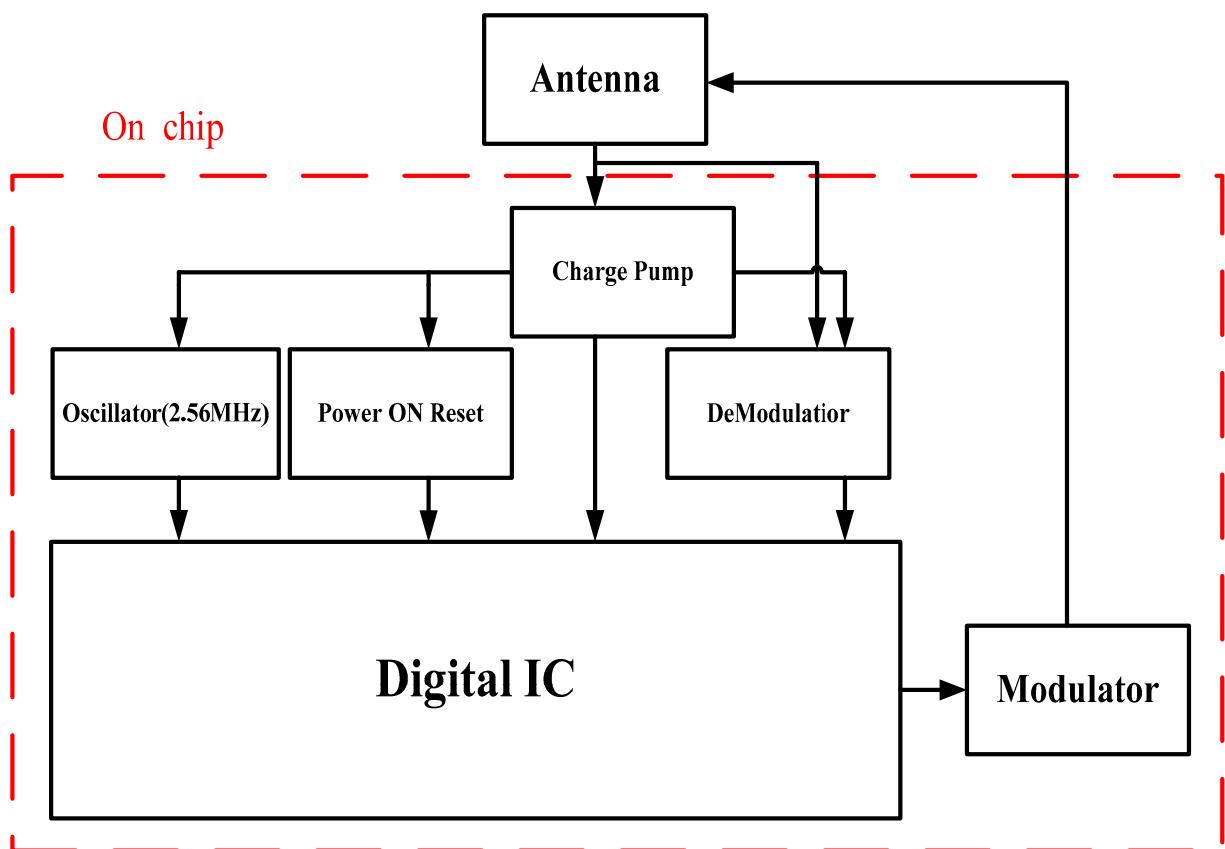

此篇論文乃著墨於 RFID 標籤前端電路類比的部份，所以此篇論文下線主要分成四塊包括了充電泵(charge pump)充電泵主要包括了整流電路與限流電路(rectifier 和 limiter)以及 穩壓(Voltage reference)電路、提供後端數位處理的啟動重置(Power On Reset)電路，解調變電路(Demodulator)以及環形震盪(Ring Oscillator)，以及調變電路(Modulator)而使用 On off keying 的調變方式，而數位邏輯訊號處理部分整合在一起的 RFID 標籤系統關係圖如下圖 2.1 所示。

圖 2.1 RFID 標籤系統圖

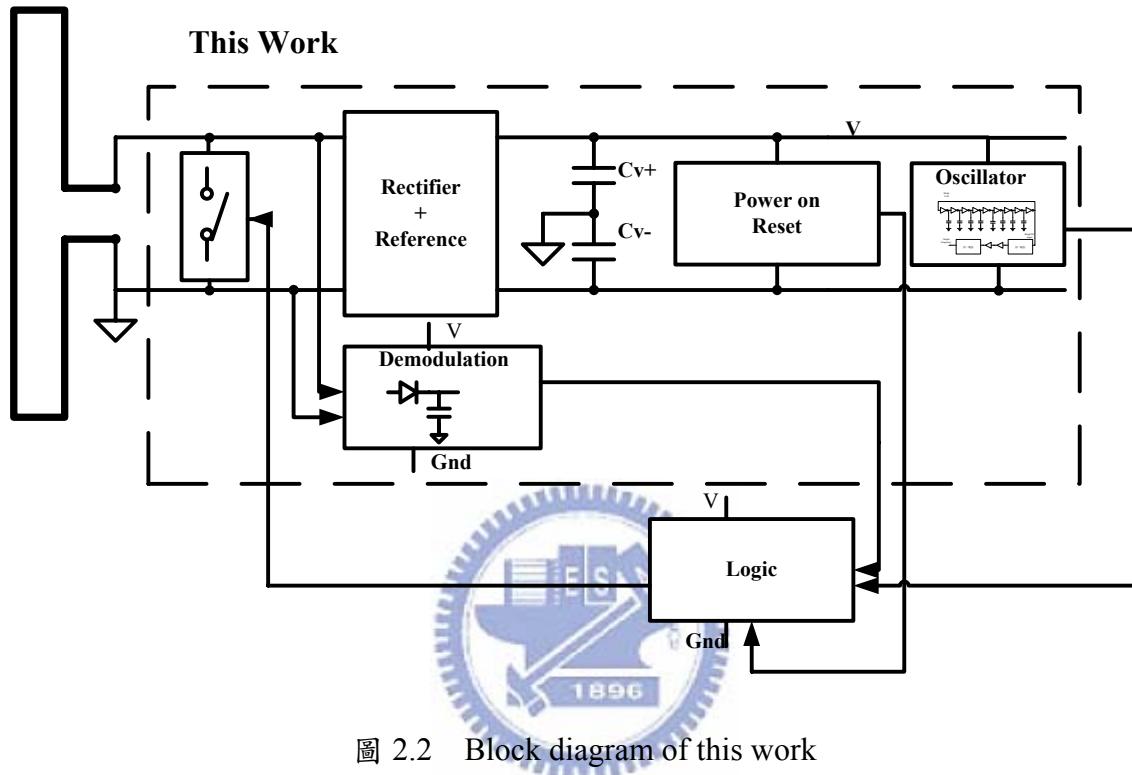

而此篇論文下線的晶片架構如下圖 2.2 基本上是以圖 2.1 的架構為主而不包括數位訊號處理邏輯的部份，主要是以 RFID 標籤前端類比電路為主。而此篇論文電路架構圖如下圖 2.2。

圖 2.2 Block diagram of this work

### 2.1.1 充電泵電路(Charge pump)

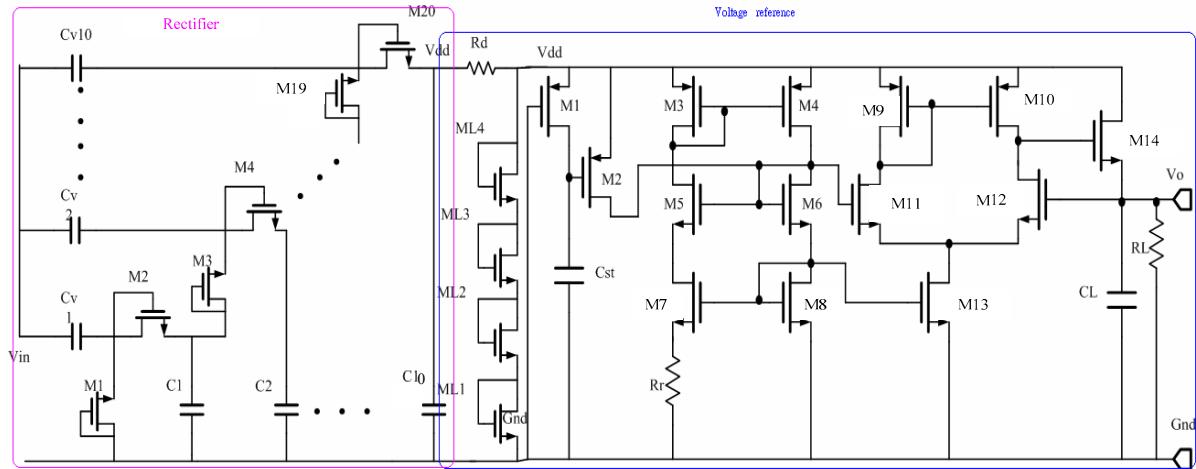

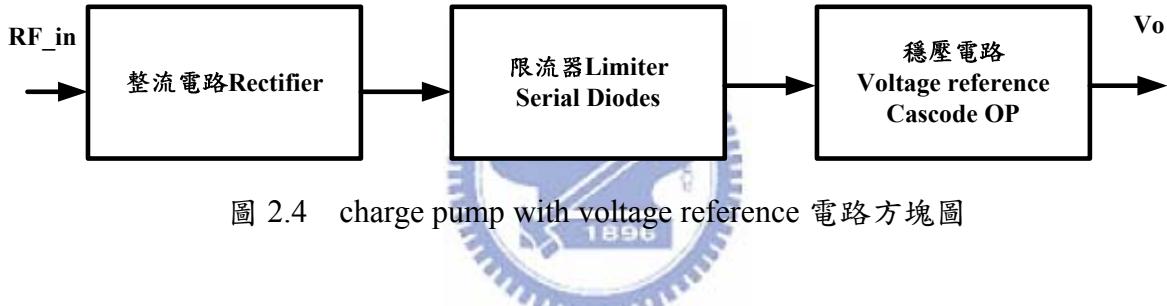

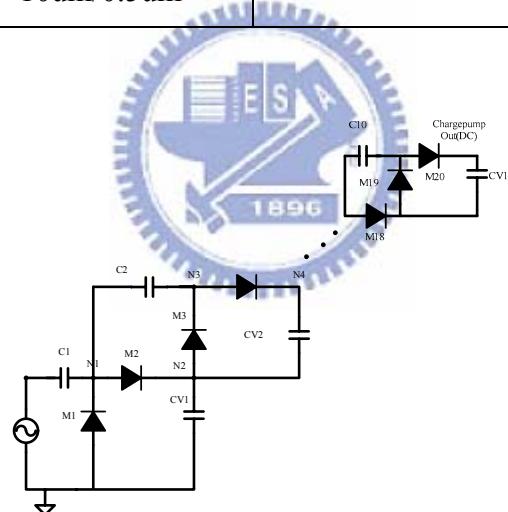

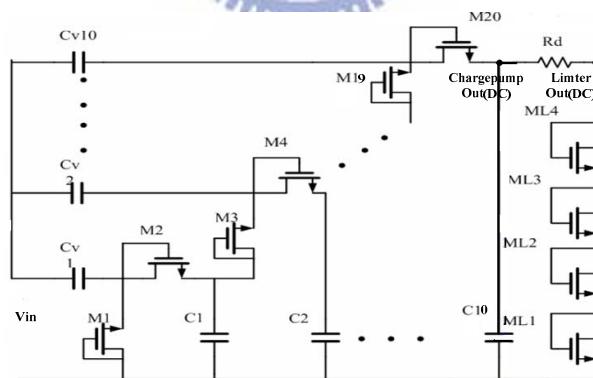

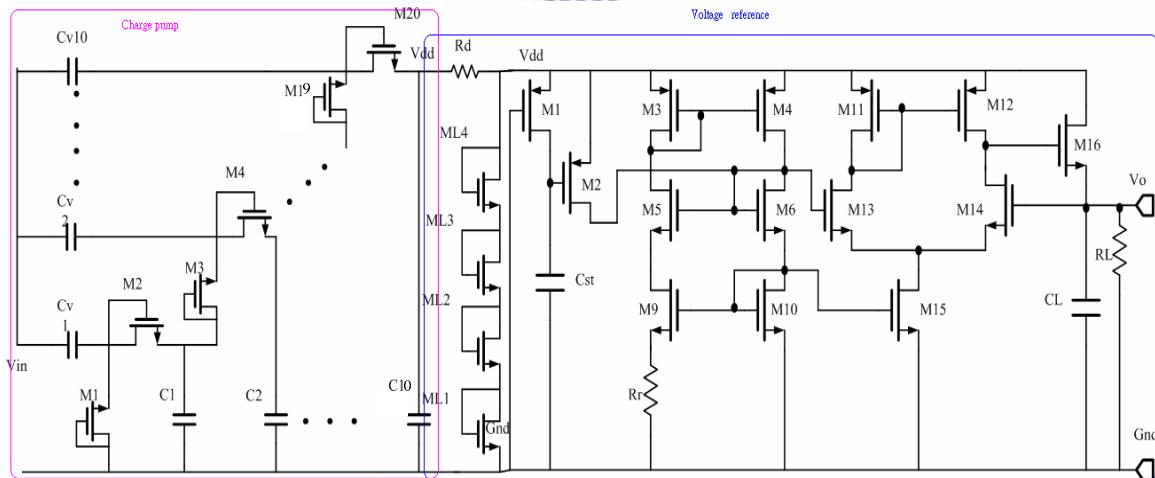

根據其輸入源的不同共可分為 AC/DC 充電泵以及 DC/DC 充電泵[7]，由於其較佳的能量轉換效率(Power conversion Efficiency)以及簡單的架構被廣泛的使用在 RFID 以及 EEPROM 或者 flash memory[6]，而本篇論文主要組成充電泵(charge pump)電路如下圖 2.3 所示包括 RF 轉成 DC 的整流電路(Rectifier)以及限流電路(Limiter)穩壓電路(Voltage reference) 所提供後端解調電路(Demodulator)穩定偏電壓(Bias Voltage)用的  $V_o$  可由下圖 2.3 可知電路主要分成充電泵電路(charge pump)和穩壓電路(voltage reference)兩個部份。

圖 2.3 charge pump with voltage reference

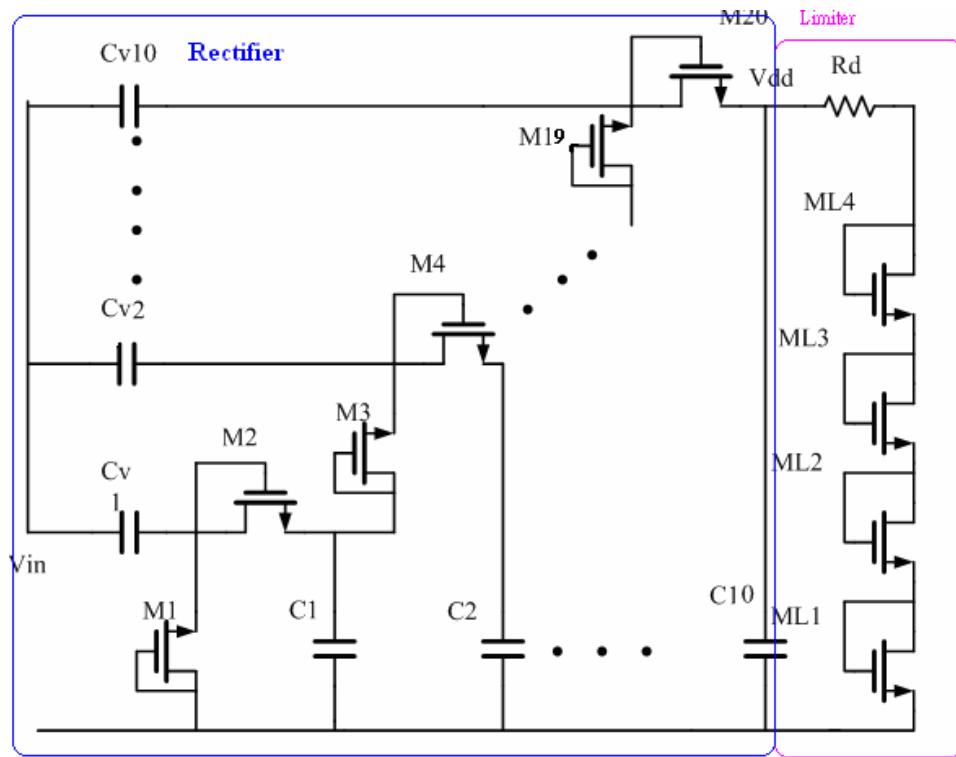

此篇論文設計的充電泵電路(Charge pump)如上圖 2.3 與圖 2.4 所示主要包括兩個部分第一部分 Native-NMOS 充電泵和限流器，由前級整流器將 915MHz RF 訊號轉成 DC，接著後級限流電路(limiter)以及穩壓電路(voltage reference)做限壓以及穩壓功能。以下子節將對充電泵電路內子電路分別做架構介紹。

#### A. 整流電路

傳統整流電路(conventional rectifier)一般而言有 bootstrapped 以及 voltage multiplier 的方式，bootstrapped 方式[10]：其優點為避免 Diode-connected MOS 的 Threshold voltage 的問題，但缺點為因切換時所造成的 Switch ripple 造成輸出 DC 直流偏壓的不穩 voltage multiplier[6][7][15]的方式：相較於 boot strapped 的方式，雖效率較差但有較小的 DC output ripple 而主要缺點為 Threshold voltage 的問題，雖可透過控制 bulk 電壓方式[16]可以降低

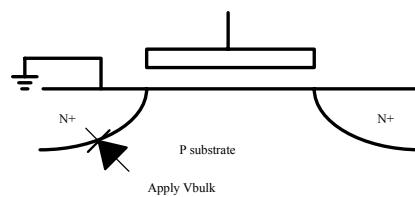

P substrate 和 N+ 間的 barrier 電壓以降低 Threshold voltage，然而，相對也會有 source 和 bulk 會有漏電電流，如圖 2.6 所示。對 RFID 被動式標籤在低耗功(low power)方面而言是極為不利，因此此篇文章採用 TSMC 1P6M 0.18um Process 中 native NMOS 因有較小的  $tox$  所以有較大的  $Cox$  從[17]可知 Body effect Eq.(1)，可以減緩因 body effect 所造成的 Threshold voltage 變大的問題，因此 native MOS 具有較低的 Threshold voltage，所以可以改善 voltage multiplier 在 Threshold voltage 問題，可以將 Threshold voltage 有效降至約 70mV，以提高 DC 輸出電壓效率。

圖 2.5 整流電路電路圖

圖 2.6 Bulk 加電壓 forward bias 圖

$$V_{th} = V_{th0} + r \left( \sqrt{|2\phi_F + V_{SB}|} - \sqrt{|2\phi_F|} \right) \quad (1)$$

Where the factor  $r = \frac{\sqrt{2q\epsilon_s N_{sub}}}{C_{ox}}$

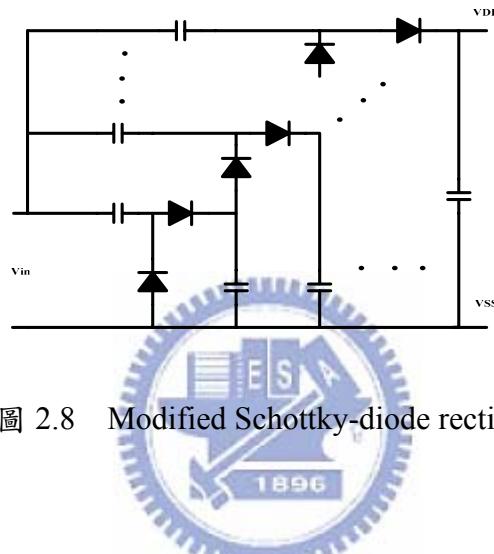

將其中整流電路主要是以[8]的 conventional ladder capacitor-diode charge pump 架構如同圖 2.7 所示，但其有輸出阻抗太大以及 dc 輸出 ripple 太大及倍壓倍率較小缺陷，經由[6][7][15]改良為基整流電路架構，架構如同圖 2.8 所示，比較其兩種圖 2.7 與圖 2.8 優缺點，如表 2.2 所示的十級比較中可以看出圖 2.8 Modified rectifier 雖有較佳的表現但限制於使用 Schottky Diode 會有與一般 CMOS 製程不相容，限制應用範圍，也有和其他電路合成的問題，所以此篇文章將其 Schottky Diodes 修改成如同圖 2.9 所示，以 low threshold voltage 的 native MOS diode 替代維持其與其他電路的整合性以及低 Threshold Voltage 特性。此處 MOS size 的設計根據 Eq.(2) 可知道當

$$V_d = V_{ds} = \sqrt{\frac{2I_{ds}}{\beta}} + V_{th} \quad (2)$$

Where the factor  $\beta = \mu_n C_{ox} W/L$

$$W \uparrow \Rightarrow \beta \uparrow \Rightarrow V_d \downarrow \text{ or } L \downarrow \Rightarrow \beta \uparrow \Rightarrow V_d \downarrow$$

利用此種方式透過提升 Width 或是減少 Length 以減少 MOS-diode 所消耗的跨壓，而 native MOS 所提供的 channel length 最小為 0.5um，所以此篇論文使用 MOS diode 其寬長比為  $W/L=10\text{um}/0.5\text{um}$ ，整理成下表 2.1 為整流電路中電容大小與 MOS diode 尺寸。

表 2.1 整流電路電容大小與 MOS diode 尺寸

| Device    | Size       | Device     | Size       |

|-----------|------------|------------|------------|

| <b>M1</b> | 10um/0.5um | <b>M15</b> | 10um/0.5um |

| <b>M2</b> | 10um/0.5um | <b>M16</b> | 10um/0.5um |

| <b>M3</b> | 10um/0.5um | <b>M17</b> | 10um/0.5um |

|            |            |                 |            |

|------------|------------|-----------------|------------|

| <b>M4</b>  | 10um/0.5um | <b>M18</b>      | 10um/0.5um |

| <b>M5</b>  | 10um/0.5um | <b>M19</b>      | 10um/0.5um |

| <b>M6</b>  | 10um/0.5um | <b>M20</b>      | 10um/0.5um |

| <b>M7</b>  | 10um/0.5um | <b>C1~C10</b>   | 1.000124 P |

| <b>M8</b>  | 10um/0.5um | <b>Cv1~Cv10</b> | 1.000124 P |

| <b>M9</b>  | 10um/0.5um | <b>Rd</b>       | 9133.16 歐姆 |

| <b>M10</b> | 10um/0.5um |                 |            |

| <b>M11</b> | 10um/0.5um |                 |            |

| <b>M12</b> | 10um/0.5um |                 |            |

| <b>M13</b> | 10um/0.5um |                 |            |

| <b>M14</b> | 10um/0.5um |                 |            |

圖 2.7 Conventional ladder Schottky-diode rectifier

表 2.2 傳統 Ladder Rectifier 與 Modified rectifier 比較表

(MOS diode W/L=10um/0.5um and C=1pF)

| 10-stage                               | Ladder [8]  | Modified    |

|----------------------------------------|-------------|-------------|

| <b>Multiplier Factor=20<br/>(RL=∞)</b> | 較少<br>6.975 | 較多<br>8.575 |

|                      |                 |                 |

|----------------------|-----------------|-----------------|

| Rising time (to1.8V) | 較快<br>1.2E-07   | 較慢<br>1.51E-07  |

| RL=100k, Vp=0.4V     | 不可驅動<br>650mV   | 可驅動<br>3.35V    |

| DC Ripple (RL=∞)     | 較大<br>2.79~2.63 | 較小<br>3.43~3.41 |

| 跨壓承受度                | 電容平均分配          | 電壓完全跨在最後一級電容    |

圖 2.8 Modified Schottky-diode rectifier

圖 2.9 Modified native MOS-diode rectifier and Limiter

(a) 整流電路基本整流單元工作原理

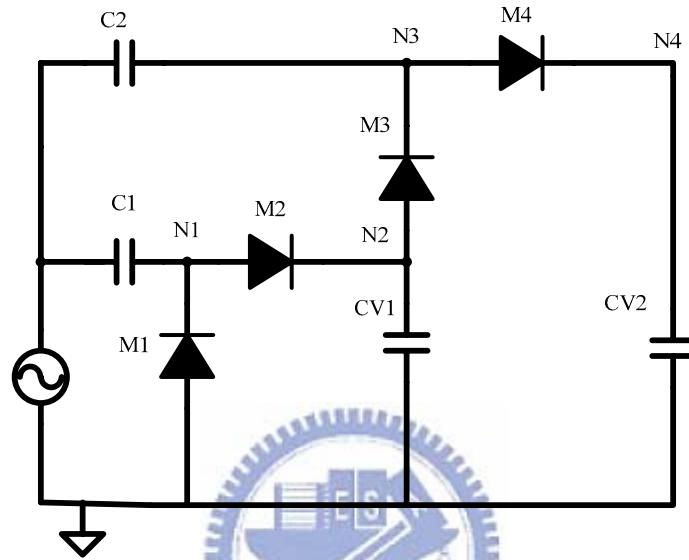

如下圖 2.10 為本篇論文所使用的整流電路中充電單元電路，本篇論文利用 HSPICE

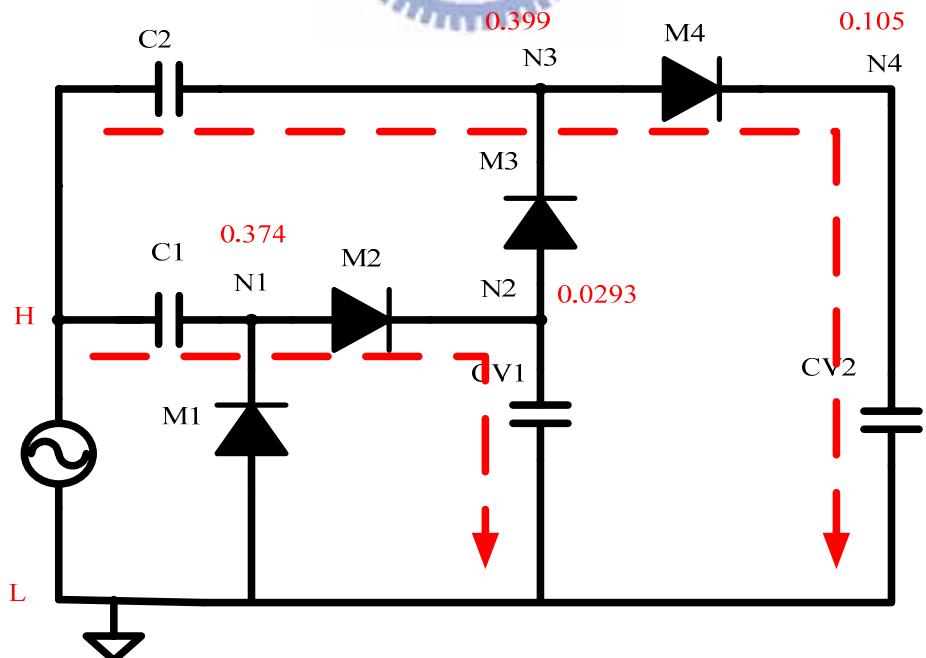

模擬整流電路中整流單元電路，模擬利用輸入 RF 訊號兩正負周期將 DC 電壓建立起來的關係，可以透過此關係了解其充電方式。圖 2.11 為利用 HSPICE 所做的時域模擬圖，當 RF 輸入為  $V_{peak}=0.4V$  去看圖 2.10 中 N1-N4 的節點電壓。取其首 2 個週期以驗證整流電路建立電壓工作原理。

圖 2.10 充電泵電路圖

圖 2.11 建立電壓時域圖

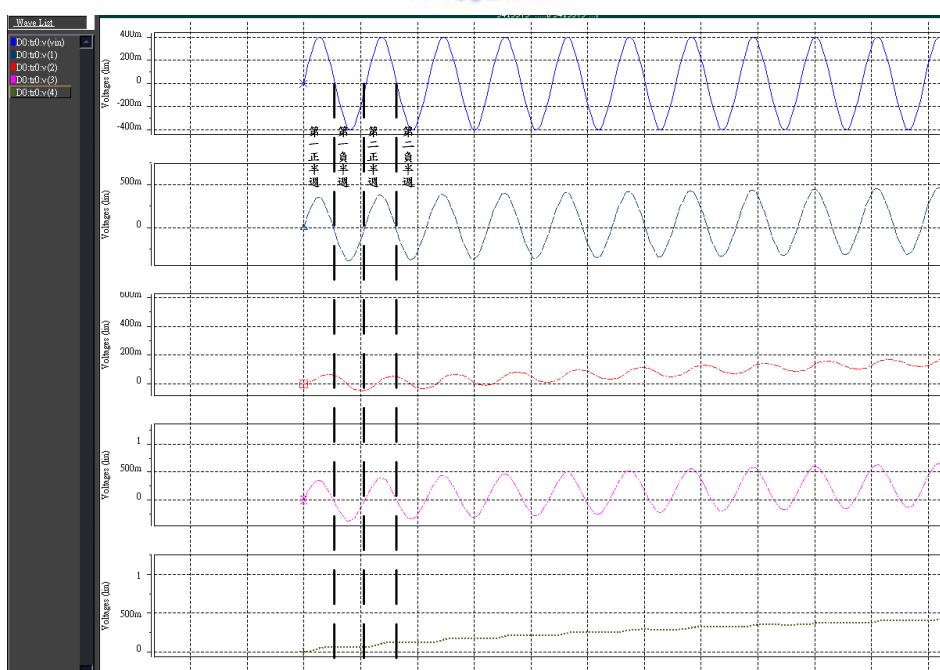

圖 2.12 為模擬 RF 訊號第一正半週狀態，可以經由模擬此時，MOS diode M1 和 M3 是反向偏壓，是關閉的狀態，而 M2 以及 M4 為正向偏壓，所以為開啟的狀態，就如同虛線所示電流流向，而此時 N4 電壓為-0.0457

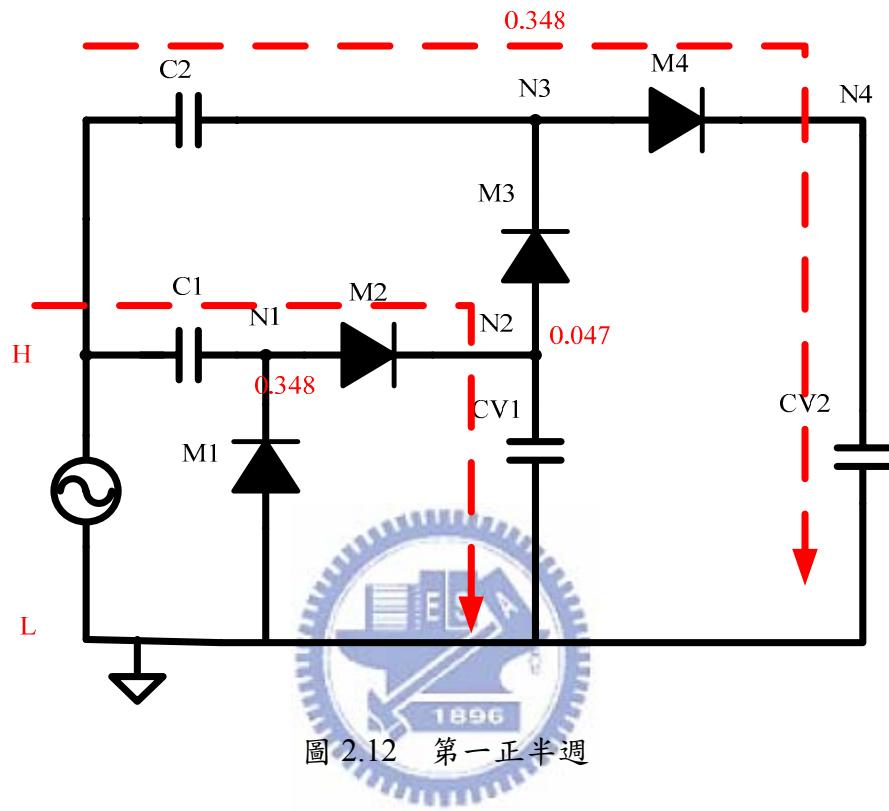

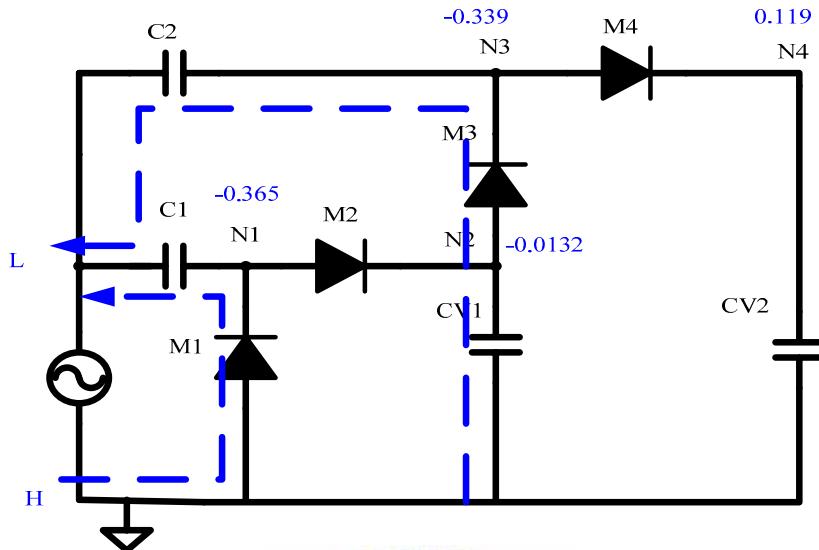

圖 2.13 為模擬 RF 訊號第一負半週狀態，可以經由模擬此時，MOS diode M2 和 M4 是反向偏壓，是關閉的狀態，而 M1 以及 M3 為正向偏壓，所以為開啟的狀態，就如同虛線所示電流流向，而此時 N4 電壓為 0.0614

圖 2.13 第一負半週

圖 2.14 為模擬 RF 訊號第二周期正半週狀態，可以經由模擬此時，MOS diode M1 和 M3 是反向偏壓，是關閉的狀態，而 M2 以及 M4 為正向偏壓，所以為開啟的狀態，就如同虛線所示電流流向，而此時 N4 電壓為 0.105

圖 2.14 第二正半週

圖 2.15 為模擬 RF 訊號第二周期負半週狀態，可以經由模擬此時，MOS diode M2 和 M4 是反向偏壓，是關閉的狀態，而 M1 以及 M3 為正向偏壓，所以為開啟的狀態，就如同虛線所示電流流向，而此時 N4 電壓為 0.119V

圖 2.15 第二正半週

利用圖 2.11 至圖 2.15 可以清楚觀察出充電泵整流電路中的充電單元是先利用正半週將 M2 以及 M4 開啟對電容充電，但當負半週時，M1 與 M3 會打開，將電流流出，但在此時電流所累積電荷已儲存在電容內，所以再當下個週期的輸入信號進入會利用原本的累積的電壓再往上墊，透過多週期後便能建立起 DC 電壓。推廣至十級本篇論文所使用的整流電路圖 2.9，便可知當 RF 輸入信號為正半週時 M2 至 M20 為順向偏壓因此開啟利用輸入訊號對電容充電，負半週期時，便是 M1 至 M19 為順向偏壓，電容經由此放電，透過多個週期的 RF 輸入訊號對電容一充一放所累積在電容內的電荷所建起立的 DC 輸出電壓。

## (b) 整流電路級數決定

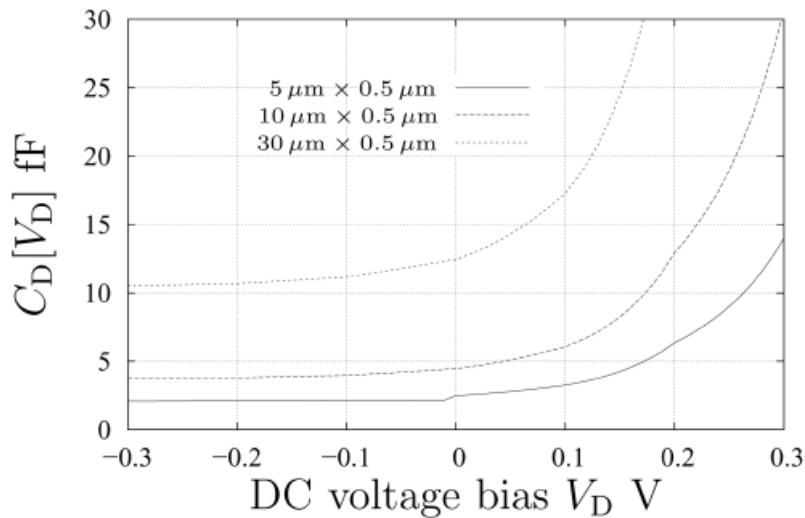

而級數(stage)主要決定在於此篇論文所需要的 DC 直流電壓，但隨著級數(stage)增加其倍壓效率(efficiency)會降低，下圖 2.16 可以看出當  $V_d$ (MOS-diode)跨壓越大時，寄生電容  $C_d$  越大，代表 MOS-diode 透過 RF 充電時，因本身級數越高級時，因  $V_d$  越高，所損失的跨壓會越大，所以造成多加 stage 效率越差。所以此篇論文決定設計十級。

圖 2.16 VD versus CD[18]

## (C)十級整流電路間寬長比例

整流電路架構如上圖 2.5，而整流電路十級間的寬長比比例間的設定，本篇論文利用 HSPICE 模擬整流電路十級 MOS-diode 比例，將其模擬結果整理於表 2.3。模擬環境為 RF 輸入訊號峰值為 0.4V，在觀看 Limiter Out(DC)輸出值，可以觀察到使用 110um/0.5um~100um/0.5um 逐級線性(Linear)增加 size 有最佳的 DC 輸出倍率但寬長比也增加到 100um/0.5um，相對所佔用面積增加，增加效率因寄生電容也同時增加而不是很多，甚至從表 2.3 可見最後以平方速度增加寬長比即使增加到 100um/0.5um 出現了不增

反降的現象。所以在倍率與 size 面積有極大的 trade off。所以整流電路此篇論文選擇十級的 MOS-Diode size 為 10um/0.5um。

表 2.3 充電泵十級各級寬長比例與 DC 輸出比較表

|                          | Original<br>(全<br>10/0.5) | 10/0.5~100/0.5<br>逐級增加<br>(1 倍 liner) | 1/0.5~10/0.5<br>逐級增加<br>(1 倍 linear) | 1/0.5~18/0.5<br>逐級兩倍增<br>加 size<br>(2 倍 linear) | 全部<br>15/0.5 | 1/0.5<br>~100/0.5 以<br>級數平方<br>增加<br>(平方增加) |

|--------------------------|---------------------------|---------------------------------------|--------------------------------------|-------------------------------------------------|--------------|---------------------------------------------|

| <b>Output(V)</b>         | 2.79                      | 3.42                                  | 2                                    | 2.27                                            | 3.14         | 2.72                                        |

| <b>倍壓<br/>(Ideal=20)</b> | 6.975                     | 8.55                                  | 5                                    | 5.675                                           | 7.85         | 6.8                                         |

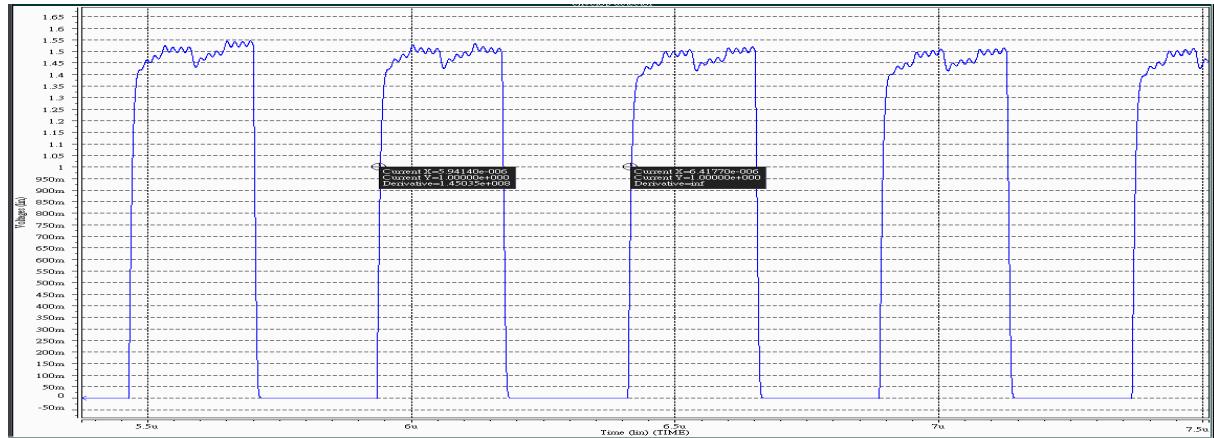

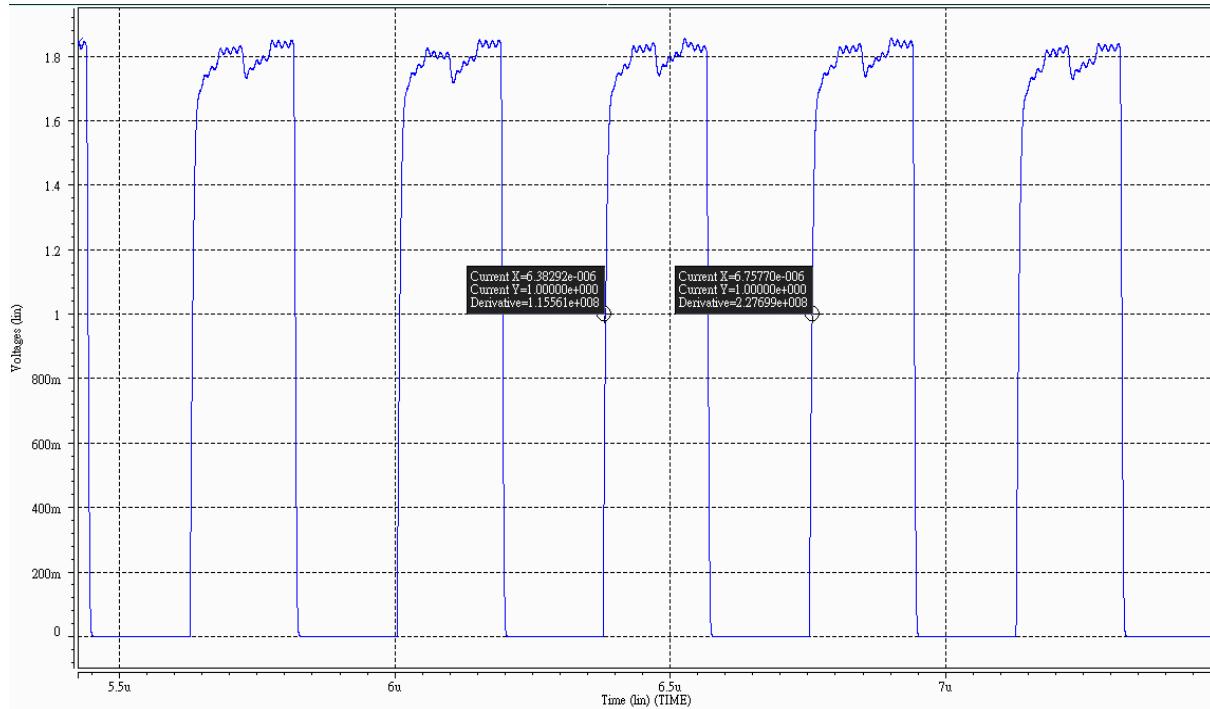

#### (d) 整流電路模擬結果

整流電路模擬結果顯示在圖 2.17 圖 2.18 圖 2.19 中，模擬的項目為 HSPICE model 中的 TT、SS、FF corner 其輸出如圖，可以看出因製程漂移所造成極端 TT、FF、SS 的效應，仍然能正常工作能夠整流出 DC 電壓至少 1.8V 以上

##### a.. TT Corner :

圖 2.17 TT corner

## b. SS Corner :

圖 2.18 SS corner

## c. FF Corner :

圖 2.19 FF corner

## B. 限流電路(Limiter)

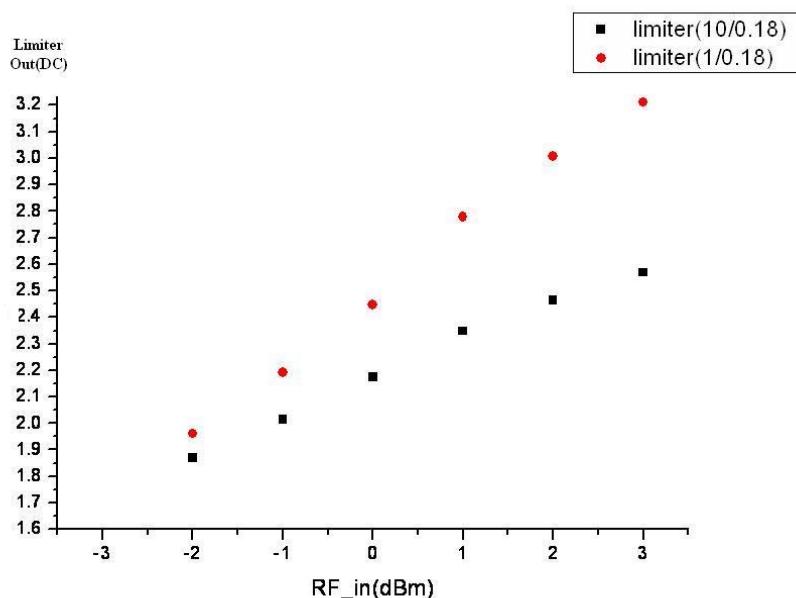

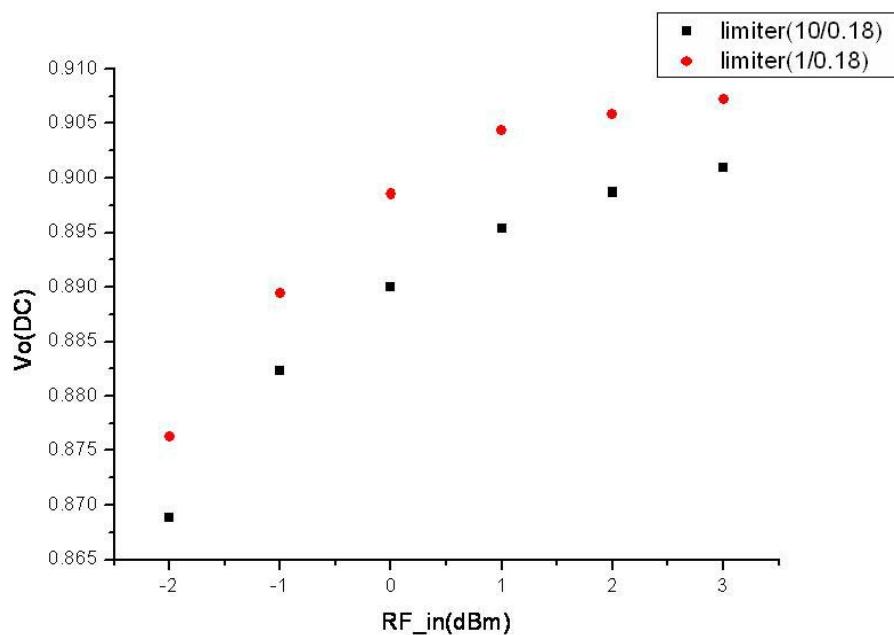

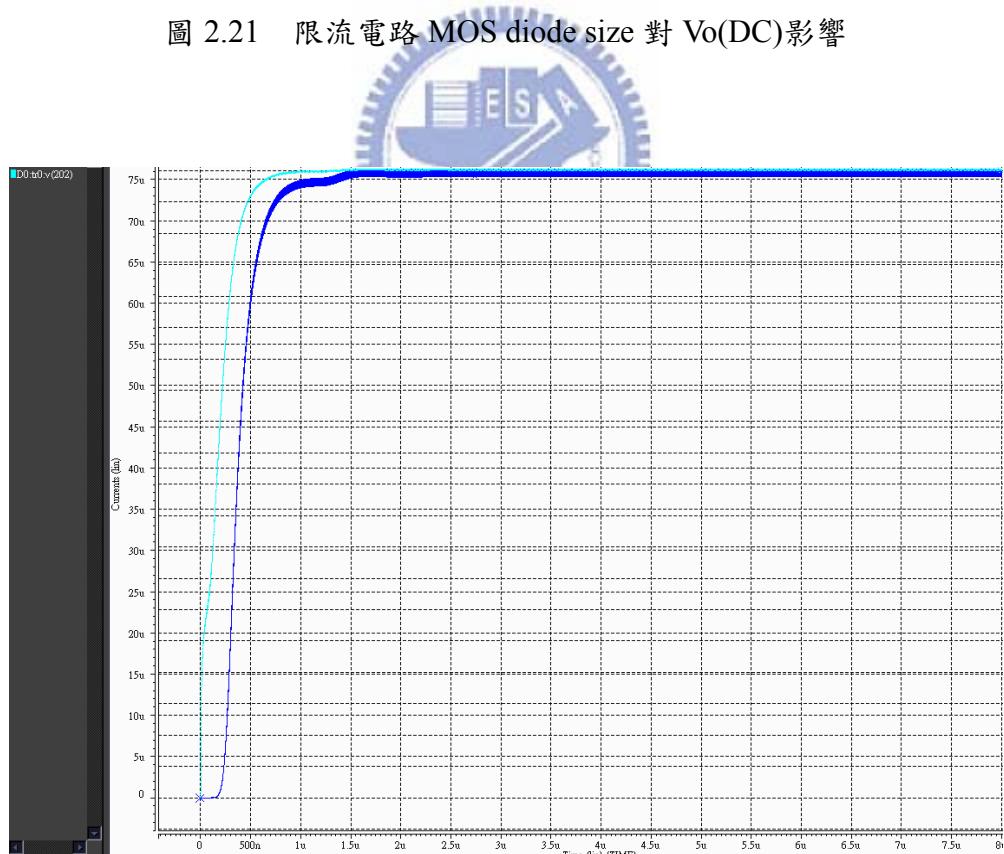

在充電泵輸出掛上一由 MOS diode 串接而成的 Limiter，在充電泵輸出掛上一由 MOS diode 如圖 2.6 所示， $R_d$  設計在  $1K\Omega$ ，主要功用為了阻絕 RF 信號漏到 DC 直流端，另外串接的 MOS diode 避免造成和 Reader 太近，接收能量太強，造成後端電路燒掉，而 MOS diode 寬長比的設計，由圖 2.20 及圖 2.21 驗證可知，當 MOS diode 寬長比設計在  $(1\mu m/0.18\mu m)$  比較設計在  $(10\mu m/0.18\mu m)$  有較高的 Limiter Out(DC) 以及  $V_o(DC)$  輸出電壓，所以本篇論文將限流電路內的 MOS diode 設計在  $(1/0.18\mu m)$ ，限流電路中電阻與 MOS

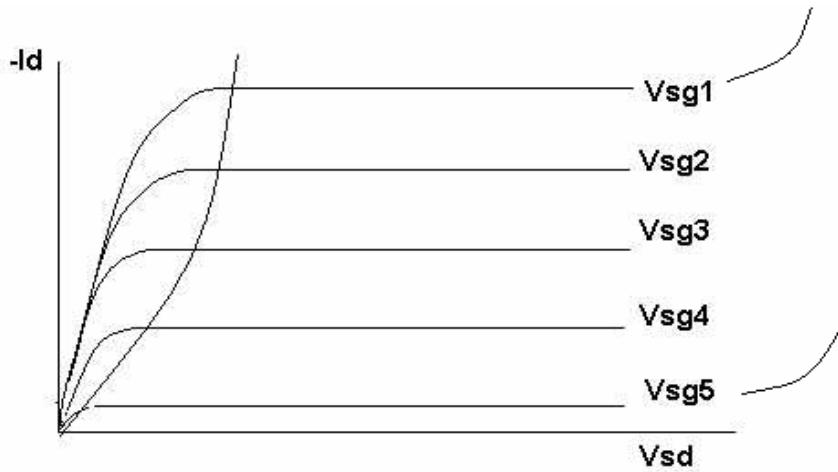

diode 尺寸的選擇表列於下表 2.4 經由 HSPICE 模擬可知其限流電路大約會在 RF Input Power 為-6dBm 啟動。其限流電路極限約為 75uA 如圖 2.22 所示，這是當 RF Input Power=13dBm 時的模擬值，但從此圖 2.22 中 Limiter Out(DC)並看不出已到達極限的情況，主要是由於 TSMC Model 在 HSPICE 中 Vds 和 Id 如下圖 2.23，在 Vds 增加至很大時，Id 仍然為定值，然而當 Vds 很大時候 Id 會隨著 vds 往上增加才對，所以 TSMC Model 就是在此時出現偏差，Id 並不會跟著上升，換句話說便是燒掉的情況並無法從模擬中察覺。

表 2.4 限流電路電晶體尺寸

| Device | Size       | Device | Size       |

|--------|------------|--------|------------|

| M21    | 1um/0.18um | M24    | 1um/0.18um |

| M22    | 1um/0.18um | Rd     | 1um/0.18um |

| M23    | 1um/0.18um |        |            |

圖 2.20 限流電路 MOS diode size 對 Limiter Out(DC)影響

圖 2.21 限流電路 MOS diode size 對  $V_o(DC)$  影響

圖 2.22 RF Input Power 為 13dBm 時流經限流電路電流

圖 2.23 TSMC Model 中源級至汲級電壓與 Id 關係圖

## B. 穩壓電路(Voltage Reference)

### (a) 穩壓電路設計與工作原理

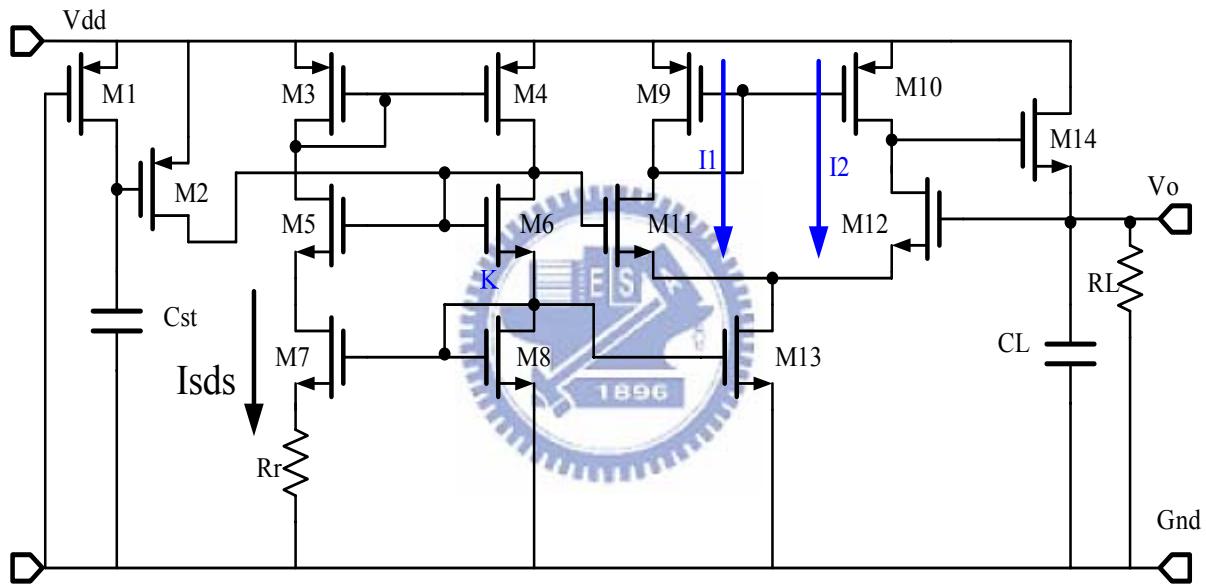

如圖 2.24 為此篇文章設計使用的穩壓電路主要為[7]的架構，包括三個部份。是使用 startup 電路以及 single stage op amp 以及最後利用 M14 當作 negative feedback 以及 buffer stage。Vdd 是接前一級 Limiter out(DC)所產生的直流電壓源，而 startup 電路包括圖 2.24 的 M1 和 M2 以及 Cst，其透過 M1 gate 接地 always on 接著導通 M2 接著 M2 drain 電壓升高，提供後段電路有偏壓，避免 cascode 兩邊電流等於 0 電路 idle 的情況，等到 Cst 充電完成便會自動把 PMOS M2 關掉，完成 start up 程序將 start up。而 cascode 是利用 M5-M8 構成 cascode 而具有負回授功能有效壓制各 MOS Gate 電壓穩定，透過穩定 MOS Gate 電壓，可以使 M5-M8 穩定工作在 subthreshold region，也因此始  $I_{sds}$  穩定工作在幾十 nA，可以大幅降低能量消耗(power consumption)，而汲級到源級(drain-source)電流如 Eq.(3)所示

$$I_{sds} = I_{do} \frac{W}{L} e^{q(V_{gs} - V_{th})/nkT} \quad (3)$$

其中

$$I_{do} = \mu_n C_{ox} \left( \frac{KT}{q} \right)^2 e^{1.8} \quad (4)$$

再利用 Eq.(3)(4)推出 M7 和 M8 閘級對源級(Gate-source)電壓，其中 M7 寬長比為 M8 的 Q 倍。

$$V_{gs8} = n \frac{kT}{q} \ln \left[ \frac{I_{sds} * L}{I_{do} * W} \right] + V_{th} \quad (5)$$

$$V_{gs7} = n \frac{kT}{q} \ln \left[ \frac{I_{sds} * L}{I_{do} * Q * W} \right] + V_{th} \quad (6)$$

$$V_{gs7} = V_{gs8} + I * R_r \quad (7)$$

利用 Eq.(5)(6)(7)導出 Eq.(8)

$$I_{sds} = \frac{nkT}{q R r} \ln Q \quad (8)$$

從 Eq.(8)得知當 vdd 有微幅抖動時可以透過 M7 和 M8 關係式將變動電壓隔絕使電壓變動對 M8 閘級(gate)電壓變動不大達到穩壓的效果，使其連接到第二部份 M13 的閘級成為一穩定電流源(constant current source)，使差動輸入(Differential input)電流合會變成 constant 加上 M14 當作負回授(negative feedback)來抑制 M12 汲級(drain)電壓與 Vo 的關係使得 Vo 有穩定的電壓輸出。

此外在 cascode 我們使其工作在 subthreshold region 但我們並沒有使用如同前面 charge pump 一樣的 native MOS，基於 low power 考量我們採用一般的 MOS，主要由於 [19] 中的 Eq.(9)可以看出當 Vt 越小時會造成 Ioff 電流成 exponential 的增加，所以基於低功耗(low power)考量此篇論文採用一般的 MOS

$$I_{off} = (100nA) \frac{W}{L} e^{\frac{-qV_T}{\eta kT}} \quad \text{where } \eta = 1 + \frac{C_{dep}}{C_{ox}} \quad (9)$$

另外而當 Vdd 有微幅抖動時可以透過 M7 和 M8 關係式 Eq.(8)將變動電壓因素隔絕使電壓變動對結點 K 電壓變動不大而達到穩壓的效果，並且如圖 2.10 中節點 K 連接到第二部份單級 OP 的 M13 的閘極使其成為一穩定電流源(constant current source)，促使如圖

2.24 中所示  $I_1+I_2$  會變成 constant 加上  $M_{14}$  當作負回授(negative feedback)來抑制  $M_{12}$  汲級(drain)電壓與  $V_o$  的關係使得  $V_o$  有穩定的電壓輸出。

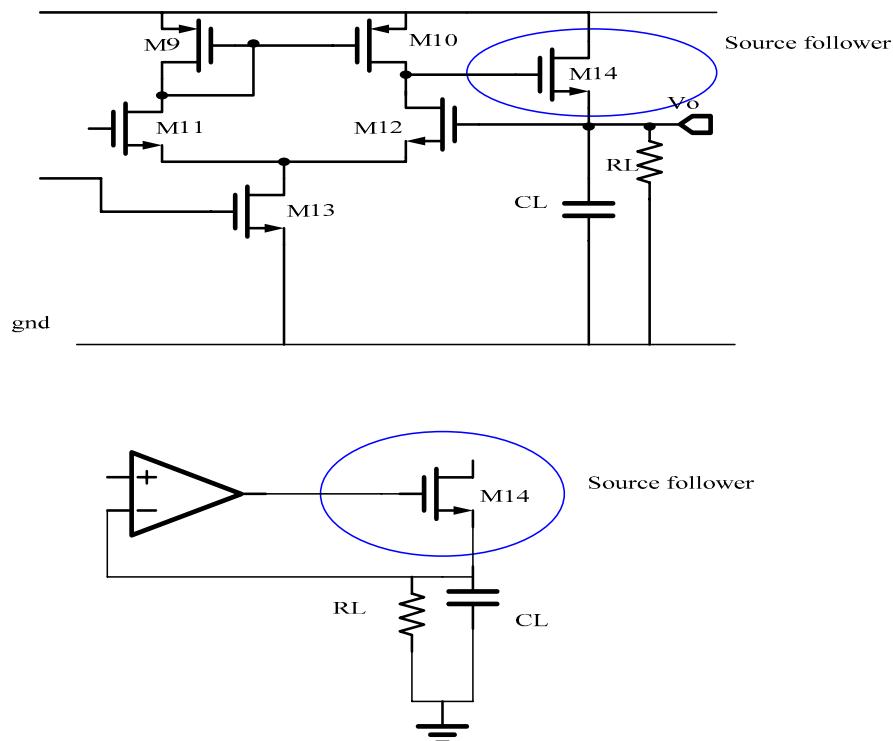

就如上面所提  $M_{14}$  source follower 作用是一方面當作負回授(negative feedback)的作用另外主要作用是用來當作 drive 重載(heavy load)用如圖 2.25 所示，由於從  $M_{14}$  源級看進去阻抗(impedance)較小，可以加強對於後級  $RL$  的驅動能力，而另外設計過程中必須小心  $M_{14}$  汲級與源級跨壓( $V_{ds}$ )不能損失太多，造成  $V_o$  輸出電壓過低，此缺點可以透過 Eq.(2). 關係透過提高  $W/L$  來降低對  $V_{dd}$  造成的跨壓損失，以提高  $V_o$  的電壓輸出。

圖 2.24 Modified native MOS-diode charge pump and Limiter

圖 2.25 穩壓電路等效圖

而本篇論文所使用的穩壓電路所使用電晶體尺寸整理成下表 2.5

表 2.5 穩壓電路電晶體尺寸

| Device    | Size         | Device     | Size         |

|-----------|--------------|------------|--------------|

| <b>M1</b> | 1um/0.18um   | <b>M10</b> | 0.6um/5um    |

| <b>M2</b> | 1um/0.18um   | <b>M11</b> | 0.42um/5um   |

| <b>M3</b> | 3.8um/0.6um  | <b>M12</b> | 0.42um/4.6um |

| <b>M4</b> | 3.8um/0.6um  | <b>M13</b> | 2.2um/2.6um  |

| <b>M5</b> | 0.8um/0.25um | <b>M14</b> | 10um/10um    |

| <b>M6</b> | 1um/0.25um   | <b>Cst</b> | 6.6612 P     |

| <b>M7</b> | 1.2um/0.3um  | <b>Rr</b>  | 913.757 歐姆   |

| <b>M8</b> | 1.2um/0.3um  |            |              |

| <b>M9</b> | 0.6um/0.3um  |            |              |

## (b) 穩壓電路(Voltage Reference)模擬

下圖 2.26 與圖 2.27 為用 HSPICE 模擬當 RF input power 變化時 RF 轉成 DC 輸出值 Limiter out(DC) 以及 Voltage reference 的直流輸出  $V_o$ 。而模擬時負載選擇使用模擬後端數位邏輯電路的負載  $1\text{pF}$  以及  $1\text{Mega}\text{ }\Omega$  電阻以及模擬環境為  $30^\circ\text{C}$ ，負載選擇  $1\text{ Mega}\text{ }\Omega$  的原因是由於依照[20]ATMEL ATA5590 的 IC 中數位邏輯電路耗電流  $2\text{uA}$ ，可以依此推估出  $2\text{V}/2\text{uA}=1\text{Mega}\text{ }\Omega$ ，所以模擬負載是選擇  $1\text{Mega}\text{ }\Omega$ 。

可以從圖 2.26 與圖 2.27 模擬結果比較可以看出原本在 RF Input Power 變化下 Limiter Out 輸出變化極大，但在穩壓電路工作下，可以讓  $V_o$  輸出穩定在  $800\text{mV}$  以上，以作為穩定的偏壓，以供解調變電路中比較器的穩定電流源偏壓。

圖 2.26 Limiter Out(DC) 輸出 versus RF input power

圖 2.27  $V_o(DC)$  輸出 versus RF input power

### 2.1.2 啟動重置電路(Power On Reset Circuit)

#### (a) 啟動重置電路架構介紹

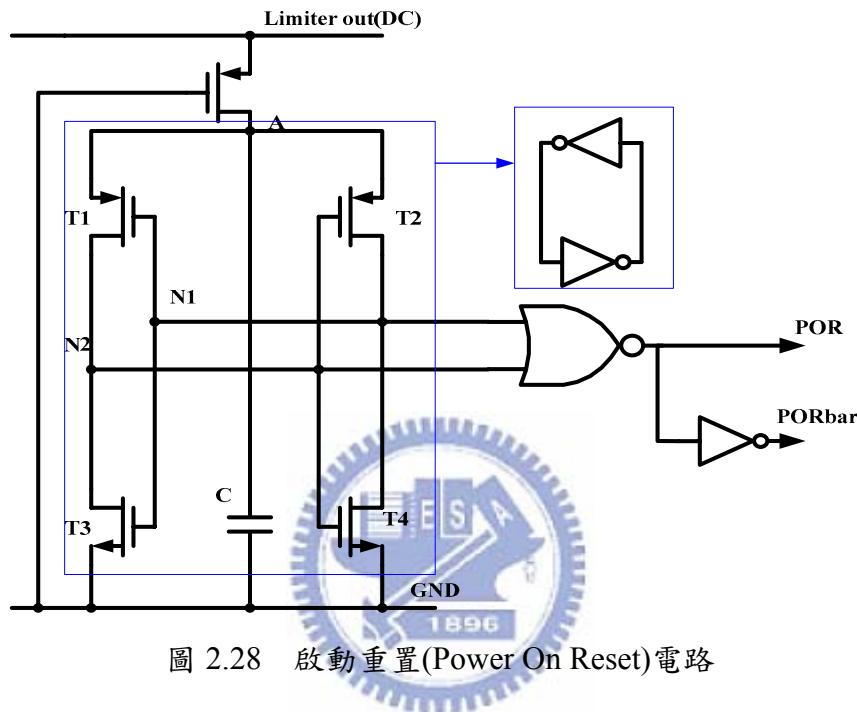

由於後端數位訊號處理邏輯部分，在電壓足夠工作開始時，需要一個重置(Reset)訊號來促使邏輯電路歸為預設狀態，所以在RFID標籤前端電路中也需要一個啟動重置電路(Power On Reset)以免數位訊號處理端因干擾造成訊號錯誤。本篇論文所使用的啟動重置電路如下圖 2.28，其優點是利用數位邏輯方式產生訊號，所以反應快速，也可以取最小尺寸，以節省能量以及電路面積，啟動重置(Power On Reset)電路主要原理是利用兩個反向器(Inverter)間當節點 N1 和節點 N2 相反所以當電壓足夠開始反向器(Inverter)正常工作時，節點 N1 和節點 N2 會不同所以 POR 輸出 0，另外由於反向器還未正常工作時，

節點 N1 和節點 N2 都是 0 所以邏輯閘 NOR 輸出 POR=1，但可以足夠供應反向器電壓工作時 POR 會變成 0，另外設計實可以利用控制 C 越大因充電多進而控制延遲大，所以利用控制 C 的大小，來調整工作電壓與重置訊號延遲的時間。表 2.6 為起動重置電路內電晶體尺寸表，由於始用數位方式，所以設計上基本採用最小面積。

圖 2.28 啟動重置(Power On Reset)電路

表 2.6 啟動重置電路電晶體尺寸

| Device    | Size         | Device (Nor)        | Size         |

|-----------|--------------|---------------------|--------------|

| <b>M1</b> | 1um/0.18um   | <b>M1</b>           | 1um/0.18um   |

| <b>T1</b> | 1.5um/0.36um | <b>M2</b>           | 1um/0.18um   |

| <b>T2</b> | 3um/0.36um   | <b>M3(PMOS)</b>     | 1.5um/0.18um |

| <b>T3</b> | 4um/0.18um   | <b>M4(PMOS)</b>     | 1.5um/0.18um |

| <b>T4</b> | 2um/0.18um   | <b>Device (Inv)</b> | Size         |

| <b>C</b>  | 951.6 f      | <b>PMOS</b>         | 1.5um/0.18um |

|           |              | <b>NMOS</b>         | 1um/0.18um   |

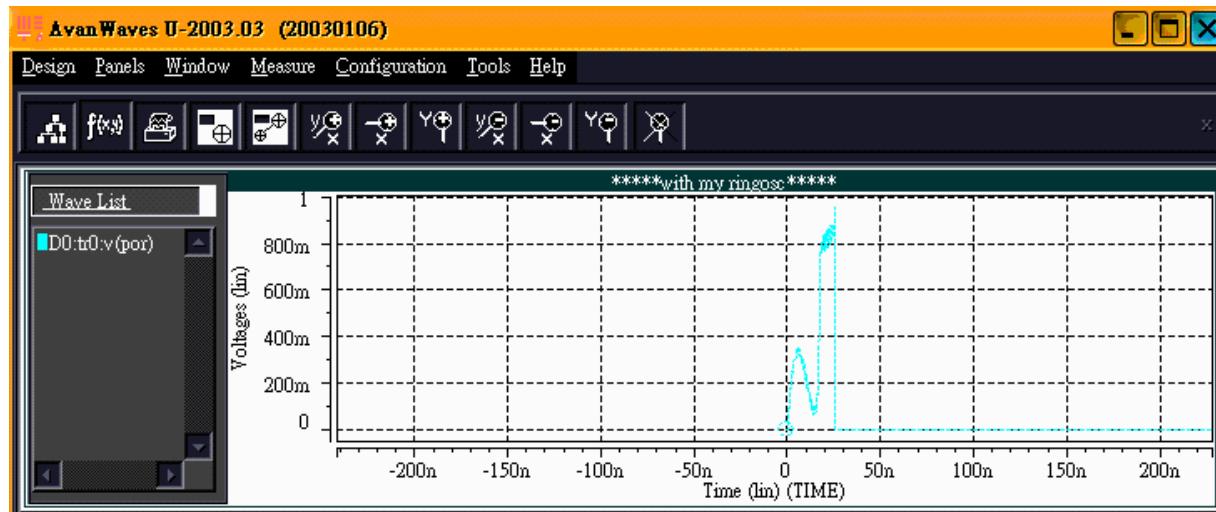

## (b) 啟動重置電路架構模擬

下圖 2.29 為 Hspice 中模擬啟動重置電路功能，能在當 Limiter Out(DC)電壓由前端整流電路倍壓產生後，驗證 Power On Reset 會產生一 trigger 給後端數位訊號處理有個重置訊號後，但由於電壓持續上升反向器正常工作，使圖 2.28 中的 NOR logic 功能將 Por 的訊號壓至低準位。

圖 2.29 Por signal 時間變化圖

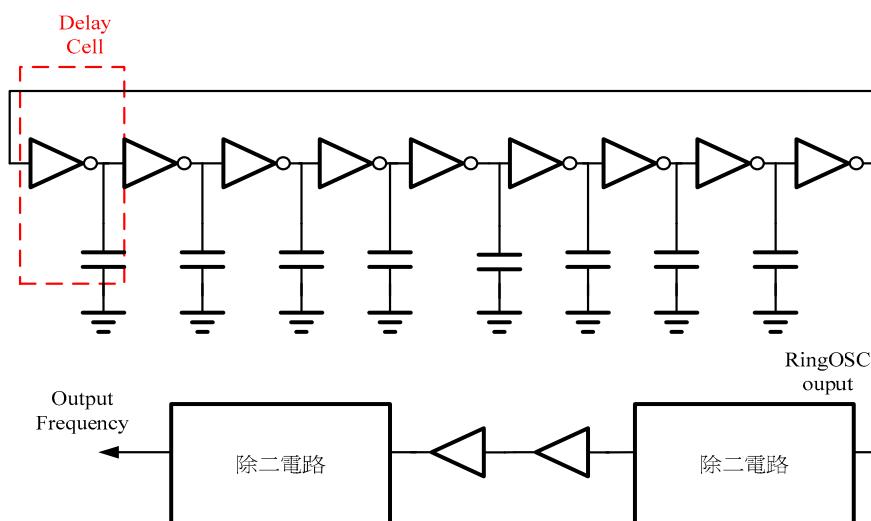

## 2.1.3 環式振盪電路(Ring Oscillator)

## (a) 環式振盪電路架構

為了提供數位訊號處理邏輯部份 FPGA 一個振盪源，所以此篇論文採用環式振盪器(Ring Oscillator)搭配兩個除法器來使用使輸出頻率約 2.56MHz 左右，選擇在 2.56MHz 的原因，是因為要配合數位訊號處理端是使用 FPGA 實現功能。振盪器主要選擇是在延遲單元(Delay Cell)的選定如下圖 2.30，如果為了配合 FPGA 設計出已達到我們所需要的

極低頻率，方式有二

- 可以透過增加電容

- 增加 delay stage

但由於使用過大的電容會造成整個震盪電路面積相當大，所以透過兩級的除法器，將原本 10.24MHz 的震盪頻率降至數位邏輯所需的 2.56MHz 左右，以節省原本所需頻率的電容面積，因此此篇論文採取九級的架構，而延遲單元使用的電容為 1.23741p，以達到換式振盪器輸出為 10.24MHz。下圖 2.30 為整個環式振盪器(Ring Oscillator)的架構。

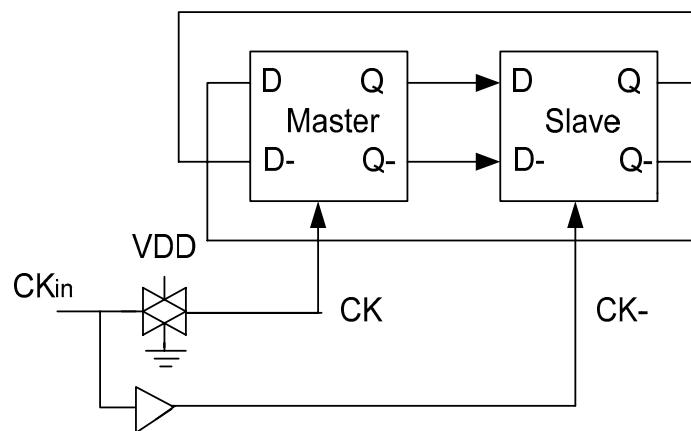

其中除二電路通常是由 2 個門鎖(latches)以主僕式(master-slave)架構組成，其具有正交相位輸出的特點，圖 2.31 所示為主僕式除頻器的示意圖。振盪器輸入除二電路訊號之工作週期(Duty cycle)的對稱度，與除頻器輸入端是否匹配，是除頻器法能否產生準確信號的關鍵。由於使用除頻器對於製程上的偏移容忍度較高、所佔的晶片面積較小、具有增益可使信號增強，並且應用的頻帶較廣而有別與多相位濾波器的窄頻應用。然而其缺點在於因為增加了除頻器，而提高了整體電路在功率上的消耗。

而圖 2.32 所示為除二電路中使用的兩個閘鎖與中間的緩衝器(buffer)，雖然為了提高電壓位準而提供較佳的除二波形輸出，但其缺點也因此提高了整體電路在功率上的消耗。另外將整個環式振盪器與除二電路的電晶體尺寸與電容大小整理表列於表 2.7 中。

圖 2.30 環形震盪電路

圖 2.31 主僕式除頻器方塊圖

圖 2.32 除二電路

表 2.7 環式振盪電路及除二電路電晶體尺寸

| Device(Ring OSC) | Size          | Device (Divider 2)      | Size          |

|------------------|---------------|-------------------------|---------------|

| C1~C8(9 stage)   | 1.237414 P    | Transmission gate(PMOS) | 1.08um/0.18um |

| Delay cell(PMOS) | 1.08um/0.18um | Transmission gate(NMOS) | 0.54um/0.18um |

| Delay cell(NMOS) | 0.54um/0.18um | Buffer(PMOS)            | 1.08um/0.18um |

|                     |               |                     |               |

|---------------------|---------------|---------------------|---------------|

| <b>Delay cell</b>   | 9 stage       | <b>Buffer(NMOS)</b> | 0.54um/0.18um |

| <b>Buffer(PMOS)</b> | 1.08um/0.18um | <b>Buffer</b>       | 2 stage       |

| <b>Buffer(NMOS)</b> | 0.54um/0.18um |                     |               |

| <b>Buffer</b>       | 2 stage       |                     |               |

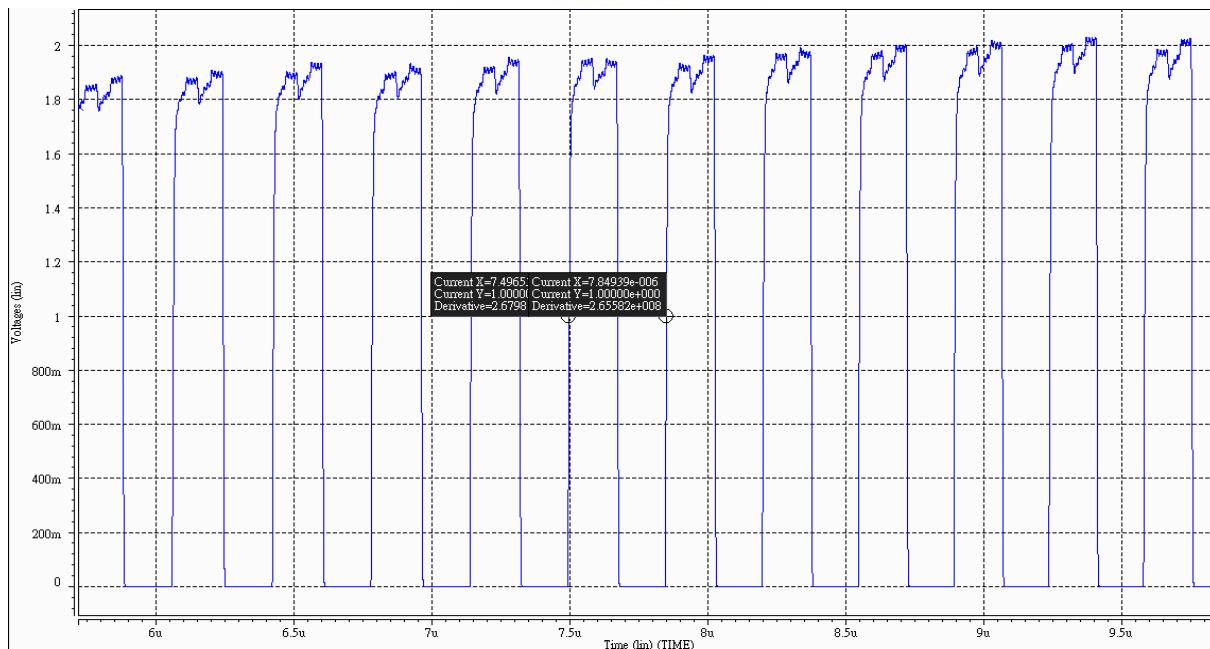

### (b) 環式振盪電路模擬

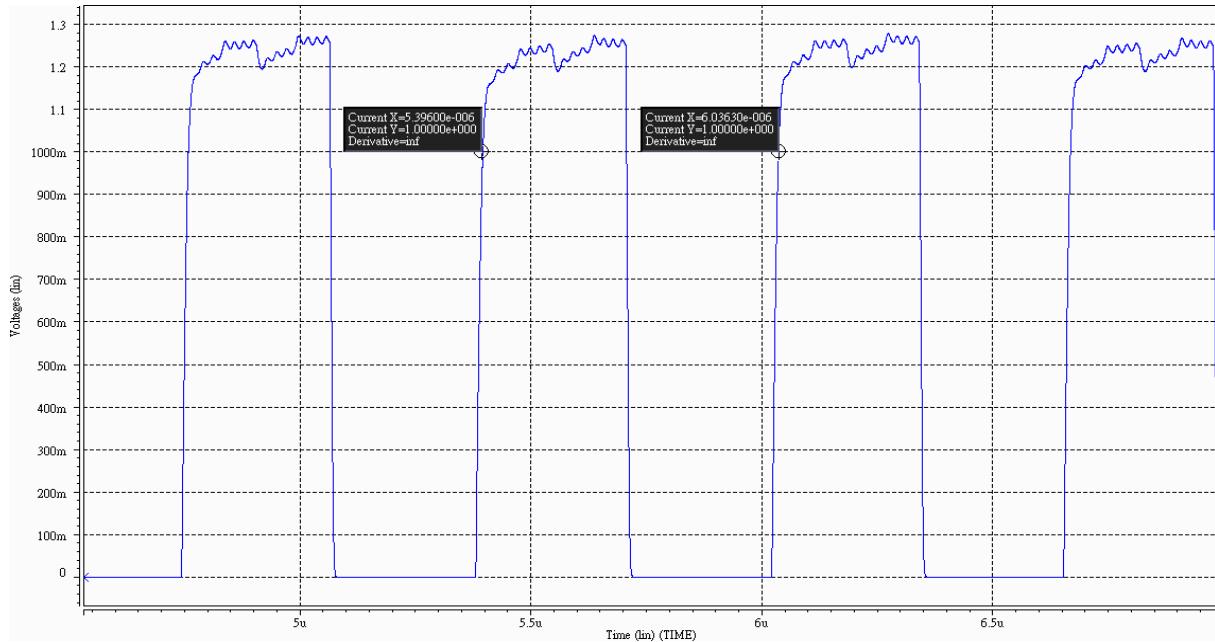

此篇論文所使用的環式振盪器(Ring Oscillator)先透過環式震盪器先振出 10.24MHz 再經過除四電路，將頻率降至 2.56MHz 附近為我們目標 Output Oscillation frequency 所使用模擬環境 Input Power 為 2dBm 且環境溫度為三十°C。下圖 2.33 圖 2.34 圖 2.35 圖 2.36 以及圖 2.37 分別針對因為製程漂移作 TT、SS、FF、FS、SF 五個 corner 的模擬，對輸出頻率的影響與漂移程度，最後將其因製程漂移的 corner 情況對振盪輸出頻率偏移程度整理成表。

- TT corner

可以由下圖 2.33 由 HSPICE 模擬在 TT 這個 corner 情況下可以找出 Output(after divider) Oscillator frequency 為 2.6682MHz

圖 2.33 TT Output Oscillation frequency

- FF corner

可以由下圖 2.34 由 HSPICE 模擬在 FF 這個 corner 情況下可以找出 Output(after divider) Oscillator frequency 為 3.3259MHz

圖 2.34 FF Output Oscillation frequency

- SS corner

可以由下圖 2.35 由 HSPICE 模擬在 SS 這個 corner 情況下可以找出 Output(after divider) Oscillator frequency 為 1.8388MHz

圖 2.35 SS Output Oscillation frequency

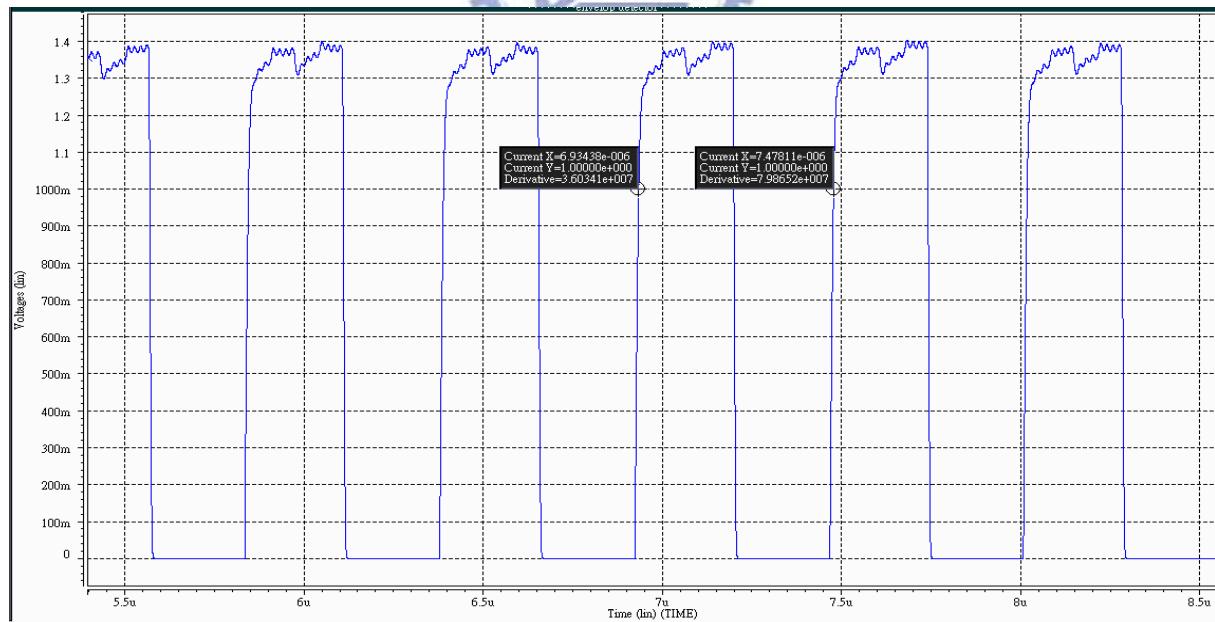

- SF corner

可以由下圖 2.36 由 HSPICE 模擬在 SF 這個 corner 情況下可以找出 Output(after divider) Oscillator frequency 為 2.0995MHz

圖 2.36 SF Output Oscillation frequency

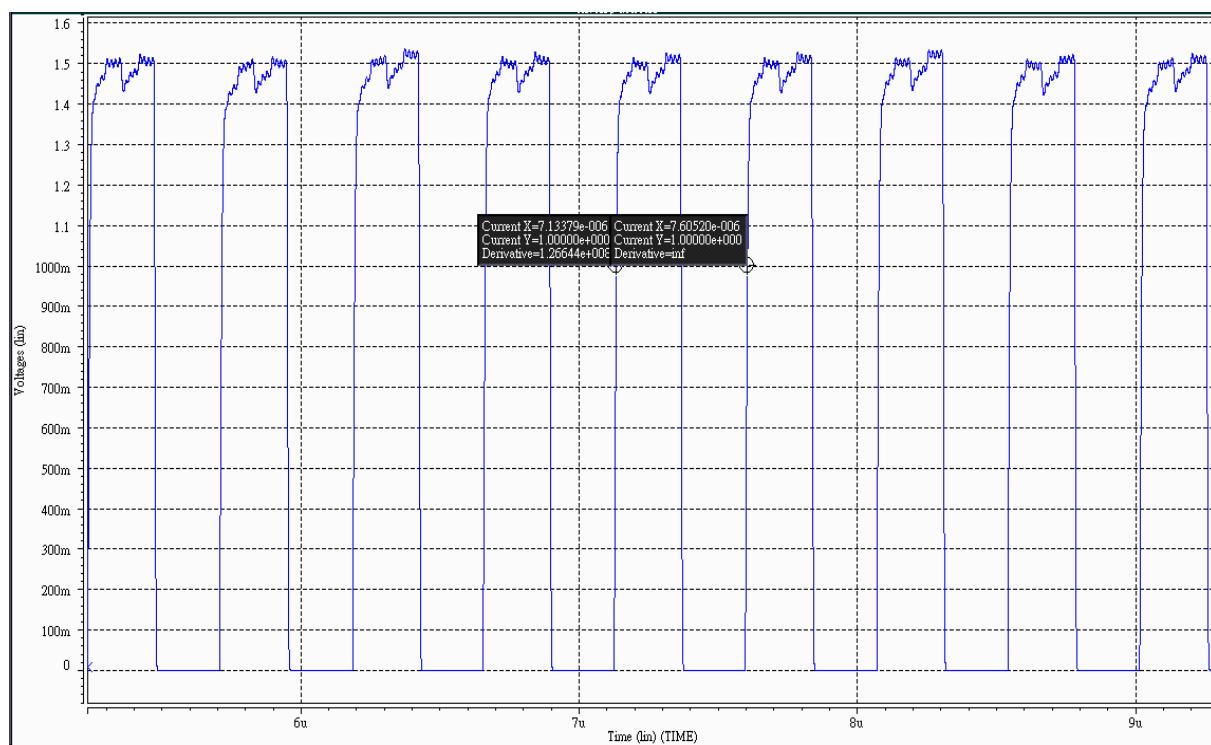

- FS corner

可以由下圖 2.37 由 HSPICE 模擬在 FS 這個 corner 情況下可以找出 Output(after divider) Oscillator frequency 為 2.8788MHz

圖 2.37 FS Output Oscillation frequency

總結以上模擬結果可整理成下表 2.8 可以由此表現出其偏差量由 1.8388MHz 到 3.3259MHz，但由於提供中華大學數位訊號處理端的時脈設定在此區間內還是可以正常處理其指令，所以符合其時脈所允許區間，所以可知因其製程漂移的五個 corner 依然可以正確的提供數位訊號處理所需要時脈振盪源。

表 2.8 五個 corner 對振盪器輸出頻率影響

| Corner                       | TT     | SF     | FS     | FF     | SS     |

|------------------------------|--------|--------|--------|--------|--------|

| <i>Output frequency(MHz)</i> | 2.6682 | 2.0995 | 2.8788 | 3.3259 | 1.8388 |

### ● 電容製程偏移

由於本篇論文設計使用環式震盪器，所以在每級的延遲單元(Delay cell)掛的電容對輸出頻率影響甚大，因此電容製程偏移也會對振盪頻率造成影響，所以此節特別針對設計電容+10%以及-10%當作模擬方式看振盪頻率的偏移量。模擬環境為 RF Input Power 為 2dBm 並且環境溫度 30°C

可以由下圖 2.38 由 HSPICE 模擬在電容偏差-10%這個情況下可以找出 Output(after divider) Oscillator frequency 為 3.2087MHz

圖 2.38 設計電容偏移 10%(-)

可以由下圖 2.39 由 HSPICE 模擬在電容偏差+10%這個情況下可以找出 Output(after divider) Oscillator frequency 為 2.6386MHz

圖 2.39 設計電容偏移 10%(+)

基於以上模擬圖 2.38 以及圖 2.39 可知當電容漂移從+10%到-10%，環式振盪器輸出頻率將從 2.6386MHz 變化到 3.2807MHz。

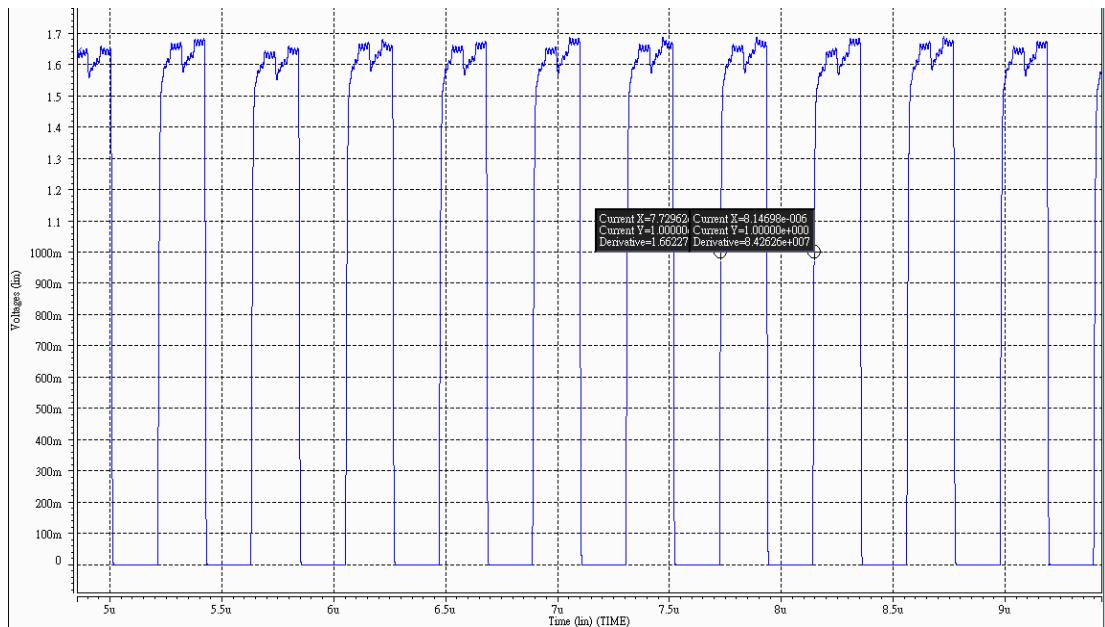

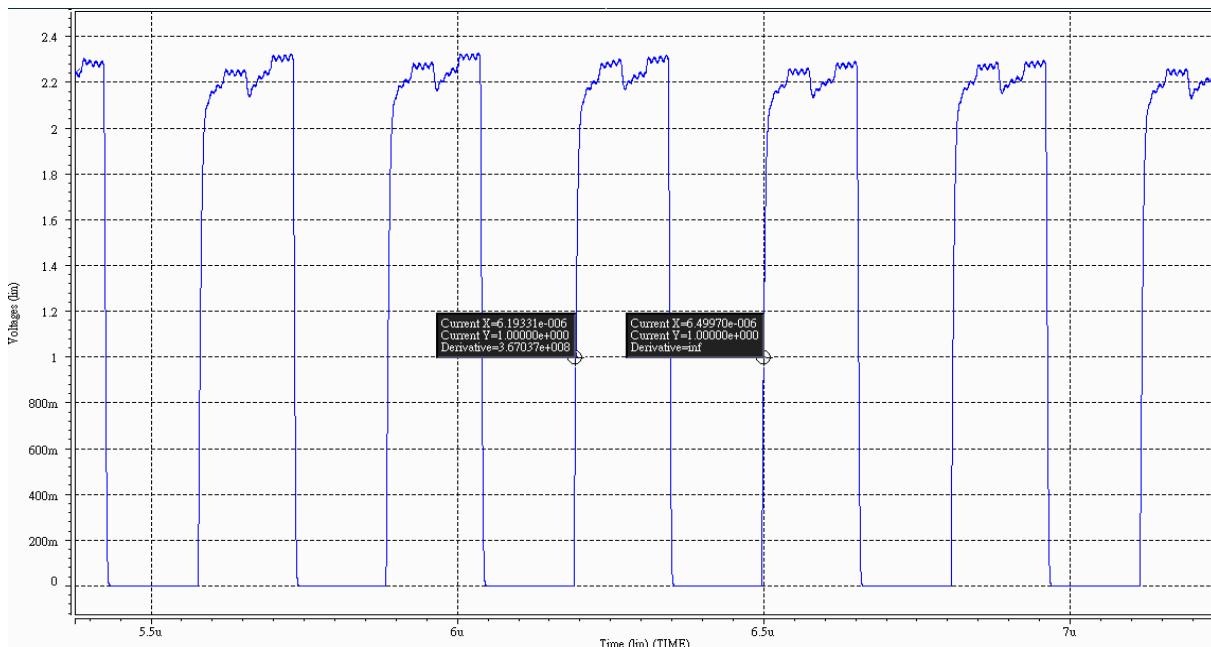

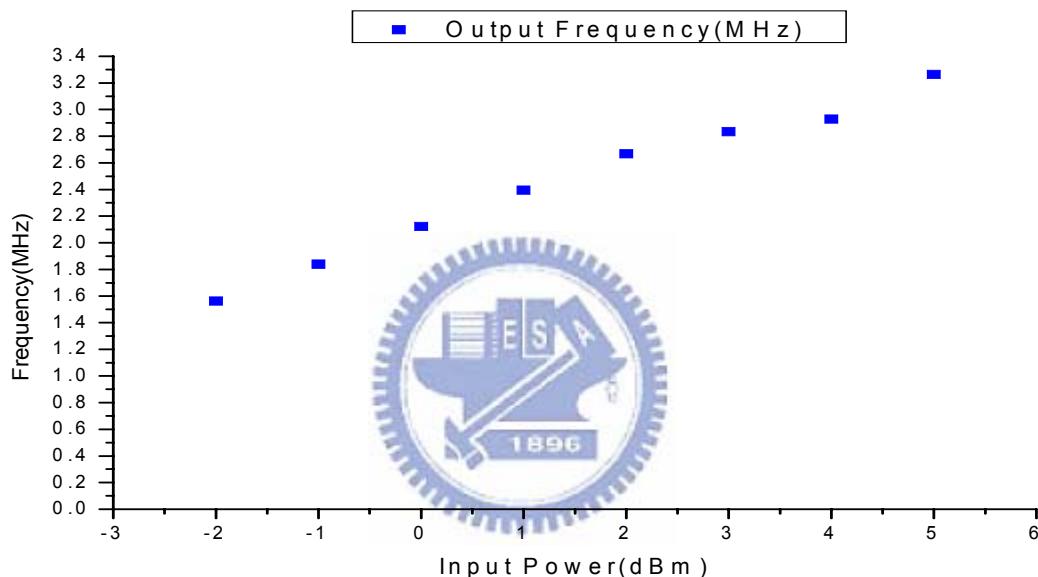

#### ● RF Input Power 變更

由於 RFID 系統會由於感應距離變化造成輸入能量(RF Input Power)的變更所以針對這一部分此篇論文也針對環式振盪器模擬對 RF Input Power 變化時而造成的 Output frequency 的變更。

可從下圖 2.40 當 RF Input Power 為-2dBm 時為環式振盪器輸出頻率為 1.5618MHz

圖 2.40 Input power 為-2dBm 時 Output Oscillation frequency

可從下圖 2.41 當 RF Input Power 為-1dBm 時為環式振盪器輸出頻率為 1.8391MHz

圖 2.41 Input power 為-1dBm 時 Output Oscillation frequency

可從下圖 2.42 當 RF Input Power 為 0dBm 時為環式振盪器輸出頻率為 2.1213MHz

圖 2.42 Input power 為 0dBm 時 Output Oscillation frequency

可從下圖 2.43 當 RF Input Power 為 1dBm 時為環式振盪器輸出頻率為 2.396MHz

圖 2.43 Input power 為 1dBm 時 Output Oscillation frequency

可從下圖 2.44 當 RF Input Power 為 2dBm 時為環式振盪器輸出頻率為 2.6682MHz

圖 2.44 Input power 為 2dBm 時 Output Oscillation frequency

可從下圖 2.45 當 RF Input Power 為 3dBm 時為環式振盪器輸出頻率為 2.8340MHz

圖 2.45 Input power 為 3dBm 時 Output Oscillation frequency

可從下圖 2.46 當 RF Input Power 為 4dBm 時為環式振盪器輸出頻率為 2.9282MHz

圖 2.46 Input power 為 4dBm 時 Output Oscillation frequency

可從下圖 2.47 當 RF Input Power 為 5dBm 時為環式振盪器輸出頻率為 3.2638MHz

圖 2.47 Input power 為 5dBm 時 Output Oscillation frequency

總結以上圖 2.40~圖 2.47 針對可能因感應距離不同而造成的 RF Input Power 變化對環式振盪器輸出頻率的影響整理製作成下圖 2.48，由圖 2.48 可知當 RF Input Power 從 -2dbm 到 6dBm 其環式振盪器輸出頻率從 1.5618MHz 也偏移至 3.2638MHz 在此區間中，仍在後端中華大學數位訊號處理時脈區間內，因此當 RFID 標籤在移動中造成讀卡機送至標籤晶片的 RF Input power 在變化時，此篇論文所提供的環式振盪器仍然能給予數位訊號處理邏輯電路在變動區間內的時脈訊號，使其可正常作數位訊號處理。

圖 2.48 Input power versus Output frequency

#### 2.1.4 解調變電路(Demodulator)與調變電路(Modulator)

##### A. 解調變電路(Demodulator)

###### (a) 解調變電路架構

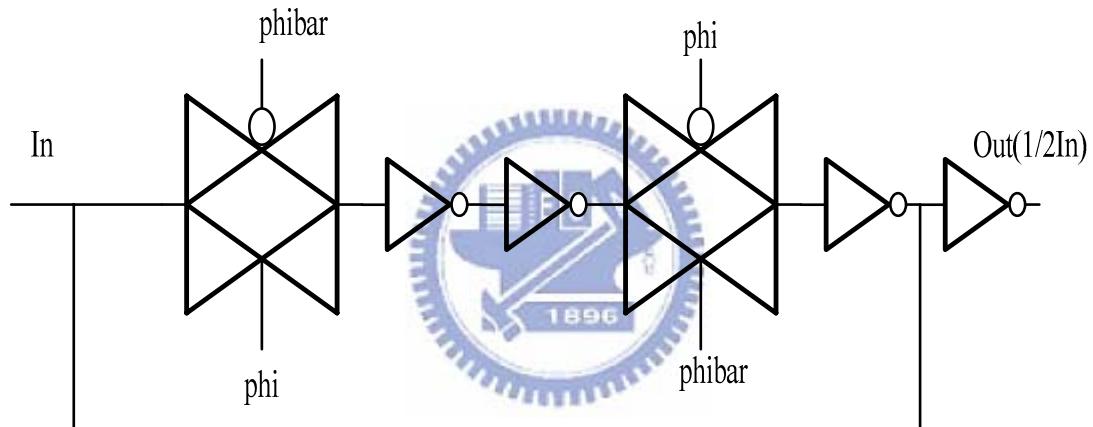

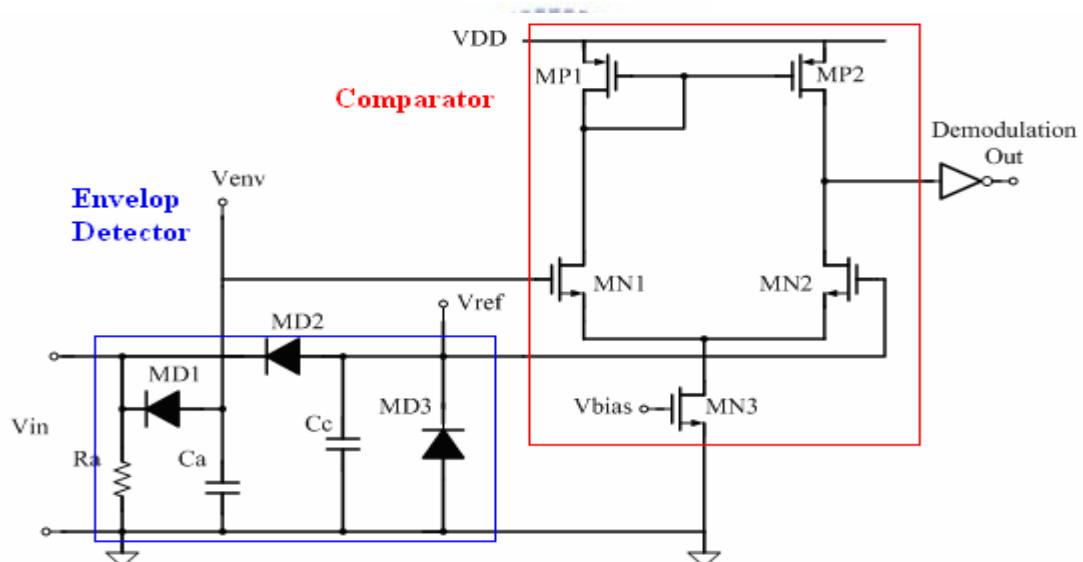

解調變電路(Demodulator)包括了檢波電路(Envelop detector)以及比較電路

(Comparator)如圖 2.49 與圖 2.50 所示其電路圖與方塊圖，而檢波器與比較器工作原理主要是利用 MOS Diode ON 使 RF 輸入訊號的負半週對電容  $C_a$  和  $C_c$  充電，當  $V_{ref} > V_{env}$  而比較器輸出為高電位，解出載波上的資訊為 1，另一方面而在 MOS diode OFF 將 RF 訊號關閉時，此時跨在電容  $C_a$  上的  $V_{env}$  放電路徑為  $MD1$  經過  $R_a$  放電而跨在電容  $C_c$  上  $V_{ref}$  為經過  $MD2$  透過  $R_a$  放電，此時  $V_{env} > V_{ref}$  用比較器差動輸入(Differential Input)讓其 demodulation Out 輸出為低電位，解出載波上的資訊為 0，完成 OOK(On off Keying)解調變機制。 $V_{env}$  會在 MOS diode off 時大於  $V_{ref}$  是由於  $MD3$  當作電阻造成放電較慢讓  $V_{ref}$  hold 住不會放太多電，所以  $V_{env}$  會在 Switch OFF 時大於  $V_{ref}$ ，另外  $V_{bias}$  是從前面圖 2.24 穩壓電路(Voltage Reference)拉出穩定偏壓  $V_o$ ，使  $MN3$  為穩定電流源。另外將本篇論文所設計的解調變電路電晶體尺寸分成檢波器與比較器整理於表 2.9 中。

圖 2.49 Demodulator

圖 2.50 Demodulator 電路方塊圖

表 2.9 環式振盪電路及除二電路電晶體尺寸

| Device(Detector) | Size       | Device(Comparator)  | Size          |

|------------------|------------|---------------------|---------------|

| <b>MD1</b>       | 2um/0.5um  | <b>MP1</b>          | 0.54um/0.18um |

| <b>MD2</b>       | 80um/0.5um | <b>MP2</b>          | 0.54um/0.18um |

| <b>MD3</b>       | 80um/0.5um | <b>MN1</b>          | 1.5um/0.18um  |

| <b>Ca</b>        | 30.475f    | <b>MN2</b>          | 1.5um/0.18um  |

| <b>Cc</b>        | 1.22736 P  | <b>MN3</b>          | 3um/0.18um    |

| <b>Ra</b>        | 913.577 歐姆 | <b>Buffer(PMOS)</b> | 1.08um/0.18um |

|                  |            | <b>Buffer(NMOS)</b> | 0.54um/0.18um |

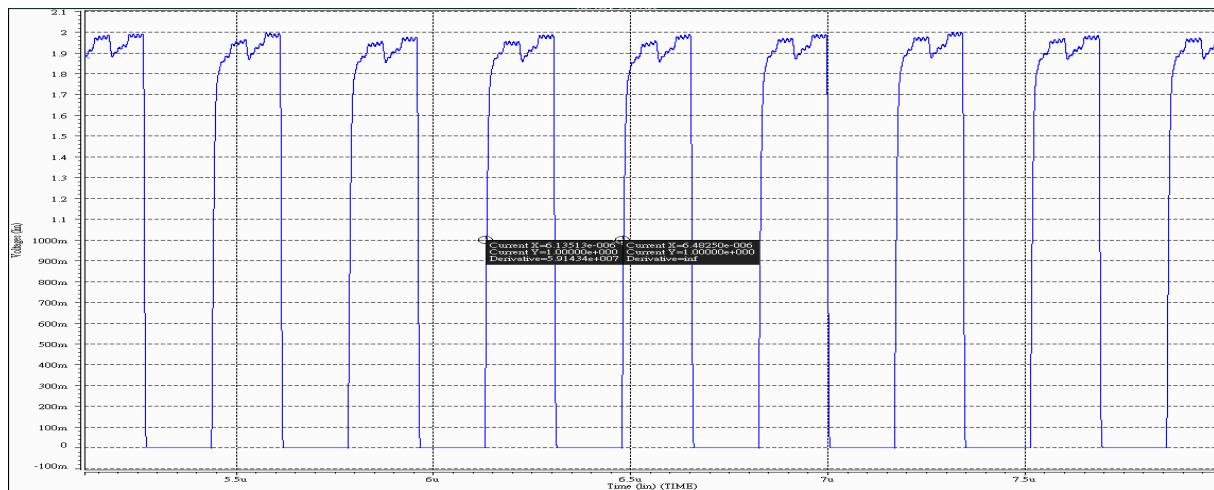

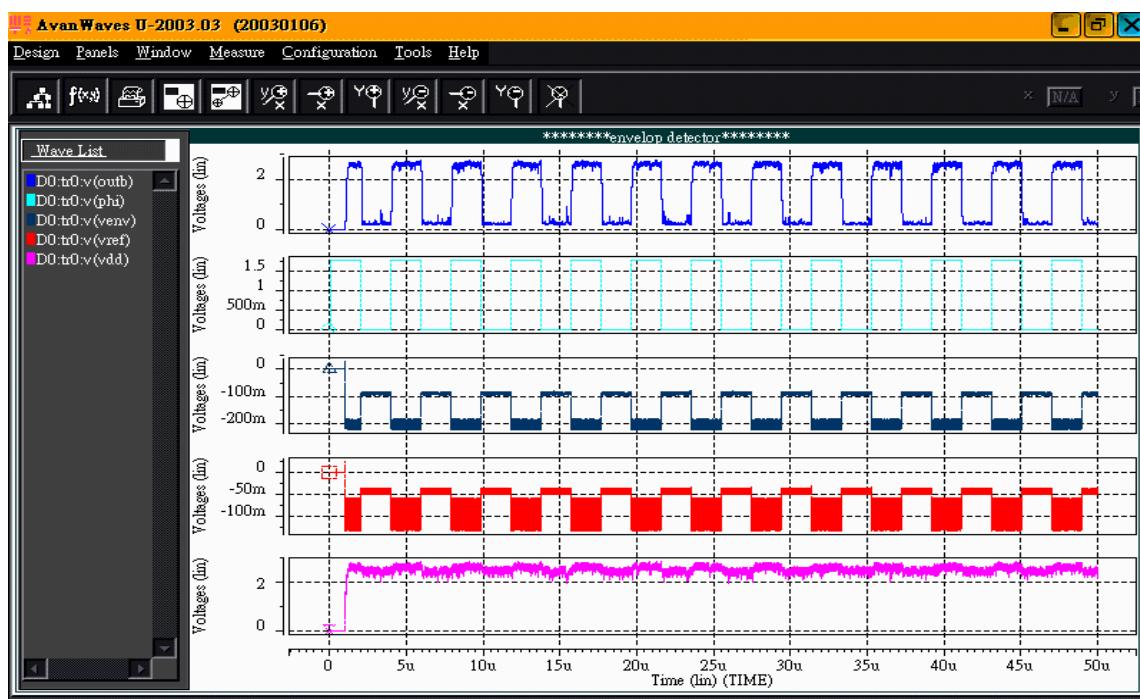

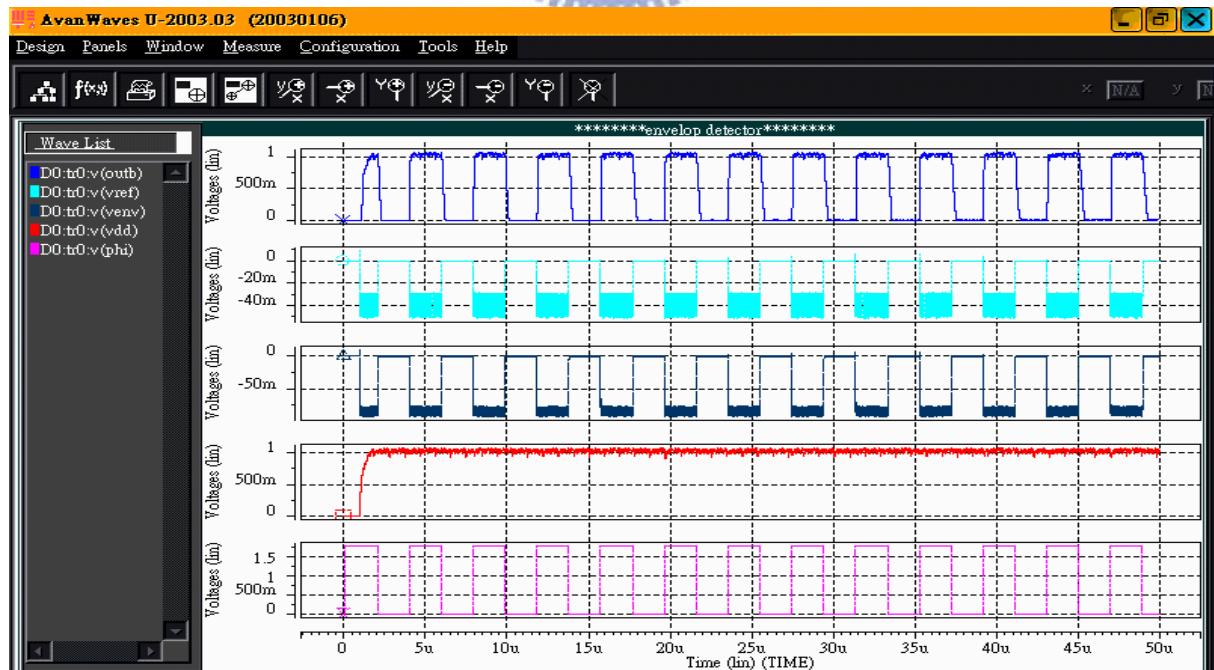

(b) 解調變電路模擬

本篇論文模擬解調變電路方式是以訊號源加上開關模擬讀卡機所送至標籤端的訊

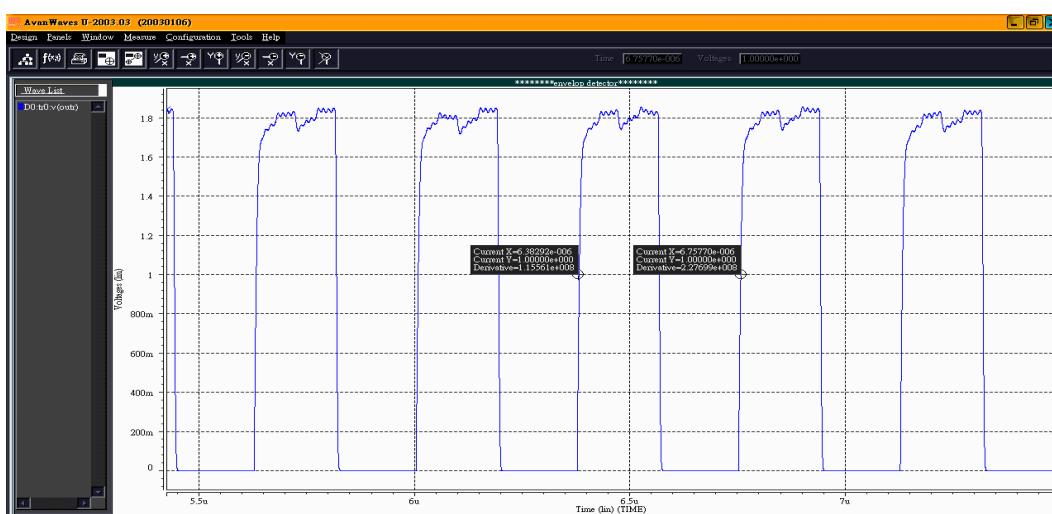

號，所以下圖 2.51 以及圖 2.52 為模擬解調變電路在 RF Input Power 變化下能夠解調變出開關外加的訊號源，達到解調變的功能。利用 HSPICE 模擬的環境便是利用一連續 SIN 波加上一個開關(Switch)利用訊號 phi clock 去控制開關來達到訊號源 OOK(On Off Keying)調變的效果所以解調變電路在正常工作下能夠把較為低頻用作 OOK 效果的開關訊號 outb 解調變出來，而將載波去掉，所以在訊號源選擇以下 RF Input Power 較為極端的兩點為 7dBm 以及 -4dBm 以模擬解調變電路在工作區間內都工作正常。

在 RF Input Power 為 7dBm 情況時模擬結果中如下圖 2.51 中 outb 解調變訊號輸出為與控制開關的脈波源 phi clock 同步代表解調變電路工作正常，正確解出調變信號。

圖 2.51 Input power 為 7dBm 的 data slicer 輸出

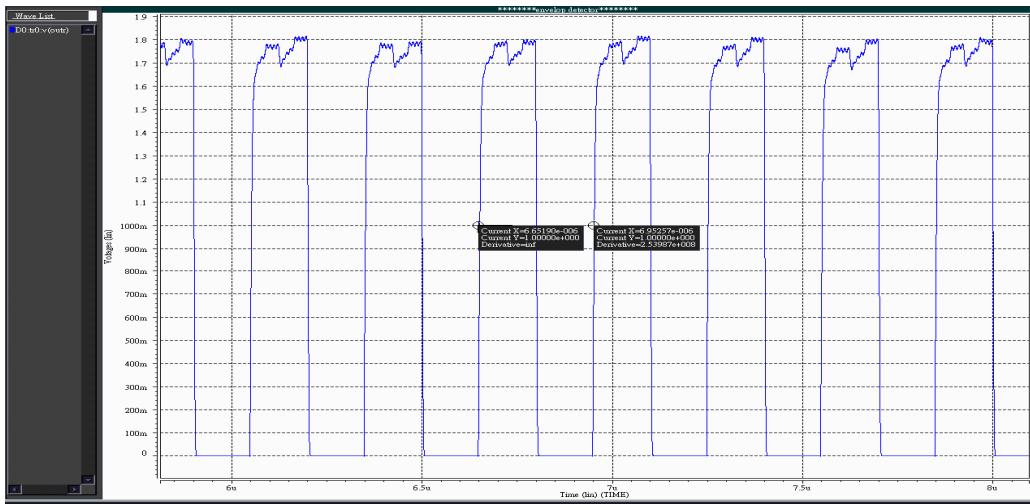

在 RF Input Power 為 -4dBm 情況時模擬結果中下圖 2.52 中 outb 解調變訊號輸出為與控制開關的脈波源 phi clock 同步代表解調變電路工作正常，正確解出調變信號。

圖 2.52 Input power 為 -4dBm 的 data slicer 輸出

## B. 調變電路(Modulator)

## (a) 調變電路架構

調變電路此篇論文使用的如圖 2.53 所示，因為採用 OOK(On off keying)(附錄 B)，所以主要利用一個 NMOS Switch 跨接在天線輸入端的兩端，在數位訊號處理端將處理後的資料送出高電位與低電位的控制訊號，來控制開關(Switch)的開或關，而在開關開路時為晶片看進去的輸入阻抗(Input Impedance)，而在控制開關為短路時為天線兩端短路起來，其輸入阻抗接近五十歐姆，利用此點  $\Gamma$  的不同，造成回覆讀卡機的 backscattering 的振幅不同，進而讀卡機便能分辨出標籤傳來的資料是 0 或 1。

圖 2.53 調變電路

## (b) 調變電路架構模擬

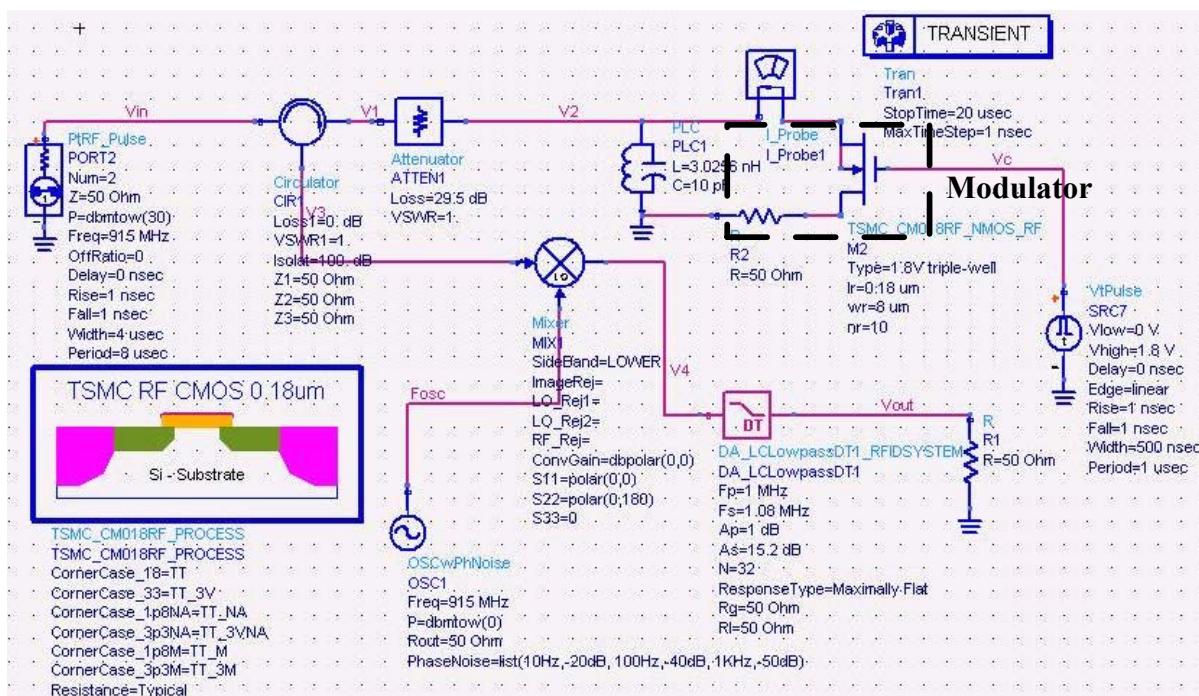

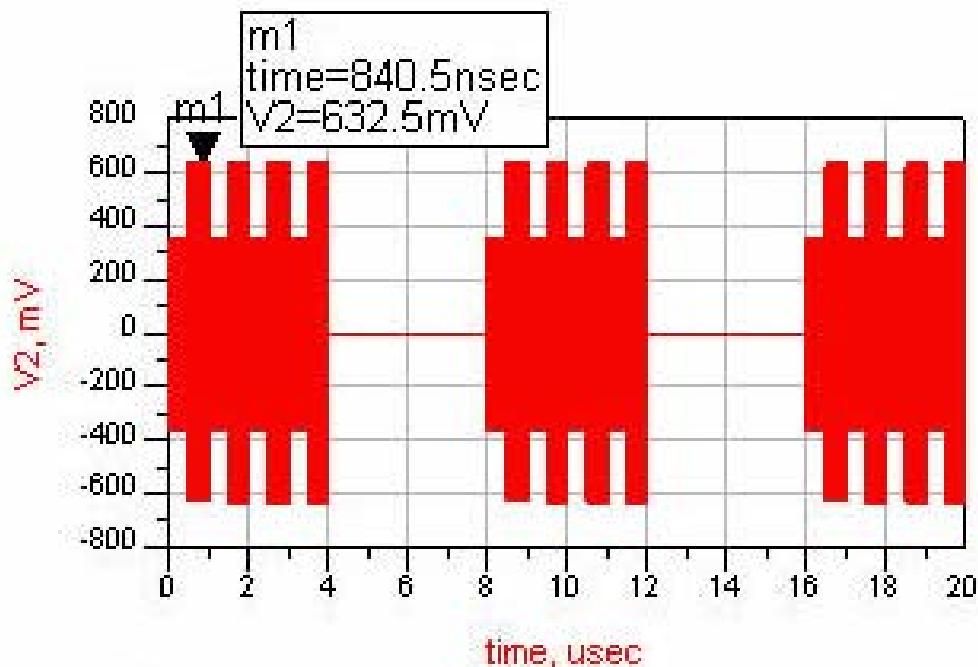

利用 ADS 所做 RFID 系統模擬調變電路的 ASK 效應，如下圖 2.54 以及圖 2.55，可以觀察出 Switch 的 OOK 的實際效應，在載波上可以看見調變波載在上面。

圖 2.54 調變電路模擬系統

圖 2.55 利用 backscatter 調變電路產生 ASK 訊號

### 2.1.4 模擬結果結論

總結以上本篇所設計的標籤前端電路模擬結果也是分成充電泵(charge pump)主要

包括了整流電路與限流電路(rectifier 和 limiter)以及 穩壓(Voltage reference)電路、提供後

端數位處理的啟動重置(Power On Reset)電路，解調變電路(Demodulator)以及環形震盪

(Ring Oscillator)，以及調變電路(Modulator)charge pump 以及 voltage reference 來做模擬

最後在整個電路去做模擬，另外也將 Bond wire 效應以掛 0.3nH 的電感加進去模擬，以

確保分部工作正常以及全部電路工作以及預期效果正確。

## 2.2 設計流程

### 2.2.1 整流電路

1. 構想整體電路架構。

2. 思考如何設計將輸入的 915MHz RF 訊號如何最有效率轉成 DC 電壓，利用 MOS size 降低  $V_{th}$ ，和 coupling capacitor 和提升 charge 的速度

3. 利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬(Pre Simulation)再做調整。

4. 利用 Cadence Virtuoso Tools 佈局

5. 佈局後驗證(Post Simulation)。

6. 晶片製作。

### 2.2.2 穩壓電路

1. 構思整體電路架構

2. 設計 cascode 的電流以達到低功耗的目標

3. 利用設計負回授 M14 並且利用 M14 大小控制 Vo 輸出直流電壓位準

4. 利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬(Pre Simulation)

再做調整。

5. 利用 Cadence Virtuoso Tools 佈局

6. 佈局後驗證(Post Simulation)。

7. 晶片製作。

### 2.2.3 啟動重置電路

1. 構思整體電路架構

2. 利用透過 C 的調整造成 Delay 以及提升 Por 的 voltage level

3. 另外一方面透過設計充電電流的 PMOS size 也可以控制 Delay 時間

4. 利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬(Pre Simulation)再做調整。

5. 利用 Cadence Virtuoso Tools 佈局

6. 佈局後驗證(Post Simulation)。

7. 晶片製作。

### 2.2.3 環式振盪器電路

1. 構思整體電路架構

2. 設計 Delay cell(取 Power , Area , frequency )及變動量來設計 Delay cell

3. 設計除二電路(取 Power 以及 Area 考量)

4. 利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬(Pre Simulation)再做調整。

5. 利用 Cadence Virtuoso Tools 佈局

6. 佈局後驗證(Post Simulation)。

7. 晶片製作。

#### 2.2.4 解調變電路與調變電路

1. 構思整體電路架構

2. 利用透過  $R_a$  ,  $C_a$  ,  $C_c$  調整  $V_{ref}$  和  $V_{env}$  接近

3. 另外一方面透過微調當做放電路徑的 MD1 和 MD2 以及電阻用的 MD3, 使  $V_{env}$  隨著 phi clock 動作大於  $V_{ref}$  使得後端比較器能夠正確比較出來  $V_{ref}$  和  $V_{env}$

4. 利用 HSPICE 作 Transistor Level 的電路設計及動作驗證與模擬(Pre Simulation)再做調整。

5. 利用 Cadence Virtuoso Tools 佈局

6. 佈局後驗證(Post Simulation)。

7. 晶片製作。

## 2.3 電路模擬功率消耗結果

對於 RFID 系統而言，RF 與 DC 功率間的轉換是極為重要的，因為在 RFID 讀卡機(Reader)與標籤(Tag)間的感應距離長度，取決於足夠能量能讓晶片正確工作，也就是當標籤使用能量越足夠時，標籤與讀卡機間正確感應距離變能延伸至更長中而在整個系統對功率消耗最為敏感的為被動式標籤，可透過兩種方式來提高其功率使用度。

- 提高 RFID 標籤能量轉換效率，提高後端電路能量可使用區間

- 盡量減少各子電路的電路消耗

- 提高天線與晶片間的阻抗匹配

由上述三種方式可以提高 RFID 標籤可使用功率的區間，其中提高天線與晶片間的組抗匹配並無在本篇論文討論，能量轉換效率將在第三章特別討論，也是本篇論文主要重點。最後將各部份子電路功率消耗整理成下表 2.10。

表 2.10 子電路功率消耗表

| <i>Part</i>                       | <i>Power consumption</i> |

|-----------------------------------|--------------------------|

| <i>Charge pump with reference</i> | 14.93uW                  |

| <i>Ring Oscillator</i>            | 1.1972m W                |

| <i>Power On reset</i>             | 270.52uW                 |

| <i>Demodulator</i>                | 8.9920uW                 |

| <i>All circuit</i>                | 1.49136mW                |

從上表 2.10 可以發現在整體的消耗耗功率主要消耗在環式振盪器，在這方面可以做到改進，由於配合中華大學為產生一個低頻振盪時脈源，所以多出了這 1.1972mW 的消耗，雖然可能可以藉由改變電路架構改從擷取載波頻率的方式來擷取出本篇論文所需的時脈源，但由於要從載波頻率 915MHz 要降到 2.56MHz 必須需  $915\text{MHz}/2.56\text{MHz}=357.42$  的除法器，相對之下會耗在除法器和各級除法器上的緩衝器(Buffer)的功率消耗更劇，所以如果待計畫中中華大學數位邏輯部份能夠成功晶片化能夠採取較工作時脈時，便能節

省在環式振盪器的功率消耗，對整體標籤前端電路而言，便能節省約七成功率消耗，另外在解調變電路中的緩衝器也可以透過減少波形的完整度，降低功率消耗，但這是電路間的 Trade off。

## 2.4 預計規格列表

透過以上子章節 2.1 至節 2.3 討論本篇論文主要提出的 RFID 標籤前端電路，將其架構內子電路的規格整理成下表 2.11

表 2.11 RFID 標籤前端電路規格表

|                              |                       |

|------------------------------|-----------------------|

| 直流輸出供應電壓                     | 可至倍壓 2.2V             |

| 功率消耗                         | Total 1.49136mW(1.8V) |

| 輸入 <i>PAD</i> 數              | 1                     |

| 輸出 <i>PAD</i> 數              | 10                    |

| 載波頻率                         | 915MHz                |

| <i>Operating Temperature</i> | 30°C                  |

| RF 輸入訊號區間                    | RF 輸入 power -4~7dBm   |

| 環式振盪器輸出頻率                    | TT 為 2.56MH(2dBm)     |

| 解調變電路                        | 可正確工作區間 -4~7dBm       |

| 穩壓電路輸出電壓                     | 850mV                 |

## 第三章

# 晶片量測與討論

此章節整理下線晶片量測結果，下線於國家晶片中心(CIC)使用 TSMC 0.18um 1P6M 製程，將實測結果與模擬結果作比較，並對量測結果做進一步討論提出此次下線量測與本篇論文第二章論點預期相同度，並針對此次下線晶片提出改進整理在第四章結論中討論，並在梯次 T18-96C 中 RFID 標籤整合型前端電路中改進。

### 3.1 915MHz RFID 標籤充電泵(Charge Pump)晶片量測

在此節，先將此梯次下線的 RFID 標籤前端電路在第 2 章的討論簡單重述，在依序將佈局圖、量測環境、量測結果、以及討論結果在此節列出。

#### 3.1.1 充電泵電路與穩壓電路架構(Charge pump)

此次下線 T18-95E No.142 RFID 標籤前端電路下線方塊圖如下圖 3.1 所示，主要包括了充電泵電路(Charge Pump)與穩壓電路(Voltage Reference)。

圖 3.1 RFID 標籤晶片前端電路方塊圖

如圖 3.1 所示此次下線為包括了充電泵電路與穩壓電路，而詳細電路架構已在第 2 章內討論，此處又將其納入如同下圖 3.2。

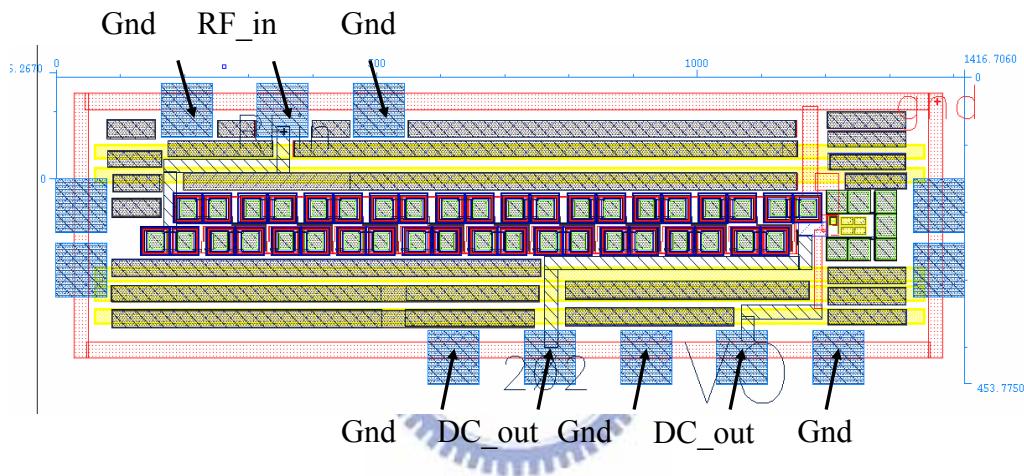

圖 3.2 charge pump with voltage reference

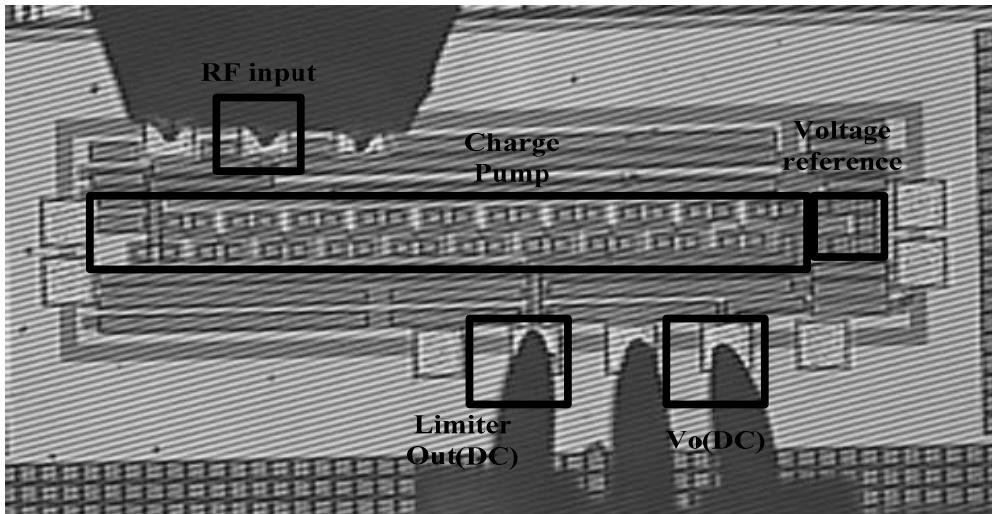

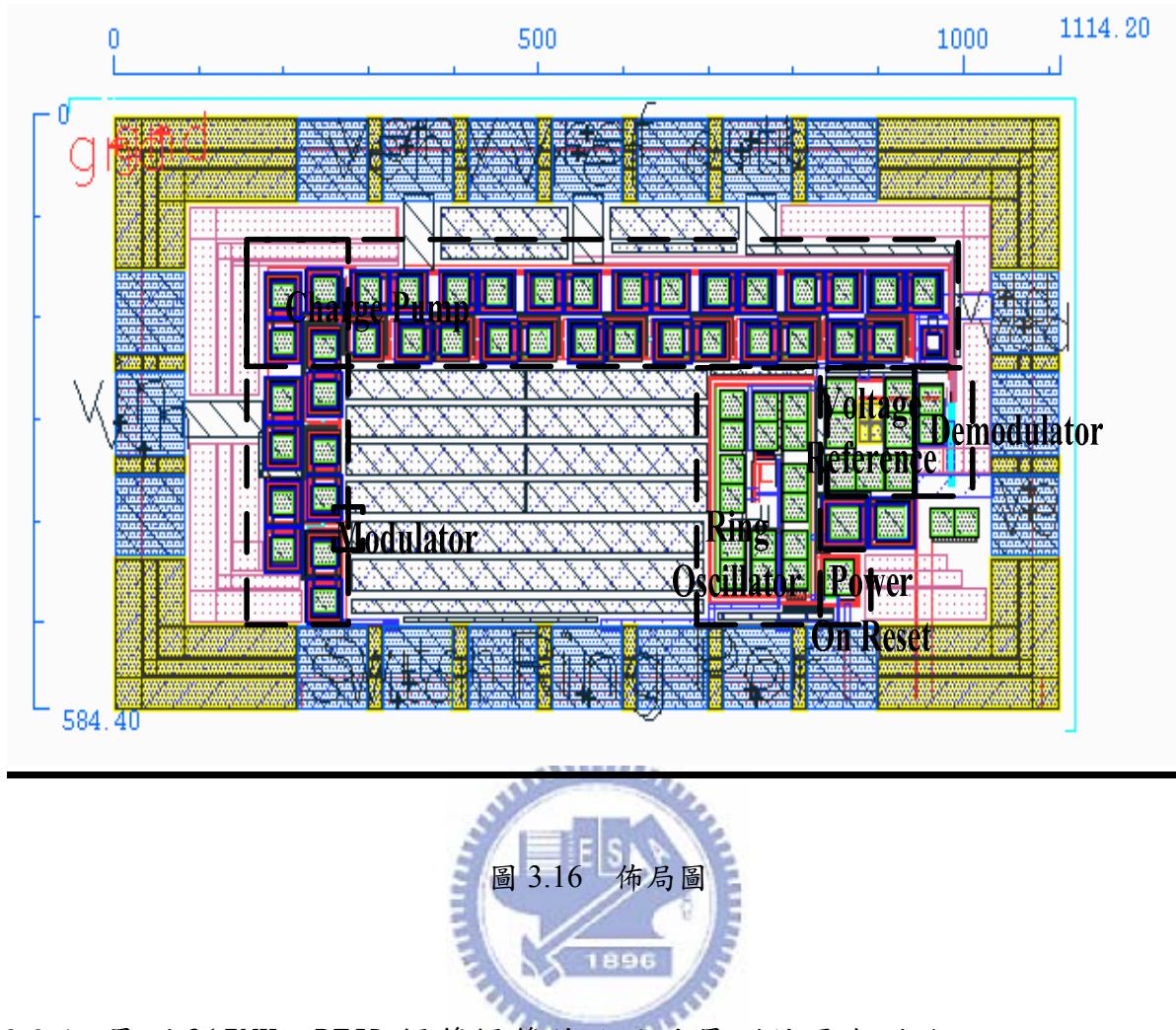

架構如上圖 3.2 所示，而此次梯次下線佈局圖如下圖 3.3 所示，整個下線晶片包括 PAD 的面積大小為 1416um\*453um，但由於其中因為必須符合

- TSMC 的 Design rule 放了許多空 Metal 以符合各金屬層面積比例限制

- 符合國家晶片中心 On Wafer probe 平台針腳距離必須限制於間隔 150um

所以真正電路面積只有 570um\*420um 遠比[7]中的小。另外如圖 3.3 所示包括了一個輸入 PAD 為灌入 RF Input Power 用，另外圖 3.3 佈局圖下方留了兩個 DC 輸出 PAD 分別為圖 3.2 中 Limiter Out(DC)以及 Vo(DC)。

圖 3.3 佈局圖

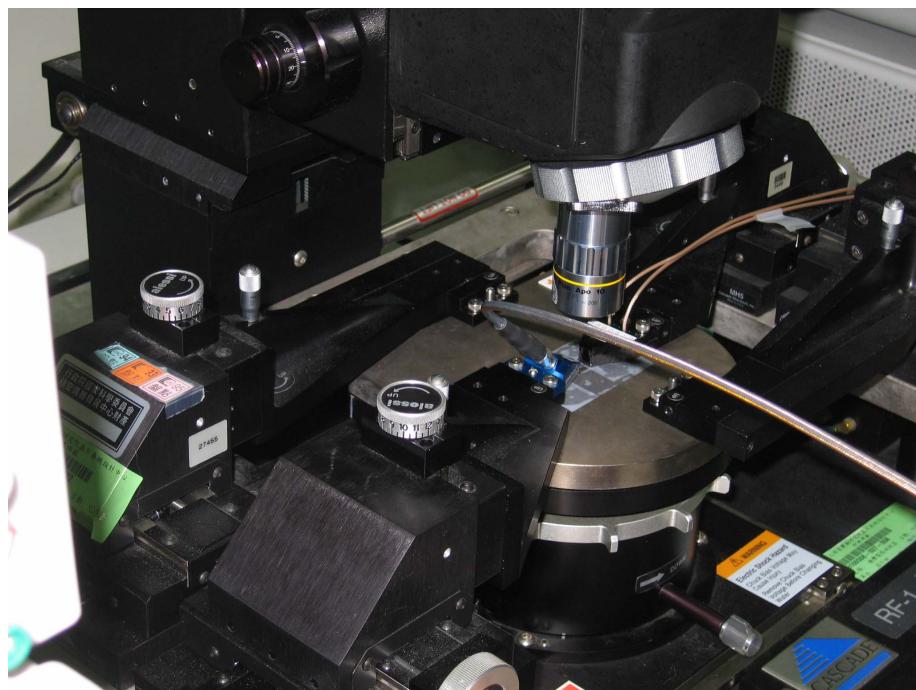

下圖 3.4 為下線晶片實際放在 On Wafer 平台的圖片，上方包括了 RF Input Power 所使用的 RF 針其中包括了 GSG(Ground Signal Ground)，而下方便是 Limiter Out(DC)與 Vo(DC)。

圖 3.4 實際晶片圖

### 3.1.2 量測環境

此節為介紹晶片量測環境與量測儀器，圖 3.5 為在國家晶片中心高頻實驗室的 On Wafer 平台。接著為在國家晶片中心實驗室使用的量測儀器，包括如圖 3.6 Agilent E8274C signal generator，其輸入 power 上限為 15dBm，此篇論文量測各 RFID 標準頻段 915MHz、2.4GHz、與 5.8GHz，其結果會在後面章節論述，其中環境中 cable loss 為 1.2375dB 但在 On Wafer 實測晶片約在 RF Input Power 達 13dBm 時，在限流電路已承受至 75uA 上限，之後灌入的大電流足以將晶片燒毀。另外圖 3.7 為了在作天線阻抗匹配，而量測晶片輸入阻抗所使用的 Agilent 8510C。其 RF Input Power 上限為 5dBm，所以量測時也以此為上限。

圖 3.5 On Wafer 平台

圖 3.6 Agilent Technologies E8247C Signal Generator

圖 3.7 Agilent Technologies 8510C

### 3.1.3 量測 915MHz RFID 標籤充電泵(Charge Pump)晶片量測結果與討論 (T18-95E-No. 142)

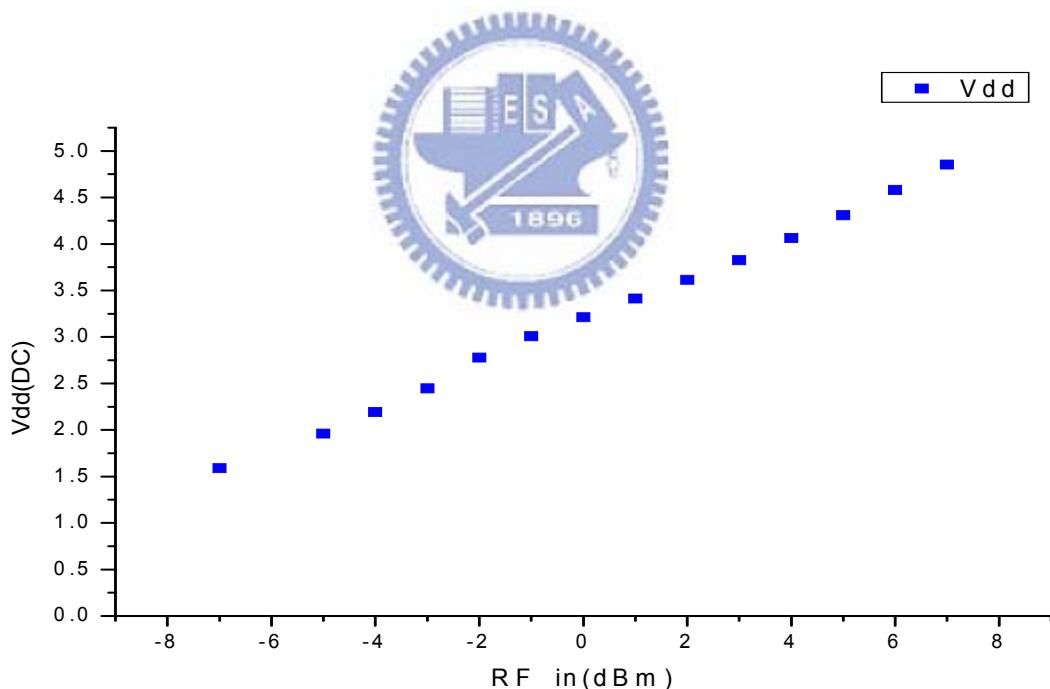

#### A. Limiter Out(DC)輸出量測

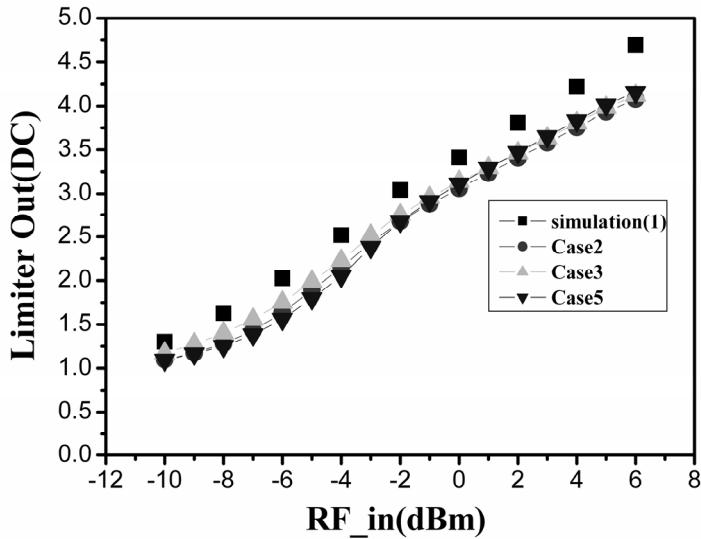

經由 3.1.1 以及 3.1.2 的基本環境介紹，下圖 3.8 為使用 Agilent Technologies E8247C Signal Generator 從 RF Input PAD 將 RF Input power 輸入，再利用 probe 量測晶片編號 2、編號 3、以及編號 5 的 Limiter Out(DC)，可以由圖 3.7 觀察出當 RF Input Power 逐步增加時，Limiter Out(DC)也會逐步增加，由於後端電路利用此電壓工作所以至少要保持 DC 輸出為 1.8V 以上，所以我們可從圖 3.8 觀察出當 RF Input Power 為-6dBm 以上 DC 輸出電壓都能保持在 1.8V 以上。另外從圖 3.8 看出晶片實際量測也與第二章所模擬的結果相

近，誤差可能因製程偏差造成模擬與量測的些微差距。

圖 3.8 Limiter Out (DC) versus RF input power

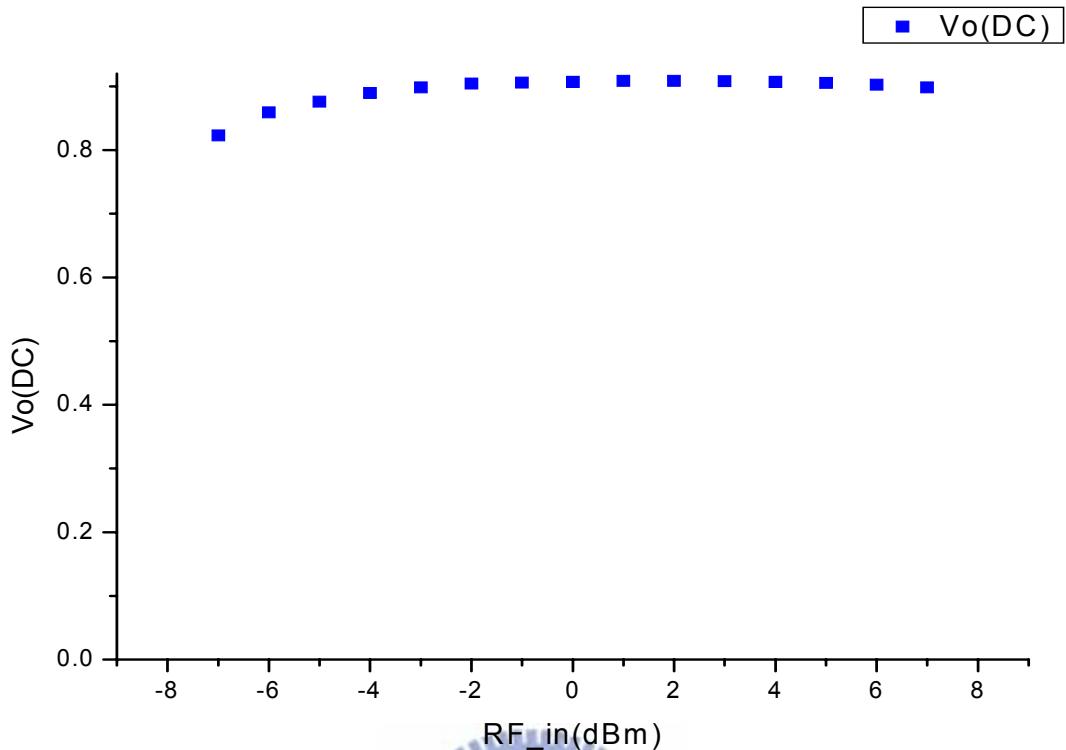

#### B. 穩壓電路 (Voltage Reference) DC 輸出 $V_o$ 量測

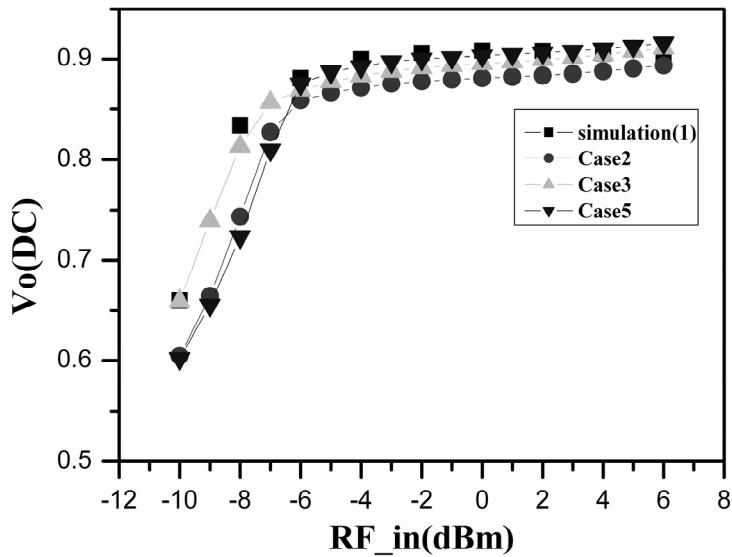

下圖 3.9 為使用 Agilent Technologies E8247C Signal Generator 從 RF Input PAD 將 RF Input power 輸入，再利用 probe 量測晶片編號 2、編號 3、以及編號 5 的  $V_o$ (DC)，可以由圖 3.9 觀察出當 RF Input Power 逐步增加時，穩壓電路有正確工作，將變動的 Limiter Out(DC)依預期般轉換成提供了穩定  $V_o$ ，足夠給予當做 T18-96C 解調變電路中的穩定偏壓源。然而我們可從圖 3.9 觀察出當 RF Input Power 為-6dBm 以上 DC 輸出電壓都能保持在 900mV 左右，能夠完全工作。另外從圖 3.9 看出晶片實際量測也與第二章所模擬的結果相近，誤差可能因製程偏差造成模擬與量測的些微差距。

圖 3.9  $V_o$  (DC) versus RF input power

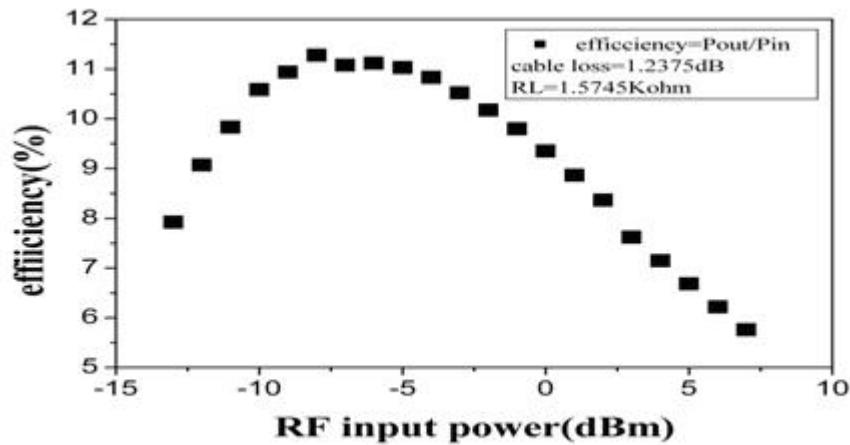

### C. 能量轉換效率 (Power Conversion Efficiency) 量測

本篇文章所使用的 Power Conversion Efficiency =  $P_{out}/P_{in}$ ，其中  $P_{out}$  便是量測  $V_o$  的 DC 輸出電壓與流經輸出電流所算出來的，而其中  $P_{in}$  便是 RF Input Power。利用此能量轉換關係式，在量測時依然使用 Agilent Technologies E8247C Signal Generator 將 RF Input Power 逐步提高，且量測時  $V_o$  輸出所掛的負載電阻為 1.5745K ohm，依此環境將晶片量測數據依能量轉換效率整理為下圖 3.10，可以發現在 RF Input Power 達到約 -7dBm 時能量轉換效率達到最高值，再往上增加 RF Input Power 的同時因為限流電路啟動導流掉部份電流因而造成能量轉換效率的下降。當其重載時可提供 DC 電流可提供至 570uA 較[7]所提供的 1.5uA 與 ATMEL ATA5590[20]有較大的後端電路設計空間，另外當  $V_o$  如果掛負載電阻至 1Mega 輕載電阻時，其能量轉換效率也可達 21% 也較[20]中所指的 ATMEL ATA5590 14% 為佳。

圖 3.10 重載情況下的能量轉換效率量測

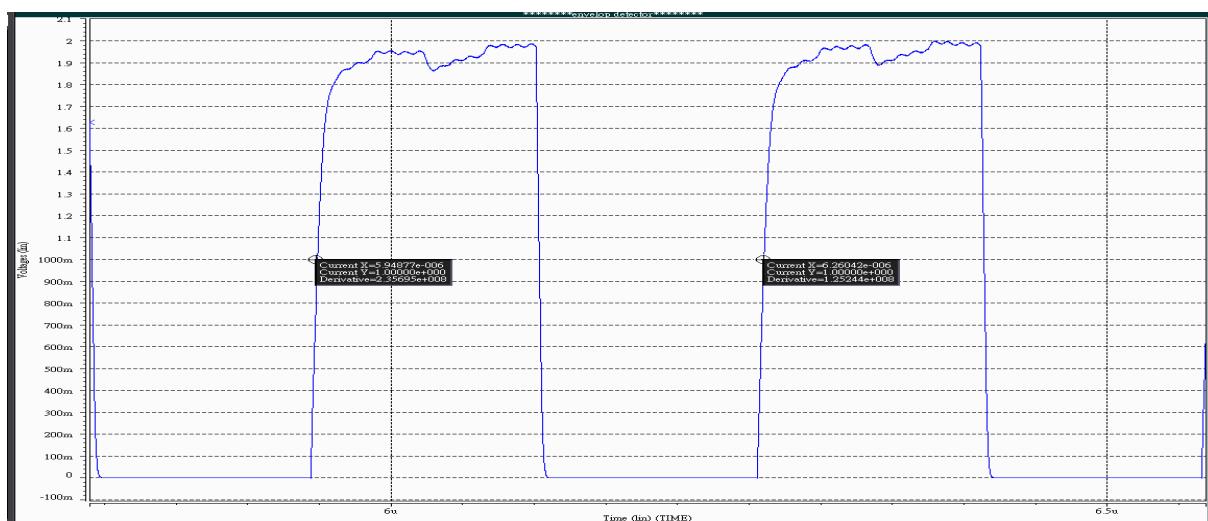

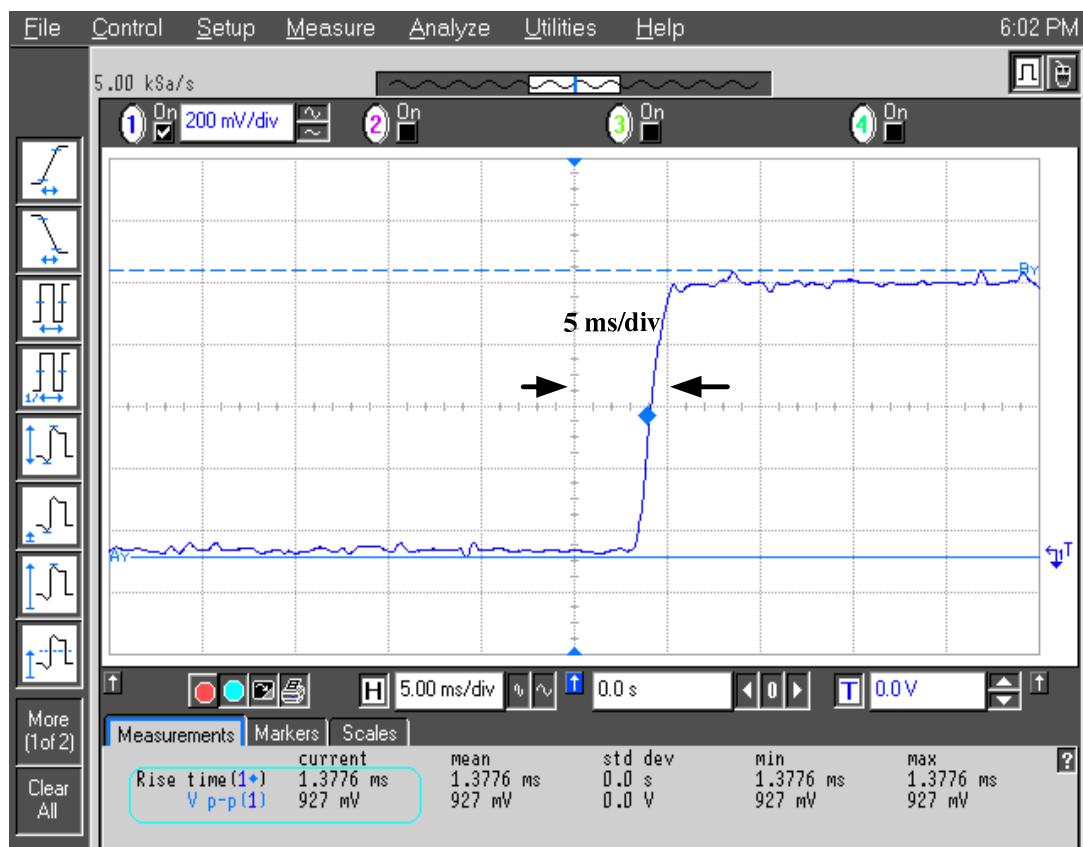

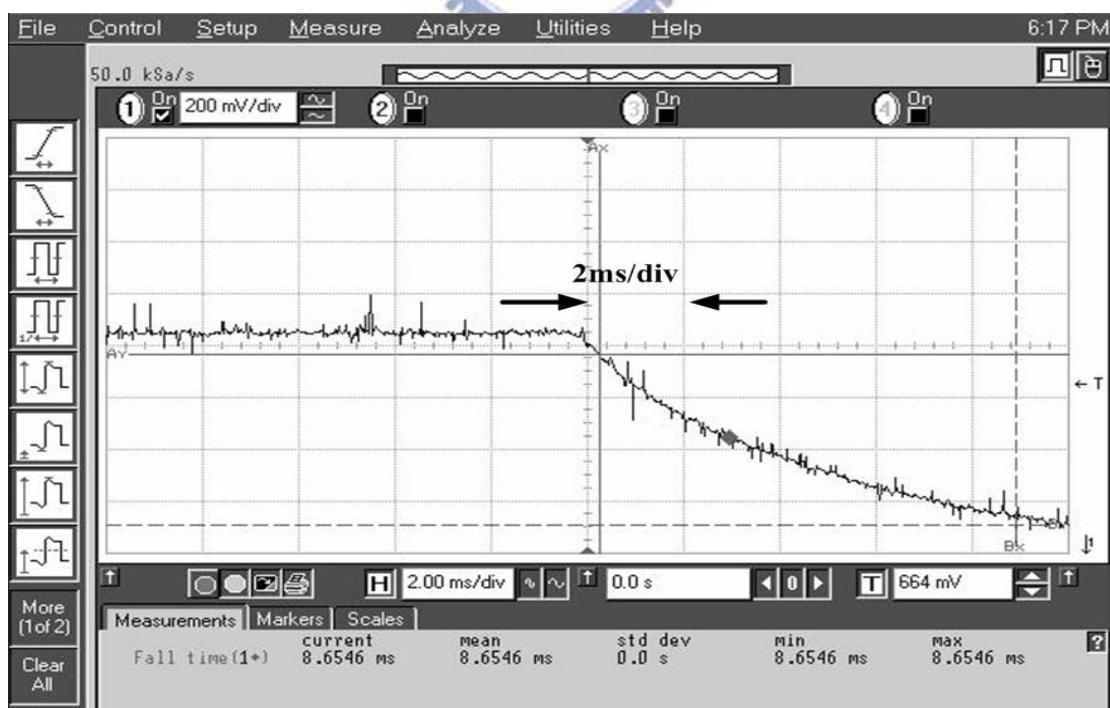

#### D. 上升時間 (Rising Time) 與下降時間 (Falling Time) 量測

對於 RFID 標籤而言，上升時間 (Rising Time) 與下降時間 (Falling Time) 是相當重要的，所以理想目標為上升時間能夠盡量短，而下降時間能夠盡量長，要盡量避免在傳遞的連續射頻載波消失後，標籤前端電路必須儲存足夠能量能將標籤內所攜帶的資料能在能量不足前將資料傳送完，以免訊息中斷。所以此節量測重點便在標籤前端電路的上升時間與下降時間。

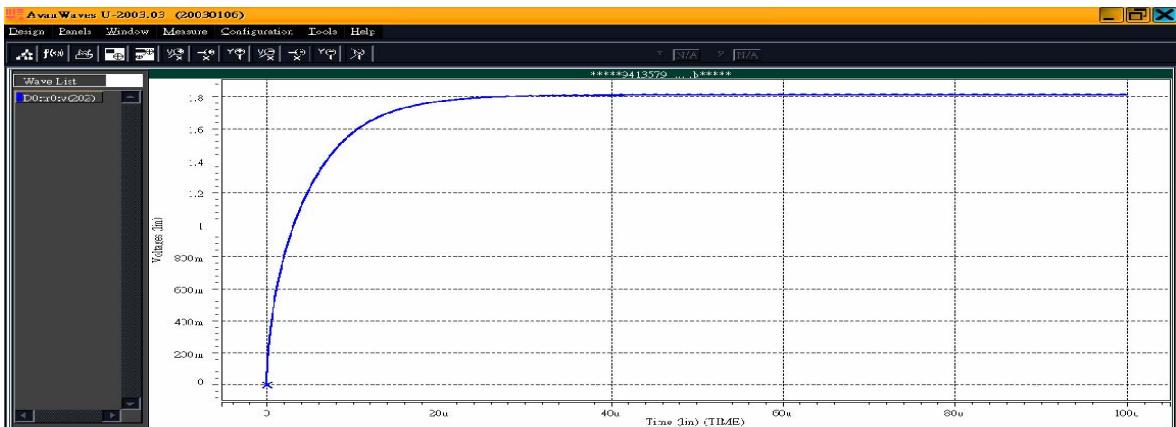

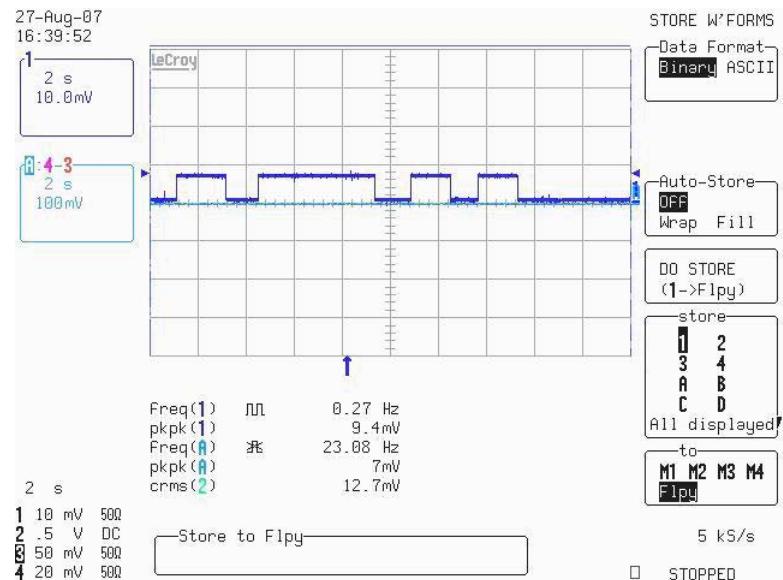

如圖 3.11 所示為量測標籤前端電路直流  $V_o$  上升時間為 1.3776ms，而圖 3.12 為量測標籤前端電路的下降時間可以清楚觀察到為 8.6546ms，此下降時間大於後端數位訊號處理端將 EPC global Class-1 Generation-2 EPC code 96bits 的資料用 256KHz 傳送完畢的時間 1.1ms。

圖 3.11 標籤前端電路輸出直流  $V_o$  上升時間圖 3.12 標籤前端電路輸出直流  $V_o$  下降時間

## E. 標籤前端電路在其他頻率量測

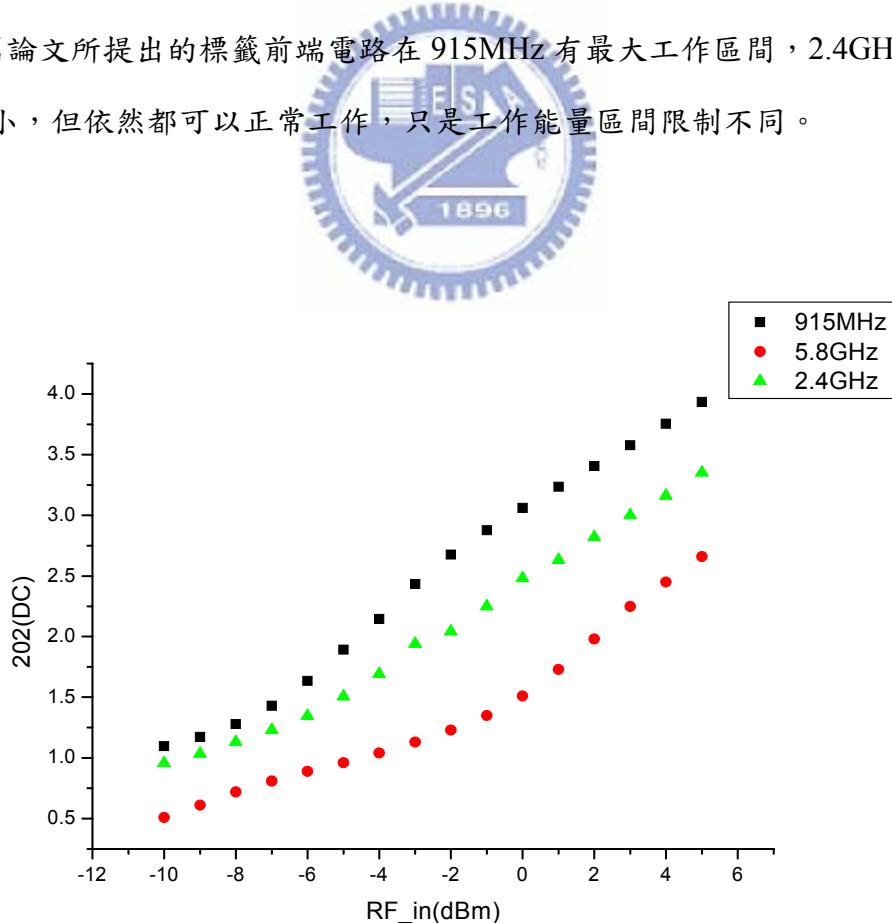

針對其他 RFID UHF 使用頻率 2.4GHz 以及 5.8GHz 也分別量測 Limiter Out(DC) , 量測時依然使用 Agilent Technologies E8247C Signal Generator 將 RF Input Power 逐步提高 , 將結果與 UHF 915MHz 結果一起整理於圖 3.13 , 可以從圖 3.13 可以觀察出 , 本篇論文所設計的 RFID 標籤前端電路使用在 915MHz 有最大工作區間 , 2.4GHz 次之 , 5.8GHz 最小 , 由於前端電路中的充電泵電路利用 RF Input Signal 正負半週充放電 , 所以當頻率越高時所能儲存在電容內能量越少 , 所以工作區間較小 。

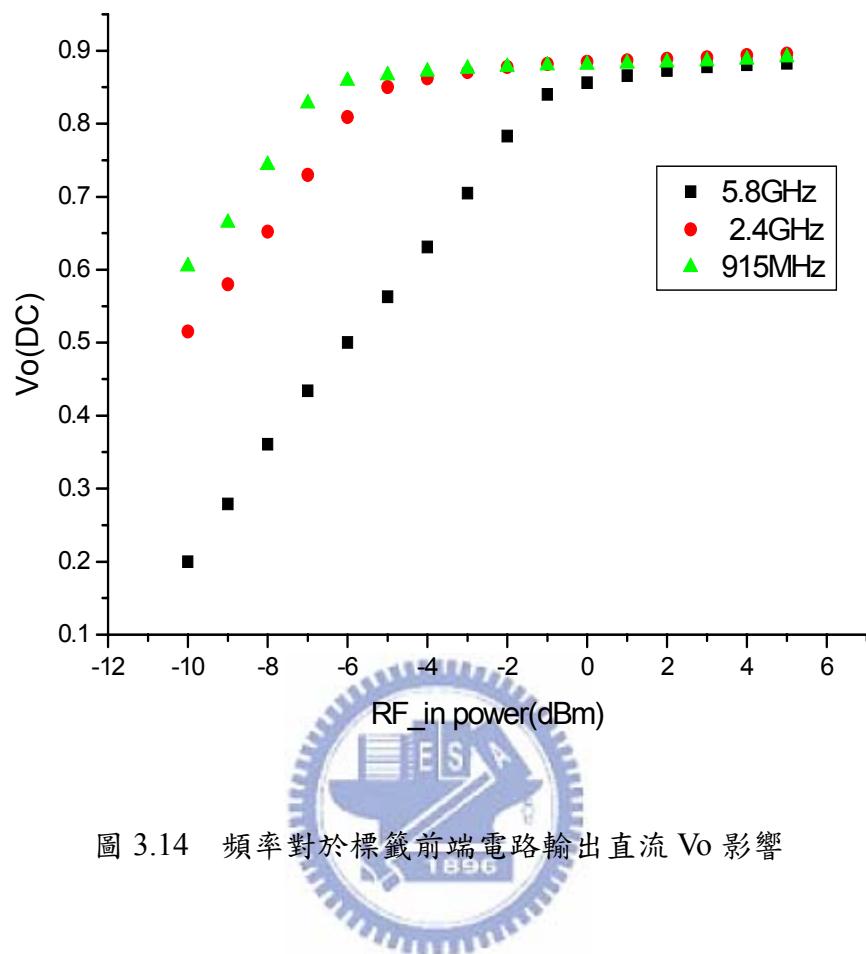

而圖 3.14 為量測本篇論文所設計的 RFID 標籤前端電路使用在 915MHz 、 2.4GHz 、以及 5.8GHz 時的 DC 輸出  $V_o$  變化 , 可以從圖 3.14 上觀察到為了維持 900mV 左右 , 使用 5.8GHz RF 輸入訊號時最小能量必須在 -1dBm 以上 , 而在 2.4GHz 情況下 , RF 訊號最小能量必須到達 -5dBm 以上 , 而在預設的設計目標下只需 -6dBm 的 RF 輸入訊號 , 所以可知本篇論文所提出的標籤前端電路在 915MHz 有最大工作區間 , 2.4GHz 次之 , 5.8GHz 最小 , 但依然都可以正常工作 , 只是工作能量區間限制不同 。

圖 3.13 頻率對於標籤前端電路 Limiter Out 影響

圖 3.14 頻率對於標籤前端電路輸出直流 Vo 影響

### 3.2 915MHz RFID 標籤前端電路晶片量測(T18-96C)

T18-96C 晶片下線如圖 3.15 所示主要分成四塊包括了充電泵(charge pump)，而充電泵主要包括了整流電路與限流電路(rectifier 和 limiter)以及穩壓(Voltage reference)電路、提供後端數位處理的啟動重置(Power On Reset)電路，解調變電路(Demodulator)以及環形震盪(Ring Oscillator)，以及調變電路(Modulator)

圖 3.15 RFID 標籤系統圖

### 3.2.1 量測 915MHz RFID 標籤前端晶片量測結果與討論

(T18-96C-No. 180)

本節將量測結果將依如圖 3.15 所示依序將解調電路(Demodulator)、環式振盪電路(Ring Oscillator)、以及調變電路(Modulator)依序介紹量測結果。

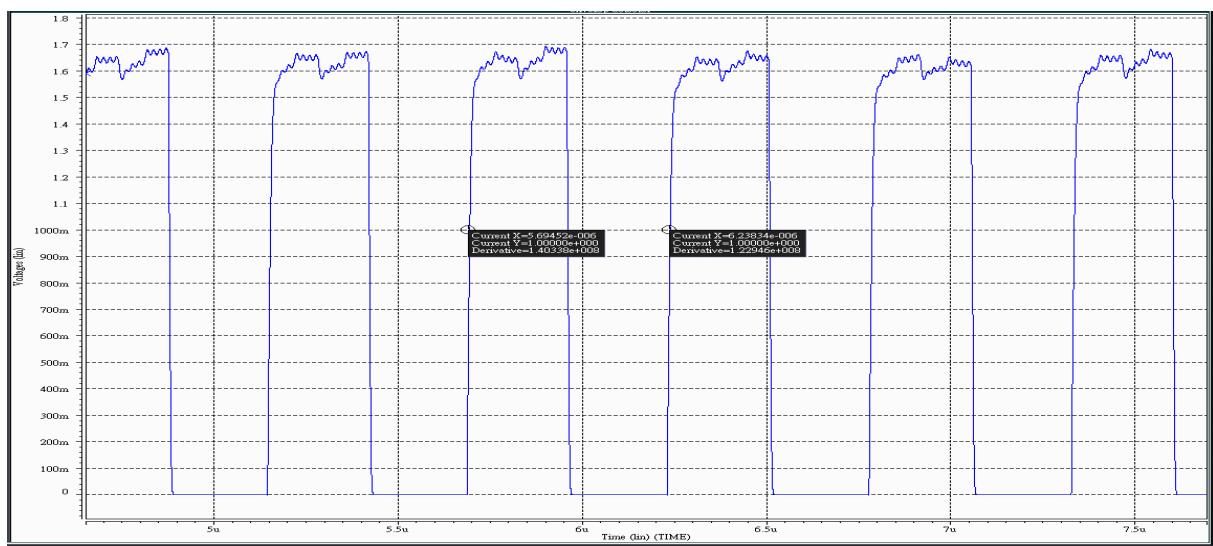

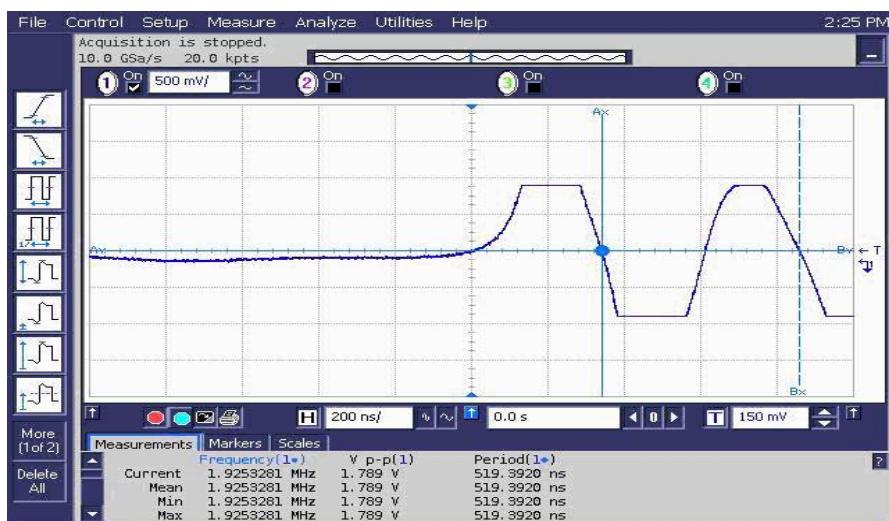

#### A. 解調變電路(Demodulator)輸出波形量測

圖 3.17 為解調變電路示波器量測結果，此為當 RF 轉 DC 產生 1.8V 工作電壓時，在 Signal generator 信號調至 ASK 100%，解調變電路的量測結果，可以從圖 3.17 中發現解調變電路工作正常，能成功將 ASK 100% 訊號調變訊號去掉 915MHz 載波，留下我們手動所加的低頻訊號，但由於其示波器 Loading 過大，造成輸出波形 High 僅達 10mV，但

經由三用電表所測到 high 為 1.8171V，而 Low 準位為 0.002V 遠較示波器的值為高。

圖 3.17 解調變電路示波器波形量測結果

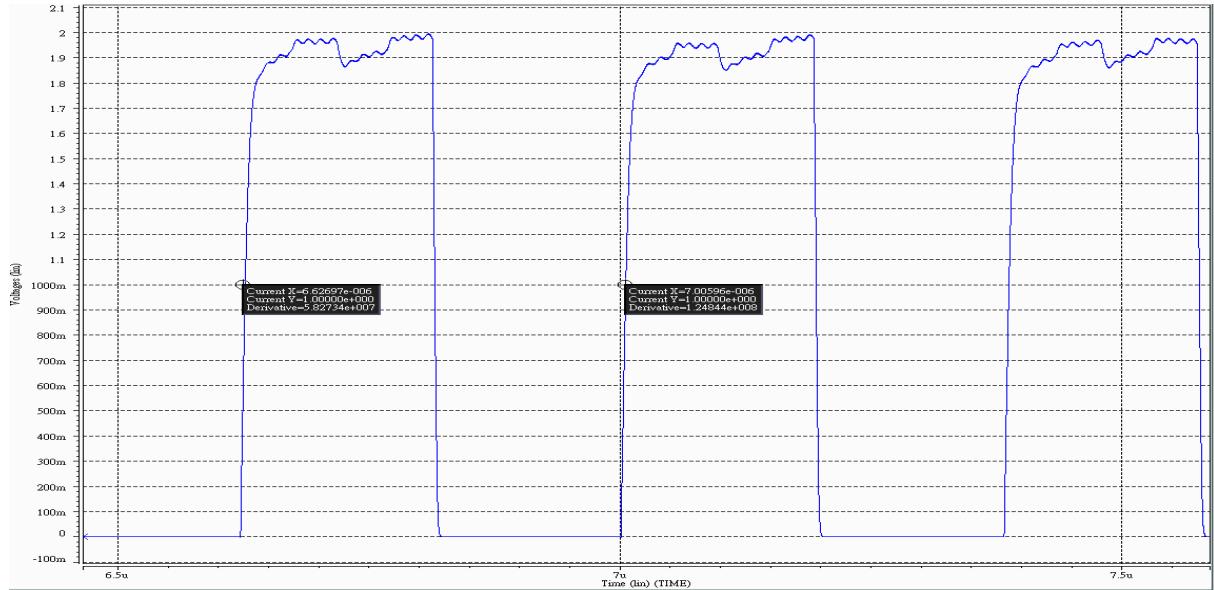

### B. 環式振盪電路(Ring Oscillator)輸出波形量測

圖 3.18 為當振盪器輸出波形圖，可以從圖 3.18 中觀察出其振盪震幅約為 1.8V 與 VDD 相同，而環式振盪器輸出頻率為 1.92538MHz

圖 3.18 環式振盪器輸出

## C. 調變電路(Modulator)輸入阻抗量測

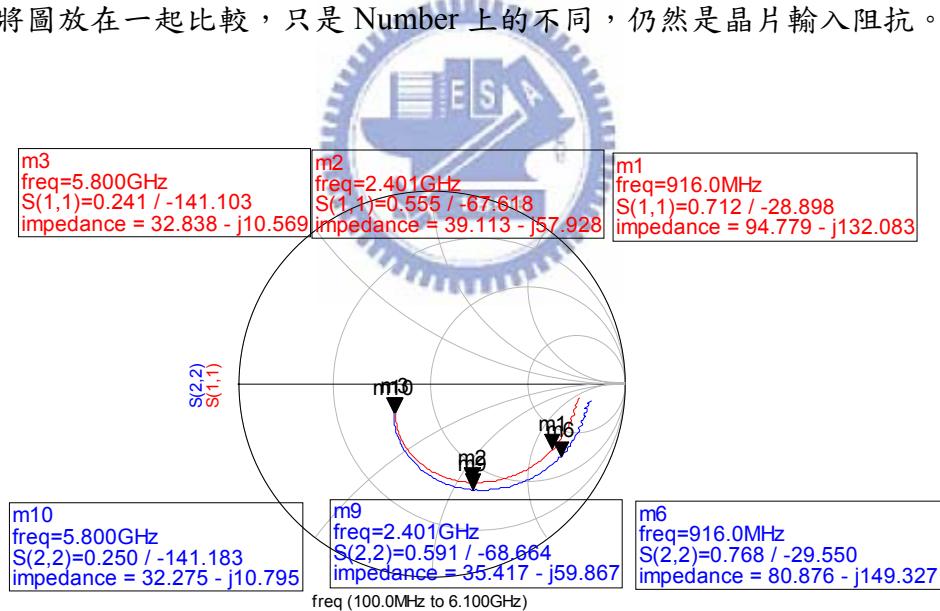

此節將調變電路所造成的輸入阻抗變化量測依序列出。量測結果將數位訊號輸入的高準位控制調變電路中的開關打開，以及低準位時調變電路中開關關上時，所造成輸入阻抗以 Smith Chart 方式呈現。

## a. RF 輸入訊號為-6dBm

下圖 3.19 為 RF Input Power 為-6dBm 時晶片的輸入阻抗，紅色線為調變電路接收數位電路高準位訊號，使開關打開時的輸入阻抗，而藍色線為調變電路接收到數位電路低準位訊號開關關上時的輸入阻抗，另外 Marker 分別為 RFID 系統中 916MHz 與 2.4GHz 以及 5.8GHz。可以從結果圖中可以發現在 915MHz 附近時有較大輸入阻抗分別，使讀取器端較容易從 ASK 訊號中辨別出數位訊號低準位與高準位。另外注意圖中 S(2,2) 乃是為了將圖放在一起比較，只是 Number 上的不同，仍然是晶片輸入阻抗。

圖 3.19 RF Input Power 為-6dBm 時輸入阻抗

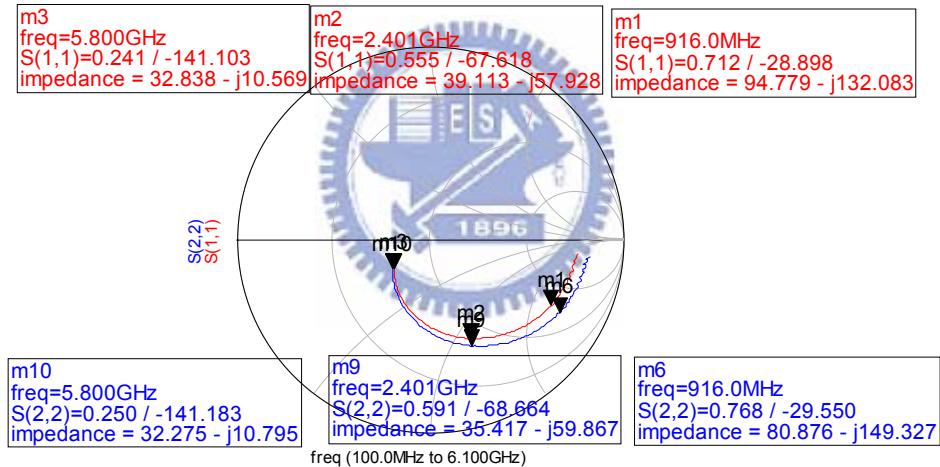

b. RF 輸入訊號為 0dBm

下圖 3.20 為 RF Input Power 為 0dBm 時晶片的輸入阻抗，紅色線為調變電路接收到數位電路高準位訊號，使開關打開時的輸入阻抗，而藍色線為調變電路接收到數位電路低準位訊號開關關上時的輸入阻抗，另外 Marker 分別為 RFID 系統中 916MHz 與 2.4GHz 以及 5.8GHz。可以從結果圖中可以發現在 915MHz 附近時有較大輸入阻抗分別，使讀取器端較容易從 ASK 訊號中辨別出數位訊號低準位與高準位。

另外注意圖中 S(2,2)乃是為了將圖放在一起比較，只是 Number 上的不同，仍然是晶片輸入阻抗。

圖 3.20 RF Input Power 為 0 dBm 時輸入阻抗

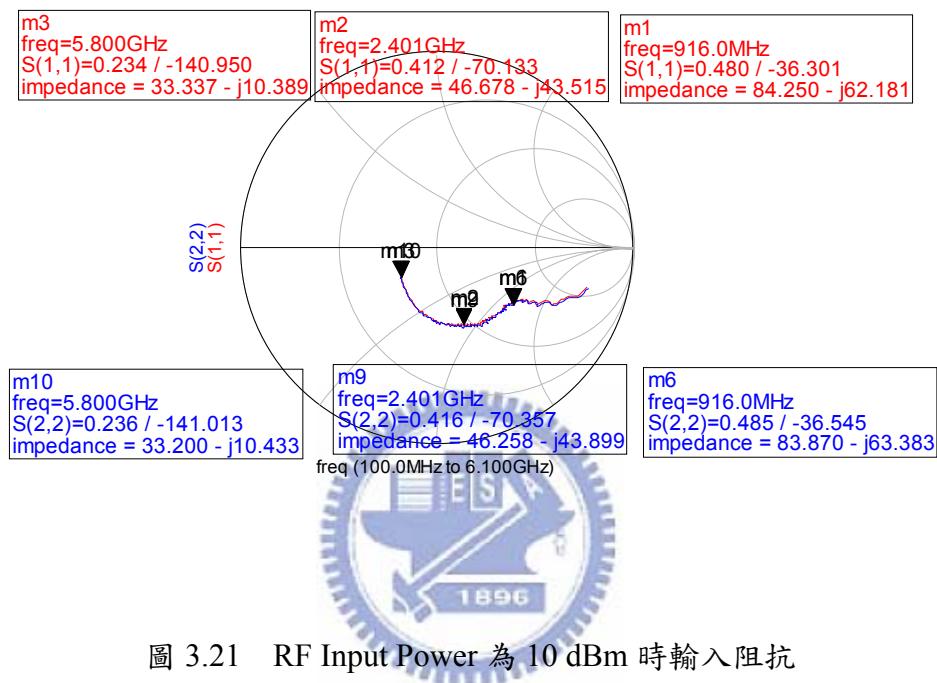

c. RF 輸入訊號為 10dBm

下圖 3.21 為 RF Input Power 為 0dBm 時晶片的輸入阻抗，紅色線為調變電路接收到數位電路高準位訊號，使開關打開時的輸入阻抗，而藍色線為調變電路接收到數位電路低準位訊號開關關上時的輸入阻抗，另外 Marker 分別為 RFID 系統中 916MHz 與 2.4GHz 以及 5.8GHz。可以從結果圖中可以發現在 915MHz 附近時有較大輸入阻抗分別，

使讀取器端較容易從 ASK 訊號中辨別出數位訊號低準位與高準位。

另外注意圖中 S(2,2)乃是為了將圖放在一起比較，只是 Number 上的不同，仍然是晶片輸入阻抗。

圖 3.21 RF Input Power 為 10 dBm 時輸入阻抗

## 第四章

### 結論

本篇論文利用 TSMC 1P6M 0.18um 製程實現 RFID 標籤前端電路。在標籤前端電路中成功整合了充電泵(charge pump)，而其中充電泵主要包括了整流電路與限流電路(rectifier 和 limiter)以及穩壓(Voltage reference)電路、提供後端數位處理的啟動重置(Power On Reset)電路，解調變電路(Demodulator)以及環形震盪(Ring Oscillator)，以及調變電路(Modulator)。

而在本篇論文研究中對於能量轉換方面特別專注，由於對 RFID 系統而言，RF 與 DC 功率間的轉換是極為重要的，因為在 RFID 讀卡機(Reader)與標籤(Tag)間的感應距離長度，取決於足夠能量能讓晶片正確工作，也就是當標籤使用能量越足夠時，標籤與讀卡機間正確感應距離便能延伸至更長，而在整個系統對功率消耗最為敏感的為被動式標籤，可透過以下三種方式來提高其功率使用度。

- 提高 RFID 標籤能量轉換效率，提高後端電路能量可使用區間

- 盡量減少各子電路的電路消耗

- 提高天線與晶片間的阻抗匹配

而在其中充電泵電路中的能量轉換效率的研究，本篇論文使用了 native NMOS 使 RF 訊號轉換成高 DC 輸出電壓位準，在十級的整流電路中提供倍壓比率到達 8.575，且其 DC 輸出也成功穩定在各種情況。另外和[9][15]相較，仍然有不錯的能量轉換效率，也提供了後端電路大電流供應，以及較小的晶片面積，另外也提供寬頻的使用，分別在載波頻率為 2.4GHz 以及 5.8GHz 標籤前端電路皆能正常工作。

在 On wafer 量測中由於與特徵阻抗 50 歐姆情況不匹配(Mismatch)的情況下，最小 RF 輸入功率約為-6dBm，但在實際情況下天線與標籤前端電路晶片輸入阻抗匹配的情況下，實測距離可達 4 公尺，模擬最小 RF 輸入能量也可以在匹配情況下可以跨大至-16dBm 左右。

未來進一步的工作包含有：

1. 在充電泵電路中 native NMOS 只提供 long channel model 如能，如能再進一步提供 short channel model，可將 DC 倍壓更進一步提高，或者依需求減少倍壓級數

2. 充電泵電路中整流電路 MOS diode 長寬比(aspect ratio)最佳化

3. 整體電路功率消耗太高，耗至 1.49136mW，但其中環式振盪器就佔了 1.1972mW，待中華大學數位訊號處理邏輯端積體電路化，便能改變電路架構，改變成 Clock extractor 方式將訊號源內的載波萃取出來當做本地震盪源。

## 附錄 A

### RFID 系統應用實例

#### A.1 系統發展實例與應用

依[24-32]根據市調公司 Data Monitor 的估計,2010 年全球零售業對於 RFID 技術(包括 Tag、Reader、Printer、Software、Services)的需求將突破 10 億美元,與 2006 年的 4.3 億美元相較呈現倍數成長。且看好 RFID 技術於零售業的發展,德國約有 40% 的業者於 2006 年底之前導入 RFID 系統,其市場成長潛力由此可見。根據 ASK 的預測,2005 年以後全球 RFID 技術的應用範疇將由「人」的辨識轉換到「物」的辨識,特別是零售業或供應鏈管理等領域將是市場發展重要趨勢。根據此一發展趨勢,若將 RFID 技術的應用範疇進一步的提升到流通服務業(涵蓋批發、零售、物流),其市場成長幅度更為可觀。根據 Marketstrat 的預測,2010 年全球 RFID 市場的規模將達 80 億美元,其中應用於流通服務之市場規模超過 31 億美元,約占全球 RFID 市場規模的四成左右,其市場規模為 RFID 各應用領域之冠,且 2005 年到 2010 年成長率將高達三成以上。RFID 產業結構大致可分為硬體、軟體及系統服務三大項,依據市場規模比重,目前軟體所占之市場規模較小,但未來在硬體價格快速下降的趨勢下,軟體服務所占的市場規模將逐漸擴大。根據 VDC 統計,2005 年全球 RFID 軟體市場規模僅有 2 億美元,估計 2008 年將快速成長至 7 億美元,年成長率達 51.6%,較整體 RFID 產業 35.3% 的成長率高出甚多。繼美國 Wal-Mart 之後,許多國際性大廠紛紛推動 RFID 技術的應用,其驗證範圍也從棧板(Pallet)或盒裝(Case)層次,提升到產品品項層次(Item Level),例如 METRO 及 TESCO 將 RFID 電子標籤貼附於 DVD 或 VCD、馬莎百貨將 RFID 電子標籤用於男女生套裝及襯衫、日本三越百貨將 RFID 電子標籤應用於鞋子及牛仔褲,另外包括 Gap、PARDA

及 LEVIS 等品牌業者，也將 RFID 電子標籤應用於店面管理，這些應用案例說明 RFID 應用已經由棧板或紙箱層次拓展至 Item Level 的應用。受到 IC 設計和晶體電路技術的改善，RFID 電子標籤的價格下滑幅度將更為明顯，在價格和功能兩大優勢下，包括 Wal-Mart 及 METRO 等零售業者亦開始評估轉換 EPC Gen2 標準的可行性。且在產品功能提升與採用成本下降的激勵下，相對的使用量也快速增加，根據 ABI 的研究資料顯示，2006 年全球 UHF(Ultra High Frequency)標籤的出貨量將大幅成長至 10.7 億個，較 2005 年的 2.7 億個成長了 3 倍，且 2006 到 2010 年市場需求量亦將以 98% 的年成長率快速成長。看好 RFID 將掀起供應鏈的革命，國際供應大廠都已開始卡位布局，例如 Philips、Sharp、Hitachi、TI、Toshiba、ST Micro-electronics、Infineon 等半導體廠商積極布局 RFID 相關晶片；Alien、Symbol、Intermec、Texas Instruments、ASK、Toppan 印刷等業者年產 RFID 電子標籤上看 20 億個；另外，像軟體業者的微軟、資料庫業者的甲骨文、資料倉儲業者 NCR、IT 業者的昇陽公司及飛利浦等也已成功進入 RFID 產業。而在非商用利用範圍[3]包括了，國際民航組織(ICAO)電子旅行文件(MRTD)標準，無線射頻系統生物辨識系統 臉部(face)為必要使用，指紋(fingerprint)，虹膜(iris)為選用生物辨識存放於 RFID 晶片所需容量:(基本資料+臉部=32k，基本資料+臉部+2 指指紋=64k，基本資料+臉部+2 指指紋+2 顆虹膜=128k)。另外 RFID 也應用在電子旅行文件的例子如 SmartGate 比對方式:持電子旅行文件:RFID 晶片內的生物特徵+現場擷取的生物特徵+後端資料庫儲存儲存生物特徵或持 MRP(Machine Readable Zone)護照:現場擷取的生物特徵+後端資料庫儲存的生物特徵。美軍伊拉克戰爭也大量使用 RFID 系統例如:RFID 智慧型晚帶，大量傷患管理，傷兵後送與轉送管理，緊急狀況人員管理等。類似的方向 RFID 應用於的醫療應用案例如

美國哈佛大學醫學院附設醫院 RFID 行動醫療車(病人管理，HIS 資訊，自動驗證，自動記錄)，和 RFID Smart OR table(病人身分，輸血管理，手術內容，自動驗證)等。

而在學界中的發展如麻省理工學院的 Auto ID 中心所提出的 EPC(Electronic Product Code)，用意在規範 PML(Product Markup Language)敘述語言，使從 RFID 標籤所讀出之資料，流經網路到中心有統一的 EPC 碼，使各業界有遵循的標準，並在 2002 年

秋公布1.0 版。其發起稱為「Auto-ID Center」的研究計劃，參加的業者包括美國國防部、嬌生、百事可樂、吉利、UPS、大日本印刷、永豐餘造紙，可口可樂、Tesco、Wal-Mart Store、Pfizer 等全球各國知名企業，以及條碼管理組織美國的UCC(Uniform Code Council, Inc.)、歐洲的EAN International等。該計劃的最終目的是每個產品都配有RFID標籤，可以透過「自動讀取」的動作，而能和網路連結，使工廠的工程管理、流通、消費者服務到回收都能獲得最有效率的管理。現已完成RFID 標籤96 位元的ID 碼，稱為EPC(Electronic Product Code)。到2003 年止，英國劍橋、澳洲、瑞士、日本、上海復旦多所大學先後加入Auto-ID Center 研究中心，遍佈四大洲超過100 家的公司給予支持。

在業界如日立所完成的稱為「 $\mu$ -Chip」的晶粒大小只有  $0.4\text{mm} \times 0.4\text{mm} \times 0.06\text{mm}$ ，幾乎接近粉末，在1 片8 吋晶圓上，可以生產高達數十萬顆的晶粒，配合  $3\text{mm} \times 60\text{mm}$  的天線，可以讀取 20~30 公分距離的資料。該公司宣稱整個搭配起來，約數十美分。Motorola 專為 RFID 標籤開發的晶片，稱為 Bistatix，利用以印刷方式形成的天線，可以直接印製在紙張、紙箱上，每個約 30 美分，而美國的 Alien Technology 所開發的晶粒，比日立的「 $\mu$ - Chip」還要小，對角線長度只有  $0.1\text{mm} \sim 0.2\text{mm}$ ，一片8 吋晶圓可做 20 萬顆晶粒，可外附  $30\text{mm} \times 100\text{mm}$  的天線，用於 915MHz(美國用)、868MHz(歐洲用)和 2.45GHz(日本用)三種頻段，傳輸距離可達 5 公尺，並配合晶粒的縮小，天線和晶粒組裝的自動化，方有機會抑制成本至十美分以下。

由於現今主要的製造方式和材料都是沿襲傳統半導體技術，成本欲降低至貼近條碼，幾乎不可能完成，其一替代方式為利用有機電晶體技術，將有機半導體材料製造成溶媒，以近似印表機的噴墨方式噴出，在微細的面積上形成源極和汲極。此一方式和條碼一樣，近似印刷的技術能有效地降低成本。目前全球已有多家公司進行這種半導體的研究和開發計劃，IBM、Lucent 和 Philips 都是當中的代表。而 Motorola 開發出一近似墨水般的天線，可以形同條碼一樣，直接印在紙張、包裝盒等上面。美國也有中小企業投入 RFID 的開發，如 Intermec。而 2005 年美國那斯達克的上市公司 Symbol 用 2.3 億美金併購 Matrics(RFID 標籤製造供應商) ，而目前 RFID Tag 和解決方案供應商以 Philips、TI (AIM Global )、Temic、Microchip 和 Motorola 為其領導廠商。

## A.2 台灣 RFID 應用計畫

- 92 年 SARS 示範性醫院：

新竹東元綜合醫院、彰化秀傳醫院、台北醫學大學附設醫院、和信治癌中心醫院。

- 93 年宏碁 EPC ONS 網路平台示範性計畫。

- 93 年產業物流發展暨國際接軌推動計畫：

長榮空運倉儲、弘煒電子、台灣絲路數碼、中保物流、功學社、中華僑泰物流、泰舜捷盟行銷、萬達國際、台灣双葉電子。

- 93~94 年醫院導入 RFID：

高雄榮總、基隆長庚醫院、三軍總醫院、萬芳醫院、恩主公醫院。

- 94 年產業物流發展暨國際接軌推動計畫

RFID 實證評估測試輔導(P2)：裕唐汽車、美德向邦、車麗屋、遠榮氣體工業

RFID 先導運作系統輔導(P3)：陽明海運、龍笛實業、新竹貨運、捷盟行銷、精技電腦、萬達國際。

產業示範性 Logistic/Business Hub 輔導：裕隆汽車、台灣双葉電

## 附錄 B

### 調變電路討論

依據本論文利用 Backscattering 的方式[21]將輸入的波利用開關(Switch)調變的方式，將標籤資料的訊號載在原輸入載波上完成調變波，再回傳給讀卡機將標籤傳回之調變波解調回來，取出標籤上所要回傳的資料。在附錄 B 內討論標籤的調變機制

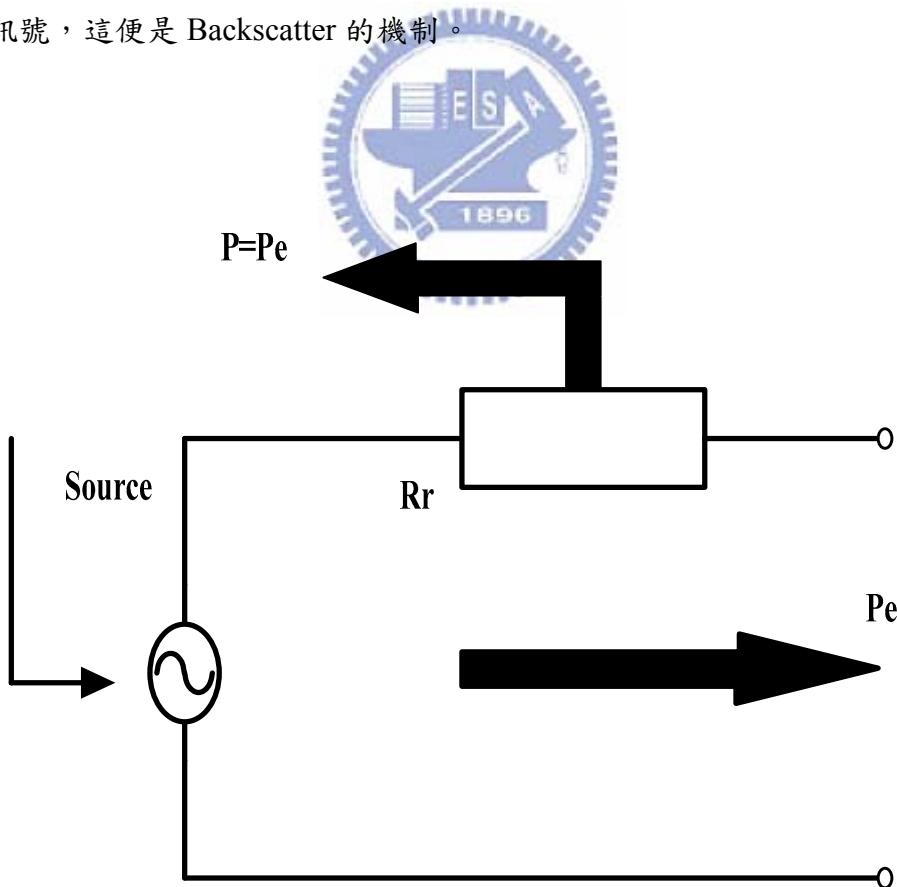

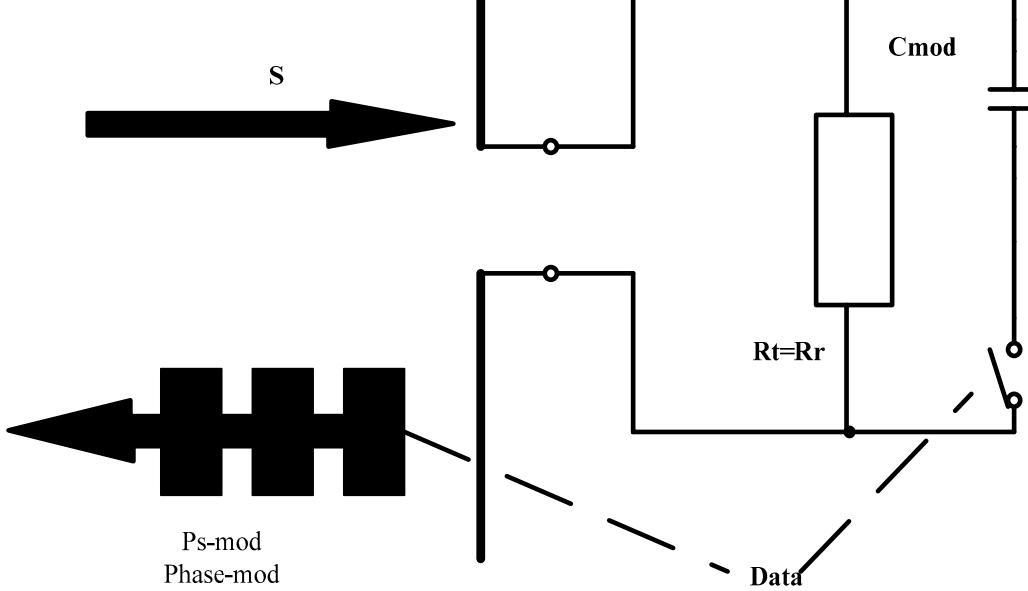

首先為標籤輸入端的天線電路模型如圖 B.1 所示當讀卡機端發射連續波，標籤接收其射頻波當作標籤的 source 而能量為  $P_e$ ，而在理想情況下內電路不消耗能量情況下，天線  $R_r$  會再將能量  $P_e$  完整送回讀卡機端，利用原讀卡機發射的 RF 訊號，標籤反射回去這 RF 訊號，這便是 Backscatter 的機制。

圖 B.1 天線等效電路

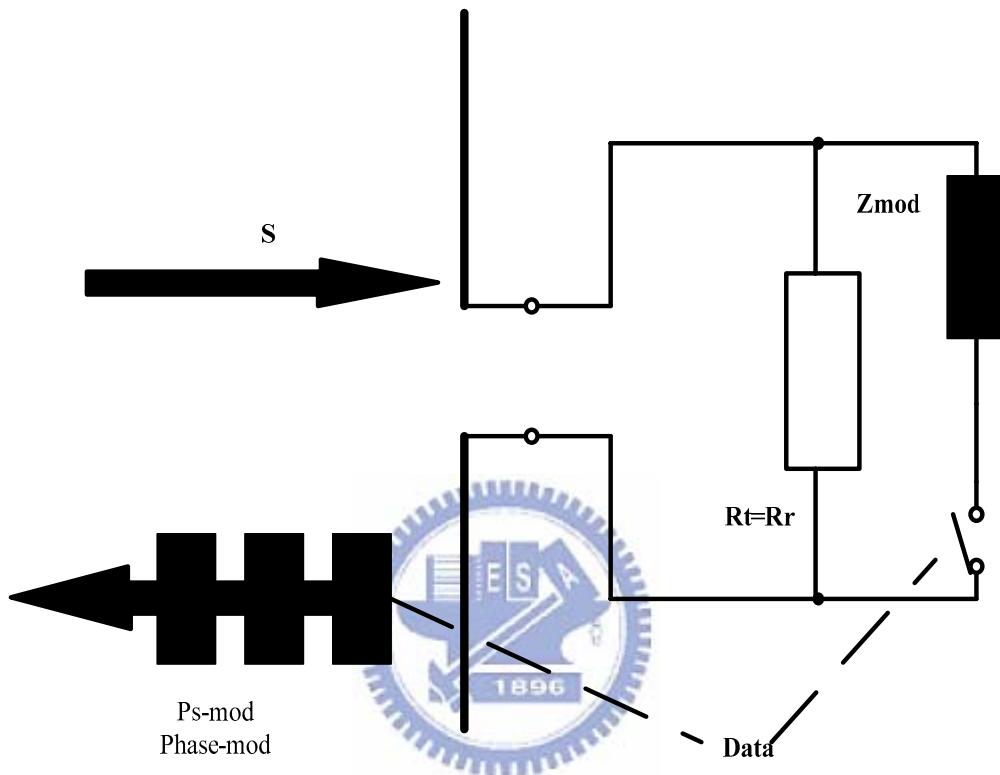

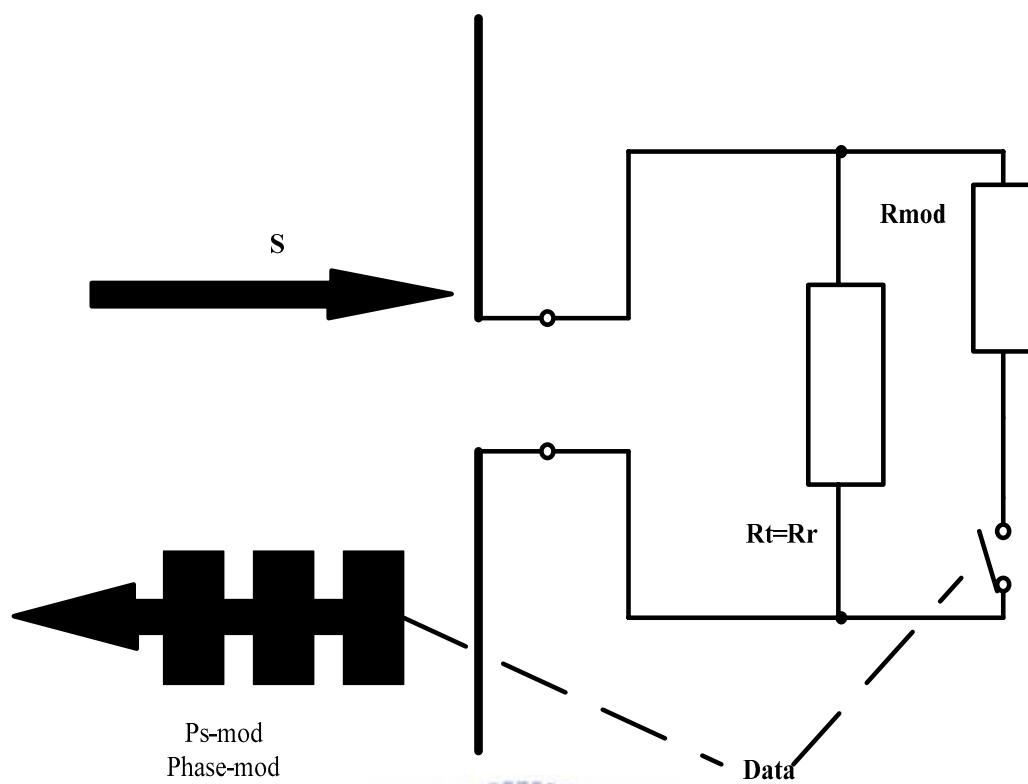

圖 B.2 為本篇論文所使用的調變機制利用數位訊號來控制開關，來控制 Zmod 是否有跨在天線的兩端，來達到傳送 Data 的目的，而圖 C.2 中  $R_t=R_r$  為晶片輸入阻抗與天線阻抗達到匹配，讓 Source Power  $P_s$  能夠完全進入標籤內。

圖 B.2 利用 Switch 所調變 modulated backscatter model

圖 B.3 與 B.4 為本篇論文所始用的調變電路的等效電路圖，在本文第二章曾提及調變電路主要架構為一顆開關 Switch，而本篇文章所使用的 Switch 為一顆 NMOS，但 NMOS 所產生的寄生電容( $C_{mod}$ )與內阻( $R_{mod}$ )分別如 B.3 與 B.4 所示。但  $R_{mod}$  造成了  $P_s$  振幅上的調變(ASK)， $C_{mod}$  而造成了相位上的調變 phase-mod(PSK)，所以當 Switch 開啟時 Backscatter 在反射波時造成了振幅與相位的差別，便包含了 ASK 與 PSK 兩種調變機制。

圖 B.3 利用 Switch 所調變的實部調變(real modulation)

圖 B.4 利用 Switch 所調變的電容調變(Capacitive modulation)

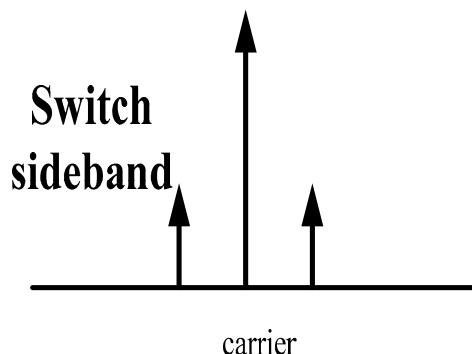

由於本篇論文在調變電路採取了 Switch 方式所以當原本 RF 弦波訊號加上了 Switch 的方波調變訊號下，透過 Fourier transform 可知會造成，DSB(Double side band)的效應如下圖 B.5 所示，在頻譜上載波頻率旁會有兩個標籤資料訊號所產生的 Side Band，也會造成輸入 RF 訊號的 Pe 會被分給載波與兩個 Side Band 上。

圖 B.5 Switch 所造成的 DSB 效應

## 參考文獻

- [1] 許博景,“RFID 實驗室建置”,APAS 先進排程國際股份有限公司,2006

- [2] 陳美玲,“RFID 將掀供應鏈革命”,經濟日報,2007

- [3] “RFID 與 TPMS 訊號的原理與量測”,太克 2007 春季電子展暨亞洲區巡迴研討會,2007

- [4] 李建斌,“RFID 技術現況與應用新趨勢”,Agilent RFID 技術應用研討會,2006

- [5] P. Adamcova and Z. Tobes, “UHF RFID Technology and its Applications,” Radioelektronika, 2007. 17<sup>th</sup> International conference, No.24-25, pp. 1-5, 2007

- [6] U. Karthaus and M. Fischer, “Fully Integrated Passive UHF RFID Transponder IC With 16.7- $\mu$ W Minimum RF Input Power,” IEEE Journal of Solid-State Circuits, Vol.38, No.10, pp. 1602-1608, Oct. 2003.

- [7] Y. Yao, Y. SHi, and F. Dai. Foster, “A novel Low-power Input-Independent MOS AC/DC Charge Pump,” IEEE Trans. Electron, vol.e86-c, no.4, pp.521-527, April 2003.

- [8] Tam, K.-S , and ERIC Bloodworth, “Automated topological generation and analysis of voltage multiplier circuits,” IEEE Trans. On Circuits and Systems Vol. 37, No. 3, Page(s):432 – 436, March 1990

- [9] J. Curty, N. Joehl, F. Krummenacher, C. Dehollain, and M. Declercq, ”A Model for u-Power Rectifier Analysis and Design,” IEEE TRANSACTION ON CIRCUITS AND SYSTEMS,” Vo. 52, No. 12,2005

- [10] H. San, H. Kobayashi, T. Myono, T. Iijima, and N. Kuroiwa, "High-Efficient Low-Voltage-Operation Charge Pump Circuits Using Bootstrapped Gate Transfer Switches," T. IEE Japan, Vol. 120-C, No.10, 2000

- [11] H. Jianyun , H. Yan, and M. Hao,”Design and Analysis of Analog Front-End of

- Passive RFID Transponders,” CHINESE JOURNAL OF SEMICONDUCTORS, Vo. 27, No. 6, 2006

- [12] U. Kaiser and W. Steinhagen, “A Low-Power Transponder IC for High-Performance Identification Systems,” IEEE JOURNAL OF SOLID-STATE CIRCUITS, Vo. 30, No. 3, 1995

- [13] 何菁嵐, 李強, 韓益鋒, 閔昊, “一種活用於 RFID 系統的低功耗檢波器設計和實現”

復旦學報, Vo. 45, No. 1, 2006

- [14] [http://lwca.org/library/regs/Part15\\_20040108.pdf](http://lwca.org/library/regs/Part15_20040108.pdf)

- [15] J. S. Brugler, “Theoretical Performance of Voltage Multiplier Circuits,” IEEE Journal of Solid-State Circuits, pp.132-135, Jun.1971.

- [16] Pierre Favrat, Philippe Deval, and Michel J. Declercq, “A High-Efficiency CMOS Voltage Doubler”, IEEE Journal of Solid-State Circuits, pp.410-416, March. 1998

- [17] B. Razavi, “Design of analog CMOS integrated circuits,” chap2, McGraw-Hill, 2001.

- [18] P. V. Nikitin, Member, IEEE, K. V. S. Rao, Senior Member, IEEE, S. F. Lam, V. Pillai, Member, IEEE, Rene Martinez, and H. Heinrich, “Power Reflection Coefficient Analysis for Complex Impedances in RFID Tag Design,” IEEE TRANSACTIONS ON MICROWAVE THEORY AND TECHNIQUES, vol. 53, no. 9, pp. 2721-2725, September 2005.

- [19] D. Neamen, “Semiconductor Physics and Devices: Basic Principles,” chap11, 3<sup>rd</sup>, McGraw-Hill, 1992

- [20] [http://www.atmel.com/dyn/resources/prod\\_documents/doc4817.pdf](http://www.atmel.com/dyn/resources/prod_documents/doc4817.pdf).

- [21] K. Finkenzeller, RFID Handbook, Radio-Frequency Identifications Fundamentals and Applications, 2nd ed. New York: Wiley, 2003.

- [22] P. M. Lin and L. O. Chua, “Topological Generation and Analysis of Voltage Multiplier Circuits,” IEEE Trans. on Circuits and Systems, Vol. CAS-24, No.10, pp.517-530, Oct. 1977.

- [23] P. Favrat, P. Deval, and M. J. Declercq, "A High-Efficiency CMOS Voltage Doubler," *IEEE Journal of Solid-State Circuits*, pp.410-416, March. 1998

- [24] J. Gavan, "TRANSPONDERS FOR THE DETECTION AND IDENTIFICATION OF REMOTE COOPERATIVE TARGETS," Center for Technological Education Holon, P.O.B. 305, Holon 58102, Israel.

- [25] AIM (Automatic Identification Manufacturers), the trade association for the Automatic Identification and Data Collection (AIDC) industry, Getting Started in RFID - A Step approach, 2003, [http://www.aimglobal.org/technologies/rfid/resources/papers/rfid\\_basics\\_primer.htm](http://www.aimglobal.org/technologies/rfid/resources/papers/rfid_basics_primer.htm)

- [26] RF Code, Inc., <http://rfcode.com/ProductsFrame.asp>.

- [27] The MIT Auto-ID Center. <http://www.autoidcenter.org/>.

- [28] K. V. Rao, "An overview of backscattered radio frequency identification system (RFID)," *Microwave Conference, 1999 Asia Pacific*, Vol. 3, pp. 746-749, 1999.

- [29] D. Schell, "Why Aren't More VARs Selling RFID?" *Business Solutions*, July 2001.

- [30] S. Sarma, K. Ashton, and D. Brock, "The Networked Physical World," *MIT-AUTOID WH-001*, MIT, Cambridge, Mass., 1999.

- [31] S. Sarma, D. Brock, Daniel Engels, MIT Auto-ID Center, "RADIO FREQUENCY IDENTIFICATION AND THE ELECTRONIC PRODUCT CODE," *IEEE MICRO*, NOVEMBER-DECEMBER 2001.

- [32] S. Sarma and D. W. Engels, "On the Future of RFID Tags and Protocols," *MIT-AUTOID-TR-018*, MIT, Cambridge, Mass., 2003.

- [33] J. Curty, N. Joehl, C. Dehollain, and M. J. Declercq, "Remotely Powered Addressable UHF RFID Integrated System," *IEEE JOURNAL OF SOLID-STATE CIRCUITS*, Vo. 40, No. 11, 2005

# 簡歷

姓 名： 劉嘉川

居住地： 台北市

出生日期： 民國七十年十月二十九日

學 經 歷：

交通大學電機與控制工程學系 輔系土木工程學系(88年9月~94年6月)

交通大學電信工程學系碩士班 (94年9月~96年7月)