# 國立交通大學電信工程學系碩士班

操作於弱反轉層場效電晶體之極低功率損耗與 極小面積 CMOS 參考電壓之設計與實現 The Design and Implementation of an Ultra Low Power and Small Area CMOS Voltage Reference Based on MOSFET Operated in Weak Inversion Region

# 研究生:林信太指導教授:闕河鳴博士

西元二〇〇七年十月

操作於弱反轉層場效電晶體之極低功率損耗與極小面積 CMOS 参考電壓之設計與實現 The Design and Implementation of an Ultra Low Power and Small Area CMOS Voltage Reference Based on MOSFET Operated in Weak Inversion Region

研究生:林信太

Student: Shin-Ta Lin

指導教授:闕河鳴 博士

Advisor: Dr. Herming Chiueh

#### 國立交通大學

電信工程學系碩士班

碩士論文

A Thesis

Submitted to Department of Communication Engineering College of Electrical Engineering and Computer Science National Chiao Tung University In Partial Fulfillment of the Requirements For the Degree of Master of Science in

Communication Engineering

October 2007

Hsinchu Taiwan

西元二〇〇七年十月

操作於弱反轉層場效電晶體之極低功率損耗與

極小面積 CMOS 參考電壓之設計與實現

研究生:林信太

指導教授:闕河鳴 博士

國立交通大學 電信工程學系碩士班

#### 中文摘要

本篇論文使用 0.18 微米互補式金氧半標準製程設計並實現一個與溫度無關 的穩定參考電壓源。最近幾年電池供應的系統越來越廣泛使用,隨著這個趨勢, 在設計電路時都要求小面積、低功率、高效能,而很多類比電路都會需要一個穩 定的參考電壓,因此本論文設計一個低功率與小面積的參考電壓去運用在電池供 應的系統中。本電路工作在弱反轉區可用來取代傳統電路中的雙極性電晶體去實 現與溫度無關的參考電壓,其功率消耗只有幾百奈瓦且面積只有幾百平方微米。 另外,溫度範圍也可以從-80℃到 165℃,而其電壓誤差也僅有幾十毫伏特。因 此,本設計可以運用在電池供應的系統去供應一個穩定的參考電壓。

# The Design and Implementation of an Ultra Low Power and

Small Area CMOS Voltage Reference Based on MOSFET

Operated in Weak Inversion Region

Student: Shin-Tai Lin

**Advisor: Dr. Herming Chiueh**

Department of Communication Engineering National Chiao Tung University Hsinchu, Taiwan

This thesis uses standard CMOS 0.18µm process technique to design and realize a stable voltage reference which does not change with temperature. In the recent years, battery-operated systems are used extensively. Along with this tendency, we demand low-power, small-area, and high performance when designing circuits. Many analog circuits need a stable voltage reference, so the thesis shows a low-power and small-area voltage reference to apply in battery-operated systems. Proposed circuits work in weak inverse region to replace the bipolar devices in conventional circuit and using proposed circuits realize CMOS voltage reference which does not change with temperature. Its power consumption only has several hundred nano-Watt and its area is only several hundred squre nanometer. In addition, the voltage derivation only has several dozens milli-Volt when temperature range is from -80°C to 165°C. Therefore, proposed architectures can supply a stable voltage reference in battery-operated systems.

### 誌謝

本論文可以順利完成,首先要感謝我的指導教授闕河鳴博士,他指導我如何 去完成本論文,很多該注意我沒注意的重點,教授都會仔細一步一步的告訴我該 如何去做,適時給予我意見與正確的方向,我覺得老師教導我的不只是如何去完 成一本論文的方法,而是去完成很多做事情的方法,這是我最受益良多的。

再來,我要感謝嘉儀、江俊、俊誼這三位同窗的好朋友,他們幫我很多事情, 不論是課業或是研究都給我莫大的幫助,然後,感謝佐昇學長在研究上總是會指 導我很多重點,他總是會給我有關論文方面的知識與方法;在這研究所生活中, 這實驗室帶給我很多很多東西,讓我兩年多的研究所生活過得相當充實,有大家 的相伴研究所學習生活多采多姿了起來。

最後,我要感謝我家人,沒有他們就沒有今天的我,還有我女朋友宛樺,她 總是在精神上給予我最大的支持,不論遇到任何問題,她都會安慰我、鼓勵我, 真的非常感謝。

# CONTENTS

| Chinese Abstract | I   |

|------------------|-----|

| English Abstract | II  |

| Acknowledgements | III |

| Contents         | IV  |

| List of Tables   | VI  |

| List of Figures  | VII |

| Chapt | er 1 Introduction                   | 1 |

|-------|-------------------------------------|---|

| -     | Overview of Battery-Operated System |   |

|       | Motivation.                         |   |

| 1.3   | Organization                        | 4 |

|       | Thomas and the second               |   |

#

| 2.1 | Backg | ground                                                  | 5  |

|-----|-------|---------------------------------------------------------|----|

| 2.2 | Conve | entional Bandgap Reference                              | 7  |

|     | 2.2.1 | Bandgap Reference                                       | 8  |

|     | 2.2.2 | BJT and MOS Comparison                                  | 9  |

| 2.3 | СМО   | S Voltage References                                    | 10 |

|     | 2.3.1 | Voltage Mode of V <sub>PTAT</sub> and V <sub>CTAT</sub> | 12 |

|     | 2.3.2 | Current Mode of V <sub>PTAT</sub> and V <sub>CTAT</sub> | 15 |

|     | 2.3.3 | Voltage Reference Uses Parallel Voltages                | 17 |

|     | 2.3.4 | Zero Temperature Coefficient Point (ZTC)                | 19 |

|     | 2.3.5 | Voltage Reference Uses Non-standard Process             | 20 |

|     | 2.3.6 | Comparison of Voltage Reference                         | 22 |

|     | 2.3.7 | Summary                                                 | 25 |

| Chapt | er 3   | Circuitry Architecture                                                                                          | .26 |

|-------|--------|-----------------------------------------------------------------------------------------------------------------|-----|

| 3.1   | Design | Process                                                                                                         | 26  |

|       | 3.1.1  | Reference Paper                                                                                                 | 26  |

|       | 3.1.2  | V <sub>PTAT</sub> (Proportional to Absolute Temperature)                                                        | 27  |

| 3.2   | All N  | MOSFET Voltage Reference (ANVR)                                                                                 | 31  |

|       | 3.2.1  | Principle of ANVR                                                                                               | 31  |

|       | 3.2.2  | Derivation of ANVR                                                                                              | 32  |

|       | 3.2.3  | Post-Layout Simulation of ANVR                                                                                  | 34  |

|       | 3.2.4  | Discussion of ANVR                                                                                              | 39  |

| 3.3   | NMO    | SFET and PMOSFET Voltage Reference (NPVR)                                                                       | 40  |

|       | 3.3.1  | Principle of NPVR                                                                                               | 40  |

|       | 3.3.2  | Derivation of NPVR                                                                                              | 41  |

|       | 3.3.3  | Post-Layout Simulation of NPVR                                                                                  | 44  |

|       | 3.3.4  | Discussion of NPVR                                                                                              | 49  |

| 3.4   | NMO    | SFET PMOSFET and Capacitor Voltage Reference (NPCVR).                                                           | 50  |

|       | 3.4.1  | Start-up Circuit of NPCVR                                                                                       | 50  |

|       | 3.4.2  | Power Supply Reject Ratio (PSRR)                                                                                | 51  |

|       | 3.4.3  | Post-Layout Simulation of NPCVR                                                                                 | 53  |

|       | 3.4.4  | Discussion of NPCVR                                                                                             | 57  |

| 3.5   | Com    | parison                                                                                                         | 58  |

| 3.6   | Sumr   | nary                                                                                                            | 60  |

|       |        | Contraction of the second s |     |

# Chapter 4 Measurement......61

| 4.1 | Meas  | urement Set-up              | 61 |

|-----|-------|-----------------------------|----|

| 4.2 | Expe  | rimental Result             | 63 |

|     | 4.2.1 | Experimental Result of ANVR | 63 |

|     | 4.2.2 | Experimental Result of NPVR | 66 |

|     | 4.2.3 | Discussion of ANVR and NPVR | 69 |

|     | 4.2.4 | Comparison of ANVR and NPVR | 70 |

| 4.3 | Summ  | nary                        | 72 |

## Chapter 5 Conclusion and Future Works......73

| Refere | nces         | 75 |

|--------|--------------|----|

| 5.2    | Future Works | 74 |

| 5.1    | Conclusion   | 73 |

|        |              |    |

# **List of Tables**

## Chapter 2

| Table 2.1: | The Comparison between MOS and BJT                                     | 9  |

|------------|------------------------------------------------------------------------|----|

| Table 2.2: | Researches for Voltage Mode of $V_{PTAT}$ and $V_{CTAT}$               | 14 |

| Table 2.3: | Researches for Current Mode of V <sub>PTAT</sub> and V <sub>CTAT</sub> | 17 |

| Table 2.4: | Researches of Voltage Reference of Parallel Voltages                   | 19 |

| Table 2.5: | Researches of ZTC                                                      | 20 |

| Table 2.6: | Researches of Voltage Reference of Non-standard Process                | 22 |

| Table 2.7: | Comparison for Five Kinds of CMOS Voltage References                   | 23 |

| Table 2.8: | Researches for All CMOS Voltage Reference                              | 23 |

|            |                                                                        |    |

## Chapter 3

| Table 3.1: | Post-Layout Simulation of ANVR                              | 35 |

|------------|-------------------------------------------------------------|----|

| Table 3.2: | Corners of ANVR Post-Layout Simulation (V <sub>REF</sub> )  | 39 |

| Table 3.3: | Post-Layout Simulation of NPVR                              | 45 |

| Table 3.4: | Corners of NPVR Post-Layout Simulation (V <sub>REF</sub> )  | 48 |

|            | Comparison between ANVR and NPVR.                           |    |

| Table 3.6: | Post-Layout Simulation of NPCVR                             | 53 |

| Table 3.7: | Corners of NPCVR Post-Layout Simulation (V <sub>REF</sub> ) | 57 |

| Table 3.8: | Comparison between NPVR and NPCVR                           | 57 |

| Table 3.9: | Comparison of All Voltage Reference's Architectures         |    |

|            |                                                             |    |

# Chapter 4

| Table 4.1: | The Derivation for V <sub>REF</sub> of ANVR                   | 64 |

|------------|---------------------------------------------------------------|----|

| Table 4.2: | Experimental Results of ANVR                                  | 65 |

| Table 4.3: | Resistor Variation                                            | 66 |

| Table 4.4: | The Derivation for V <sub>REF</sub> of NPVR                   | 67 |

| Table 4.5: | Experimental Results of NPVR                                  | 68 |

| Table 4.6: | Process Variation of V <sub>REF</sub>                         | 68 |

| Table 4.7: | PSRR of NPVR (4pF in output)                                  | 69 |

| Table 4.8: | Comparison of Post Layout Simulation and Experimental results | 70 |

| Table 4.9: | Comparison of Taped-out Voltage Reference's Architectures     | 71 |

|            |                                                               |    |

# **List of Figures**

### Chapter 1

| Figure 1.1: | Features and Examples of Battery-Operated System | 2 |

|-------------|--------------------------------------------------|---|

| Figure 1.2: | Block Diagram of a Battery-Operated System       | 3 |

### Chapter 2

| Figure 2.1.1: | Block Diagram of Conventional Voltage Reference                                     | 6  |

|---------------|-------------------------------------------------------------------------------------|----|

| Figure 2.1.2: | The Curvature of $V_{\text{REF}}$ Formed by $V_{\text{PTAT}}$ and $V_{\text{CTAT}}$ | 6  |

| Figure 2.2.1: | Conventional Bandgap Reference Circuit                                              | 8  |

| Figure 2.3.1: | Circuit Architecture for Voltage Mode of $V_{PTAT}$ and $V_{CTAT}$ (REF[2]).        | 12 |

| Figure 2.3.2: | Circuit Architecture for Current Mode of $V_{\text{PTAT}}$ and $V_{\text{CTAT}}$    |    |

| (REF[10])     | 1                                                                                   | 15 |

| Figure 2.3.3: | Circuit Architecture of Parallel Voltages (REF[21])                                 | 17 |

| Figure 2.3.4: | Circuit Architecture of ZTC (REF[27])                                               | 19 |

| Figure 2.3.5: | Circuit Architecture of Non-standard Process (REF[29])                              | 21 |

| Figure 2.3.6: | Vpn and Vnn as a Function of Temperature                                            | 21 |

|               | 1896                                                                                |    |

# Chapter 3

# 1896

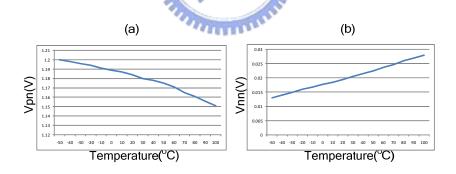

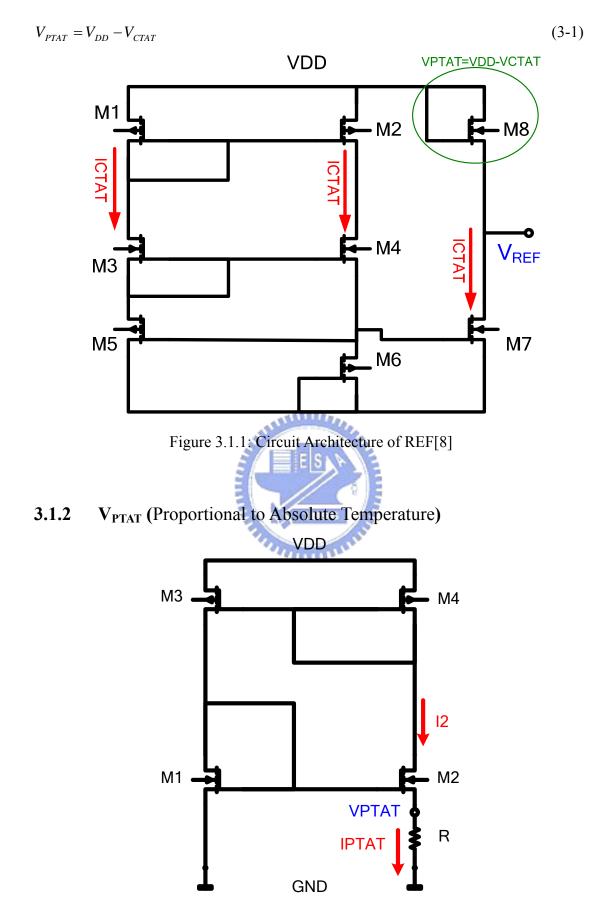

| Figure 3.1.1: | Circuit Architecture of REF[8]                      | 27 |

|---------------|-----------------------------------------------------|----|

| Figure 3.1.2: | Conventional V <sub>PTAT</sub> Circuit Architecture | 27 |

| Figure 3.1.3: | The V <sub>PTAT</sub> Proposed Architecture         | 30 |

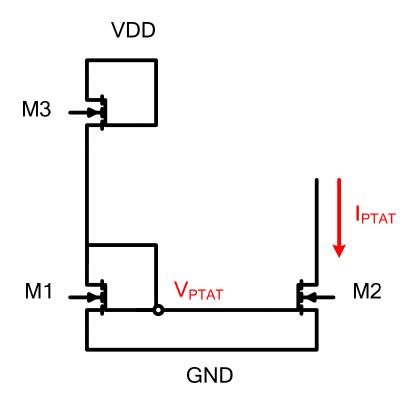

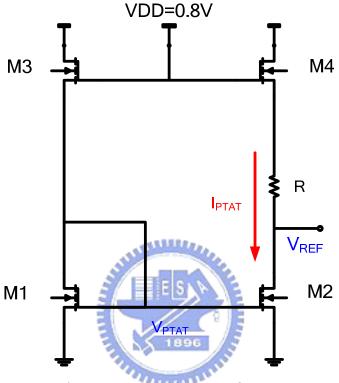

| Figure 3.2.1: | Architecture of ANVR                                |    |

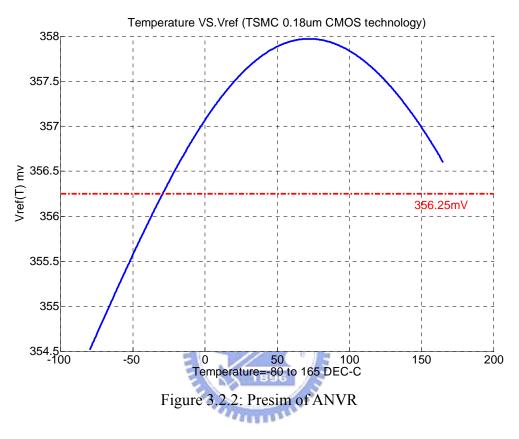

| Figure 3.2.2: | Presim of ANVR                                      | 35 |

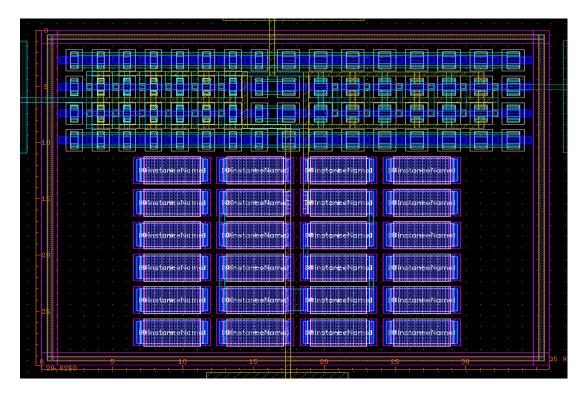

| Figure 3.2.3: | Layout of ANVR in TSMC 0.18µm CMOS Technology       |    |

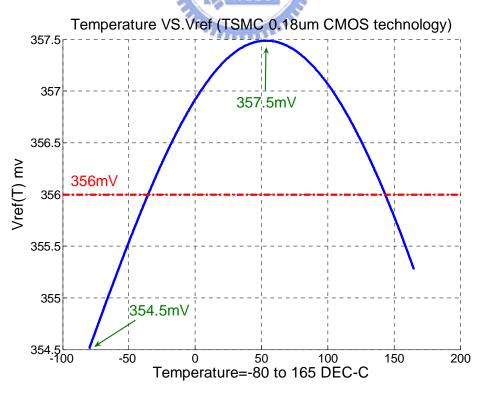

| Figure 3.2.4: | TT TT_RES Corner of ANVR                            |    |

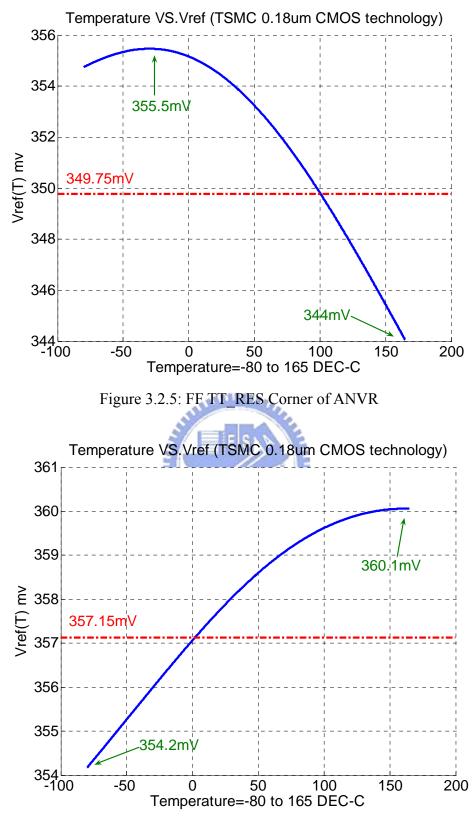

| Figure 3.2.5: | FF TT_RES Corner of ANVR                            |    |

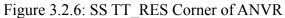

| Figure 3.2.6: | SS TT_RES Corner of ANVR                            |    |

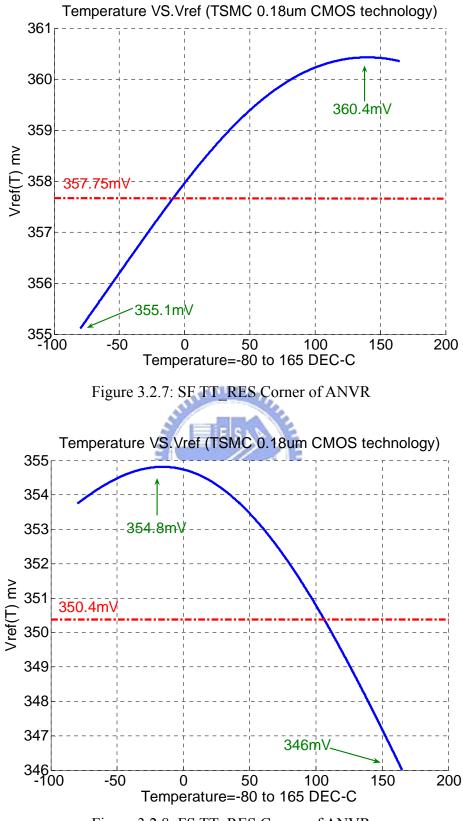

| Figure 3.2.7: | SF TT_RES Corner of ANVR                            |    |

| Figure 3.2.8: | FS TT_RES Corner of ANVR                            |    |

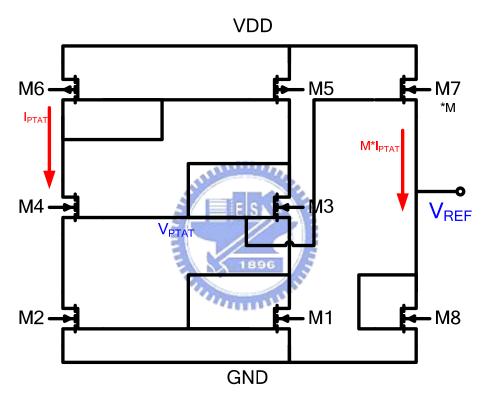

| Figure 3.3.1: | Architecture of NPVR                                | 40 |

| Figure 3.3.2: | Presim of ANVR                                      | 44 |

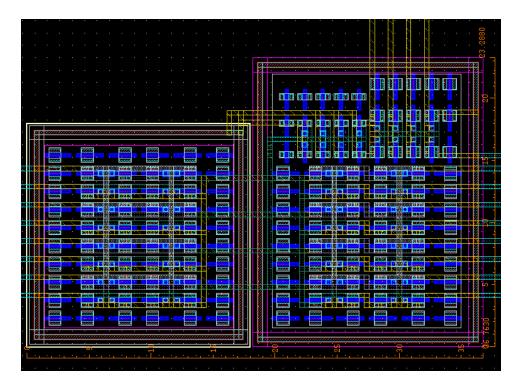

| Figure 3.3.3: | Layout of NPVR in TSMC 0.18µm CMOS Technology       | 45 |

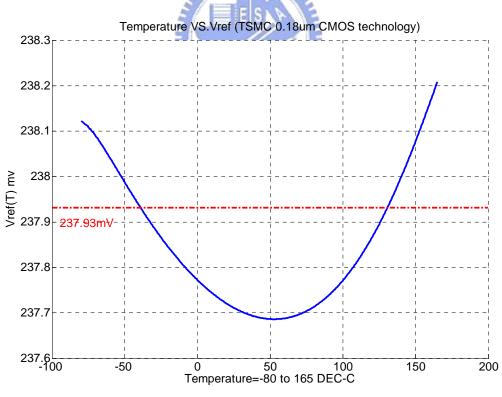

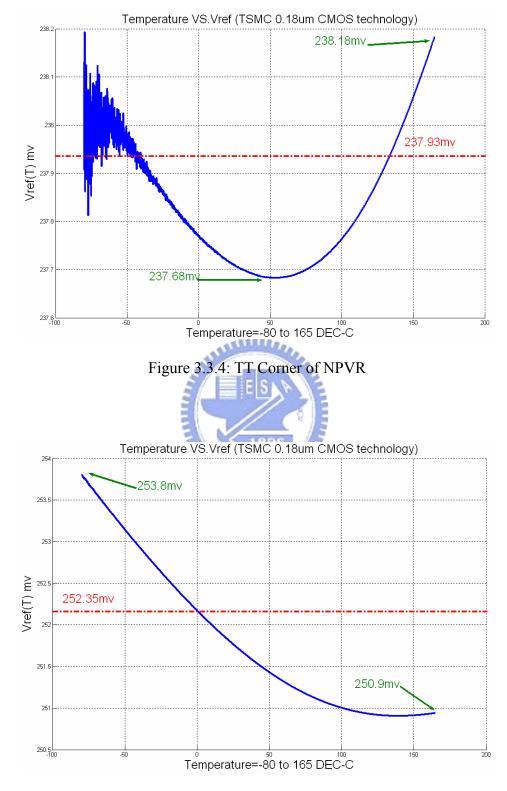

| Figure 3.3.4: | TT Corner of NPVR                                   | 46 |

| Figure 3.3.5: | FF Corner of NPVR                                         | 46 |

|---------------|-----------------------------------------------------------|----|

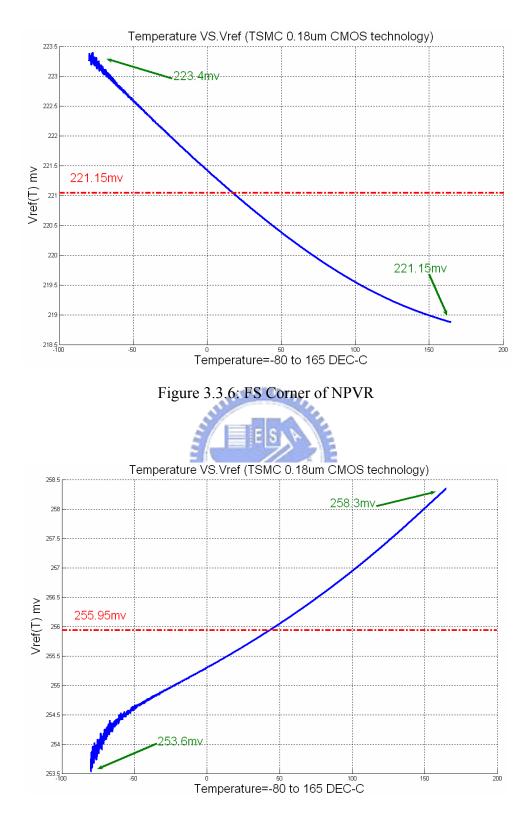

| Figure 3.3.6: | FS Corner of NPVR                                         | 47 |

| Figure 3.3.7: | SF Corner of NPVR                                         | 47 |

| Figure 3.3.8: | SS Corner of NPVR                                         | 48 |

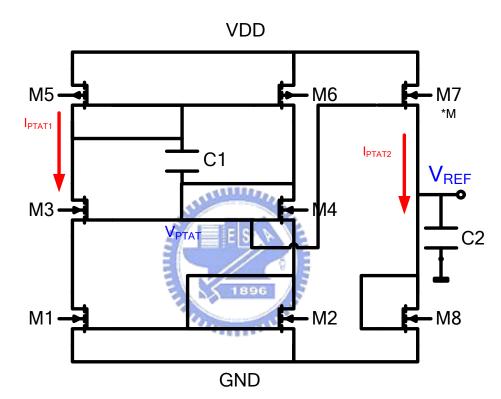

| Figure 3.4.1: | Voltage Reference uses NMOS, PMOS, and Capacitor (NPCVR). | 50 |

| Figure 3.4.2: | Small Signal of NPCVR                                     | 51 |

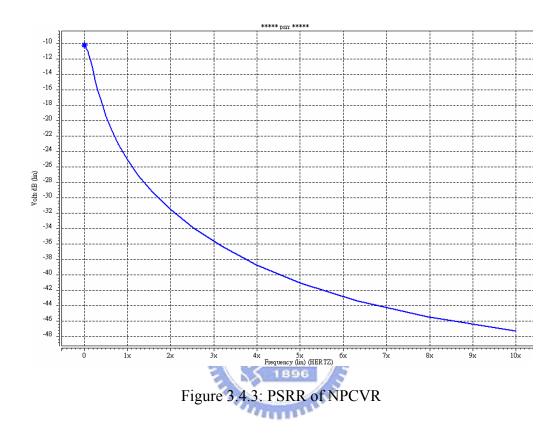

| Figure 3.4.3: | PSRR of NPCVR                                             | 53 |

| Figure 3.4.4: | Layout of NPCVR                                           | 54 |

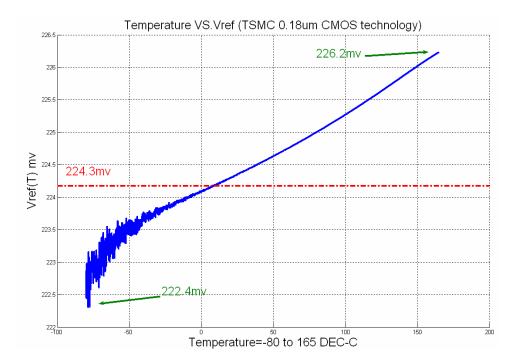

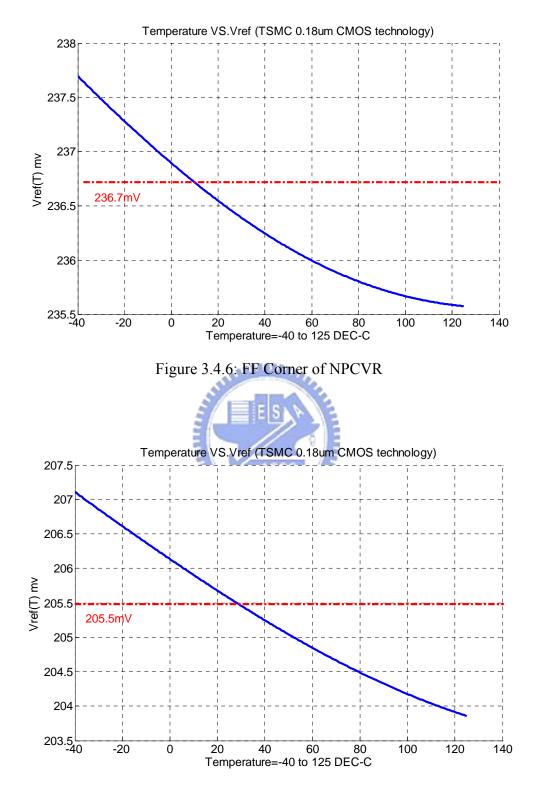

| Figure 3.4.5: | TT Corner of NPCVR                                        | 54 |

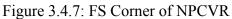

| Figure 3.4.6: | FF Corner of NPCVR                                        | 55 |

| Figure 3.4.7: | FS Corner of NPCVR                                        | 55 |

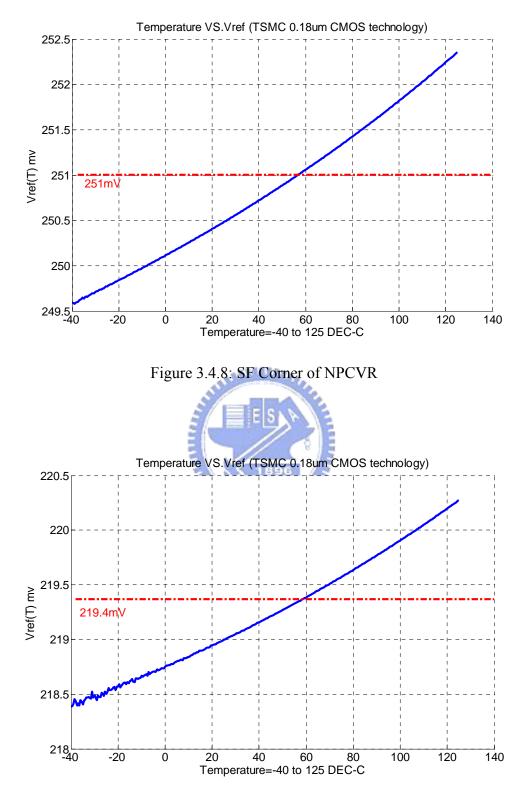

| Figure 3.4.8: | SF Corner of NPCVR                                        | 56 |

| Figure 3.4.9: | SS Corner of NPCVR                                        | 56 |

# Chapter 4

| Chapter     | - AND   |    |

|-------------|---------------------------------------------|----|

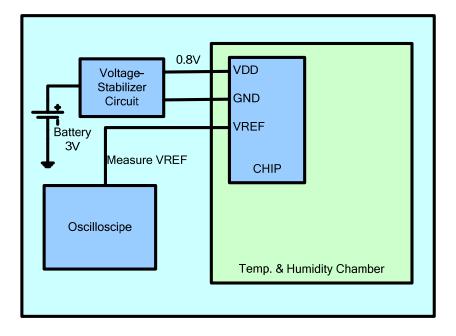

| Figure 4.1: | Block Diagram of Measurement Environment    | 62 |

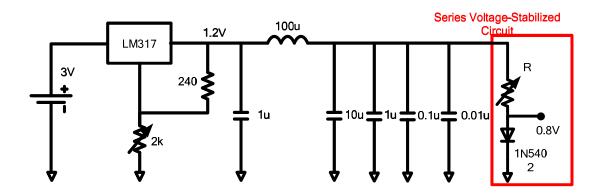

| Figure 4.2: | Block Diagram of Voltage-Stabilized Circuit | 62 |

| Figure 4.3: | The Pictures of Measurement Environment     | 63 |

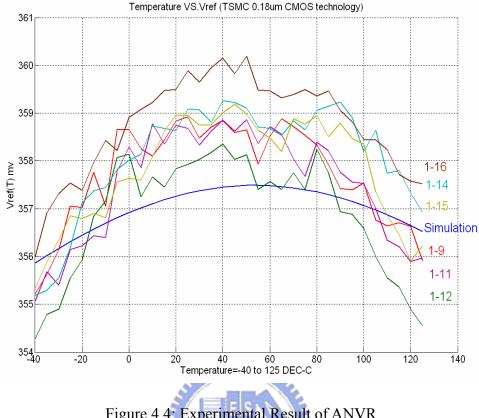

| Figure 4.4: | Experimental Results of ANVR                |    |

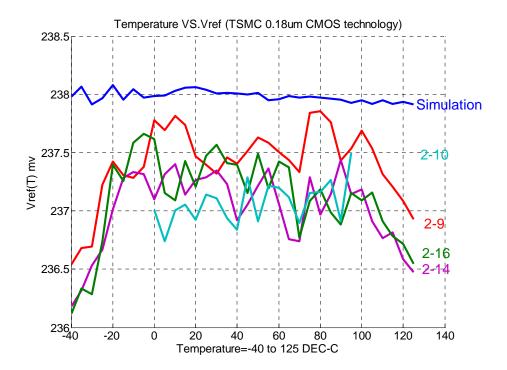

| Figure 4.5: | Experimental Results of NPVR                |    |

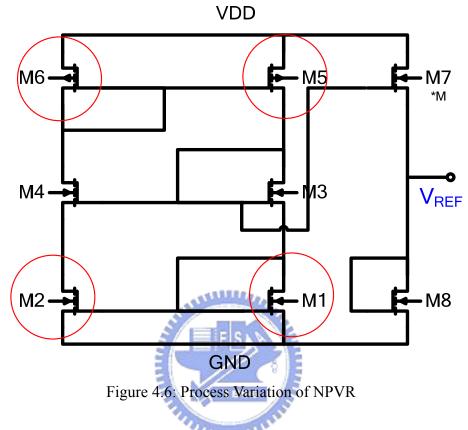

| Figure 4.6: | Process Variation of NPVR                   | 69 |

# CHAPTER 1

# Introduction

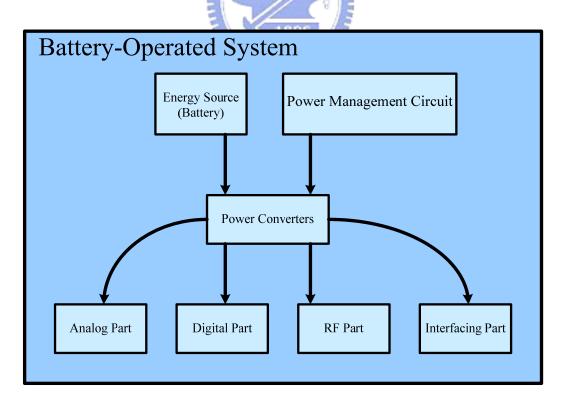

This chapter will introduce battery-operated system and illustrate motivation. Then, we show that voltage reference is an important circuit in analog circuits and voltage reference needs to become small-area and low-power.

#### 1.1 Overview of Battery-Operated System

In recently these years, battery-operated systems are used widely. For example, cell phone, PDA, GPS, digital watch, notebook, etc, see Figure 1.1. Those give people convenient and support, and those machines will be more and more widespread. Therefore we know that battery-operated system is inseparable with the humanity. Because battery-operated system is already a trend, we should understand battery-operated system. Roughly, battery-operated system has fundamental characteristics which are battery-operated, small-area, portable, and multi-function. Beside, battery-operated systems have a very serious issue which is hot. Now, we will discuss every characteristics in the below parts individually.

#### 1. Battery

Battery-operated systems use battery to supply it working. Battery-operated systems are requested to reach low-power, so the batteries can use longer and save more power. It is good for consumers, because no one want to bring a lot of batteries on body. Therefore designers should take the low power as the goal to design circuit architectures for battery-operated systems.

#### 2. Portable Function

Portable function is convenient for people. Because people can bring powerful electronic products on body and use them anytime and anywhere. Therefore, electronic products want to have portable function, designers should notice that using small-area to design circuit architecture. Using small area and achieving high performance is already a trend at battery-operated systems.

Figure 1.1: Feature and Examples of Battery-Operated System

#### 3. Multi-Function

Multi-function means that providing the most functions in a finite area. In other words, multi-function implies system integration and small area. It is very efficient to accomplish in battery-operated system. Therefore, we need to treasure every area by system integration and small circuit architectures which also request high performance.

#### 4. Thermal Issue

Nowadays, battery-operated systems are quite small, and the situation will cause thermal issue. Because a lot of circuit architectures integrate in finite and small area, the heat will increase quickly and be not easy to radiate heat. Therefore battery-operated systems must need smart temperature sensors which can sense temperature and admonish system. Smart temperature sensors need two voltages which are  $V_{PTAT}$  and  $V_{REF}$  to compare. And a stable  $V_{REF}$  is our goal at battery-operated system.

In the above introduction, we know that battery-operated systems have some key point which are low-power and small-area and need to solve thermal issue. In the next section, we will explain the motivation of voltage reference at battery-operated system.

#### **1.2 Motivation**

Voltage reference is a key element in many circuit architectures. For example, PLL, oscillator, data converter, voltage regulator, DRAM(Dynamic Random Access Menory), flash, and temperature sensor, etc. Those circuit architectures are important and conventional circuit architectures in analog systems. If those want to have high performance, they must need a stable voltage reference which is independent strongly with temperature, process variation, and supply voltage. Therefore, we should not ignore the importance of voltage reference.

Figure 1.2: Block Diagram of Battery-Operated System

It is block diagram of battery-operated system in Figure 1.2. We can know that those above circuits are always used at analog part, power converter, and power management circuit. So, those circuits are designed in battery-operated system, they must need an adaptable voltage reference. It means that a low-power, small-area, and high performance voltage reference is needed in battery-operated systems.

#### **1.3 Organization**

Chapter 2 begins with introduction of conventional voltage reference, and three bandgap references are shown and discussed. Then bandgap reference and CMOS voltage reference are compared. Finally, we assort five voltage references of MOS and advance that voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$  is as our excogitative architecture.

Chapter 3 shows that  $V_{CTAT}$  is produced by MOS transistor which works in subthreshold region and  $V_{PTAT}$  is produced by  $V_{CTAT}$ . Then proposed design architectures are implemented and described in detail. Comparison with proposed design architectures and researches is presented finally.

In Chapter 4, measured method and measurement environment are presented. Experimental results for the voltage references fabricated in a standard 0.18-µm CMOS technology are reported and discussed in this chapter.

41111

The conclusions of this work are given in Chapter 5.

# chapter 2

# **Review of Voltage Reference**

First, this chapter introduces general method of voltage reference. Conventional bandgap references are presented and illustrated. Comparison with bandgap reference and CMOS (Complementary MOS) voltage reference is shown after understanding conventional bandgap references. Then CMOS voltage reference is chosen because it is better than bandgap reference at our design goal. And, CMOS voltage reference is assorted five types at many researches. Finally, choosing voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$  is the better adaptable design architecture of voltage reference.

1000

#### 2.1 Background

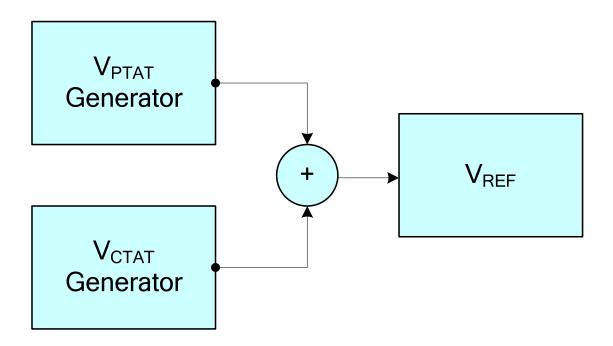

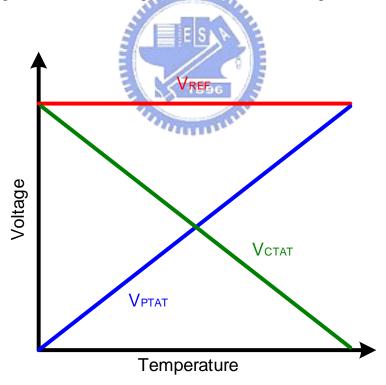

Nowadays, voltage reference has developed maturely. We can know how to produce voltage reference in many books and researches. And Figure 2.2.1 is block diagram of voltage reference which shows that a stable voltage is produced by two different voltages. In Figure 2.1.2, a traditional  $V_{REF}$  which does not change with temperature is added by  $V_{PTAT}$  and  $V_{CTAT}$ . If  $V_{PTAT}$  and  $V_{CTAT}$  are high linearity,  $V_{REF}$  will be a stable voltage. The method is suitable for voltage reference of BJT (Bipolar transistor) or MOS because  $V_{CTAT}$  can be produced easily by characteristic of BJT or MOS, and  $V_{PTAT}$  is produced by  $V_{CTAT}$ . Underside will show what  $V_{PTAT}$  and  $V_{CTAT}$  are?

Figure 2.1.1: Block Diagram of Conventional Voltage Reference

Figure 2.1.2: The Curvature of  $V_{REF}$  Formed by  $V_{PTAT}$  and  $V_{CTAT}$

If analog circuits want to have a stable voltage reference, two important elements which are  $V_{PTAT}$  and  $V_{CTAT}$  are needed. CTAT is complementary to absolute temperature. It means that a voltage decreases with temperature.  $V_{CTAT}$  is used to compensate  $V_{PTAT}$ , so  $V_{REF}$  will not change with temperature. It is always produced by  $V_{BE}$  of BJT or  $V_{GS}$  of MOS which work in subthreshold region. In addition,  $V_{CTAT}$  is also used to produce  $V_{PTAT}$  by two different  $V_{CTAT}$  which subtract each other. Therefore, the linearity of  $V_{CTAT}$  is important at circuits of voltage reference.

PTAT is proportional to absolute temperature. It means that a voltage increases with temperature. The above paragraph has said that  $V_{PTAT}$  is always produced by two different  $V_{CTAT}$ . This is a significant issue how to reach high linearity of  $V_{PTAT}$  in circuits of voltage reference, because it will affect  $V_{REF}$  directly.  $V_{PTAT}$  is always used to another purpose which is as a compared voltage in smart temperature sensor. First stage of smart temperature sensor needs two voltages to compare, and the result is an authority of temperature difference which delivers to second stage of smart temperature sensor. Usually,  $V_{PTAT}$  is compared with  $V_{REF}$ . By this, smart temperature sensor can have an accurate temperature difference. But, premise is that smart temperature sensor needs high precise  $V_{REF}$  and  $V_{PTAT}$ .

After knowing the produced method of voltage reference, we need to notice three issues which relate very much to voltage reference. There are supply voltage variation, temperature variation, and process variation. If we can overcome the three issues, a stable voltage reference is produced.

The above principle is often used to produce voltage references, but the principle can derive many different circuits of voltage reference. The traditional voltage reference is designed by BJT, and it is called bandgap reference. In the next section, bandgap reference will be introduced and illustrated.

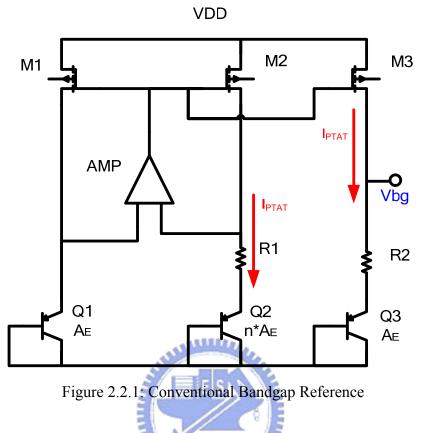

#### 2.2 Conventional Bandgap Reference

This section will illustrate bandgap reference and show bandgap reference's architectures. Then a comparison with BJT and MOS is shown and explained. Finally, we choose MOS to design voltage reference because MOS is more suitable to apply in battery-operated system.

#### 2.2.1 Bandgap Reference

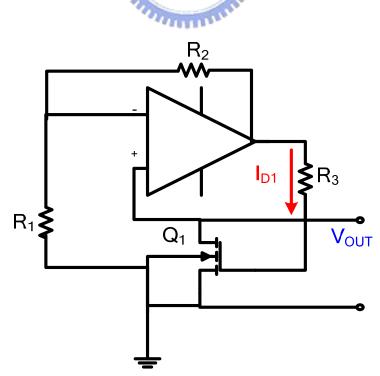

In Figure 2.2.1, bandgap reference has been shown. M1 $\sim$ M2, Q1 $\sim$ Q2, and operational amplifier is used to produce I<sub>PTAT</sub>. By mirroring from M2 to M3, we have the function which is shown as follows,

$$V_{bg} = V_{PTAT} + V_{CTAT} = \Delta V_{BE} + V_{BE}$$

(2-12)

And

$$\Delta V_{BE} = \frac{R_2}{R_1} V_T \ln(n)$$

(2-13)

$\triangle V_{BE}$  is a voltage of positive TC, and  $V_{BE}$  is a voltage of negative TC. Then,  $V_{REF}$  will be independent of temperature by adding  $\triangle V_{BE}$  and  $V_{BE}$ .

After bandgap reference has been illustrated, we will be curious that the difference of voltage reference which use MOS or BJT to design. Why are researches of CMOS voltage reference more and more? What are they advantages and disadvantages? In the next section, we will compare CMOS voltage reference and

bandgap reference. Finding out the advantages and disadvantages of voltage references which are designed by MOS and BJT is very important. Why do we use MOS to design voltage reference, not BJT? The answer will explain afterward.

#### 2.2.2 BJT and MOS comparison

We have understood bandgap reference how to produce in the above section. Now, the focus is that bandgap reference compares with CMOS voltage reference. We list some key points which more important when designing voltage reference. The comparison of voltage references which use MOS or BJT to design is shown in Table 2.1.

|               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                 |  |  |  |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--|--|--|--|--|

|               | MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | BJT                             |  |  |  |  |  |

|               | ALLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                 |  |  |  |  |  |

| Advantages    | 1. V <sub>TH</sub> =0.45V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1. Low process variation        |  |  |  |  |  |

|               | 2. Small area S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2. Low supply voltage variation |  |  |  |  |  |

|               | 3. V <sub>REF</sub> <1.21V, low-voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                 |  |  |  |  |  |

| Disadvantages | 1. Process variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1. $V_{BE}=0.6V$                |  |  |  |  |  |

|               | 2. Supply voltage variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2. Large area                   |  |  |  |  |  |

|               | A STATE OF S | 3. Vbg=1.21V                    |  |  |  |  |  |

Table 2.1: The Comparison between MOS and BJT

Let's see the advantages of MOS which are also the disadvantages of BJT. First,  $V_{TH}$  of MOS is lower than  $V_{BE}$  of BJT. We know that MOS operates in subthreshold region is like  $V_{BE}$  which is a voltage of negative TC. It means that  $V_{GS}$  has the inverse ratio with the temperature when  $V_{GS} < V_{TH}$ (about 0.45V in TSMC 0.18um process). Therefore, the same circuit architecture of voltage reference, MOS's supply voltage is lower than BJT's supply voltage. In the recent years, a lot of architectures are demanded for low-power, low-voltage, and small-area. The trend is ineluctability and more and more attention, and voltage reference is also following the trend. Therefore, CMOS voltage reference is more ascendant than bandgap reference in low-power architectures.

Second, area of MOS is smaller than area of BJT in the standard CMOS process and the same conditions. So area of voltage reference will decrease when using MOS to design it. The excellence is very useful to design in battery-operated system, because battery-operated systems usually have some characteristics which are light, small, and portable. Therefore, MOS is easy to reach system integration and decrease the area.

Third, curvature compensation techniques are often used at bandgap reference. Because the linearity of  $V_{BE}$  is not very good at overall temperature range, it needs additional circuit which means curvature compensation techniques to compensate the linearity of  $V_{bg}$ . On the other hand,  $V_{TH}$  of MOS has superior linearity, and MOS does not need curvature compensation technique at wide temperature range. Therefore, the area of voltage reference circuit can be reduced. But, the performance is still good or even better.

Even if MOS has a lot of advantages which is very adaptable in battery-operated system, we still need to attend to process variation when we want to design CMOS voltage reference. Process variation of MOS is more serious than that of BJT, but it can be got over by every corner simulation. We need to run every corner and limit corners at an acceptive range when we simulate voltage reference.

In the above comparison, we know that MOS is better than BJT when designing voltage reference in battery-operated system, so we decide that using MOS to design voltage reference. Before design, we should review researches of MOS voltage reference in the recent six years. Because we can understand how to design CMOS voltage reference by reviewing researches. And it is important to find out advantages and disadvantages from every circuit architectures of voltage reference in researches. The introduction of CMOS voltage reference will be presented in the next section. In addition, we will compare five circuit architectures of voltage reference and choose the best adaptable architecture to discuss in depth.

#### 2.3 CMOS Voltage References

Bandgap reference is a traditional voltage reference. It is formed by  $V_{BE}$  of BJT.  $V_{BE}$  is a voltage of negative temperature coefficient, and two different  $V_{BE}$  subtract to produce  $V_{PTAT}$  which is a voltage of positive temperature coefficient. So, a stable voltage reference which is not change with temperature, supply voltage, and process is produced by  $V_{PTAT}$  and  $V_{CTAT}$ . As the process advances, voltage references request more and more seriously for low power and small area. But, BJT is hard to accord with the goal at the present age. Therefore, BJT was replaced by MOS when designing voltage reference. The source had been illustrated them in the above sections.

Near present year, someone discover MOS work in subthreshold region has a characteristic which is analogous to BJT. It means that  $V_{GS}$  of MOS which works in subthreshold region is a voltage of negative temperature coefficient. So voltage reference starts to use MOS. In the above sections, we know that MOS has two main advantages. First, it is low voltage, because  $V_{GS}$  is lower than  $V_{BE}$ . Second, MOS's area is small. Because having the two advantages, researches of CMOS voltage references are increasing in the recent six years.

In the recent six years, a lot of researches of CMOS voltage references are designed. CMOS can be assorted five types by those researches. The classified basis is produced method of voltage reference. All types have advantages and disadvantages by themselves. In the following sections, we will illustrate and discuss. Now, the five types are shown below.

1. Voltage Mode of  $V_{PTAT}$  and  $V_{CTAT}$ : CMOS voltage reference is produced by  $I_{PTAT}$  and  $V_{CTAT}(V_{GS})$ .

#### 2. Current Mode of V<sub>PTAT</sub> and V<sub>CTAT</sub>: 1896

CMOS voltage reference is produced that  $I_{PTAT}$  and  $I_{CTAT}$ .  $I_{REF}$  multiplies resistor to produce  $V_{REF}$ .

#### 3. Voltage Reference Uses Parallel Voltages:

The circuit uses that two  $V_{GS}$  which have the same slope to subtract, then CMOS voltage reference is produced.

#### 4. Zero Temperature Coefficient Point (ZTC):

When MOS work at a fixed point, the  $V_{GS}$  and  $I_D$  will not change with temperature. The point is called zero temperature coefficient point. So  $V_{GS}$  can be designed as voltage reference.

#### 5. Voltage Reference Uses Non-standard Process:

CMOS voltage reference which does not use standard CMOS process technique is designed.

The five types will be showed in the below sections. In addition, I choose five researches to illustrate the five types and list the performance of five types. Then the comparison of researches will be shown and discussed. We will illustrate that voltage mode of VPTAT and VCTAT is more suitable than other architectures to design voltage reference in battery-operated system.

#### **2.3.1** Voltage Mode of V<sub>PTAT</sub> and V<sub>CTAT</sub>

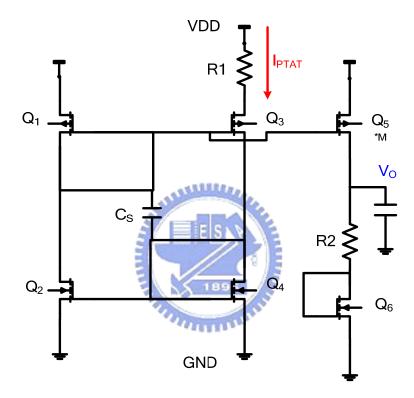

Figure 2.3.1: Circuit Architecture for Voltage Mode of VPTAT and VCTAT (REF[2])

In the last few years, CMOS voltage reference's circuits can work under 1V. But, those circuits present a high level of complexity. It may cause undesirable behavior and a high quiescent current. Consequently, efforts have been made to develop a simple circuit of voltage reference which has a power supply lower than the bandgap voltage.

The circuit refers to Ref [2]: A CMOS Voltage Reference Based on Threshold Voltage for Ultra Low-Voltage and Ultra Low-Power. It is assorted to voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$ . Voltage reference uses only resistors and transistors working in weak inversion, without any bipolar transistors. The circuit was implemented in a standard

$0.35\mu m$  TSMC CMOS process. V<sub>REF</sub> is 514mV for a power supply of 900mV, and temperature coefficient is 39 ppm/°C for temperature range from 0°C to 100°C. (Ref: [2])

The derivative is as follows:

All MOS operate in subthreshold region, and the function is (2-14) (2-15),

$$I_{DS}(T) = I_{S}\left(\frac{W}{L}\right) \exp\left(\frac{V_{GS}(T) - V_{th}(T)}{n\left(\frac{kT}{q}\right)}\right)$$

(2-14)

$$V_{GS}(T) = V_{th}(T) + n \frac{kT}{q} \ln \left( \frac{I_{DS}(T)}{I_{S}\left(\frac{W}{L}\right)} \right)$$

(2-15)

Using two  $V_{GS}$  to produce  $\triangle V_{GS}$  which is proportional to absolute temperature (PTAT), see (2-16),

$$\Delta V_{GS} = V_{GS1} - V_{GS3} = n \frac{kT}{q} \ln \left( \frac{(W/L)_3 (W/L)_2}{(W/L)_1 (W/L)_4} \right)$$

(2-16)

Deciding the slope of  $\triangle V_{GS}$  is feasible by adjusting (W/L). And, we can know  $I_{PTAT}$  is  $\triangle V_{GS} / R_1$ , see (2-17),

$$I_{PTAT} = \frac{\Delta V_{GS}}{R_1}$$

(2-17)

$I_{Q5}$  is M\*I<sub>PTAT</sub>, beside V<sub>GS</sub> is complementary to absolute temperature (CTAT). So, voltage reference (V<sub>REF</sub>) is the function of (2-18),

$$V_{\text{REF}} = V_{GS6} + \frac{M * I_{\text{PTAT}}}{R_2}$$

$$V_{REF}(T) = V_{Q6}(T) + n \left(\frac{kT}{q}\right) \frac{R_2(T_0) \left(\frac{W}{L}\right)_5}{R_1(T_0) \left(\frac{W}{L}\right)_1} \ln \left[\frac{\left(\frac{W}{L}\right)_2 \left(\frac{W}{L}\right)_3}{\left(\frac{W}{L}\right)_4 \left(\frac{W}{L}\right)_1}\right]$$

(2-18)

The architecture of CMOS voltage reference has some advantages:

- 1. Low power and low supply voltage: All MOS operate in subthreshold region. The power and voltage will be very low.

- 2. **Small area:** Resistors of the above architecture occupies a half above area. If the resistors can be decreased or deleted, area will be very small. It is conform to design in battery-operated system.

- 3. **Simple:** It uses no curvature compensation technique, but it has high performance. The circuit has only three current paths, so the power can scale down.

Those advantages are very powerful help for designing voltage reference in battery-operated system. In Table 2.2, it shows researches for voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$ . The power can scale down to several dozens nano-Amp and the area can reach  $\mu m^2$ . Under comparison, the performance certainly does not lose to bandgap reference.

| - 41 | 200 |         |  |

|------|-----|---------|--|

|      |     | <br>L., |  |

|      | _   | _       |  |

|      |     |         |  |

|      |     |         |  |

| PAPER     | VDD        | Temperature                           | Temperature | VREF | Tech. | AREA     | PSRR | POWER |  |

|-----------|------------|---------------------------------------|-------------|------|-------|----------|------|-------|--|

| (year)    | <b>(V)</b> | Range                                 | Coefficient | (mV) | (µm)  | $(mm^2)$ | (dB) | (W)   |  |

|           |            | (°C)                                  | (ppm/°C)    |      |       |          |      |       |  |

| Voltage N | lode of    | V <sub>PTAT</sub> and V <sub>CT</sub> | TAT         |      |       |          |      |       |  |

| *[1] 2004 | 4.5~5      | 25~90                                 | 347         | 1320 | 0.18  |          |      |       |  |

| *[2] 2005 | 0.9        | 0~100                                 | 39          | 514  | 0.35  | 0.12     | 22   | 780n  |  |

| *[3] 2005 | 2          | 0~70                                  | 62          | 579  | 0.35  | 0.126    | 84   | 4.6u  |  |

| *[4] 2006 | 0.9~4      | 0~80                                  | 10          | 670  | 0.35  | 0.045    | 40   | 63n   |  |

| [5] 2004  | 1.1~2.2    | -10~70                                | 85          | 504  | 0.18  |          |      | 176u  |  |

| [6] 2005  | 3.3        | 0~150                                 | 26          | 711  | 0.35  |          |      |       |  |

| [7] 2006  | 1.3        | -50~130                               | 9           | 546  | 0.18  |          | 100  | 80u   |  |

| [8] 2006  | 0.5        | -40~100                               | 2.2         | 319  | 0.13  | 0.0002   | 14   | 40n   |  |

Table 2.2: Researches for Voltage Mode of  $V_{PTAT}$  and  $V_{CTAT}$

#### **2.3.2** Current Mode of V<sub>PTAT</sub> and V<sub>CTAT</sub>

The circuit refers to Ref [10]: A Simple Subthreshold CMOS Voltage Reference Circuit With Channel-Length Modulation Compensation. It is assorted to current mode of V<sub>PTAT</sub> and V<sub>CTAT</sub>. The circuit uses MOS works in subthreshold region to produce a reference voltage of 221mV at supply voltage of 0.85V. The power consumption has only  $3.3\mu$ W at room temperature uses TSMC 0.18µm technology. The area of proposed circuit is less than 0.0238 mm<sup>2</sup>, and the reference voltage variation is 2mV/V for supply voltage from 0.9 to 2.5V. Beside, the temperature variation is 6mV in the range from -20°C~120°C. (Ref: [10])

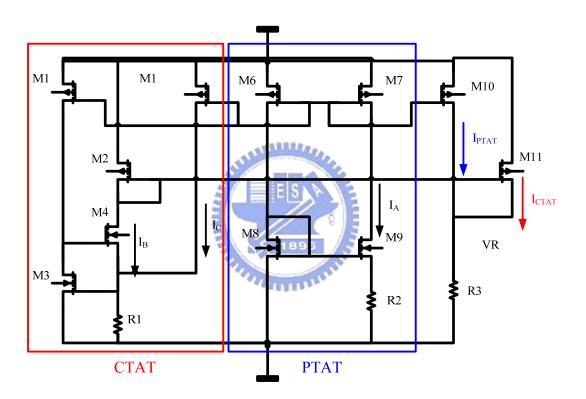

Figure 2.3.2: Circuit Architecture for Current Mode of VPTAT and VCTAT (REF[10])

The circuit is a typical current mode of  $V_{PTAT}$  and  $V_{CTAT}$ , and it is divided into three parts.

CTAT part: It is made of transistors M1 to M5 and resistor R1. To analyze the circuit, M3 operates in subthreshold region. V<sub>GS3</sub> is negative-temperature voltage. So, we can know that (2-19).

$$I_{B} = \frac{V_{GS3}}{R_{1}} - I_{C}$$

(2-19)

$I_C$  is used to compensate channel-length modulation.  $I_B$  is a current of negative-temperature coefficient, so  $I_{CTAT}$  is produced in this part.

2. **PTAT part:** A general I<sub>PTAT</sub> generator is made of transistors M6 to M9 and resistor R2. Transistors M8 and M9 operate in subthreshold region, and the function is as follows : (2-20)

$$I_{A} = \frac{\left(V_{GS8} - V_{GS9}\right)}{R_{2}} = \frac{\Delta V_{GS}}{R_{2}}$$

(2-20)

$\Delta V_{GS}$  is positive-temperature voltage, so  $I_A$  is positive-temperature current. Therefore  $I_{PTAT}$  is produced in the part.

3. **V**<sub>REF</sub> **part:** Using transistors M10 to M11 and resistor R3, we can get V<sub>REF</sub>. The function of V<sub>REF</sub> is as follows : (2-21)

$$V_{REF} = \left(\frac{\left(\frac{W}{L}\right)_{10}}{\left(\frac{W}{L}\right)_{7}}I_{A} + \frac{\left(\frac{W}{L}\right)_{11}}{\left(\frac{W}{L}\right)_{2}}I_{B}\right) * R_{3}$$

(2-21)

Although, those circuit can be designed in low voltage architecture, but they always need resistors. It must cause big area, so it is not easy to accord with our goal which is design in battery-operated system. Besides, resistors have more variation in standard CMOS process. It may decrease the accuracy of voltage reference. Further, voltage reference is the currents to multiply the resistor. If  $V_{REF}$  needs a higher value, the currents and resistor must be large enough to reach the value. Therefore, power is hard to decrease.

In Table 2.3, it shows researches for current mode of  $V_{PTAT}$  and  $V_{CTAT}$ . We can discover that temperature coefficient of current mode is not better than voltage mode. Because current mode of  $V_{PTAT}$  and  $V_{CTAT}$  needs current mirror and resistors, they will cause deviation of voltage reference. Therefore, temperature coefficient is difficult to scale down. The power is hard to scale down, too. Those issues have been illustrated in the above section.

| PAPER            | VDD     | Temperature                           | Temperature            |        |      | AREA               | PSRR | POWER |

|------------------|---------|---------------------------------------|------------------------|--------|------|--------------------|------|-------|

| (year)           | (V)     | Range<br>(°C)                         | Coefficient<br>(ppm/℃) | (mV)   | (µm) | (mm <sup>2</sup> ) | (dB) | (W)   |

| Current <b>N</b> | lode of | V <sub>PTAT</sub> and V <sub>CT</sub> | ſAT                    |        |      |                    |      |       |

| *[9] 2003        | 1.2     | -25~125                               | 119                    | 295    | 1.2  | 0.23               | 40   | 4.32u |

| *[10]2006        | 0.85    | -20~120                               | 194                    | 221    | 0.18 | 0.0238             |      | 3.3u  |

| [11] 2003        | 0.6     | -40~100                               | 93                     | 400    | 0.13 |                    |      |       |

| [12] 2003        | 1.5     | -40~125                               | 37.88                  | 800    | 0.13 |                    |      | 120u  |

| [13] 2003        | 0.6~1.8 | 0~80                                  | 80                     | 405    | 0.18 | 0.1                | 82   | 25u   |

| [14] 2004        | 3~5     | -60~100                               | 4                      | 1165.4 | 1.2  | 0.18               |      | 30u   |

| [15] 2004        | 1       | -20~80                                | 200                    | 400    | 0.35 |                    |      | 3u    |

| [16] 2004        | 0.8     | 0~100                                 | 33                     | 592    | 0.6  | 0.05               | 50   | 0.88u |

| [17] 2005        | 1       | -40~125                               | 66.7                   | 225    | 0.5  |                    |      | 4u    |

| [18] 2005        | 1.8     | 0~70                                  | 32.5                   | 615.1  | 0.18 | 0.1                | 35   | 1.6u  |

| [19] 2006        | 1.2     | -20~90                                | 61.64                  | 718    | 0.09 |                    |      | 1.6u  |

| [20] 2006        | 0.8~2.6 | -20~120                               | 64.2                   | 278    | 0.18 | 0.04               |      | 5.4u  |

Table 2.3: Researches for Current Mode of  $V_{PTAT}$  and  $V_{CTAT}$

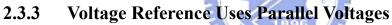

Figure 2.3.3: Circuit Architecture of Parallel Voltages (REF[21])

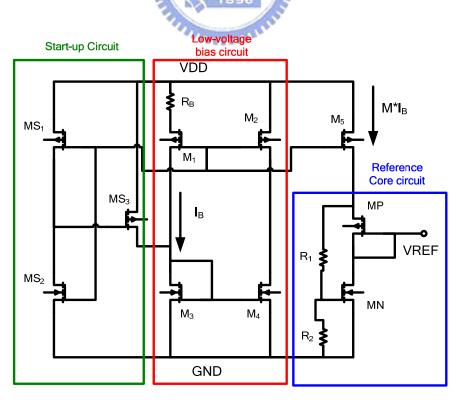

A voltage reference is necessary for LDO design, and it provides a low-supply-dependence and low-temperature-drift reference voltage to define the LDO output voltage. The circuit refers to Ref[21]: A CMOS Voltage Reference Based On Weighted  $\triangle Vgs$  For CMOS Low-Dropout Linear Regulators. It is assorted to parallel voltages. A CMOS voltage reference been implemented in a standard 0.6µm CNOS technology. The area is 0.055mm<sup>2</sup>, and the lowest supply voltage is 1.4V. A typical temperature coefficient is 36.9 ppm/°C. (Ref: [21])

The proposed CMOS voltage reference is based on the different temperature dependencies of the threshold voltages of an NMOS and a PMOS. See Fig 2.3.3, it can be divided into three parts.

- 1. **Start-up circuit:** It is formed by MS1-MS3. It uses to trigger this circuit, when the circuit operates in wrong state.

- 2. Low-voltage bias circuit: It is formed by M1-M4 and R<sub>B</sub>. It provides a stable bias current.

- Reference core circuit: It is formed by M5, MP, MN, R<sub>1</sub> and R<sub>2</sub>. Its function of V<sub>REF</sub> is showed as follows: (2-22)

$$V_{REF} = \left(1 + \frac{R_1}{R_2}\right) V_{GSn} - \left|V_{GSp}\right|$$

(2-22)

Using two parallel voltages which mean two  $V_{GS}$  to subtract is a method to produce voltage reference. But, the architecture has two disadvantages. First, two slopes of VGS is not parallel, because the two MOS is not in the same situation which means different  $V_{BS}$  and different MOS type. This will cause inexactitude voltage reference. See Table 2.4, we discover temperature coefficient of the architecture is not bad, but they almost do not have good temperature range. Second, these circuits have a disadvantage which is resistors. Because we need most current (M\*I<sub>B</sub>) run through MP and MN, resistors  $R_1$  and  $R_2$  must be large enough. This causes the resistor derivation to increase.

| PAPER     | VDD        | Temperature     | Temperature | VREF  | Tech. | AREA     | PSRR | POWER      |

|-----------|------------|-----------------|-------------|-------|-------|----------|------|------------|

| (year)    | <b>(V)</b> | Range           | Coefficient | (mV)  | (µm)  | $(mm^2)$ | (dB) | <b>(W)</b> |

|           |            | (°C)            | (ppm/°C)    |       |       |          |      |            |

| Voltage R | eference   | e Uses Parallel | Voltages    |       |       |          |      |            |

| *[21]2003 | 1.4        | 0~100           | 36.9        | 309   | 0.6   | 0.055    | 20   | 13.58u     |

| *[22]2004 | 5          | -10~80          | 32          | 2670  | 0.5   | 0.0936   |      | 970u       |

| *[23]2005 | 1.5        | 0~80            | 25          | 168   | 0.35  | 0.08     | 59   | 3.6u       |

| *[24]2006 | 1.5~4.3    | 0~80            | 12          | 891.1 | 0.35  | 0.015    | 59   | 300n       |

| [25] 2005 | 0.6~1.8    | 0~75            | 70          | 332   | 0.18  |          |      |            |

| [26] 2006 | 0.9~3.3    | -40~100         | 33          | 181   | 0.35  |          |      | 1.1u       |

Table 2.4:

Researches of Voltage Reference of Parallel Voltages

#### 2.3.4 Zero Temperature Coefficient Point (ZTC)

The circuit refers to Ref[27]: Mutual Compensation of Mobility and Threshold Voltage Temperature Effects with Applications in CMOS Circuits. It is assorted to ZTC. Mutual compensation of mobility and threshold voltage temperature variations may result in a ZTC (zero temperature coefficient) bias point of a MOS transistor. The circuit can be applied in voltage reference circuits and temperature sensors with linear dependence of voltage versus temperature. (Ref: [27])

Figure 2.3.4: Circuit Architecture of ZTC (REF[26])

See Figure 2.3.4, Q1 operates on ZTC point. To use feedback to stabilize MOS Q1, so variations will decrease. In the circuit, for transistor Q1 the following design relationship should be satisfied

$$I_{D1} = I_{DF} = V_{GS1} \frac{R_2}{R_1 R_3} = V_{GSF} \frac{R_2}{R_1 R_3}$$

(2-23)

The values of  $I_{DF} = 192\mu A$  and  $V_{GSF} = 869mV$  were considered as the parameters of the ZTC bias point at  $T=T_0=300^{\circ}K$ .

But ZTC has a problem that  $V_{REF}$  is hard to be designed in ultra low voltage. That is because MOS has no ZTC point in ultra low voltage. In Table 2.5,  $V_{REF}$  can't be lower than 600mV, even if supply voltage scales down 1V. Therefore, the architecture is hard to apply in battery-operated system.

| PAPER<br>(year) | VDD<br>(V) | Temperature<br>Range<br>(°C) | Temperature<br>Coefficient<br>(ppm/°C) | VREF<br>(mV) |      | AREA<br>(mm <sup>2</sup> ) | POWER<br>(W) |

|-----------------|------------|------------------------------|----------------------------------------|--------------|------|----------------------------|--------------|

| ZTC             |            |                              |                                        |              |      |                            |              |

| *[27]2001       | 3~3.3      | -20~100                      | 15 189                                 | 799          | 0.35 | 0.0204                     |              |

| [28]2004        | 1          | -50~150                      | 4                                      | 640          | 0.18 |                            |              |

| [29]2005        | 3.3        | -50~120                      | 50                                     | 821          | 0.35 |                            | 26.24        |

|                 |            |                              |                                        | 1264         |      |                            | 36.3u        |

Table 2.5: Researches of ZTC

#### 2.3.5 Voltage Reference Uses Non-standard Process

The circuit refers to Ref [30]: CMOS Voltage Reference Based on Gate Work Function Differences in Poly-Si Controlled by Conductivity Type and Impurity Concentration. It is assorted to special process. A new CMOS reference circuit consisting of two pairs of transistors is presented. One pair exhibits a threshold voltage difference with a negative temperature coefficient, while the other exhibits a positive temperature coefficient. (Ref: [30])

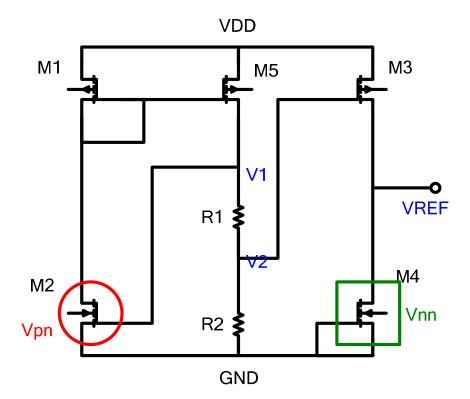

Figure 2.3.5: Circuit Architecture of Non-standard Process (REF[30])

For a pair of MOS transistors with gates of different conductivity types or different impurity concentrations, it will produce  $V_{PTAT}$  or  $V_{CTAT}$ , see Figure 2.3.6.

Figure 2.3.6: (a) Vpn and (b) Vnn as a Function of Temperature

In Figure 2.3.5, we can know

$$V_2 = \frac{R_2}{R_1 + R_2} V_1 = \frac{R_2}{R_1 + R_2} V_{pn} .$$

(2-24)

$V_{\text{pn}}$  is  $V_{\text{CTAT}}\text{,}$  and  $V_{\text{nn}}$  is  $V_{\text{PTAT}}\text{.}$   $V_{\text{REF}}$  can be shown

$$V_{\text{REF}} = V_{nn} + \frac{R_2}{R_1 + R_2} V_{pn}$$

(2-25)

We just adjust R<sub>1</sub> and R<sub>2</sub>, so V<sub>REF</sub> can be designed very well.

Although, special process needs not only standard CMOS process technique, so it may want to have special or additional process. This will cause more cost and resource, but we don't hope to see. In Table 2.6, it is researches of Non-standard Process. Some researches use floating-gate to design voltage reference, and it is also Non-standard Process.

| Table 2.0. Researches of voltage Reference of Non-standard Flocess |                                             |             |             |           |       |          |      |       |

|--------------------------------------------------------------------|---------------------------------------------|-------------|-------------|-----------|-------|----------|------|-------|

| PAPER                                                              | VDD                                         | Temperature | Temperature | VREF      | Tech. | AREA     | PSRR | POWER |

| (year)                                                             | <b>(V)</b>                                  | Range       | Coefficient | (mV)      | (µm)  | $(mm^2)$ | (dB) | (W)   |

|                                                                    |                                             | (°C)        | (ppm/°C)    |           |       |          |      |       |

| Voltage R                                                          | Voltage Reference Uses Non-standard Process |             |             |           |       |          |      |       |

| *[30]2003                                                          | 1                                           | -50~100     | 80          | 410       |       |          |      | 0.6u  |

| *[31]2004                                                          | 2.8~5.5                                     | -20~100     | 54.6        | 0.8~1.5   | 0.5   | 0.081    | 80   | 500u  |

| *[32]2005                                                          | 4.5~9                                       | -40~85      |             | 1250~5000 | 1.5   | 1.6      | 67   | 3.15u |

| *[33]2006                                                          | 1.2                                         | -60~140     | 130 185     | <u> </u>  | 0.35  | 0.0022   |      | 40u   |

| The second second                                                  |                                             |             |             |           |       |          |      |       |

Table 2.6: Researches of Voltage Reference of Non-standard Process

#### 2.3.6 Comparison of Voltage Reference

See Table 2.7, it is comparison of the above five circuit architectures. Our goal is to design voltage reference in battery-operated systems which demand low-power and small-area. Because there is no ZTC in ultra low voltage, ZTC architecture does not match with our goal. On the other hand, current mode of PTAT and CTAT architecture and parallel voltages architecture always need resistances which occupy the bigger area and cause more derivation, so they do not match our goal, too. Special process always needs additional process steps which will increase cost that we do not want to see.

|                                           | Comparison                        |

|-------------------------------------------|-----------------------------------|

| Voltage Mode of $V_{PTAT}$ and $V_{CTAT}$ | 1. Can no resistor                |

|                                           | 2. Power arrives to nano-Watt     |

| Current Mode of $V_{PTAT}$ and $V_{CTAT}$ | 1. Resistor and current trade off |

| Voltage Reference Uses Parallel Voltages  | 1. Need resistors                 |

| ZTC                                       | 1. No ZTC in ultra low voltage    |

| Voltage Reference Uses Non-standard       | 1. No apply in standard process   |

| Process                                   |                                   |

Table 2.7: Comparison for Five Kinds of CMOS Voltage References

See Table 2.8, it is researches for CMOS voltage reference, and five circuit architectures has been assorted. We can discover that performance of voltage mode is better than performance of other architectures. First, temperature coefficient is low generally at voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$ , and temperature range is wide enough. Second, power of voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$  can scale down to several dozens nW. It is very beneficial to design voltage reference in battery-operated system. Third, small area is achieved at voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$ . We can see that area is several hundred  $\mu m^2$ , and no other architectures are batter than voltage mode of  $V_{PTAT}$  and  $V_{CTAT}$ . Although, special process has the same small area, it needs additional process steps which will increase costs. Therefore, we don't consider special process.

| PAPER     | VDD       | Temperature                            | Temperature | VREF   | Tech.    | AREA     | PSRR     | POWER        |

|-----------|-----------|----------------------------------------|-------------|--------|----------|----------|----------|--------------|

| (year)    | (V)       | Range                                  | Coefficient | (mV)   | (µm)     | $(mm^2)$ | (dB)     | (W)          |

|           |           | (°C)                                   | (ppm/℃)     |        |          |          |          |              |

| Voltage M | lode of V | V <sub>PTAT</sub> and V <sub>CTA</sub> | AT          | * is 1 | hat rese | arch has | experime | ental result |

| *[1]2004  | 4.5~5     | 25~90                                  | 347         | 1320   | 0.18     |          |          |              |

| *[2]2005  | 0.9       | 0~100                                  | 39          | 514    | 0.35     | 0.12     | 22       | 780n         |

| *[3]2005  | 2         | 0~70                                   | 62          | 579    | 0.35     | 0.126    | 84       | 4.6u         |

| *[4]2006  | 0.9~4     | 0~80                                   | 10          | 670    | 0.35     | 0.045    | 40       | 63n          |

| [5] 2004  | 1.1~2.2   | -10~70                                 | 85          | 504    | 0.18     |          |          | 176u         |

| [6] 2005  | 3.3       | 0~150                                  | 26          | 711    | 0.35     |          |          |              |

| [7] 2006  | 1.3       | -50~130                                | 9           | 546    | 0.18     |          | 100      | 80u          |

| [8] 2006  | 0.5       | -40~100                                | 2.2         | 319    | 0.13     | 0.0002   | 14       | 40n          |

Table 2.8: Researches for All CMOS Voltage Reference

| Current <b>M</b> | Iode of T                                   | V <sub>PTAT</sub> and V <sub>CT</sub> | TAT      |           |      |        |    |        |

|------------------|---------------------------------------------|---------------------------------------|----------|-----------|------|--------|----|--------|

| *[9]2003         | 1.2                                         | -25~125                               | 119      | 295       | 1.2  | 0.23   | 40 | 4.32u  |

| *[10]2006        | 0.85                                        | -20~120                               | 194      | 221       | 0.18 | 0.0238 |    | 3.3u   |

| [11] 2003        | 0.6                                         | -40~100                               | 93       | 400       | 0.13 |        |    |        |

| [12] 2003        | 1.5                                         | -40~125                               | 37.88    | 800       | 0.13 |        |    | 120u   |

| [13] 2003        | 0.6~1.8                                     | 0~80                                  | 80       | 405       | 0.18 | 0.1    | 82 | 25u    |

| [14] 2004        | 3~5                                         | -60~100                               | 4        | 1165.4    | 1.2  | 0.18   |    | 30u    |

| [15] 2004        | 1                                           | -20~80                                | 200      | 400       | 0.35 |        |    | 3u     |

| [16] 2004        | 0.8                                         | 0~100                                 | 33       | 592       | 0.6  | 0.05   | 50 | 0.88u  |

| [17] 2005        | 1                                           | -40~125                               | 66.7     | 225       | 0.5  |        |    | 4u     |

| [18] 2005        | 1.8                                         | 0~70                                  | 32.5     | 615.1     | 0.18 | 0.1    | 35 | 1.6u   |

| [19] 2006        | 1.2                                         | -20~90                                | 61.64    | 718       | 0.09 |        |    | 1.6u   |

| [20] 2006        | 0.8~2.6                                     | -20~120                               | 64.2     | 278       | 0.18 | 0.04   |    | 5.4u   |