# 國立交通大學

# 電信工程學系

# 碩士論文

連續時間轉導電容式三角積分調變器之實現

Implementation of the continuous-time transconductor-capacitor Delta-Sigma modulator

## 研究生:吴國璽

指導教授:洪崇智 博士

中華民國九十六年十月

## 連續時間轉導電容式三角積分調變器之實現 Implementation of the continuous-time transconductor-capacitor Delta-Sigma modulator

研究生:吴國璽

Student : Kuo-Hsi Wu

指導教授:洪崇智

Advisor: Chung-Chih Hung

## 國 立 交 通 大 學 電信工程系 碩士論文

#### A Thesis

Submitted to Department of Communication Engineering College of Electrical Engineering and Computer Science National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of

Master

in

Communication Engineering

October 2007

Hsinchu, Taiwan, Republic of China

中華民國九十六年十月

#### 連續時間轉導電容式三角積分調變器之實現

#### 學生:吳國璽

#### 指導教授:洪崇智

#### 國立交通大學電信工程學系碩士班

#### 摘要

由於近年來無線通訊蓬勃發展,因此適用於無線通訊中的類比數位轉換器也受 到更大的矚目。一般無線通訊常為窄頻通訊,為了簡化架構通常希望類比到數位轉 換器在頻帶內可有更高的抗雜訊能力。另一方面也希望能夠在低電壓、低功率下操 作,因此,一個高解析度、低功率耗電且面積小的類比數位轉換器是很重要的。而 三角積分類比數位轉換器就非常符合這個需求,因為它在有限頻寬的限制下可以達 到非常高的解析度。除此之外,類比所佔的成份也相對比較少且對製程漂移的影響 也比較小。因此,近幾年來三角積分類比數位轉換器都扮演著非常重要的角色。

三角積分類比數位轉換器在不同的應用範圍下通常會有兩種種類,一種是離散時間三角積分類比數位轉換器,因為它通常都是用交換電容的電路下實現,所以又稱為交換電容三角積分類比數位轉換器。早期論文以離散時間三角積分類比到數位 為主,但是 2002 年以後,連續時間三角積分類比到數位則大量的被發表。原因為連續時間三角積分通常對於運算放大器的要求比較寬鬆,它不需要在一個 clock 的時間下做處理,所以耗費功率比較低,而且具有 Anti-aliasing 的性質。

因此,為了將連續時間三角積分類比數位轉換器的優點應用在通信的範圍內,此研究主題就是做出一個適用於 GSM 系統 200k 赫茲頻帶、取樣頻率 20MS/s 的低功率三階零點最佳化的連續時間轉導電容三角積分類比數位轉換器,以符合可攜式電子產品需要低消耗功率的趨勢。

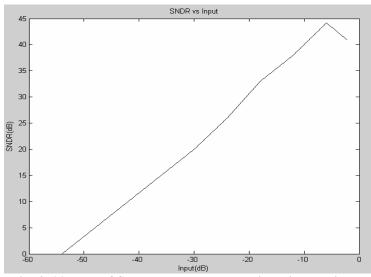

晶片是以台積電 0.18 微米標準互補式金氧半導體製程所製造。在 200k 赫茲頻 帶內的量測結果為:最大訊號雜訊失真比為 45dB,訊號雜訊比為 47.8dB,動態範 圍是 49dB,解析度為 7.2 位元,與預測結果相差約 4 位元。

### Implementation of the continuous-time transconductor-capacitor Delta-Sigma modulator

Student : Kuo-Hsi Wu

Advisors : Dr. Chung-Chih Hung

### Department of Communication Engineering National Chiao Tung University

#### Abstract

Because of the rapid growth of wireless communication, there has been more focus on analog-to-discrete converter (ADC) for wireless communication. Since the frequency is usually narrow-band in general wireless communication, in order to reduce the complexity of the architecture, we usually require the ADC has the ability of in-band anti-noise. Besides, it is important the ADC operates in low voltage, low-power, and small area. The delta-sigma ( $\Delta\Sigma$ ) ADC is very suitable for the application because they can achieve high accuracy for narrow band signals with few analog components and insensitivity to process and component variation.

Typically, there are two kinds of  $\Delta\Sigma$  ADCs. The first one is the discrete-time (DT)  $\Delta\Sigma$  ADC and the other is the continuous-time (CT)  $\Delta\Sigma$  ADC. The DT  $\Delta\Sigma$  ADC also called the switched-capacitor (SC)  $\Delta\Sigma$  ADC because of using switched capacitors. The CT  $\Delta\Sigma$  ADC obtains lots of attentions lately. Because the requirement of integrator is relaxed, it does not need to process signals within a clock time. This results in further power reduction.

In order to combine the advantages of the CT  $\Delta\Sigma$  ADC system into low-power communication system, this research focuses on low power 20MS/s sample frequency 3-rd order zero optimization CT GM-C  $\Delta\Sigma$  ADC for GSM communication system.

The chip has been fabricated by TSMC 0.18-um CMOS process. The measured peak SNDR is 45dB, SNR is 47.8dB and the DR is 49dB. The resolution is 7.2 bits that is 4 bits lower than prediction in 200k HZ signal band.

#### 誌謝

隨著這份碩士論文的完成,兩年來在交大的求學生活也即將告一個段落,往後 迎接著我的,又是另一段嶄新的人生旅程。本論文得以順利完成,首先,要感謝我 的指導教授<u>洪崇智</u>老師在我兩年的研究生活中,對我的指導與照顧,並且在研究主 題上給予我寬廣的發展空間。而類比積體電路實驗室所提供完備的軟硬體資源,讓 我在短短兩年碩士班研究中,學習到如何開始設計類比積體電路,乃至於量測電路, 甚至單獨面對及思考問題的所在。此外要感謝<u>李育民</u>教授、<u>黃淑娟</u>教授、<u>陳科宏</u>教 授撥冗擔任我的口試委員並提供寶貴意見,使得本論文更為完整。也感謝國家晶片 系統設計中心提供先進的半導體製程,讓我有機會將所設計的電路加以實現並完成 驗證。

另一方面,要感謝所有類比積體電路實驗室的成員兩年來的互相照顧與扶持。 首先,感謝博士班的學長<u>羅天佑、薛文弘、廖介偉、黃哲揚</u>以及已畢業的碩士班學 長<u>何俊達、黃琳家、蔡宗諺、林政翰、楊家泰和陳家敏</u>在研究上所給予我的幫助與 鼓勵,尤其是俊達學長,由於他平時不吝惜的賜教與量測晶片時給予的幫助,使得 我的論文研究得以順利完成。另外我要感謝<u>白逸維、邱建豪、廖德文、高正昇、林</u> 明澤、黃旭右和傳崇賢等諸位同窗,透過平日與你們的切磋討論,使我不論在課業 上,或研究上都得到了不少收穫。尤其是718實驗室的同學們,兩年來陪我一塊兒努 力奮鬥,一起渡過同甘苦的日子,也因為你們,讓我的碩士班生活更加多采多姿, 增添許多快樂與充實的回憶。此外也感謝學弟們<u>林永洲、郭智龍、夏竹緯、楊文霖</u>, <u>邱楓翔</u>,黃介仁的加入,讓實驗室注入一股新的活力與朝氣。另外感謝好友<u>呂玉玲</u>, 在我低潮時陪伴我,讓我有勇氣面對接下來的挑戰。感謝新竹伙食團所有夥伴,讓 我吃飽睡好,體力充沛。

到這邊,特別要致上最深的感謝給我的父母及家人們,謝謝你們從小到大所給 予我的栽培、照顧與鼓勵,讓我得以無後顧之憂地完成學業,朝自己的理想邁進, 衷心感謝你們對我的付出。

最後,所有關心我、愛護我和曾經幫助過我的人,願我在未來的人生能有一絲 的榮耀歸予你們,謝謝你們。要感謝的人事物太多了,那就謝天吧!

> 吴國璽 于 交通大學工程四館 718 實驗室 2007.10.9

## Contents

| 摘要                                                                    | I    |

|-----------------------------------------------------------------------|------|

| Abstract                                                              | .II  |

| 誌謝                                                                    |      |

| Contents                                                              | IV   |

| List of figures                                                       |      |

| List of tables                                                        |      |

|                                                                       |      |

| CH1 Introduction                                                      | 1    |

| 1.1 Research Motivation                                               | 1    |

| CH2 Problem Definition                                                | 3    |

| 2.1 Continuous-Time vs. Discrete-Time $\Delta\Sigma$ Modulators       | 3    |

| 2.2 Single-bit vs. multi-bits $\Delta\Sigma$ Modulators               |      |

| 2.3 Active RC vs. GM-C filter $\Delta\Sigma$ Modulators               |      |

| 2.4 Conclusion                                                        | 9    |

| CH3 An Overview of Sigma Delta Data Converters                        | .10  |

| 3.1 Introduction                                                      |      |

| 3.2 Overview of Analog-to-Digital Data Converters                     | . 10 |

| 3.2.1 Categories of Analog-to-Digital Data Converters                 |      |

| 3.2.2 Over-sampling Ratio (OSR)                                       |      |

| 3.2.3 Signal to Noise Ratio (SNR) & Spurious Free Dynamic Range (SNDR | 12   |

| 3.2.4 Spurious Free Dynamic Range (SFDR)                              | . 12 |

| 3.2.5 Dynamic Range at the input (DR)                                 |      |

| 3.2.6 Effective Number of Bits (ENOB)                                 |      |

| 3.2.7 Overload Level (OL)                                             |      |

| 3.3 Sampling Theorem                                                  |      |

| 3.4 Quantization Noise                                                |      |

| 3.5 Over-sampling Technique                                           |      |

| 3.6 Noise Shaping                                                     |      |

| 3.6.1 Architecture of noise shaping                                   |      |

| 3.6.2 First-Order $\Delta\Sigma$ Modulator                            |      |

| 3.6.3 Second-Order $\Delta\Sigma$ Modulator                           |      |

| 3.6.4 Higher-Order $\Delta\Sigma$ Modulator                           |      |

| 3.6.5 System Analysis of $\Delta\Sigma$ Analog-to-Digital Converters  |      |

| 3.7 Conclusion                                                        |      |

| CH4 Transformation of a Discrete-Time to Continuous-Time              |      |

| 4.1 Introduction                                                      |      |

| 4.2 The Impulse-Invariant Transform                                   |      |

| 4.3 NRZ Transformation                                                |      |

| 4.3.1 Effect of Excess Loop Delay                                     |      |

| 4.3.2 Root locus of effect of Excess Loop Delay                       |      |

| CH5 Implementation of Low-Power GM-C Continuous-Time SDM              | .46  |

| 5.1 Introduction                                                 | 46 |

|------------------------------------------------------------------|----|

| 5.2 Behavior Simulation                                          | 46 |

| 5.2.1 Determine the coefficients for CRFB structure              | 46 |

| 5.2.2 Transfer coefficient from discrete-time to continuous-time | 49 |

| 5.2.3 Optimization of the NTF zeros                              | 51 |

| 5.3 Circuit level Simulation                                     | 52 |

| 5.3.1 GM cell                                                    | 53 |

| 5.3.2 Comparator                                                 | 58 |

| 5.3.3 Feedback DAC                                               | 59 |

| 5.4 Simulation Result                                            | 61 |

| 5.5 Layout level design                                          | 62 |

| CH6 Test Setup and Experimental Results                          | 64 |

| 6.1 Measuring equipment                                          |    |

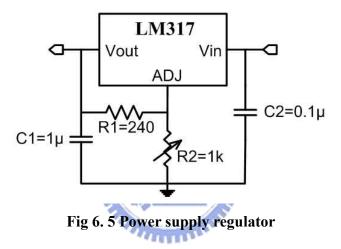

| 6.2 Power supply regulators                                      |    |

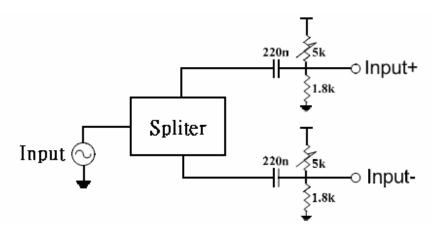

| 6.3 Input terminal circuit                                       |    |

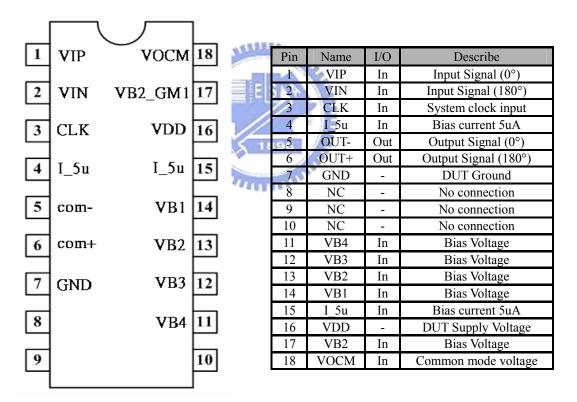

| 6.4 Pin configuration and testing board                          |    |

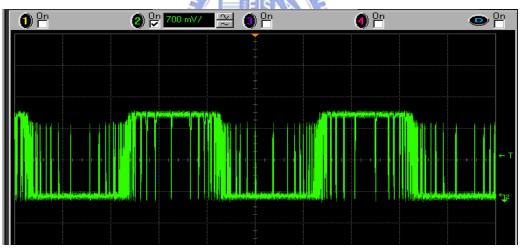

| 6.5 Performance evaluations of SDM                               |    |

| 6.6 Summary                                                      | 70 |

| CH7 Conclusions                                                  |    |

| Bibliography                                                     |    |

| 2                                                                |    |

# List of figures

| Fig 1. 1 Application of $\Delta\Sigma$ ADC in communication receiver                                   | 1  |

|--------------------------------------------------------------------------------------------------------|----|

| Fig 2. 1 Discrete-time $\Delta\Sigma$ modulator                                                        | 3  |

| Fig 2. 2 Continuous-time $\Delta\Sigma$ modulator                                                      | 4  |

| Fig 3. 1 A/D Converter technologies, resolution and bandwidth                                          | 11 |

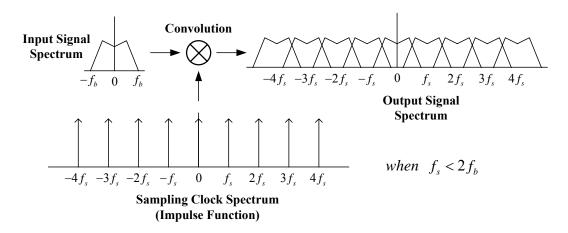

| Fig 3. 2 Illustration of the aliasing of the sampling process $(f_s < 2f_b)$                           | 13 |

| Fig 3. 3 Illustration of the aliasing of the sampling process $(2f_b \le f_{ns})$                      |    |

| Fig 3. 4 Quantized signal                                                                              | 15 |

| Fig 3. 5 Quantizer and its linear model                                                                |    |

| Fig 3. 6 The pdf of quantization noise                                                                 |    |

| Fig 3. 7 Power spectrum density of q(n)                                                                | 17 |

| Fig 3. 8(a)Quantization noise power spectrum density for Nyquist-rate                                  | 19 |

| Fig 3. 9 (a) Over-sampling conversion with digital low-pass filter                                     | 19 |

| Fig 3. 10 Block diagram of (a) a noise-shaped SDM and (b) its linear model                             | 21 |

| Fig 3. 11 The First-Order SDM                                                                          | 22 |

| Fig 3. 12 The Second-Order SDM                                                                         | 25 |

| Fig 3. 13 Power spectrum density of 1 <sup>st</sup> order, 2 <sup>nd</sup> order noise-shaping and non |    |

| noise-shaping strategy                                                                                 | 27 |

| Fig 3. 14 Magnitude of NTF                                                                             | 27 |

| Fig 3. 15 The Higher-Order SDM                                                                         | 28 |

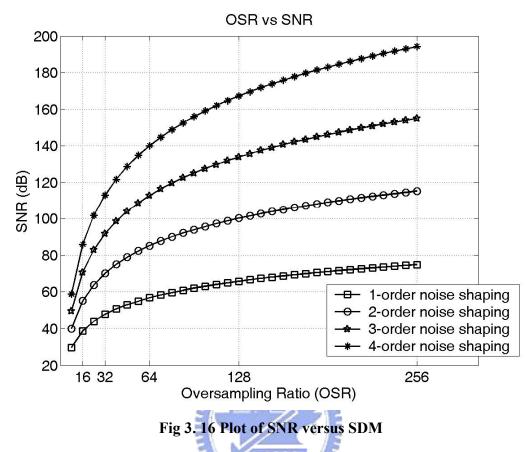

| Fig 3. 16 Plot of SNR versus SDM                                                                       |    |

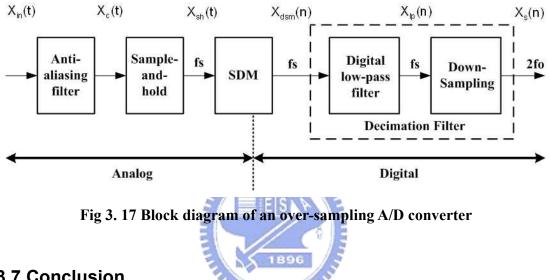

| Fig 3. 17 Block diagram of an over-sampling A/D converter                                              |    |

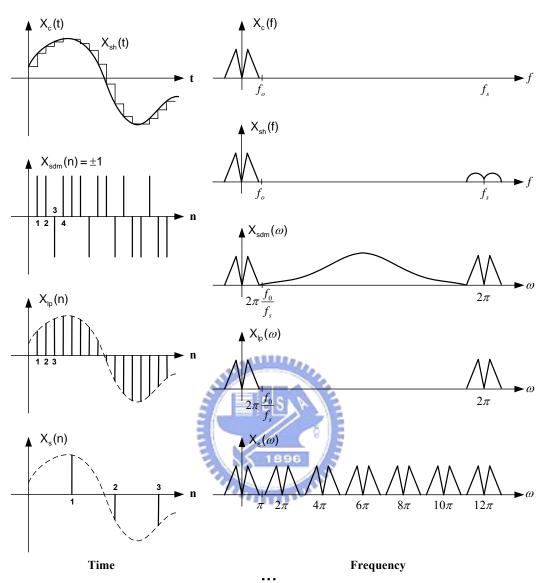

| Fig 3. 18 Signal and spectra in an over-sampling ADC                                                   |    |

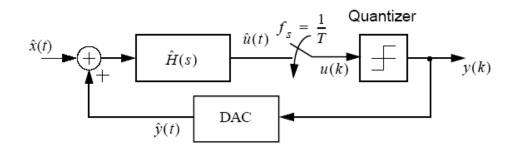

| Fig 4. 1 continuous-time ΔΣmodulator<br>Fig 4. 2 ΔΣ open loop block diagram                            | 34 |

|                                                                                                        |    |

| Fig 4. 3 Open-loop impulse response of the second-order low-pass modulator                             |    |

| Fig 4. 4 A continuous-time ΔΣmodulator in S-domain                                                     |    |

| Fig 4. 5 The DAC pulse                                                                                 |    |

| Fig 4. 6 Illustrations of excess loop delay on NRZ DAC pulse                                           |    |

| Fig 4. 7 The delayed NRZ pulse as a linear combination                                                 |    |

| Fig 4. 8 Linear SDM with one-bit quantizer arbitrary gain k.                                           |    |

| Fig 4. 9 Effect of loop delay on root locus of $NTF(z, \tau_d)$                                        | 45 |

| Fig 5. 1 MATLAB code for creating a low-pass NTF                                                       |    |

| Fig 5. 2 MATLAB code with coefficient and CRFB structure                                               | 49 |

| Fig 5. 3 A CIFB $\Delta\Sigma$ structure                                                               |    |

| Fig 5. 4 CRFB continuous-time $\Delta\Sigma$ in time domain                                            |    |

| Fig 5. 5 The time-domain output data                                                                   |    |

| Fig 5. 6 The power spectrum of output data                                                             |    |

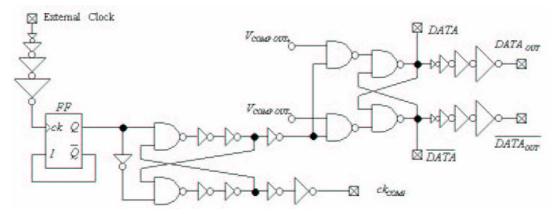

| Fig 5. 7 Implementation of third-order GM-C continuous-time SDM                                        |    |

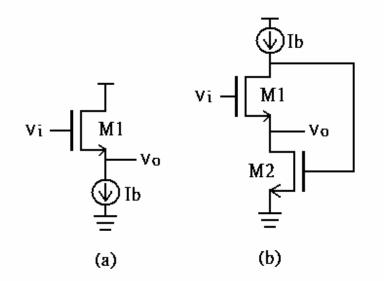

| Fig 5. 8 (a) Common-drain amplifier (voltage follower)       (b) FVF.                                  |    |

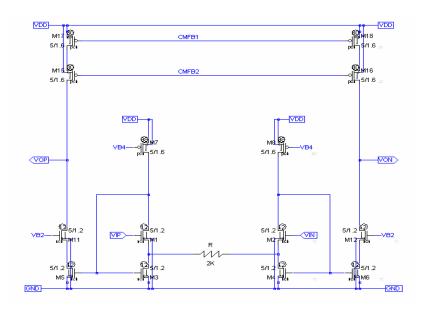

| Fig 5. 9 Schematic of FVF GM                                                                           | 55 |

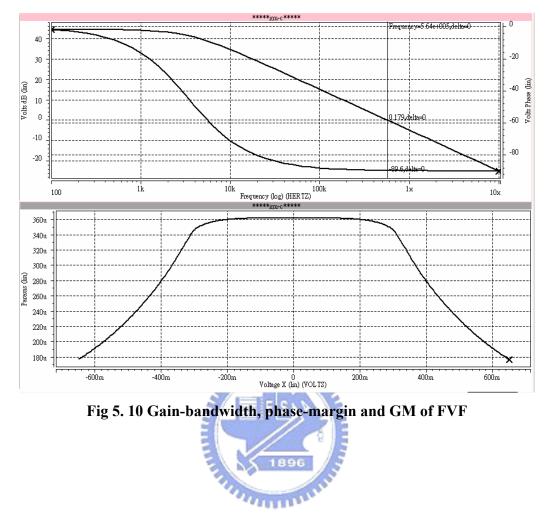

| Fig 5. 10 Gain-bandwidth, phase-margin and GM of FVF                                                   | 56 |

| Fig 5. 11 Schematic of 2 <sup>nd</sup> , 3 <sup>rd</sup> source degeneration GM                        | 57 |

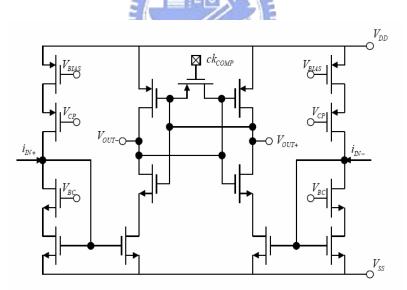

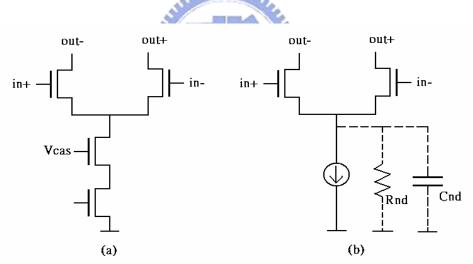

| Fig 5. 12 Current-Mode Comparator                                              | 58   |

|--------------------------------------------------------------------------------|------|

| Fig 5. 13 Comparator latch and sampling clock                                  | 59   |

| Fig 5. 14 (a) The cascade transistors DAC. (b) DAC with ideal current source.  | 59   |

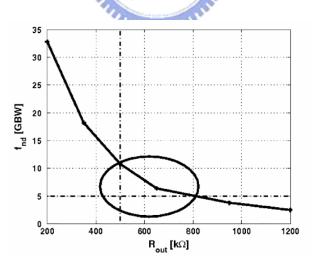

| Fig 5. 15 Tradeoff between dc output resistance and the non-dominant pole. [20 | ] 60 |

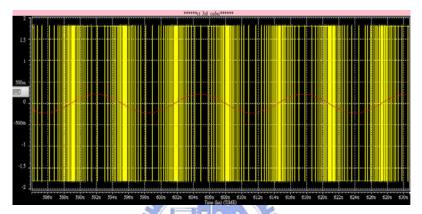

| Fig 5. 16 The simulation of continuous-time GM-C SDM in time-domain            | 61   |

| Fig 5. 17 The power spectrum of continuous-time GM-C SDM                       | 61   |

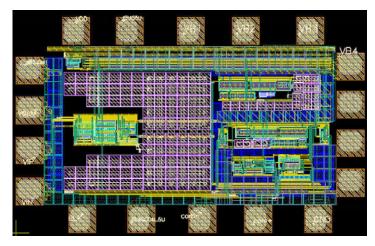

| Fig 5. 18 Diagram of SDM layout                                                | 63   |

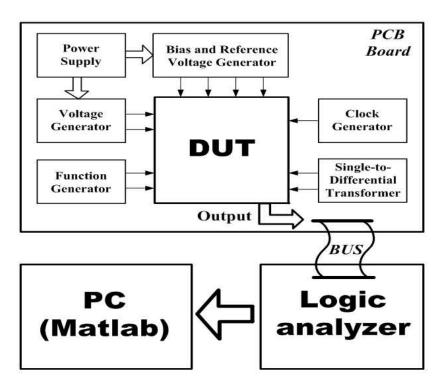

| Fig 6. 1 Experimental testing setup                                            | 64   |

| Fig 6. 2 Function generator Agilent 33250A                                     | 65   |

| Fig 6. 3 Logic analyzer Agilent 16702B                                         | 65   |

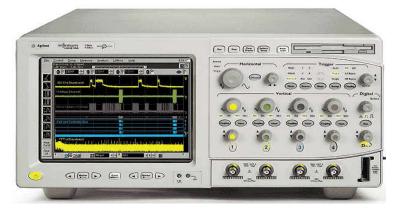

| Fig 6. 4 Oscilloscope Agilent S4832D                                           | 65   |

| Fig 6. 5 Power supply regulator                                                | 66   |

| Fig 6. 6 Input terminal circuit                                                | 67   |

| Fig 6. 7(a) Pin configuration diagram and (b) Pin assignment                   | 67   |

| Fig 6. 8 Photograph of the SDM DUT board                                       | 68   |

| Fig 6. 9 Measurement result of output waveform                                 | 68   |

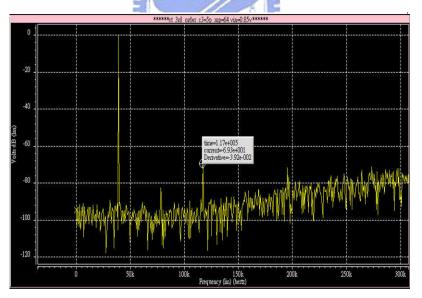

| Fig 6. 10 Measured output spectrum                                             |      |

| Fig 6. 11 Plot of SNDR versus normalized input signal                          | 69   |

# List of tables

| Table 2.1 Main advantages of continuous-time $\Sigma\Delta$ modulators over DT $\Sigma\Delta$ |    |

|-----------------------------------------------------------------------------------------------|----|

| modulators                                                                                    | 6  |

| Table 2.2 Main disadvantages of continuous-time $\Sigma\Delta$ modulators compared to I       | ЭТ |

| ΣΔ modulators                                                                                 | 6  |

| Table 4.1 s-domain equivalences for z-domain loop filter poles [12]                           | 40 |

| Table 5.1 The zero placements for minimum in-band noise                                       | 52 |

| Table 5.2 Specification of the first amplifier                                                | 57 |

| Table 5.3 The specification of the continuous-time GM-C SDM.                                  | 62 |

| Table 6.1 Summary of measured results of the SDM                                              | 70 |

## **CH1** Introduction

#### **1.1 Research Motivation**

Nowadays, the demand for the wide band communications is driving the advancement of the digital modulation techniques and the increasing complexity of circuits. For this purpose, the analog signal processing is replaced with the digital signal processing circuit in the receiver.

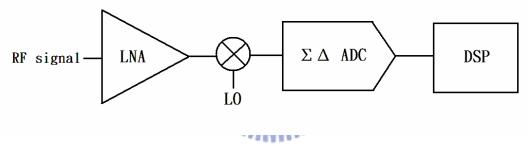

Besides this, the complexity and single-chip integration of the analog circuit in the receiver chain can also be implemented by a proper architecture. As shown in Fig.1.1, by pushing the A/D converters close to the antenna, the total analog components in the receiver chain will be reduced.

Fig 1. 1 Application of  $\Delta\Sigma$  ADC in communication receiver

Many design challenges, however, exist when the A/D converters move close to the antenna. It is challenging to achieve high-resolution, low-voltage and low-power operation in high-performance communication systems. Without the switched -capacitor circuits in continuous-time delta-sigma ADCs, the requirements of the transconductance amplifiers(GM) are more relaxed and the power consumption of the GM are thus greatly reduced. In addition to this, the speed of the continuous-time circuits is not limited to the settling time of the charge, and the wide bandwidth is more easily attained. The over-sampling techniques with noise shaping strategy are widely used to implement the analog-to-digital interface between analog and digital domain in digital systems. This type of systems require high resolution or low power consumption. Sigma-delta data

converters have meaningful advantages over traditional Nyquist-rate counterparts. The anti-aliasing filter is usually in front of the switched capacitor circuits to avoid the aliasing effect. However the filter is not required in the continuous-time delta-sigma ADC, that further simplify the receiver design.

## **CH2** Problem Definition

## 2.1 Continuous-Time vs. Discrete-Time ΔΣ Modulators

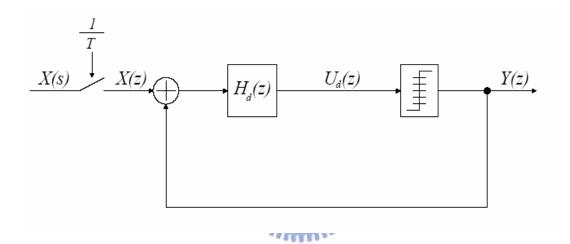

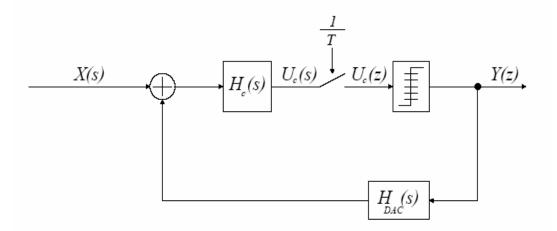

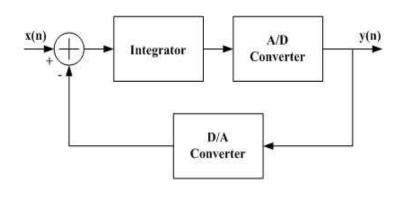

The general structures of DT and CT  $\Sigma\Delta$  modulators are shown in Figures 2.1 and 2.2 respectively.

In the following we will discuss the main advantages of CT  $\Sigma\Delta$  modulators over their DT counterparts.

Fig 2. 1 Discrete-time  $\Delta\Sigma$  modulator

#### Low Voltage Operation:

The continuously decreasing supply voltage of recent CMOS technologies is causing important limitations to the performances of switched-capacitor circuits. Switch-bootstrapping or switched-OPamp circuit techniques are now necessary in order to obtain sufficiently low on-resistances.

Fig 2. 2 Continuous-time  $\Delta \Sigma$  modulator

#### **Sampling Frequency:**

In switched-capacitor circuits several errors occur while sampling the input signal. These errors are due to the switch non-linearity, charge injection, clock feedthrough and finite settling time. Sampling errors in switched-capacitor circuits limit the sampling frequency, fs, of DT  $\Sigma\Delta$  modulators.

In CT modulators sampling occurs inside the  $\Sigma\Delta$  loop, therefore sampling errors are shaped out of the frequency band of interest just like quantization noise.

#### **Power Consumption:**

In switched-capacitor circuits the unity gain frequency of operational amplifiers must be at least five times the sample rate. High quiescent current is then required to achieve high bandwith. On the other hand, unity gain frequencies of the integrators in the CT  $\Sigma\Delta$ are usually lower than the sampling frequency.

Furthermore, since sampling occurs inside the  $\Sigma\Delta$  loop, this strongly reduces:

- . Thermal noise is aliasing in the frequency band of interest.

- . Aliasing of out of band signals, so that the antialiasing filter may be eliminated.

It is then expected that for the same specifications, CT  $\Sigma\Delta$  modulators will have lower

power consumption than their DT counterparts.

It has also been shown, in [1], that CT  $\Sigma\Delta$  modulators are less sensitive to asynchronous substrate interference from neighboring digital circuitry than DT  $\Sigma\Delta$  modulators. This will be an important issue for future SOC (System on Chip) design.

While DT  $\Sigma\Delta$  modulators are insensitive to the shape of the feedback signal as long as full settling occurs, the main disadvantages of CT  $\Sigma\Delta$  modulators are related to switching characteristics of the feedback signal:

#### **Excess Loop Delay:**

The delay in the feedback signal is mainly due to the comparator response-time. This delay has been found to alter the frequency response and degrade the signal-to-noise ratio (SNR) of the CT  $\Sigma\Delta$  modulators. Using a Return-to-Zero (RZ) feedback signal gives enough time for the comparator output to settle and thus eliminates any influence of the comparator delay on the SNR.

#### DAC Output Rise and Fall Time Asymmetry:

Unequal rise and fall times of the DAC output current introduces harmonic distortion. The effect of this waveform asymmetry can also be highly attenuated by the use of a RZ feedback DAC.

#### **Clock Jitter:**

Clock jitter in feedback signal increases the noise level in the signal band. Unlike excess loop delay and DAC waveform asymmetry, clock jitter influence on the CT modulators cannot be attenuated by a RZ feedback signal.

After this discussion on the advantages and disadvantages of CT  $\Sigma\Delta$  modulators compared to the DT  $\Sigma\Delta$  modulators (summarized in tables 2.1 and 2.2), we believe that CT modulators will play an important role in recent and future CMOS technologies. This is mainly because of their advantages concerning low voltage, low power and high sampling frequency.

# Table 2.1 Main advantages of continuous-time $\Sigma\Delta$ modulators over DT $\Sigma\Delta$ modulators

|                         | DISCRETE-TIME $\Sigma\Delta$          | CONTINUOUS-TIME $\Sigma\Delta$ |

|-------------------------|---------------------------------------|--------------------------------|

| Input Switch Resistance | $r_{ds} = rac{1}{eta(V_{gs} - V_t)}$ | No input switches              |

| Sampling Errors         | Critical                              | Shaped out of band             |

| Unity Gain Frequency    | $f_T = 5 * f_s$                       | $f_T \leq f_s$                 |

| Thermal Noise Aliasing  | Increases noise level                 | Highly attenuated              |

| Anti-Aliasing Filter    | Essential                             | May be discarded               |

Table 2.2 Main disadvantages of continuous-time  $\Sigma \Delta$  modulators compared to DT  $\Sigma \Delta$  modulators

|                              | DISCRETE-TIME $\Sigma\Delta$ | CONTINUOUS-TIME $\Sigma\Delta$ |

|------------------------------|------------------------------|--------------------------------|

| Excess Loop Delay            | Low sensitivity              | SNR degradation                |

| Rise and Fall Time Asymmetry | Low sensitivity              | Introduces harmonic distortion |

| Clock Jitter                 | Low sensitivity              | Increases noise level          |

In the following, we will discuss the main difficulties and the different issues associated with the design and implementation of CT  $\Sigma\Delta$  modulators.

#### 2.2 Single-bit vs. multi-bits $\Delta\Sigma$ Modulators

The ADC resolution at a low OSR can be improved by using a higher-order loop filter, and/or by increasing the internal quantizer resolution. For single-bit, single-loop modulators, the integrator's gain must be reduced to preserve the loop stability. Therefore, simply increasing the loop filter order at a low OSR will result in a poor SNR improvement.

Since multibit quantizers have a more linear gain than single-bit quantizers, the stability of multibit, single-loop SD modulators is significantly improved. As a result, more aggressive noise transfer function can be designed, with the benefit of extra dynamic range for every additional bits n of DR  $\propto 20 \log (2^n - 1) dB$ .

Alternatively, increasing quantizer resolution enables us to use a lower noise-shaping filter for a given OSR. Unfortunately, it is necessary to double the number of comparators for each additional bit of quantizer resolution. Obviously, this costs silicon area as well as

power dissipation and thus degrades the FOM for a given resolution In addition, multi-bits SD ADCs are sensitive to non-idealities such as mismatch in the feedback digital-to-analog converter (DAC), as these errors are added directly to the input signal and are thus not noise-shaped.

Nevertheless, deep-submicron technologies feature excellent matching characteristic as high as 11 bits or 12 bits of resolution. Hence, careful layout and design can fulfill linearity requirements of an internal-feedback DAC, provided that the SD ADC is lower than 12-bit resolution, which is typically the case for W-CDMA.

For a SD ADC's resolution that exceeds the matching possibilities of CMOS or Bi-CMOS, this problem must be addressed. The solution consists of using dynamic element matching (DEM).

DEM converts the DAC element errors to high frequency noise. Thereby, highly linear over-sampling DAC can be built with only moderate matching requirements for the DAC element.

DEM techniques have been developed since 1998, starting with randomization of the DAC elements. The methods are continuously improved with respect to implementation efficiency and order of shaping. Since the presentation of [2] in 1995 and the disclosure of the ADC design in 1997, these techniques have been well established in the sigma

delta design community, allowing efficient and robust implementation of sigma-delta ADC's with resolution of more than 14 bits and bandwidth beyond 1 MHz.

However, the single bit should be preferred to multi-bit SD ADCs when the conversion bandwidth is lower than 5 MHz (GSM, Bluetooth, W-CDMA) because they achieved better FOM and are less silicon area-consuming.

#### 2.3 Active RC vs. GM-C filter $\Delta\Sigma$ Modulators

Active RC integrator has an amplifier in feedback loop and gives better **linearity performance** than a GM-C integrator. In a GM-C integrator, the transconductor is in open loop and hence you would expect lower linearity than an amplifier operating in a feedback loop.

In a CT sigma-delta (or for that matter any sigma-delta), the linearity of the overall system is limited by the linearity of the first stage and the linearity of the DAC connected to the first stage (higher OSR helps to suppress this requirement to some extent). The linearity of the subsequent stages is masked by the loop gain upto that stage, so the 2nd and 3rd stage does not have very stringent linearity requirements. Because of this reason, **it is preferable to have active-RC integrator as first stage**.

The main disadvantage of active-RC is that the **amplifier bandwidth** has to be high enough to operate in feedback configuration. In addition, it needs to have **enough gain** in the signal bandwidth to provide good linearity (linearity is related to gain at that frequency, **higher the amplifier gain** in the signal frequency, better is the linearity). The gm of GM-C integrator has lower gain bandwidth requirement since it operates in open loop and hence can consume lower power.

So in terms of power optimization, first stage has active-RC (higher power) and subsequent stages have GM-C (lower power). Overall, this arrangement gives best performance optimum power consumption.

However, linearity of the DAC connected to the first stage should be => linearity of the

first stage active-RC integrator.

Advantage of an all GM-C would be lower power at the cost of lower linearity. Input referred noise comparison cannot be generalized as it depends on the value of R in the active-RC integrator, but the R values can be adjusted such that input referred noise of active-RC integrator can be made lower than the GM-C integrator, which implies a higher dynamic range if active-RC integrator is used as the first stage.

#### 2.4 Conclusion

The published SD ADCs for wireless applications have been reviewed for the 2002-2004 period. Since 2003, there has been a strong trend to increase the bandwidth conversion while keeping reasonable clock frequency. This means that the OSR tends to decrease.

As a result, multi-bit SD loops are preferred for bandwidth demanding applications such as WLAN. However, single-bit SD modulators are recommended for wireless applications that require less than 5 MHz conversion bandwidth because they offer better trade-offs for power, area and circuit complexity. Moreover **CT SD modulators** are suited for a **low-cost integration** because they provide anti-aliasing filtering without silicon-area penalty and can potentially operate with less power consumption than DT implementation. At least, **single loop topology is preferable in low-voltage, low-power designs** because it is less sensitive to analog circuit non-idealities, such as insufficient op-amp dc gain that tends to decrease at each CMOS technology node.

# CH3 An Overview of Sigma Delta Data

## Converters

### 3.1 Introduction

This chapter reviews the basic concept of design the sigma-delta data converter. The discussion begins with a brief overview of data converter in the aspects of speed, resolution, and architecture. After this issue, the theories of how sigma-delta modulators work including sampling, quantization, over-sampling, and noise shaping will be discussed. Following the introduction, tradeoffs of various sigma-delta modulator architectures will be discussed.

#### and the second

## 3.2 Overview of Analog-to-Digital Data Converters

The operations of analog-to-digital data converters can be roughly separated into two steps: sampling and quantization. The process of sampling transforms continuous time analog signals into discrete time step-like signals. The process of quantization converts the step-like signals to a set of discrete levels. Then, these discrete levels signals can be coded and be transmitted into DSP units or digital systems.

#### 3.2.1 Categories of Analog-to-Digital Data Converters

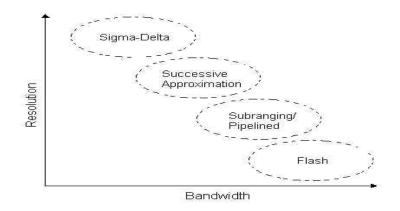

According to operation, speed, and accuracy, there are three categories of analogto-digital converter shown in Fig.3.1. Each category is applied in different field. But the demarcation for some structures nowadays is a little blurred.

Fig 3. 1 A/D Converter technologies, resolution and bandwidth

#### 3.2.2 Over-sampling Ratio (OSR)

The over-sampling ratio (OSR) of a data converter is defined as

$$OSR = \frac{f_s}{2f_b}$$

(3.1)

where  $f_s$  is the sampling frequency and  $f_b$  is the signal bandwidth. When the OSR is equal to 1 ( $f_s = 2f_b$ ), it means the data converter is the Nyqist-rate data converter, however, when the OSR is great than 1, it means the data converter is the over-sampling data converter. The OSR is the important parameter for over-sampling data converters. The OSR increases the SNR by  $(2n+1)\cdot 3dB$  or by 2n+1 per octave, where n is the order of loop-filter.

The larger the OSR, the larger the sampling frequency when the signal bandwidth is fixed. Thus, it will need faster circuit and consume more power consumption. But the OSR need to keep as low as possible for high signal bandwidth consideration. In order to obtain the advantages of using noise- shaping strategy, the OSR should be at least 4 [3].

#### 3.2.3 Signal to Noise Ratio (SNR) & Spurious Free Dynamic Range (SNDR)

The signal-to-noise ratio (SNR) of a data converter is the ratio of the signal power to the noise power, which measured at the output of the data converter. The maximum SNR that a converter can achieve is called the peak signal-to-noise ratio. Generally, the theoretical value of SNR for an N-bit Nyquist-rate ADC is given by

$$SNR = 6.02 \cdot N + 1.76 \quad dB$$

(3.2)

But for over-sampling ADC, the theoretical value of SNR is

$$SNR = 6.02 \cdot N + 1.76 + 10\log(OSR) \, dB \tag{3.3}$$

The signal to noise and distortion ratio (SNDR) of a data converter is the ratio of the signal power to the power of the noise plus the harmonic distortion components, which measured at the output of the data converter. The maximum SNDR that a converter can achieve is called the peak signal to noise and distortion ratio. Generally, SNDR is lower than SNR.

### 3.2.4 Spurious Free Dynamic Range (SFDR)

The spurious free dynamic range (SFDR) is defined as the ratio of rms value of amplitude of the fundamental signal to the rms value of the largest harmonic distortion component in a specified frequency range. SFDR may be much larger than SNDR of a data converter.

#### 3.2.5 Dynamic Range at the input (DR)

The dynamic range is defined as the ratio between the power of the largest input signal which didn't significantly degrade the performance and the power of the smallest detectable input signal which is determined by the noise floor of converters.

#### 3.2.6 Effective Number of Bits (ENOB)

For data converter, a specification often used in place of the SNR or SNDR is ENOB, which is a global indication of how many bits would be required to get the same performance as the converter. ENOB can be defined as follows:

$$ENOB = \frac{SNDR - 1.76}{6.02} \quad bits \,. \tag{3.4}$$

#### 3.2.7 Overload Level (OL)

OL is defined as the relative input amplitude where the SNR is decreased by 6dB compared to peak SNR value.

#### 3.3 Sampling Theorem

Naturally, signals transmitted in the air are analog whether they originate from. The analog signals need to be sampled to become the digital signals for suitability in processing in the digital system. Thus, sampling is a very important procedure in the front end of the overall system. How much information can be preserve from the original signals depend on how fine to sample the signals and deal. It is crucial to choose the sampling frequency with a fixed signal bandwidth. And the relationship between the sampling frequency,  $f_s$ , and the signal bandwidth,  $f_b$ , is shown as follows :

$$f_s \ge 2f_b \tag{3.5}$$

At least the sampling frequency must be greater than twice the input signal bandwidth to avoid aliasing. If  $f_s$  is smaller than twice the signal bandwidth, aliasing will occur at the output signal spectrum as shown in Figure 3.2.

Fig 3. 2 Illustration of the aliasing of the sampling process  $(f_s < 2f_b)$

To deal with these problems is increasing  $f_s$  to new sampling frequency  $f_{ns}$  in

order to match the equation. The frequency  $f_{ns}$  show be larger than  $2f_b$ . This is more popular to deal with aliasing problems because there is no information of original input signal loss as shown in Figure 3.3. And just a low pass filter at the output is needed to recover the original signal.

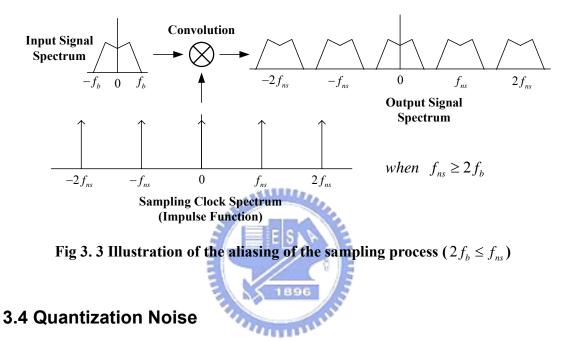

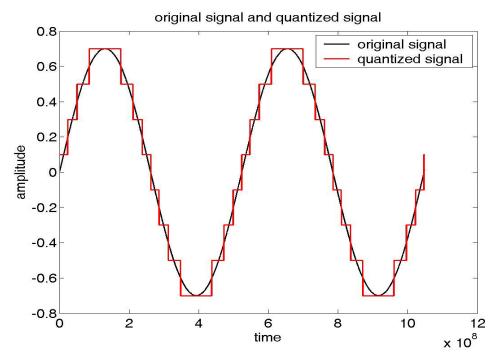

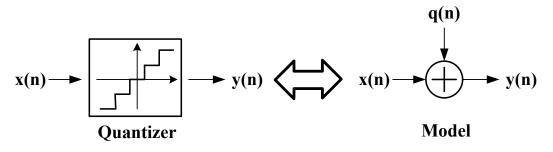

The quantizer is the interface between analog and digital domain. Once the analog signals pass through the quantizer, the signals will be digitized and separated into several different levels. The space between two adjacent levels is called a step size,  $\Delta$ . There are two types of quantizer. One is uniform, and another is non-uniform. In a uniform quantizer, the distance between two adjacent levels is uniform; otherwise it is a non-uniform quantizer.

The process of quantization introduces an error, q(n). The error is defined as the difference between the input signal, x(n), and the output signal, y(n). And it is called the quantization error. Figure 3.4 and Figure show the quantization process and assume the quantizer is uniform.

Many of the original results and insights into the behavior of quantization error are due

to Bennett [4]. Bennett first developed conditions under which quantization noise could be reasonably modeled as additive white noise. A common statement of the approximation is that the quantization error has the following properties, which we call it the "input-independent additive white-noise approximation" [5]:

- **a.** q(n) is statistically independent of the input signal

- **b.** q(n) is uniformly distributed in  $[-\Delta/2, \Delta/2]$

- **c.** q(n) is an independent identically distributed sequence or q[n] has a flat power spectral density (white).

Fig 3. 4 Quantized signal

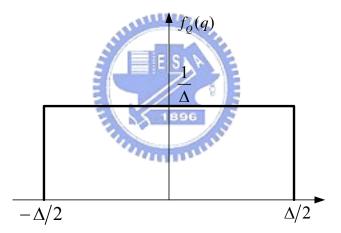

Since the quantization noise, q(n), is equal to y(n)-x(n), a quantizer can be modeled as shown in Figure 3.5 [6]. For a uniform quantizer, if the input signal does not overload, the quantization error will be bounded by  $\pm \Delta/2$ . If the  $\Delta$  is very small, it is convenient and reasonable to assume the quantization noise is zero mean and uniform distribution (Figure 3.6). The probability density function (pdf) of the quantization noise can be express as

$$f_{\mathcal{Q}}(q) = \begin{cases} 1/\Delta, & -\Delta/2 \le q(n) \le \Delta/2\\ 0, & \text{otherwise} \end{cases}$$

(3.6)

Fig 3. 5 Quantizer and its linear model

Fig 3. 6 The pdf of quantization noise

From Figure 3.6, the power of quantization noise can be shown as follows:

$$P_{Q,noise} = \frac{1}{\Delta} \int_{-\Delta/2}^{\Delta/2} q^2 dq = \frac{\Delta^2}{12}$$

(3.7)

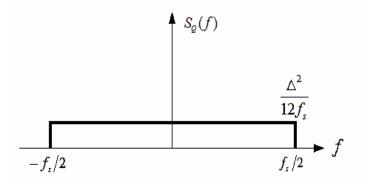

The power spectrum density of q(n),  $S_Q(f)$ , within the range of  $\pm f_s$  calculated using the equation (3.8) is

$$P_{Q,noise} = \frac{\Delta^2}{12} = \int_{-f_s/2}^{f_s/2} S_Q(f) df$$

(3.8)

And we obtain the final result of  $S_Q(f)$  as

$$S_{Q}(f) = \frac{\Delta}{12f_{s}} \tag{3.9}$$

From equation (3.9) we show that power spectrum density is inversely proportional to sampling frequency shown in Figure 3.7. The larger the sampling frequency is, the less the noise amplitude is.

Fig 3. 7 Power spectrum density of q(n)

Assume the quantization signal is uniformly distributed over the range  $\pm V_A$ , and *N* is the bits per sample. The step size can be write as

$$\Delta = \frac{2V_A}{2^N} \tag{3.10}$$

According to the equations above, the SNR can be shown as

$$SNR = 10\log\frac{P_{signal}}{P_{Q,noise}} = 10\log(\frac{V_A^2/2}{\Delta^2/12}) = 6.02N + 1.76$$

(3.11)

Equation (3.11) shows that increasing the number of bits per sample in the qunatizer increases the accuracy of the converter by 6dB for each extra bit.

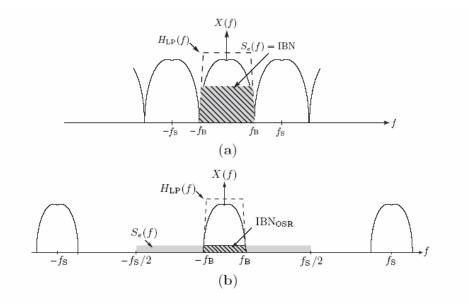

#### 3.5 Over-sampling Technique

Over-sampling is an important technique for sigma-delta ADCs. It can release the requirement of anti-aliasing filter. And it also can improve the resolution of a sigma-delta ADC. This improvement is achieved by over-sampling the signal. In other words, the sampling rate is much greater than Nyquist-rate. The definition of over-sampling ratio (OSR) is

$$OSR = \frac{2f_s}{f_b} \tag{3.12}$$

where  $f_s$  is the sampling frequency and  $f_b$  is the input signal bandwidth. Assuming the quantization noise is white noise. It means that noise power is uniformly distributed between  $-f_s/2$  and  $f_s/2$ . It had shown that total amount of noise power injected into the quantized signals are the same whether they are over-sampling or Nyquist-rate conversions. But the distributions are different due to different sampling frequencies. Figure 3.8 shows the power spectrum density of quantization noise  $S_Q(f)$  for conversion of Nyquist-rate (dotted line) sampling with sampling frequency,  $f_{s,NR}$ , and over-sampling (solid line) sampling with sampling frequency,  $f_{s,OS}$ , which is much greater than input signal bandwidth,  $f_b$ . The power spectrum density of input signal bandwidth for Nyquist rate is much greater than over-sampling.

The area of the both two rectangles meaning the total amount of noise power are the same and equal to  $\Delta^2/12$ . From Figure 3.8, it shows that the quantization noise power has spread to  $f_{s,os}/2$  and only a small fraction of quantization noise fall into the range of  $-f_b$  and  $f_b$ . And the quantization noise outside the signal band will be attenuated by a digital low-pass filter as shown in Figure 3.9. Recollecting the quantization noise power

Fig 3. 8(a) Quantization noise power spectrum density for Nyquist-rate (b) Over-sampling (solid line) conversion

spectrum density in equation (3.9) then we can show that the quantization noise is becoming

(a)

(b)

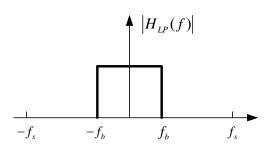

Fig 3. 9 (a) Over-sampling conversion with digital low-pass filter (b)magnitude of frequency response of digital low-pass filter

$$P_{Q,noise} = \int_{-f_s}^{f_b} S_Q(f) \cdot |H_{LP}(f)|^2 df = \int_{-f_b}^{f_b} S_Q(f) df$$

=  $\frac{\Delta^2}{12f_s} \cdot (2f_b) = \frac{\Delta^2}{12} \cdot \frac{2f_b}{f_s}$  (3.13)

then we obtain

$$P_{Q,noise} = \frac{\Delta^2}{12} \cdot \frac{2f_b}{f_s} = \frac{\Delta^2}{12} \cdot \frac{1}{OSR}$$

(3.14)

According equation (3.7), (3.10), (3.12) and (3.14), the SNR of over-sampling conversion is

$$SNR = 10 \log\left(\frac{P_{signal}}{P_{Q,noise}}\right) = 10 \log\left(\frac{\frac{V_{A}^{2}}{2}}{\frac{\Delta^{2}}{12} \cdot \frac{1}{OSR}}\right) = 6.02N + 1.76 + 10 \log(OSR) \quad (3.15)$$

The first term of equation (3.15) denotes the contribution of N-bit quantizer and the last term is the enhancement of over-sampling technique. For every doubling the OSR, the SNR improve by 3dB corresponding to improve the resolution by 0.5 bit. Besides, since the resolution of N-bit quantizer is lower than overall resolution of system, it could reduce the complexity of analog circuit and power of overall system.

## 3.6 Noise Shaping

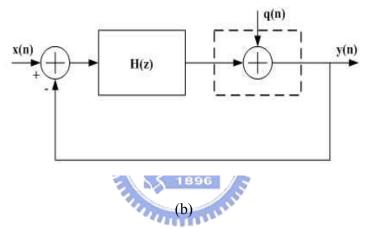

#### 3.6.1 Architecture of noise shaping

A general noise-shaped sigma-delta modulator and its linear model have been shown in Figure 3.10.

(a)

Fig 3. 10 Block diagram of (a) a noise-shaped SDM and (b) its linear model

We can show that

$$y(n) = x(n-1) + q(n) - q(n-1)$$

(3.16)

After transforming equation (3.16) by Z-transform, we obtain

$$Y(z) = \frac{H(z)}{1 + H(z)} X(z) + \frac{1}{1 + H(z)} Q(z)$$

(3.17)

Then we can derive signal transfer function ( $S_{TF}(z)$ ) by setting Q(z)=0

$$S_{TF}(z) = \frac{Y(z)}{X(z)} = \frac{H(z)}{1 + H(z)}$$

(3.18)

The same, we can derive noise transfer function  $(N_{TF}(z))$  by setting X(z)=0

$$N_{TF}(z) = \frac{Y(z)}{Q(z)} = \frac{1}{1 + H(z)}$$

(3.19)

The equation (3.17) will become

$$Y(z) = S_{TF}(z) \cdot X(z) + N_{TF}(z) \cdot Y(z)$$

(3.20)

The STF generally have all-pass or low-pass frequency response and the NTF have high-pass frequency response. In other words, the STF will be approximately unity over the signal band and the NTF will be approximately zero over the same frequency band. The quantization noise will be removed to high frequency band when using noise-shaping strategy [7]. The quantization noise over the frequency band of interest will be reduced and do not affect the input signal. This would improve the SNR significantly for overall system.

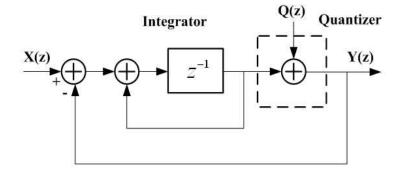

#### 3.6.2 First-Order ΔΣ Modulator

Fig 3. 11 The First-Order SDM

In Figure 3.11, it is a simple block diagram of the first-order SDM [8]. It includes an integrator and 1-bit quantizer. The noise-transfer function,  $N_{TF}(z)$ , should have a zero at DC. And zeros of  $N_{TF}(z)$  are equal to poles of the H(z) (i.e., has a pole at z=1).

Therefore, the quantization noise will be high-pass filtered. In other words, the H(z) will be small and the  $N_{TF}(z)$  will large over the frequency band of interest. Thus, the discrete time integrator with a pole at DC can be expressed as

$$H(z) = \frac{1}{z - 1} = \frac{z^{-1}}{1 - z^{-1}}$$

(3.21)

According to equation (3.18) and (3.19) we obtain

$$S_{TF}(z) = \frac{H(z)}{1 + H(z)} = \frac{z^{-1}/1 - z^{-1}}{1 + z^{-1}/1 - z^{-1}} = z^{-1}$$

(3.22)

$$N_{TF}(z) = \frac{1}{1+H(z)} = \frac{1}{1+z^{-1}/1-z^{-1}} = 1-z^{-1}$$

(3.23)

The total transfer function of system is

$$Y(z) = X(z) \cdot z^{-1} + Q(z) \cdot (1 - z^{-1})$$

(3.24)

From equation (3.24) we know the STF is just a delay and NTF is a high-pass filter. In another word, the output signal comprises the delayed input signal and high-pass filtered quantization noise. Now, we may consider the amplitude of the noise transfer function,  $|N_{TF}(z)|$ . Let  $z = e^{j\omega T} = e^{j2\pi f/f_s}$ , equation (3.23) will becomes

$$N_{TF}(z) = 1 - z^{-1} = 1 - e^{-j\omega T} = 1 - e^{-j2\pi f/f_{T}}$$

$$= \frac{e^{j\pi f/f_s} - e^{-j\pi f/f_s}}{2j} \cdot 2j \cdot e^{-j\pi f/f_s}$$

$$= \sin\left(\frac{\pi f}{f_s}\right) \cdot 2j \cdot e^{-j\pi f/f_s}$$

Then we obtain

$$\left|N_{TF}(f)\right| = 2\sin\left(\frac{\pi f}{f_s}\right) \tag{3.25}$$

The quantization noise power over the signal band is shown as follows:

$$P_{Q,noise} = \int_{-f_b}^{f_b} S_Q(f) \cdot \left| N_{TF}(z) \right|^2 df = \int_{-f_b}^{f_b} \frac{\Delta^2}{12} \frac{1}{f_s} \left[ 2\sin\left(\frac{\pi f}{f_s}\right) \right]^2 df \qquad (3.26)$$

Because  $OSR \gg 1$  for over-sampling conversion,  $f_s$  would be much larger than  $f_b$ . Thus,  $\sin(\pi f/f_s)$  can be approximated to  $\pi f/f_s$ . Equation (2.26) will become

$$P_{Q,noise} = \frac{\Delta^2}{12f_s} \int_{-f_b}^{f_b} \left[ 2\left(\frac{\pi f}{f_s}\right) \right]^2 = \frac{\Delta^2}{12} \cdot \frac{\pi^2}{3} \cdot \left(\frac{2f_b}{f_s}\right)^3 = \frac{\Delta^2 \pi^2}{36} \left(\frac{1}{OSR}\right)^3$$

(3.27)

Using the equation (3.10) and (3.27), we obtain the SNR of first-order SDM

$$SNR = 10 \log\left(\frac{P_{signal}}{P_{Q,noise}}\right) = 10 \log\left(\frac{\frac{V_A^2}{2}}{\frac{\Delta^2 \pi^2}{36} \left(\frac{1}{OSR}\right)^3}\right) = 10 \log\left(\frac{\frac{\Delta^2 2^{2N}}{8}}{\frac{\Delta^2 \pi^2}{36} \left(\frac{1}{OSR}\right)^3}\right)$$

= 6.02b + 1.76 - 5.17 + 30 log(OSR) dB (3.28)

For every doubling the OSR, the SNR will improve by **9dB** (ie., resolution will increase 1.5 bits). This result can be compared with equation (3.15), the SNR only can improve by 3dB when over-sampling conversion do not use noise-shaping strategy. It will be **much efficiency** when using noise-shaping technique.

#### 3.6.3 Second-Order ΔΣ Modulator

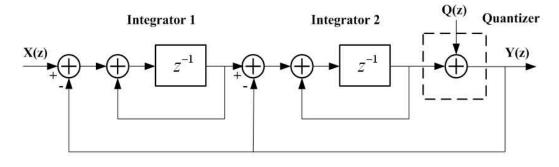

Fig 3. 12 The Second-Order SDM

In Figure 3.12, it is a block diagram of a second-order SDM. It is popular and widely used in SDM designing. It includes two integrators and a 1-bit quantizer. Its fundamental theorem is the same as the first-order SDM. Thus, the transfer function can be expressed as

And we can show the

$$S_{TF}(z)$$

and  $N_{TF}(z)$

$S_{TF}(z) = z^{-2}$

(3.29)

(3.29)

(3.29)

(3.30)

$$N_{TF}(z) = (1 - z^{-1})^2$$

(3.31)

Thus we obtain the magnitude of  $N_{TF}$

$$\left|N_{TF}(f)\right| = \left[2\sin\left(\frac{\pi f}{f_s}\right)\right]^2 \tag{3.32}$$

The quantization noise power over the signal band is shown as following

$$P_{Q,noise} = \int_{-f_b}^{f_b} S_Q(f) \cdot \left| N_{TF}(z) \right|^2 df = \int_{-f_b}^{f_b} \frac{\Delta^2}{12} \frac{1}{f_s} \left[ 2\sin\left(\frac{\pi f}{f_s}\right) \right]^2 df$$

(3.33)

$$\approx \frac{\Delta^2}{12f_s} \int_{-f_b}^{f_b} \left[ 2\left(\frac{\pi f}{f_s}\right) \right]^4 = \frac{\Delta^2}{12} \cdot \frac{\pi^4}{5} \cdot \left(\frac{2f_b}{f_s}\right)^5 = \frac{\Delta^2 \pi^4}{60} \left(\frac{1}{OSR}\right)^5$$

With the same method, we can obtain the SNR of the second-order SDM as

$$SNR = 10 \log\left(\frac{P_{signal}}{P_{Q,noise}}\right) = 10 \log\left(\frac{\frac{V_A^2}{2}}{\frac{\Delta^2 \pi^4}{60} \left(\frac{1}{OSR}\right)^5}\right) = 10 \log\left(\frac{\frac{\Delta^2 2^{2N}}{8}}{\frac{\Delta^2 \pi^4}{60} \left(\frac{1}{OSR}\right)^5}\right)$$

$$= 6.02b + 1.76 - 12.9 + 50 \log(OSR) \text{ dB}$$

(3.34)

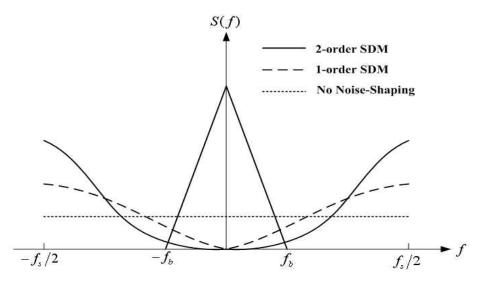

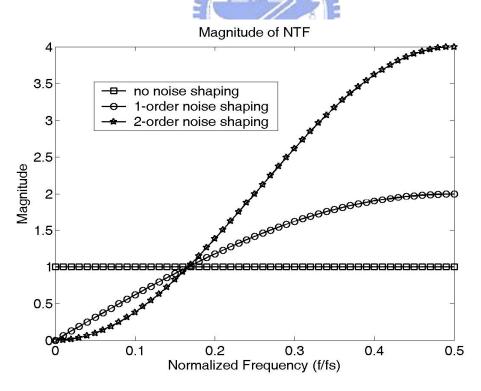

For every doubling the OSR, the SNR will improve by **15dB** (ie., resolution will increase 2.5 bits). This result can be compared with equation (3.15) and (3.28), the second-order SDM can provide more suppression over the same band, and thus more noise power outside the signal band. Figure 3.13 shows the phenomenon of using noise-shaping technique or not. For a fixed signal band, the case of no noise-shaping has the largest quantization power over the signal band. The second and the third are

Fig 3. 13 Power spectrum density of 1<sup>st</sup> order, 2<sup>nd</sup> order noise-shaping and non noise-shaping strategy

the first-order SDM and the second-order SDM respectively. As the number of order increasing, the quantization noise power will decrease over the same signal band. The simulation result can show as Figure 3.14.

Fig 3. 14 Magnitude of NTF

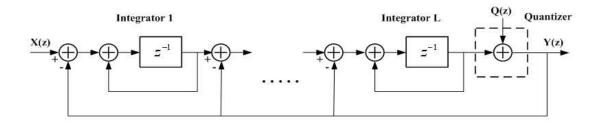

#### 3.6.4 Higher-Order ΔΣ Modulator

Fig 3. 15 The Higher-Order SDM

Higher-order SDM is divided into single-stage and multi-stage structures [9]. Figure 3.15 is the system block diagram of single-stage Lth-order SDM. Here, we will discuss the change of quantization noise and SNR when the number of order increases.

With the same approach, we obtain the noise-transfer function,  $N_{TF}$ , of the Lth-order SDM as follows:

$N_{TF} = (1 - z)^{L}$  (3.35) In a similar manner, the quantization-noise power over the signal band of the

$$P_{Q,noise} = \int_{-f_b}^{f_b} S_Q(f) \cdot \left| N_{TF}(z) \right|^2 df = \int_{-f_b}^{f_b} \frac{\Delta^2}{12} \frac{1}{f_s} \left[ 2\sin\left(\frac{\pi f}{f_s}\right) \right]^{2L} df$$

$$\approx \frac{\Delta^2}{12f_s} \int_{-f_b}^{f_b} \left[ 2\left(\frac{\pi f}{f_s}\right) \right]^{2L} = \frac{\Delta^2}{12} \cdot \frac{\pi^L}{2L+1} \cdot \left(\frac{2f_b}{f_s}\right)^{2L+1}$$

(3.36)

$$=\frac{\Delta^2 \pi^{2L}}{12(2L+1)} \left(\frac{1}{OSR}\right)^{2L+1}$$

Then the SNR of the single-stage Lth-order SDM is

single-stage Lth-order SDM with N-bits quantizer is

$$SNR = 10 \log \left(\frac{P_{signal}}{P_{Q,noise}}\right) = 10 \log \left(\frac{\frac{V_A^2}{2}}{\frac{\Delta^2 \pi^{2L}}{12(2L+1)} \left(\frac{1}{OSR}\right)^{2L+1}}\right)$$

$$= 10 \log \left(\frac{\frac{\Delta^2 2^{2N}}{8}}{\frac{\Delta^2 \pi^{2L}}{12(2L+1)} \left(\frac{1}{OSR}\right)^{2L+1}}\right)$$

Finally, we get the result

$$SNR = 6.02b + 1.76 + 10\log\left(\frac{\pi^{2L}}{2L+1}\right) + (20L+10)\log(OSR) \text{ dB} \qquad (3.37)$$

From equation (3.37), we know that for every doubling the OSR, the SNR will improve by (6L+3) dB (ie., resolution will increase L+0.5 bits). There are three ways to increase the SNR of a SDM. First, we can increase the bits of quantizer. The disadvantage is that multi-bit quantizer would induce harmonic distortion because of mismatch. Second, we can increase the number of order of a SDM. But it may have stability problem when the order is greater than 2. Third, increasing the OSR is the most popular way to improve the performance But for low power design, increasing

the OSR is not suitable because the requirement of the integrators, such as settling time, bandwidth, and slew rate will be increased. Beside, the power of decimation filter will also be increased because of high sampling frequency. Figure 3.16 is the SNR of SDM. This plot provides a tradeoff between order, OSR and the power dissipation.

#### 3.6.5 System Analysis of ΔΣ Analog-to-Digital Converters

The system architecture for a typical over-sampling ADC is shown in Figure 3.17. The anti-aliasing filter is used to filter the out-of-band noise of original input signal to avoid noise folding into signal band. Then, the signal is sampled and held and applied to a SDM and output a 1-bit digital signal. Usually, the sample-and-hold usually combines with the SDM. These three blocks are belonging to analog domain. A decimation filter which contains a digital low-pass filter and a down-sampling not only suppresses the

out-of-band quantization noise but also down-sample the sampling frequency from  $f_s$ to Nyquist-rate [10]. Note that the digital low-pass filter here is like an anti-aliasing filter to limit signals to one-half the output sampling rate. The decimation filters generally are implemented using digital circuit technique in order to reduce the power dissipation and are easy to implement. Figure 3.18 shows the signal and spectra of each stage of over-sampling ADC [11].

#### 3.7 Conclusion

In this chapter, we have introduced the basic principles of sigma-delta modulator. Among these, the most important is the properties of shaped quantization error. Here, various architectures of SDM such as single-loop and cascaded was introduced and compared. And then, the advantages and disadvantages of multi-bit quantizer was described and analyzed. In the final part of this chapter, we discuss how the signal and spectra change in different section of the over-sampling ADC and DAC. This would make us much clear about the operation of over-sampling system.

Fig 3. 18 Signal and spectra in an over-sampling ADC

•••

# CH4 Transformation of a Discrete-Time to Continuous-Time

# 4.1 Introduction

Early designs of continuous-time  $\Sigma\Delta$  modulators were approximate, guided by the intuition that the general continuous-time integrators  $\omega_0$  should work for low-pass modulators and correspondingly the continuous-time resonators  $\omega_0 S/(S^2 + \omega_0)$  for band-pass modulators. However, this simple assumption leads to implementation of an incorrect loop transfer function for a  $\Sigma\Delta$  modulator. In this chapter it is shown that a continuous-time  $\Sigma\Delta$  loop filter has to be designed according to the digital to analog converter (DAC) output waveform in the feedback path of the modulator. A simple explanation is that the continuous-time filter respond to an input signal continuously, unlike the SC filter in which an analog charge is supplied to the filter at a clock phase  $\phi$  and the output analog voltage is ready at a clock phase  $\overline{\phi}$ . So a SC filter doesn't see the variations of the input signal during the clock period  $\phi$  and  $\overline{\phi}$ . On the other hand, form the linear system theory the output of a continuous-time filter is the result of convolution of the filter response with the input signal in the time interval  $t \in [-\infty, \infty]$ .

#### 4.2 The Impulse-Invariant Transform

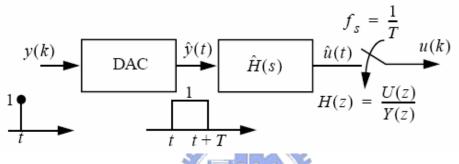

A clock diagram of a continuous-time  $\Sigma\Delta$  modulator is shown in Fig.4.1. Because of the presence of a sampler inside the loop (the quantizer is clocked, making for implicit sampling) the overall loop transfer function in a continuous-time modulator is really a discrete-time transfer function! In other words as shown in Fig. 4.2 the loop transfer function from the output of quantizer back to its input has an exact equivalent *z*-domain transfer function H(z). This doesn't mean that the waveforms inside the loop are sampled-data like the ones in a switched-*C* (discrete-time) modulator.

Fig 4. 1 continuous-time  $\Delta\Sigma$  modulator

Fig 4. 2  $\Delta\Sigma$  open loop block diagram

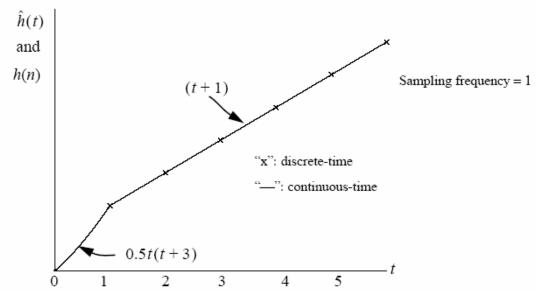

However, the sample values of the continuous-time waveform at the input of the quantizer at the sample times define an exact discrete-time impulse response for the continuous-time loop. In order to clarify this statement a examples of a second-order low-pass  $\Sigma\Delta$  modulators with loop transfer functions of  $z^{-1}(2-z^{-1})/(1-z^{-1})^2$  is given here briefly. The loop impulse responses of these discrete-time systems and their corresponding continuous-time counterparts are shown in Fig. 4.3.

Fig 4. 3 Open-loop impulse response of the second-order low-pass modulator

As shown in these figures the open-loop impulse responses of the discrete-time loop filters match the samples of the impulse response of the continuous-time modulator loops. The continuous-time waveforms shown in Fig. 4.3 is actually the pulse responses of the continuous-time  $\Delta\Sigma$  loop filter as depicted in Fig. 4.2. Detailed analysis of these examples is given in next Sec. 4.3.

The loop behavior is completely determined by what the sampler inside the loop sees at its sample times, and that can be written as a difference equation. So, if a designer wants to analyze the performance of a continuous-time  $\Delta\Sigma$  modulator (*SNR* and stability), he/she should first derive the equivalent *z*-domain transfer function for the  $\Delta\Sigma$  loop. Then further analysis can be done in the *z*-domain as for traditional discrete-time modulators. Therefore the noise-shaping behavior of "continuous-time"  $\Delta\Sigma$  loops can be designed entirely in the "discrete-time" domain and the exact same noise-shaping behavior obtained for either continuous-time or discrete-time systems.

## 4.3 NRZ Transformation

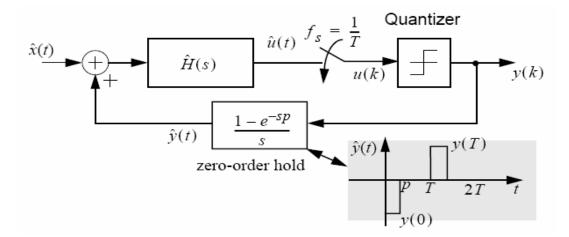

The  $\Delta\Sigma$  modulator of Fig. 4.1 is shown again in Fig.4.4 in more detail. The loop filter is represented by  $\hat{H}(s)$  and the DAC transfer function by a zero-order-hold (*ZOH*) in

which *p* is the opening aperture. The non-return-to-zero(NRZ) DAC *p*=*T* where *T* is a sampling period. Fig. 4.2 shows the  $\Delta\Sigma$  signal path from the output of quantizer back to its input for a NRZ DAC.

Fig 4. 4 A continuous-time  $\Delta\Sigma$  modulator in S-domain

As can be seen from Fig. 4.2 the overall  $\Delta\Sigma$  loop gain is a discrete-time function, so one can derive the exact discrete-time transfer function, H(z), of the loop given the transfer functions of the continuous-time loop filter,  $\hat{H}(s)$ , and the *ZOH* as follows:

$$Z^{-1}[H(z)] = L^{-1}\left[\frac{1 - e^{-sp}}{s}\widehat{H}(s)\right]_{t=nT}$$

(4.1)

Equation (4.1) can be expressed in the time domain by

$$h(nT) = \left[R_p(t) * \hat{h}(t)\right]\Big|_{t=nT} = \left(\int_{-\infty}^{\infty} R_p(\tau)\hat{h}(t-\tau)d\tau\right)\Big|_{t=nT}$$

(4.2)

where  $R_p(t)$ , the impulse response of *ZOH*, is a pulse with width of *p* as shown in Fig. 4.4,  $\hat{h}(t)$  is the impulse response of the continuous-time loop filter, h(n) is the overall discrete-time impulse response of the loop, and \* denotes time convolution. Since  $R_p(t)$  has a pulse waveform, (4.1) and (4.2) are known as the pulse invariant transformation.

Consider the case where p=T corresponding to NRZ feedback pulse. Then the loop filter NRZ pulse response from (4.2) can be described as following:

$$h(t) = R_{NZ}(t) * \hat{h}(t) = \int_{-\infty}^{\infty} R_{NZ}(\tau) \hat{h}(t-\tau) d\tau = \begin{cases} t \\ \int \hat{h}(t-\tau) d\tau & 0 \le t < T \\ 0 \\ T \\ \int \hat{h}(t-\tau) d\tau & t \ge T \\ 0 \\ 0 & t < 0 \end{cases}$$

(4.3)

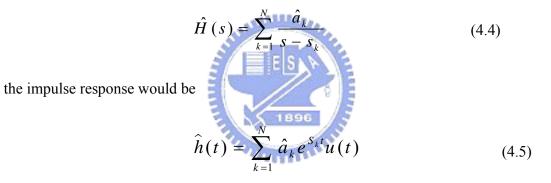

For a continuous-time loop filter with single-poles described in residue form by

Substituting  $\hat{h}(t)$  into (4.3), we have

$$h(t) = \begin{cases} \int_{0}^{t} \left(\sum_{k=1}^{N} \hat{a}_{k} e^{s_{k}(t-\tau)}\right) d\tau = \sum_{k=1}^{N} \hat{a}_{k} e^{s_{k}t} \left[\int_{0}^{t} e^{-s_{k}\tau} d\tau\right] = \sum_{k=1}^{N} \frac{\hat{a}_{k}}{-s_{k}} e^{s_{k}t} (e^{-s_{k}t}-1) \quad 0 \le t < T \\ \int_{0}^{T} \left(\sum_{k=1}^{N} \hat{a}_{k} e^{s_{k}(t-\tau)}\right) d\tau = \sum_{k=1}^{N} \hat{a}_{k} e^{s_{k}t} \left[\int_{0}^{T} e^{-s_{k}\tau} d\tau\right] = \sum_{k=1}^{N} \frac{\hat{a}_{k}}{-s_{k}} e^{s_{k}t} (e^{-s_{k}T}-1) \quad t \ge T \\ \end{cases}$$

(4.6)

Looking at samples of loop impulse response, h(t), at sampling times *i.e.* t=nT gives the discrete-time loop impulse response equivalent

$$h(nT) = \begin{cases} 0 & 0 \le t < T \\ \sum_{k=1}^{N} \frac{\hat{a}_{k}}{-s_{k}} e^{s_{k}nT} (e^{-s_{k}T} - 1) & t \ge T \end{cases}$$

$$(4.7)$$

The z-domain loop transfer function of the loop then can be derived from (4.7)

$$H(z) = \sum_{n = -\infty}^{+\infty} h(n) z^{-n} = \sum_{n = 1}^{\infty} \left( \sum_{k = 1}^{N} \frac{\hat{a}_k}{-s_k} e^{s_k n T} (e^{-s_k T} - 1) \right) z^{-n}$$

$$= \sum_{k = 1}^{N} \left[ \frac{\hat{a}_k}{-s_k} (e^{-s_k T} - 1) \sum_{n = 1}^{\infty} e^{s_k n T} z^{-n} \right]$$

$$= \sum_{k = 1}^{N} \frac{\hat{a}_k}{-s_k} \cdot \frac{(1 - e^{s_k T}) z^{-1}}{1 - e^{s_k T} z^{-1}}$$

(4.8)

There are some interesting properties in the pulse invariant transformation given in

(4.6)-(4.8) which have to be addressed:

1) The first sample of the loop filter pulse response is zero (4.7). This is described by a delay factor which always exists in the numerator of the pulse invariant transformation function (4.8). This delay is related to the causality property associated with convolution of two ordinary signals which don't contain any impulse function  $\delta(t)$  component. That's why, as will be seen in the transformation of any discrete-time  $\Delta\Sigma$  loop filter to a continuous-time equivalent, one delay is always absorbed in pulse transformation.

2) The overall continuous-time loop response (4.6) is described by different functions in the regions of  $0 \le t < T$  and  $t \ge T$ , where *T* is the sampling period. This has already been shown in Fig. 4.3 for second-order low-pass modulators. It should be noted that,

however, the overall loop response has continuity at T. The equivalent discrete-time loop filter (4.8) can be written as

$$H(z) = \sum_{k=1}^{N} \frac{a_k Z^{-1}}{1 - Z_k Z^{-1}}$$

(4.9)

where the new residue is

$$a_{k} = \frac{\hat{a}_{k}}{-s_{k}} (1 - e^{S_{k}T}) \cos^{-1} \theta$$

(4.10)

and the new pole is at  $Z_k = e^{S_k T}$

Note that (4.9) is the NRZ pulse transformation of (4.4) rewritten here

$$\hat{H}(s) = \sum_{k=1}^{N} \frac{\hat{a}_{k}}{S - S_{k}}$$

(4.11)

This has the properties one would expect: a pole at s = 0 transforms to one at z = 1, and a pole at  $s = j2\pi (f_s / 4)$  transforms to one at z = j.

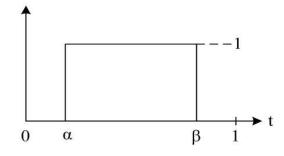

To actually do the transform, we proceed as follows. First, we write H(z) as a partial fraction expansion. Then we choose a DAC pulse shape. We can assume a perfectly rectangular DAC pulse of magnitude 1 that from  $\alpha$  to  $\beta$ . It can be shown as equation (4.11) and Figure 4.5. This covers most types of practical DAC pulse. Finally,

$$\hat{r}(\alpha,\beta) = \begin{cases} 1, \ \alpha \le t < \beta, \ 0 \le \alpha < \beta \le 1\\ 0, \text{ otherwise.} \end{cases}$$

(4.11)

Fig 4. 5 The DAC pulse

We use Table 4.1 to convert each partial fraction pole from z to s. Then we will obtain the result of  $\hat{H}(s)$ . For example, if we use the DAC type, ( $\alpha$ ,  $\beta$ )=(0,1) in (4.11). And the transfer function is

$$H(z) = \frac{-2z+1}{(z-1)^2}$$

(4.12)

Table 4.1 s-domain equivalences for z-domain loop filter poles [12]

| <i>z</i> -domain pole              | Limit for $z_k = 1$                                                                                                                                                 |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    | ALL DE CONTRACTOR                                                                                                                                                   |

| $\frac{y_0}{z-z_k}$                | $\frac{r_0}{s-s_k}, \qquad r_0 = \frac{y_0}{\beta-\alpha}$                                                                                                          |

| $\frac{y_0}{\left(z-z_k\right)^2}$ | $\frac{r_1 s + r_0}{\left(s - s_k\right)^2}, \qquad r_0 = \frac{y_0}{\beta - \alpha}  r_1 = \frac{1}{2} \frac{\left(\alpha + \beta - 2\right) y_0}{\beta - \alpha}$ |

| $\frac{y_0}{\left(z-z_k\right)^3}$ | $\frac{r_{2}s^{2} + r_{1}s + r_{0}}{(s - s_{k})^{3}},  r_{0} = \frac{y_{0}}{\beta - \alpha}  r_{1} = \frac{1}{2} \frac{(\alpha + \beta - 2)y_{0}}{\beta - \alpha}$  |

|                                    | $r_{2} = \frac{1}{12} \frac{y_{0}}{\beta - \alpha} \Big[ \beta \big( \beta - 9 \big) + \alpha \big( \alpha - 9 \big) + 4\alpha \beta + 12 \Big]$                    |

Then we write this in partial fractions yields

$$H(z) = \frac{-2}{z-1} + \frac{-1}{(z-1)^2}$$

(4.13)

Applying the first row of Table 4.1, we obtain

$$\hat{H}(s) = \frac{-2}{s} + \frac{-1 + 0.5s}{s^2} = -\frac{-1 + 1.5s}{s^2}$$

(4.14)

Then we had transformed the H(z) to  $\hat{H}(s)$  and obtain the new coefficients for continuous-time SDM.

#### 4.3.1 Effect of Excess Loop Delay

Continuous-time SDM suffers a problem not seen in discrete-time design. That is the excess loop delay [13]. Excess loop delay arises because of **nonzero delay** between the quantizer clock edge and the time when a change in output bit is seen at the feedback point in the modulator. It arises because the nonzero switching time of the transistors in the feedback path. Its effect is severe if the sampling clock speed is an appreciable fraction of the maximum transistor switching speed.

and the second

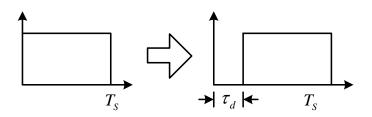

Fig 4. 6 Illustrations of excess loop delay on NRZ DAC pulse

We assume that excess loop delay can be expressed as a fraction of the sampling period

$$\tau_d = \rho_d T_S \tag{4.15}$$

In an actual circuit, the value of  $\tau_d$  depends on the switching speed of the transistors

$f_T$ , the quantizer clock frequency  $f_S$ , and the number of transistors in the feedback path  $n_t$  (as well as other things like the loading on each transistor). As a crude approximation, we could assume transistors switch fully at the maximum speed, i.e. after time  $1/f_T$ , in which case we could write

$$\rho_d = \frac{n_t f_s}{f_T} \tag{4.16}$$

$\tau_d$  could end up being a significant fraction of  $T_s$  depending on the parameters in (4.16). This is particularly likely in GHz-speed modulators built in a process with an  $f_T$  of a few tens of GHz. For example, a OSR of about 50 and 5MHz bandwidth Sigma-delta modulator ,which means we must clock at  $f_s = 50(2*5) = 500$ MHz. comparator output differential pair must switch. The DAC must also switch, and thus  $n_t = 2$ . In a  $f_T = 10$ GHz process, therefore,  $\rho_d = \frac{2 \cdot 0.5}{10} = 10\%$  is the amount of excess delay predicted by (4.16).

We recall DAC pulses as rectangular with the form

$$\hat{r}(\alpha,\beta) = \begin{cases} 1, \ \alpha \le t < \beta, \ 0 \le \alpha < \beta \le 1\\ 0, \ \text{otherwise.} \end{cases}$$

in (4.11)

Suppose we have assumed that we have an NRZ DAC with  $(\alpha, \beta) = (0,1)$ , and we have found the equivalent  $\hat{H}(s)$  for a desired H(z) using Table 4.1 or MATLAB. If we use this filter in a system with delayed pulses as in Fig 4.6, then the system no longer has the same  $\alpha$  and  $\beta$ . This means the equivalence between  $\hat{H}(s)$  and H(z) is affected.

Then we are going to understand the effect of excess loop delay of DAC. Suppose we are designing a CT double integration modulator, and we have NRZ DAC pulse, then we would have found  $\hat{H}(s)$  to be  $\hat{H}(s) = -\frac{1+1.5s}{s^2}$  suppose further that we have excess loop delay  $\tau_d$ , so that in actuality we have NR DAC pulse delayed by  $\tau_d$  as in figure

4.6. In that case, we have  $(\alpha, \beta) = (\tau_d, \tau_d + 1)$ . What is the equivalent H(z) for such an  $\hat{H}(s)$  and DAC pulse?

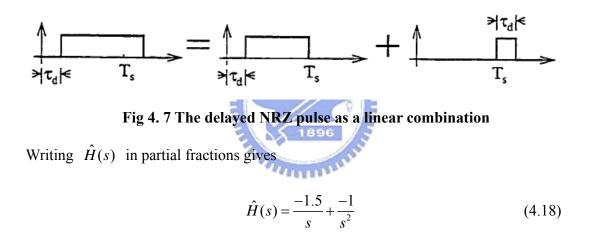

The formulae in Table 4.1 only apply for a pulse with  $\beta \le 1$ , but once again, superposition comes to our rescue: it is possible to write a  $\tau_d$ -delayed NRZ pulse as

$$\hat{\Upsilon}_{(\tau_d, 1+\tau_d)}(t) = \hat{\Upsilon}_{(\tau_d, 1)} + \hat{\Upsilon}_{(0, \tau d)}(t-1)$$

(4.17)

That is the linear combination of a DAC pulse from  $\tau_d$  to 1 and a one-sample -delayed DAC pulse form 0 to  $\tau_d$  as shown in figure 4.7.

Applying Table 4.1 to each term of (4.18), for each of the two DAC pulses in (4.17), yields

$$\frac{-1.5}{s} \rightarrow \frac{-1.5(1-\tau_d)}{z-1} + z^{-1} \frac{-1.5\tau_d}{z-1}$$

$$\frac{-1}{s^2} \rightarrow \frac{(-0.5+\tau_d-0.5\tau_d^{-2})z+0.5(-1+\tau_d^{-2})}{(z-1)^2}$$

$$+ z^{-1} \frac{\tau_d(-1+0.5\tau_d)z-0.5\tau_d^{-2}}{(z-1)^2}$$

(4.20)

Adding (4.19) and (4.2) gives

$$H(z,\tau_d) = \frac{(-2+2.5\tau_d - 0.5\tau_d^2)z^2 + (1-4\tau_d + \tau_d^2)z + (1.5\tau_d - 0.5\tau_d^2)}{z(z-1)^2} \quad (4.21)$$

We can quickly verify that for  $\tau_d = 0$ , (4.21) turn into (4.12). However, for  $\tau_d \neq 0$ , the equivalent H(z) is no longer (4.12).

The key point is, excess delay always alters the numerator coefficients of the equivalent H(z), and it turns out that using rectangular pulses yields simulation results that are similar to those found using more realistic pulse shapes.

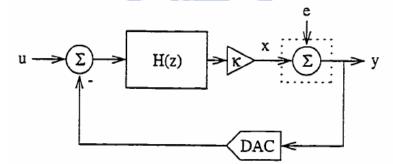

#### 4.3.2 Root locus of effect of Excess Loop Delay

The easiest way to grasp the effect of excess delay is to linearize the quantizer and look at the stability of the noise transfer function. There is, however, the gain of a one bit quantizer isn't well-defined. That is, we could insert a positive gain k immediately

Fig 4. 8 Linear SDM with one-bit quantizer arbitrary gain k.

in front of the quantizer and not affect the performance of the circuit-quantizer

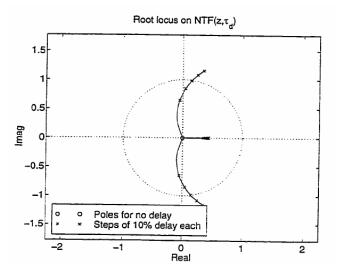

Fig 4. 9 Effect of loop delay on root locus of  $NTF(z, \tau_d)$

inputs would be scaled, but their signs remain unchanged, hence the sequence of  $\pm 1$  would be identical. Making k explicit is usually done in the linear model as shown in figure 4.8, which results in NTF $(z, \tau_d) = (1+kH(z, \tau_d))^{-1}$ . Figure 4.9 shows that for k=1 and increasing  $\rho_d$ , the poles of NTF $(z, \tau_d)$  move towards the unit circle, eventually moving outside at  $\rho_d \approx 0.31$ . Any choice of k >0 shows a similar movement of poles from their initial positions towards the unit circle; this implies modulator stability worsens as delay increases.

# CH5 Implementation of Low-Power GM-C Continuous-Time SDM

#### 5.1 Introduction

In this chapter, we will introduce the implementation of a 3<sup>rd</sup>-order continuous-time GM-C sigma-delta modulator. In section 1, we will show the behavior simulation of the SDM. In section 2, we will discuss the circuit level design of the GM-C SDM. In section 3, we will show the performance and layout of the SDM.

#### 5.2 Behavior Simulation

## 5.2.1 Determine the coefficients for CRFB structure

The first step in the design of a  $\Sigma\Delta$  modulator is the selection of the NTF. The modulator order, the number of quantization levels, and the low-pass or band-pass are all design parameters.

ALL DA

We have two methods to determine the coefficients for  $\Sigma\Delta$  in Z-domain.

#### **METHOD 1:**

The MATLAB have freeware tool to get coefficients by the Delta-Sigma Toolbox. Although it is based on filter design to determine loop filter structure, user doesn't necessary to understand algorithmic details before making use of the toolbox. A complete reference manual for this freeware toolbox, including instructions for obtaining it, may be found in MATLAB web or reference [14].

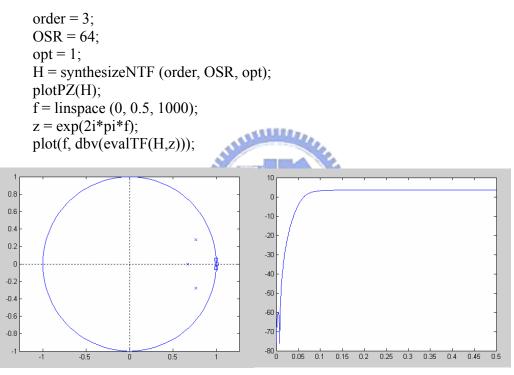

The function which synthesizes the NTF is *synthesizeNTF*. The first two arguments to *synthesizeNTF* specify the order of the NTF and the over-sampling ratio, while the third argument(opt) is a flag which specifies whether or not the NTF zeros are to be optimized

for maximum attenuation of quantization noise in the band of interest. Optional fourth and fifth arguments specify the NTF's out-of-band (Hinf) and ,for band-pass modulators,  $||H||_{\infty}$  defaults to 1.5. Likewise, since the center frequency was not specified,  $f_0$ defaults to zero. The default value of *synthesizeNTF* function as following below:

Use of *synthesizeNTF* 's optional arguments is illustrated in Fig.5.1, which contains both the MATLAB code for designing the NTF of a low-pass modulator.

Fig 5. 1 MATLAB code for creating a low-pass NTF.

After studying the function *synthesizeNTF*, we will learn two instructions *realizeNTF* and *scaleABCD*. The coefficients returned by *realizeNTF* are those of an unscaled modulator, i.e. a modulator whose internal states occupy an unspecified range. In order to restrict the state range to known values, dynamic-range scaling must be performed. Dynamic-range scaling can be applied to any linear system on a state-by-state basis, which means the internal state is scaled down by k times to reduce all incoming branches signal, and make up for the attenuation so introduced by multiplying all out-going branches by the same factor k times.

The toolbox function scaleABCD uses simulations to determine the required scaling factors for each state of a delta-sigma modulator. The modulator is simulated with inputs of various amplitudes in order to determine the maximum stable input amplitude (umax) as well as the maximum value that each state achieves for input amplitudes up to umax. The ABCD matrix of the modulator is then subjected to dynamic range scaling so that the maximum value of each state equals the specified limit (xlim, which defaults to 1). The toolbox function mapABCD then translates the scaled ABCD matrix back into the coefficients for the chosen topology.

Then we are going to determine to SDM coefficients step-by-step by the toolbox function we studied. Below we design a OSR = 50, order = 3 ,1 bit and scale the state to 0.2 modulator, the result is shown if Fig 5.2.

H = synthesizeNTF (3, 50, 1); Form = 'CRFB'; [a,g,b,c] = realizeNTF(H,form); b(2:end) = 0; ABCD = stuffABCD(a,g,b,c,form); [ABCD umax] = scaleABCD(ABCD,2,0.2); [a,g,b,c] = mapABCD(ABCDs,form);

| i | a <sub>i</sub> | $\mathbf{g}_{\mathrm{i}}$ | b <sub>i</sub> | c <sub>i</sub> |

|---|----------------|---------------------------|----------------|----------------|

| 1 | 0.15656        | 0.01021                   | 0.15656        | 0.28933        |

| 2 | 0.24871        | 0                         | 0              | 0.23195        |

| 3 | 0.13235        | 0                         | 0              | 4.2017         |

Fig 5. 2 MATLAB code with coefficient and CRFB structure

The form in MATLAB code is the loop filter structure. If form is 'CIFB' to be means cascade-of-integrator (CI) filters and feedback (FB) DAC. There are four topologies which supported by toolbox CIFB, CIFF, CRFB and CRFF.

#### **METHOD 2:**

To use behavioral simulation result of the modulator is by SIMULINK. First setting all of the OP or GM gains to be required value (ex: 40dB) and the over-sampling ratio, and use loop code to sweep all coefficients like  $a_i b_i c_i$  and  $g_i$ . We can get a nice set of coefficients relative to highest SNR.

#### 5.2.2 Transfer coefficient from discrete-time to continuous-time

When we get coefficients in Z-domain, next step is to transfer it to time-domain. It should be depend on the instruction "d2cm" in MATLAB. For example, we have a discrete-time sigma-delta in Fig 5.3, then use d2cm to transfer coefficients to time domain.

Fig 5. 3 A CIFB  $\Delta\Sigma$  structure

We first calculate the loop filter transfer function H(z), and get the numerator and denominator of H(z). If we set the value c1 = 0.2, c2 = 0.3, c3 = 0.4, a1 = -1, a2=-1 and a3=-1 in Fig 5.3, then will get the transfer function H(z) is

$$H(z) = \frac{-0.4z^2 - 0.92z - 0.304}{(z-1)^3}$$

(5.1)

Then use MATLAB built-in functions d2cm to transfer H(z) to  $\hat{H}(s)$ . We type

$$[num, den] = d2cm([-0.4 -0.92 -0.304], [1 -3 3 -1], 1)$$

d2cm is the discrete-to –continuous conversion routine of the control toolbox. The first two arguments are the numerator and denominator of H(z) in descending powers of z, while the third argument is the sample period Ts. MATLAB returns

num=0

$$-0.0813$$

$-0.0960$  $-1.6240$ den= $1.0000$  $-0.0000$  $0.0000$  $-0.0000$

which are the numerator and denominator of  $\hat{H}(s)$  in descending powers of s in other words,  $\hat{H}(s) = (-0.0813s^2 - 0.096 - 1.624)/s^3$ .

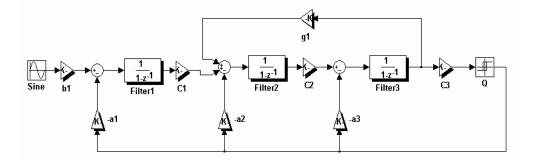

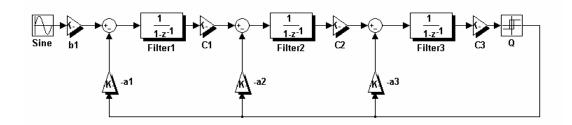

Using SIMULINK structure the continuous time sigma-delta is shown in Fig 5.4.

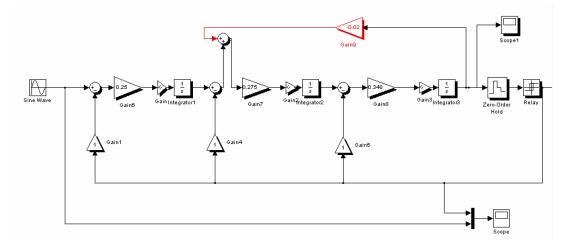

Fig 5. 4 CRFB continuous-time  $\Delta\Sigma$  in time domain

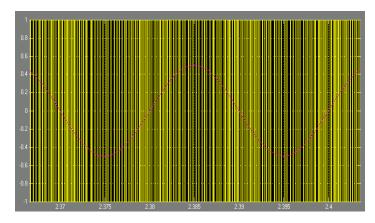

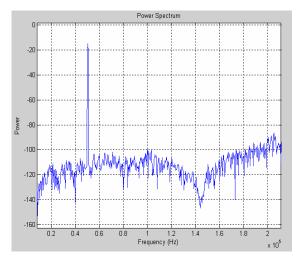

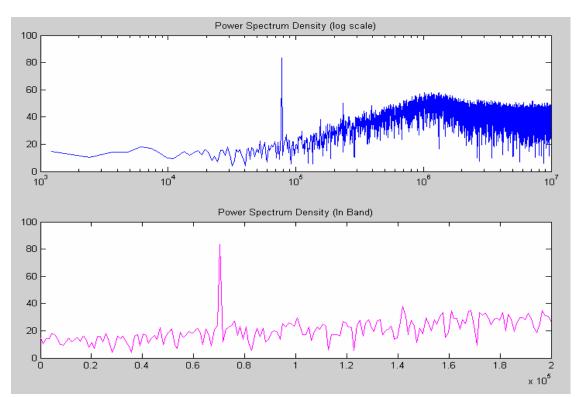

The time-domain output data is shown in Figure 5.5 and the plot of power spectrum density is shown in Figure 5.6.

Fig 5. 5 The time-domain output data

Fig 5. 6 The power spectrum of output data

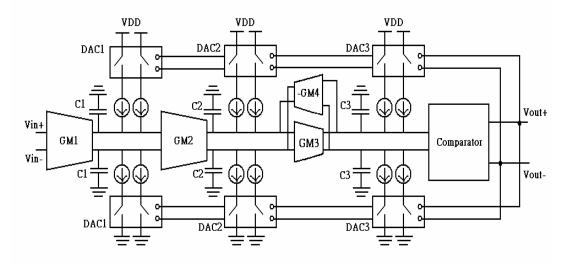

#### 5.2.3 Optimization of the NTF zeros