# 國立交通大學

機械工程學系

碩士論文

應用於微定位器之電流電荷感測電路探討

A study of the current and charge sensing circuits for micropositioners

ALL STREET

研究生:黄少侃

指導教授:陳宗麟 教授

中華民國九十七年六月

## 應用於微定位器之電流電荷感測電路探討

# A study of the current and charge sensing circuits for micropositioners

研 究 生:黃少侃 Student: Shao Kan Huang

指導教授:陳宗麟 Advisor:Tsung Lin Cheng

國立交通大學機械工程學系領士論文

A Thesis

Submitted to Department of Mechanical Engineering

College of Engineering

National Chiao Tung University

in partial Fulfillment of the Requirements

for the Degree of

Master

in

Mechanical Engineering

August 2007

Hsinchu, Taiwan, Republic of China

中華民國九十七年六月

### 應用於微定位器之電流電荷感測電路探討

研究生: 黃少侃 指導教授: 陳宗麟 博士

#### 國立交通大學機械工程學系

#### 中文摘要

微定位器(Micropositioner)屬於微機電系統的範疇,它提供高精確度、高頻寬下的驅動以及較低的成本,因此可以廣泛應用於磁性和光學性的儲存設備。當微定位器的移動元件以一固定頻率來回運動時,上下兩側的感應電容大小因為移動元件與上下兩端電極平板的距離改變而變化,故產生正比於上下兩感應電容間不匹配量的電荷,而單位時間內的電荷的改變即為電流。分別把電荷、電流輸入其適當對應的運算放大器,經過運算放大器的處理而產生輸出信號,此輸出信號就是微定位器中運動元件移動的速度或位移的函數,因此藉由量測此輸出信號即可得到微定位器的速度或是位移;之後可進一步利用噪訊比的關係,得到微定位器其最小可偵測到的位移或是速度大小。

# The research of the current and charge sensing circuit applied at micropositioners

Student: Shao Kan Huang Advisor: Tsung Lin Cheng

#### **Abstract**

Micropositioner, which provides the advantages such as high precision, the driving capability on wide-frequency bandwidth and the lower costs, belongs to Micro-electromechanical Systems (MEMS). Therefore it is widely used in the magnetic or optical storage device. The values of the two capacitors change because the distance between the moving element from upper and lower electrodes are changing respectively while the moving element is vibrating in a fixed frequency. There is a net charge proportional to the mismatch between the two sensing capacitor. Differentiating the charge yields current. Input charge and current into the corresponding op-amp respectively, and by the processing of op-amp, there is an output signal which is function of velocity or displacement of the micropositioner. Measuring the output signal then we can get the velocity or displacement of the micropositioner. Furthermore by the signal to noise ratio, we can get the magnitude of minimum detecting displacement, or call it resolution.

#### 致謝

研究所兩年的時間轉眼即逝。由於本篇碩論所做的研究需要原本完全不懂的專業知識,因此碩一修課缺乏該有的基礎讓我進展極慢,但碩二總算補足了相關的基礎可以全心投入研究領域。這段時間雖然遭遇了很多困難、經歷了很多挫折,但終究還是完成了這份論文。

能完成這篇論文,首先要感謝的是指導老師陳宗麟教授,沒有老師的指導和 幫忙我無法完成這篇論文。當然也要感謝實驗室學長建宇、俊胤、齡元、志柏、 忠福,從學長那邊得到了許多寶貴的經驗和建議;當然也要感謝一路走來互相加 油打氣的同學榜均、仁植和紹宸,每當研究遇到瓶頸的時候可以互相打氣、繼續 走下去。也謝謝學弟們給實驗室帶來活力。另外我想感謝電子所的鄭人文同學, 在我最困惑、問題解決不了時熱心的跟我討論,找尋解決的方法。

最後要感謝我的家人,讓我沒有經濟上的負擔可以專心致力於學業上,讓我 得以順利地拿到碩士學位。

1896

黃少侃 僅誌於交通大學機械所 民國 97 年六月

# 目錄

| 中文摘要i                    |

|--------------------------|

| 英文摘要ii                   |

| 致謝iii                    |

| 目錄iv                     |

| 圖目錄vi                    |

| 表目錄viii                  |

| 第一章 序論1                  |

| 1.1 研究背景與研究動機1           |

| 1.2 論文架構2                |

| 第二章 静電式微定位器3             |

| 2.1 微定位器原理3              |

| 2.2.1 側向梳狀結構4            |

| 2.2.2 横向梳狀結構             |

| 2.2.3 平行板結構              |

| 2.2.4 三種微定位器的比較          |

| 第三章 感測電路分析10             |

| 3.1 轉阻放大器電路架構10          |

| 3.1.1 開迴路分析11            |

| 3.1.2 閉迴路分析13            |

| 3.2 等效輸入雜訊14             |

| 3.3 轉阻放大器的模擬結果18         |

| 3.3.1 開迴路各參數             |

| 3.3.2 雜訊模擬圖形             |

| 3.3.3 可調外接偏壓對增益的影響       |

| 3.4 單端輸入限制與誤差22          |

| 3.4.1 誤差的造成23            |

| 3.4.2 積分器24              |

| 第四章 電荷感測電路               |

| 4.1 電荷感測之運算放大器29         |

| 4.1.1 隨機偏移電壓與電晶體不匹配30    |

| 4.1.2 選擇抑制系統偏移電壓的放大器電路32 |

| 4.2 放大器電路修改34            |

| 4.2.1 改善後之電路35           |

| 4.2.2 放大器電路輸出入組抗、增益36    |

| 4.2.3 放大器電路頻率響應          |

| 4.3 閉迴路系統40              |

| 4.3.1 輸出信號與輸入信號  | 40 |

|------------------|----|

| 4.3.2 放大級電路設計    | 44 |

| 第五章 解析度與雜訊       | 46 |

| 5.1 最小位移         | 46 |

| 5.2 等效輸出輸入雜訊推導   |    |

| 5.2.1 差動輸入級雜訊    | 48 |

| 5.2.2 全差動放大級     | 50 |

| 5.2.3 輸出級雜訊推導    | 51 |

| 5.2.4 電荷放大器總輸出雜訊 |    |

| 5.3 迴路增益與穩定性     |    |

| 第六章 結論           | 59 |

| 6.1 結果與討論        | 59 |

| 6.2 未來展望         | 59 |

| <b>参考文獻</b>      | 61 |

# 圖目錄

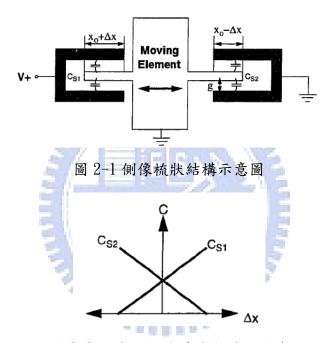

| 圖 2-1 | 側像梳狀結構示意圖                    | 4  |

|-------|------------------------------|----|

| 圖 2-2 | 側像梳狀結構電容變化曲線                 | 4  |

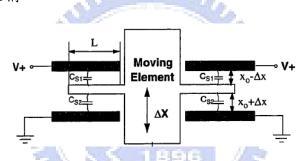

| 圖 2-3 | 横向梳狀結構示意圖                    | 5  |

| 圖 2-4 | 横向梳狀結構電容變化曲線                 | 5  |

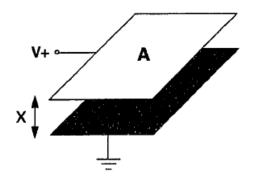

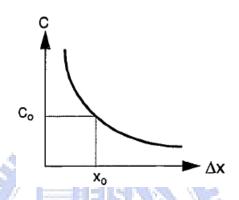

| 圖 2-5 | 平行版結構示意圖                     | 7  |

| 圖 2-6 | 平行版結構電容變化曲線                  | 7  |

| 圖 3-1 | 不包含偏壓電路的轉阻放大器                | 10 |

| 圖 3-2 | 包含偏壓電路的轉阻放大器]                | 11 |

| 圖 3-3 | 開迴路小信號圖形]                    | 11 |

| 圖 3-4 | 閉迴路小信號圖形]                    | 13 |

| 圖 3-5 | 轉阻放大器開迴路雜訊模型(1)              | 14 |

| 圖 3-6 | 轉阻放大器開迴路雜訊模型(2)              | 15 |

| 圖 3-7 | 電阻迴授圖形                       | 15 |

|       | 轉阻放大器閉迴路雜訊模型(1)              |    |

|       | 轉阻放大器閉迴路雜訊模型(2)              |    |

| 圖 3-1 | 0 轉阻放大器開迴路頻率響應]              | 19 |

| 圖 3-1 | 1轉阻放大器閉迴路頻率響應                | 19 |

|       | 2 轉阻放大器雜訊頻譜圖2                |    |

|       | 3 外接偏壓-輸出電壓曲線                |    |

|       | 4 電流感測系統                     |    |

| 圖 3-1 | 5無輸入偏移電壓的電荷感測系統              | 24 |

| 圖 3-1 | 6 有輸入偏移電壓的電荷感測系統             | 25 |

| 圖 3-1 | 7無輸入偏移電壓下電荷感測系統各節點電壓變化曲線(1)  | 26 |

| 圖 3-1 | 8無輸入偏移電壓下電荷感測系統各節點電壓變化曲線(2)  | 26 |

| 圖 3-1 | 9 有輸入偏移電壓下電荷感測系統各節點電壓變化曲線(1) | 27 |

| 圖 3-2 | 0 有輸入偏移電壓下電荷感測系統各節點電壓變化曲線(2) | 28 |

| 圖 4-1 | 電荷感測器的整體架構2                  | 29 |

| 圖 4-2 | NMOS差動輸入                     | 30 |

| 圖 4-3 | PMOS差動輸入                     | 32 |

| 圖 4-4 | 原始低偏移電壓放大器                   | 33 |

| 圖 4-5 | 低偏移電壓放大器略圖                   | 34 |

| 圖 4-6 | 一般運算放大器                      | 35 |

| 圖 4-7 | 修改後低偏移電壓放大器                  | 35 |

|       | 兩級放大器示意圖                     |    |

| 圖 4-9 | 加上CC之兩級放大器示意圖                | 37 |

| 圖 4-1 | 0 沒有加上Cc之電荷放大器頻率響應           | 39 |

| 圖 4-11 加上C電荷放大器頻率響應 · · · · · · · · · · · · · · · · · · · | 39 |

|-----------------------------------------------------------|----|

| 圖 4-12 電荷感測系統                                             |    |

| 圖 4-13 電荷感測系統各節點電壓曲線(1)                                   |    |

| 圖 4-14 電荷感測系統各節點電壓曲線(2)                                   | 44 |

| 圖 4-15 單級放大電路                                             | 44 |

| 圖 4-16 兩級放大電路                                             | 45 |

| 圖 5-1 電荷感測系統                                              | 46 |

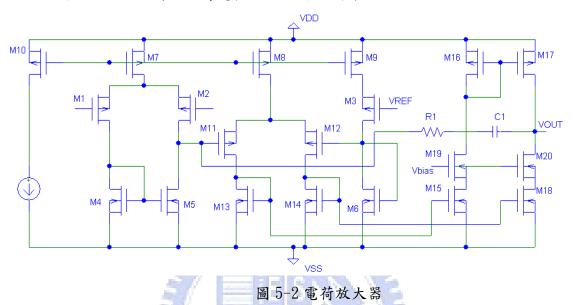

| 圖 5-2 電荷放大器                                               | 48 |

| 圖 5-3 差動輸入級雜訊模型                                           |    |

| 圖 5-4 差動輸入級等效輸入雜訊與無雜訊電路                                   |    |

| 圖 5-5 放大級電路雜訊模型                                           | 50 |

| 圖 5-6 電晶體M13 所貢獻的輸出雜訊圖形                                   |    |

| 圖 5-7 輸出級雜訊模型                                             | 52 |

| 圖 5-8 輸出級等效輸入雜訊與無雜訊電路                                     |    |

| 圖 5-9 負迴授系統方塊圖                                            | 54 |

| 圖 5-10 S-domain的負迴授、寄生電容和放大器增益表示圖                         |    |

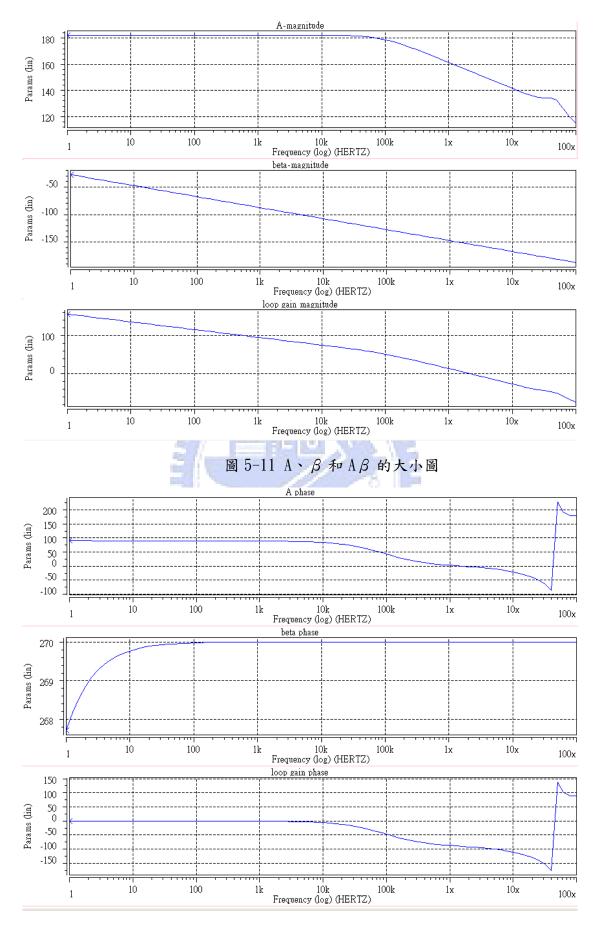

| 圖 5-11 A、 $\beta$ 和A $\beta$ 的大小圖                         | 57 |

| 圖 5-12 A、β和Aβ的相位圖                                         | 57 |

| 圖 5-13 迴路增益 $A\beta$ 的頻率響應圖形 $\dots$                      | 58 |

# 表目錄

| 表 | 2.   | 1 | 横向梳狀結 | <b>i構的各</b> | 項參  | `數. |    |   |   |   | <br> | <br> | <br> | <br> | <br> | <br> | . 8 |

|---|------|---|-------|-------------|-----|-----|----|---|---|---|------|------|------|------|------|------|-----|

| 表 | 3.   | 1 | 轉阻放大器 | 開迴路         | 、   | 迴趾  | 各模 | 擬 | 結 | 果 | <br> | <br> | <br> | <br> | <br> |      | 18  |

| 表 | 3. 2 | 2 | 轉阻放大器 | 參數規         | 格列  | ]表. |    |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 21  |

| 表 | 3. 8 | 3 | 外接偏壓與 | 增益變         | 化   |     |    |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 22  |

| 表 | 4.   | 1 | 電荷放大器 | 器参數模        | 英擬絲 | 吉果  |    |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 40  |

| 表 | 4.   | 2 | 放大級電路 | 各各電品        | 體   | 長寬! | 比. |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 45  |

| 表 | 5.   | 1 | 電荷放大器 | 各電晶         | 體長  | 寛に  | ե  |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 53  |

| 表 | 6.   | 1 | 電流感測和 | 1電荷感        | 測的  | 比車  | 交  |   |   |   | <br> | <br> | <br> | <br> | <br> |      | 59  |

## 第一章 序論

#### 1.1 研究背景與研究動機

微機電系統(Microelectromechanical Systems, MEMS)是指利用微機械加工 (Micro Machining)製造技術的微型精密系統,講求在微小尺寸的空間內控制並操作事物(註[1])。微機電系統技術主要源於1960年代積體電路技術的研究,四十年來隨著半導體工業的製程技術的迅速發展,也使得微機電的發展日益成熟。時至今日,MEMS已經是今日科技界公認最具有發展潛力以及前瞻性的研究領域。

一個完整的微機電系統包括微感測器(Micro Sensor)、微致動器(Micro Actuator)以及微電子電路(Micro Electronics)(註[2])。與傳統加工技術比較起來,使用微機電技術製作的產品有輕薄短小、低成本以及高精確度等優點,因此擁有高度的市場競爭優勢。目前已經商品化的微機電產品,包含資訊產業(如噴墨印表機噴嘴、投影機、掃瞄器)、光通訊(如光開關、RF 模組)、環境工程(如一氧化碳偵測器)、生醫產業(如血糖檢測、DNA 晶片)及汽車工業(安全氣囊、氣體偵測器、溫度偵測器)等等都是微機電領域的應用範疇。由以上可以發現微機電系統技術應用的普及和廣泛。

其中本論文所要探討的微定位器(Micropositioner)也屬於微機電系統的範疇,由於微定位器提供高精確度、高頻寬下的驅動以及較低的成本,因此可以應用於磁性和光學性的儲存設備(註[3])。為了改善微定位器的位置精確度和降低製程缺陷對性能的影響,往往會在其中加入回授控制,利用負迴授效應來穩定系統。

本論文研究首先會介紹各種微定位器的工作原理和分類,然而主要的篇幅還 是會著重在微定位器其感測電路的設計,論文中提出電流感測和電荷感測兩種不 同感測方式的感測電路,希望配合微系統整合技術,利用微電子電路的方法來產 生數位的輸出訊號,透過此輸出訊號來進一步掌控微定位器的動態,以期獲得價格低、體積小、重量輕和系統整合性高的微定位系統。

#### 1.2 論文架構

在第二章中將介紹微定位器的原理和分類,並從各類型的微定位器中比較其優缺點然後從中挑選出一個最適合的架構作為本論文研究的模型。

第三章中則會介紹電流輸入的放大器,並說明電流輸入是微定位器移動元件 速度的函數,並說明因為受限於電流單端輸入的電路架構而造成輸入節點位準的 飄移,進一步產生誤差;另外再用雜訊模型推導電流放大器的等效輸出、輸入雜 訊,以期能在設計之初就能藉由數學推算估算雜訊大小。

接著在第四章裡面就第三章電流放大器的缺點去做改正,提出電荷輸入的放大器架構,說明輸入的電荷是微定位器移動元件位置的函數;由於加上微定位器時變電容的整個系統形成積分器的架構,按照科西和夫電流定律寫出輸出信號和其他參數之間的關係;由於輸出信號可能不夠大所以需要後續增益來放大信號,因此在本章的最後介紹放大級電路的設計。

建立於第四章之上,第五章裡面先對電荷放大器的架構以雜訊模型推算其等效輸出、輸入雜訊,接著根據噪訊比的關係求得微定位器的位移解析度;並說明即使在電荷放大器的頻率響應不穩定的情況下,依然可以利用負迴授使得系統迴路增益的頻率響應呈現穩定。

第六章是本論文的結論,在此對電流和電荷兩種感測電路做比較,分析其特性和優缺點;在未來展望處提出後續研究的可行方向,期望在未來能夠把電路實體化並應用於實際的微定位器或是其他微機電系統上面。

## 第二章 静電式微定位器

#### 2.1 微定位器原理

微定位器(Micropositioner)屬於一種微機電系統。一般來說,在驅動和量 測微定位器時,為了減少製程的額外步驟和不必要的材料以及避免增加製程的複 雜性,所以選擇靜電式驅動(Electrostatic Actuation)和電容式位置感測 (Capacitive Position Sensing)的方式;而且值得注意的是,驅動端和感測端 能夠一起共用一個電極,這特性使得微定位器不需要再加上額外的內部連接層 (註[4])。

我們首先探討靜電力驅動以及電容感測的原理。當兩個電容平板間存在電壓差的時候則會產生靜電力。兩電容平板一旦距離改變,貯存在兩電容平板間的能量也會跟著改變,而靜電力就是兩平板間能量對位移的微分。因此靜電力即可寫成下式:

$$F = \frac{\partial E}{\partial x} = \frac{\partial}{\partial x} \left( \frac{CV_{dr}^2}{2} \right) \tag{2.1}$$

其中 V<sub>dr</sub>是兩電容平板間的偏壓,由(2.1)可知兩個間隙很小而且重疊面積很大的電容平板再加上大偏壓可以產生很大的靜電力。但是由(2.1)我們可以發現靜電力是偏壓的非線性函數,而且也往往是位移的非線性函數。

而電容感測原理可由下式說明:

$$C = \frac{\varepsilon_0 \varepsilon_r A}{x} \tag{2.2}$$

(2.2)中的 A 是兩平板的重疊面積,x 是兩平板間的間距, $\varepsilon_0$  是真空時的介電常數  $(electric\ permittivity)$ ,而  $\varepsilon_r$  是兩平板間介質的相關電介質常數  $(relative\ dielectric\ constant)$ 。

#### 2.2 微定位器的分類

在說明完靜電力驅動以及電容感測的原理後,接著就靜電式微定位器做說明。一般會把靜電式微定位器分做三種架構:側向梳狀結構(Lateral Comb Structure)、橫向梳狀結構(Transverse comb Structure)以及平行板結構(Parallel-plate Structure)。

#### 2.2.1 側向梳狀結構

圖 2-2 側像梳狀結構電容變化曲線

側向梳狀結構如圖 2-1 所示,其移動元件左右移動造成左右兩邊重疊面積改變,當向右邊移動時右邊兩平版重疊面積增大、左邊兩平板重疊面積縮小使得左右兩邊電容值不同;而向左邊移動時左邊兩平板重疊面積增大、右邊兩平板間重疊面積縮小。因此當移動元件移動時左右兩邊的感應電容大小分別為

$$C_{S1,S2} = \frac{\varepsilon N t(x_0 \pm \Delta x)}{g} \tag{2.3}$$

其中左邊右邊感應電容大小分別為  $C_{SI}$ 、 $C_{S2}$ , $\varepsilon$  是介電常數,t 是移動元件的厚度, $X_0$  是移動元件未發生移動前與左右兩平板的重疊部分長度, $\Delta X$  為移動元件的位移,g 是移動元件的電極和上下兩板間的距離,而  $\mathbb{N}$  是電極的總數。所以把

#### (2.3)對位移微分,我們可得到

$$\frac{dC_S}{dx} = \frac{\varepsilon Nt}{g} = \frac{C_{S0}}{x_0} \tag{2.4}$$

由(2.4)我們可以發現感應電容的大小對位移呈現性的關係,如圖 2-2 所示,而 把(2.4)帶入(2.1)得到靜電力大小

$$F = \frac{\partial C}{\partial x} \cdot \frac{V^2_{dr}}{2} = \left(\frac{\varepsilon Nt}{2g}\right) V_{dr}^2$$

(2.5)

側向梳狀結構的優點在於電容的變動和靜電力的大小與位移  $\Delta x$  無關;但其最大的缺點在於  $dC_s/dx$  和靜電力與同樣尺寸大小的橫向梳狀結構比較起來較小。

#### 2.2.2 横向梳狀結構

圖 2-3 橫向梳狀結構示意圖

圖 2-4 横向梳狀結構電容變化曲線

横向梳狀結構如圖 2-3 所示,其移動元件上下移動造成移動元件的電極與上下兩平板間距離的改變,向上移動時移動元件與上面平板間的距離縮小,而與下面平板間的距離增大,使得上端感應電容大於下端感應電容;而向下移動時移動元件與下面平板間的距離縮小,與上面平板間的距離增大使得下端感應電容大於上端感應電容。上下兩個感應電容大小分別為

$$C_{S1,S2} = \frac{\varepsilon NtL}{x_0 \pm \Delta x} \tag{2.6}$$

其中上面下面感應電容大小分別為  $C_{S1}$ 、 $C_{S2}$ ,  $\varepsilon$  是介電常數, t 是移動元件的厚度, L 是移動元件電極的長度,  $X_0$  是移動元件未移動前與上下兩平板間的距離,  $\Delta x$  是位移,而 N 是電極的總數。把(2.6)對位移微分可得

$$\left| \frac{dC_S}{dx} \right| = \frac{\varepsilon NtL}{x^2} = \frac{C_S(x)}{x} \tag{2.7}$$

而產生之靜電力大小為

$$F = \left(\frac{\varepsilon NtL}{2x^2}\right) V_{dr}^2 \tag{2.8}$$

分別比較式. (2.7)和式(2.4)以及(2.8)和(2.5)我們可以發現,對相同數量的電極來說,橫向梳狀結構的電容的改變量以及驅動的靜電力比側向梳狀結構的來的大上 L/x,即電極的長度對上與平板距離間距離的比值。另外由(2.7)我們知道電容的改變量和位移之間呈非線性的關係。把(2.6)的 Csi和 Csz相減再用利用泰勒展開式展開可以得到兩電容間的不匹配量:

$$\Delta C_S = C_{S1} - C_{S2} = \frac{2\varepsilon NtL}{x_0} \cdot \left(\frac{\Delta x}{x_0} + \left(\frac{\Delta x}{x_0}\right)^3 + \left(\frac{\Delta x}{x_0}\right)^5 + \dots\right)$$

(2.9)

偶次項因為相減而被消掉,所以電容的改變量的非線性程度由三次方項決定,若 (2.9)對位移微分可得到位移改變對電容改變的非線性程度的影響

Nonlinearity in

$$\frac{dC}{dx}$$

(%)  $\simeq \left(\frac{\Delta x}{x_0}\right)^2 \cdot 100\%$  (2.10)

其電容對位移的曲線如圖 2-4 所示,值得注意的是若位移很大的話那麼就必須對 非線性所造成的影響做考慮。

#### 2.2.3 平行板結構

圖 2-5 平行版結構示意圖

圖 2-6 平行版結構電容變化曲線

平行板結構的圖形如圖 2-5,其架構與橫向梳狀結構類似:移動元件沿著與平板垂直的方向上下運動,改變移動元件與平板間的距離造成電容大小的改變, 其感應的電容大小為

$$C_S = \frac{\varepsilon A}{x} \tag{2.11}$$

其中  $\varepsilon$  是介電常數, $\Lambda$  是移動元件平行板面積的大小,X 是移動元件與平板間的 距離。把(2.11)對位移微分可得

$$\left| \frac{dC_S}{dx} \right| = \frac{\varepsilon A}{x^2} = \frac{C_S(x)}{x} \tag{2.12}$$

其感應電容大小對位移的圖形如圖 2-6。而靜電力大小:

$$F = \left(\frac{\varepsilon A}{2x^2}\right) V_{dr}^2 \tag{2.13}$$

由於結構上的限制,平行板架構只有一個感應電容,所以需要另一個參考電容以移除位置感測信號的偏移量(offset);也因為是單端感測的緣故,泰勒展開

式中的偶次項未能因相減而抵銷,所以電容改變量的非線性程度高於橫向梳狀結構,電容改變量的非線性程度由二次方項決定。

Nonlinearity in

$$\frac{dC}{dx}$$

(%)  $\approx \frac{\Delta x}{x_0} \cdot 100\%$  (2.14)

#### 2.2.4 三種微定位器的比較

在上述的三種微定位器架構中,由於橫向梳狀結構的電容的改變量較大,以及(2.9)式的感應電容不匹配量的偶次項因為相減而消掉,使其不理想因素中的 非線性程度較低,因此在本論文中的後續章節就以橫向梳狀結構來討論。橫向梳 狀結構感應電容大小不匹配造成電荷的變化,把(2.9)帶入得到

$$\Delta Q = \Delta C_S \cdot V_{dr} = \frac{2\varepsilon NA}{x_0} \left[ \frac{\Delta x}{x_0} + \left( \frac{\Delta x}{x_0} \right)^3 + \dots \right] \cdot V_{dr} \simeq \frac{2\varepsilon NA\Delta x}{{x_0}^2} \cdot V_{dr}$$

(2.15)

而電流即為單位電荷對單位時間的變化

$$i = \frac{\Delta Q}{\Delta t} = \frac{2\varepsilon NAV_{dr} \cdot \Delta x}{x_0^2 \cdot \Delta t}$$

(2.16)

分別把此電流、電荷輸入適當的運算放大器,並藉由運算放大器的處理輸出得到數位訊號,此訊號為微定位器中移動元件速度和位移的函數。第三章先提出電流輸入的放大器電路;接著第四章再提出電荷輸入的放大器電路。本章的最後把橫向梳狀結構的各項參數列於表 2.1。

表 2.1 横向梳狀結構的各項參數

| Parameter                       | Transverse comb |

|---------------------------------|-----------------|

| Gap between electrodes( $x_0$ ) | 2μm             |

| Structure thickness(t)          | 10μm            |

| Number of electrodes(N)         | 100pairs        |

| Electrode length(l)             | 42.4μm          |

| Maximum displacement | $x_0/3$  |

|----------------------|----------|

| $C_{S}$              | 187.72fF |

## 第三章 感測電路分析

在本章節中使用一個轉阻放大器(Trans-impedance Amplifier)當作前述電流輸入的運算放大器,在本章中一開始先對轉阻放大器的各種規格、參數做說明;接著嘗試由轉阻放大器的雜訊模型推導等效輸入、輸出雜訊的表示式,並與Hspice程式模擬結果作驗證,以期在設計之初就能概略估算放大器的輸入、輸出雜訊。

#### 3.1轉阻放大器電路架構

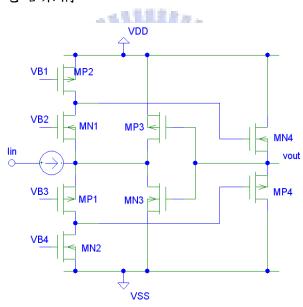

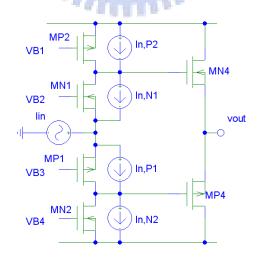

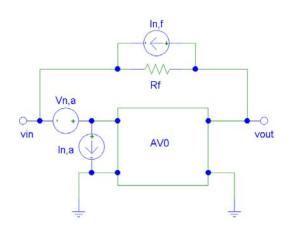

圖 3-1 不包含偏壓電路的轉阻放大器

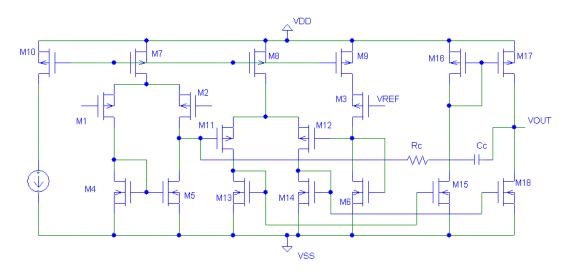

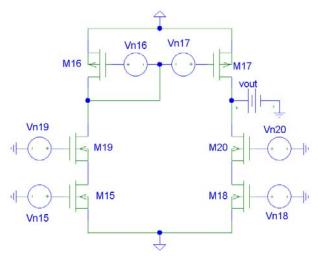

圖 3-1 是一個高增益、低雜訊以及高頻寬的轉阻運算放大器的圖形(註 [5][6])。V<sub>B1</sub> V<sub>B2</sub> V<sub>B3</sub> V<sub>B4</sub> 為偏壓,此轉阻放大器為電流輸入、電壓輸出,並在輸出端的地方連接一個反用換流器形式(inverter type)的迴授提供輸出電壓回授轉為電流至輸入端,所以此轉阻放大器是電流-電壓回授電路(shunt-shunt circuit)。共閘極組態的電晶體 M<sub>M1</sub>(M<sub>P1</sub>)和電流源 M<sub>P2</sub>(M<sub>M2</sub>)形成一個基本的電流一電壓架構。電晶體 M<sub>M4</sub>和 M<sub>P4</sub>形成一個推拉源極隨耦器(push-pull source-follower)輸出,推拉源極隨耦器可用來改善輸出的推動能力和減少輸出阻抗。電晶體 M<sub>M3</sub>

和 Mps構成一個反用換流器形式(inverter type)的轉導(trans-conductance), 提供輸出電壓轉成電流的回授路徑;除了提供回授路徑之外,由於負迴授效應所 以可以減少轉阻運算放大器的輸入和輸出阻抗。整體包括偏壓電路以及調變電晶 體的完整電路圖如圖 3-2。

圖 3-2 包含偏壓電路的轉阻放大器

896

# 3.1.1 開迴路分析

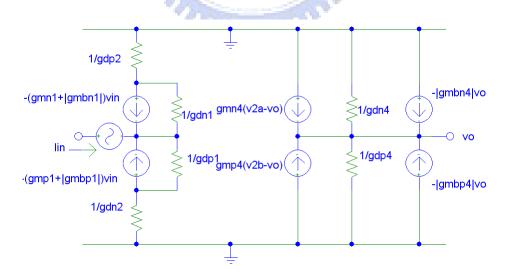

圖 3-3 開迴路小信號圖形

首先考慮開迴路的小信號模型(圖 3-3),根據科西和夫電流定律,通過單一 節點的淨電流總和為零,在此對所有的電晶體都假設 g' =g + |g b |,而且 gm>>gd, 因此可以寫出下面的關係式:

$$\begin{cases} v_{2a} \cdot g_{dP2} + \left(g_{mN1} + \left|g_{mbN1}\right|\right) \cdot (-v_i) + \left(v_{2a} - v_i\right) g_{dN1} = 0 \\ v_{2a} \cdot g_{dN2} + \left(g_{mP1} + \left|g_{mbP1}\right|\right) \cdot (-v_i) + \left(v_{2b} - v_i\right) g_{dP1} = 0 \end{cases}$$

(3.1)

$$I_{in} + \left(g_{mN1} + \left|g_{mbN1}\right|\right) \cdot (-v_i) + \left(v_{2a} - v_i\right)g_{dN1} + \left(g_{mP1} + \left|g_{mbP1}\right|\right) \cdot (-v_i) + \left(v_{2b} - v_i\right)g_{dP1} = 0$$

(3.2)

$$g_{mN4}(v_{2a} - v_o) + g_{mP4}(v_{2b} - v_o) - g_{dN4}v_o - g_{dP4}v_o - |g_{mbN4}|v_o - |g_{mbP4}|v_o = 0$$

(3.3)

從上面各式可以得到

$$\Rightarrow \begin{cases} v_{2a} = \frac{\left(g'_{mN1} + g_{dN1}\right)}{g_{dP2} / (g_{dN1})} v_i \approx \frac{g'_{mN1}}{g_{dP2} / (g_{dN1})} v_i \\ v_{2b} = \frac{\left(g'_{mP1} + g_{dP1}\right)}{g_{dN2} / (g_{dP1})} v_i \approx \frac{g'_{mP1}}{g_{dN2} / (g_{dP1})} v_i \end{cases}$$

$$(3.4)$$

$$\Rightarrow \frac{v_i}{I_i} = \frac{1}{g'_{mN1} \left[ 1 - g_{dN1} \left( r_{o,P2} // r_{o,N1} \right) \right] + g'_{mP1} \left[ 1 - g_{dP1} \left( r_{o,N2} // r_{o,P1} \right) \right]}$$

(3.5)

$$\Rightarrow \frac{v_o}{v_i} = \frac{g'_{mN4} + g'_{mP4}}{g_{mN4} \cdot g'_{mN1} (r_{o,P2} // r_{o,N1}) + g_{mP4} \cdot g'_{mP1} (r_{o,N2} // r_{o,P1})}$$

(3.6)

則開迴路增益  $r_m$   $l_{open} = \frac{v_o}{I_i} = \frac{v_i}{I_i} \cdot \frac{v_o}{v_i}$  可由 (3.5)(3.6) 相乘求得。

電晶體 Mni 和 Mpi 為共閘極組態(common gate),因此在計算輸入阻抗時可帶入共閘極組態的公式,

$$R_{in1} = \frac{r_{o,N1} + r_{o,P2}}{1 + (g_{mN1} + g_{mbN1})r_{o,N1}}$$

$$R_{in2} = \frac{r_{o,P1} + r_{o,N2}}{1 + (g_{mP1} + g_{mbP1})r_{o,P1}}$$

(3.7)

Rinl和 Rin2分別代表從輸入端向上看和向下看進去的阻抗,所以輸入阻抗就等於向上和向下的阻抗並聯,

$$R_{in}\mid_{open} = R_{in1} // R_{in2} \tag{3.8}$$

電晶體 MM和 MPA 為源極隨耦器(source follower)或稱共汲極組態(common drain),因此計算輸出阻抗時可帶入源極隨耦器的公式

$$R_{out1} = \frac{1}{g_{mN4}} / \frac{1}{g_{mbN4}} / r_{o,N4}$$

$$R_{out2} = \frac{1}{g_{mP4}} / \frac{1}{g_{mbP4}} / r_{o,P4}$$

(3.9)

其中 Routl 和分別代表從輸出端向上和向下的阻抗,因此輸出阻抗就等於從輸出端向上和向下的阻抗並聯,

$$R_{out} \mid_{open} = R_{out1} // R_{out2} \tag{3.10}$$

#### 3.1.2 閉迴路分析

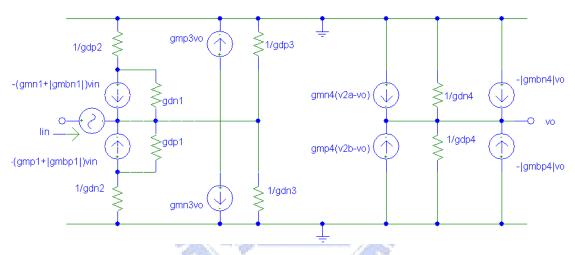

圖 3-4 閉迴路小信號圖形

接著再考慮整個閉迴路的小信號模型,如圖 3-4。同樣根據科西和夫電流守恆定律,並同樣對所有的電晶體都假設  $g'_{m}=g_{m}+|g_{mb}|$ 、 $g_{m}>>g_{d}$ ,可得到閉迴路的輸入阻抗以及輸出阻抗,其中輸入阻抗  $R_{in}$ 、 $R_{out}$  分別為

$$R_{in} \mid_{closed} = \frac{R_i}{1 + A\beta} = \frac{R_{in} \mid_{open}}{1 + r_m \mid_{open} \beta}$$

$$R_{out} \mid_{closed} = \frac{R_o}{1 + A\beta} = \frac{R_{out} \mid_{open} \beta}{1 + r_m \mid_{open} \beta}$$

(3.10)

而閉迴路的增益 rm可寫為

$$r_m = \frac{A}{1 + A\beta} = \frac{r_m \mid_{open}}{1 + r_m \mid_{open} \cdot \beta} \simeq \frac{1}{\beta} = \frac{1}{\left(g_{mN3} + g_{mP3}\right)}$$

(3.11)

為了因應製程的缺陷或是溫度的改變,這個運算放大器中加入可藉由外接偏

壓來調變增益的電晶體  $M_{NS}$ 和  $M_{PS}$ ,以補償時間常數可能的變動。由(3.11)我們知道閉迴路增益由負迴授路徑的  $M_{NS}$ 和  $M_{PS}$ 所控制,因此控制增益的最好方法就是改變負回授路徑上兩電晶體的閘極-源極電壓( $V_{CS}$ )。所以各在  $M_{NS}$ 和  $M_{PS}$ 的源極端加上兩個電晶體  $M_{PR}$ 和  $M_{NR}$ ,可調的外接偏壓  $V_{CP}$ 和  $V_{CN}$ 分別接在其閘級以控制  $V_{CS}$ ,NS和  $V_{CS}$ ,PS 以達到調整增益的目的;但為了線性的考量必須同時調整  $V_{CP}$ 和  $V_{CN}$ ,使得  $V_{CN}$  =  $-V_{CP}$ 。當偏壓上升時,操作在線性區的電晶體  $M_{NR}$ 和  $M_{PR}$ 電阻減小,使得閉迴路增益  $r_{III}$  變小並且使得頻寬變高;而當偏壓下降時,操作在線性區的電晶體  $M_{NR}$ 和  $M_{PR}$ 電阻上升使得閉迴路增益  $r_{III}$  變大並且使得頻寬減小。

#### 3.2 等效輸入雜訊

對類比電路來說,若能夠事先以數學表示式估算雜訊,判斷雜訊是否大於信號,那麼就可以避免信號被雜訊蓋掉,否則就算最後量測時量到的也是無任何意義的雜訊,因此在本節中要推導等效輸入雜訊,以此推導算出的雜訊與 H-spice 模擬的結果做比較,以判斷推算的雜訊數學式是否精確。在推導的部分,為了簡化推導過程,因此只考慮熱雜訊(thermal noise)而不考慮閃爍雜訊(flicker noise)。

圖 3-5 轉阻放大器開迴路雜訊模型(1)

圖 3-6 轉阻放大器開迴路雜訊模型(2)

要推得閉迴路的等效雜訊首先必須把負迴授路徑拿掉,先求得開迴路的等效雜訊。圖 3-5 是沒有負迴授的開迴路雜訊模型,我們試圖把  $M_{P2}$ 、 $M_{N1}$ 、 $M_{P1}$  以及  $M_{N2}$  造成的雜訊電流源  $I_{n}^{2}$ ,P2、 $I_{n}^{2}$ ,N1、 $I_{n}^{2}$ ,P1 和  $I_{n}^{2}$ ,N2 逆推回輸入端,如圖 3-6 中所示。由於我們所要得到的是開迴路的輸入雜訊頻譜密度  $I_{n}^{2}$ ,in/  $\Delta f$  ,藉由輸入端開路 (open-circuiting)(註[7][8]),我們可以忽略  $I_{n}^{2}$ ,N1 和  $I_{n}^{2}$ ,P1 對等效輸入雜訊的影響,會貢獻雜訊提及至輸入雜訊  $I_{n}^{2}$ ,in/  $\Delta f$  只有  $I_{n}^{2}$ ,P2 和  $I_{n}^{2}$ ,N2 兩項,則

$$I_{n}^{2}_{,in} = I_{n}^{2}_{,P2} + I_{n}^{2}_{,N2} = \frac{8}{3}kT(g_{mP2} + g_{mN2})$$

(3.12)

(3.12)的 k 為波茲曼常數(Boltzmann constant), k=1.38×10<sup>-23</sup>J/K, T 為絕對溫度, 一般考慮常溫下的絕對溫度為 300K。

圖 3-7 電阻迴授圖形

接著再考慮閉迴路的情況。我們先假設單純的電阻(註[9])代替複雜的反用

換流器,如圖 3-7 所示,再利用同樣方法計算迴授為反用換流器的情形。

$$I_{n,i}^{-2} = I_{n,a}^{-2} + \frac{v_{n,a}^{-2}}{R_F^2} + I_{n,f}^{-2} \Delta f = I_{n,a}^{-2} + \frac{v_{n,a}^{-2}}{R_F^2} + 4kT \frac{1}{R_F} \Delta f$$

(3.13)

在這邊  $V_{n,a}$  和  $i_{n,a}$ 分別代表開迴路的的輸入雜訊電壓和輸入雜訊電流,而雜訊電流源  $I_{n,f}$  則是由迴授電阻  $R_F$ 所造成,把這些雜訊源推回閉迴路的輸入端則可得到閉迴路的等效輸入雜訊電流  $I_{n,i}$ 。(3.13)的第二項可以被忽略掉,所以上式變成:

$$I_{n,i}^{-2} = I_{n,a}^{-2} + 4kT \frac{1}{R_F} \Delta f \tag{3.14}$$

現在回到原本的閉迴路電路,把圖3-7的電阻換回反用換流器重畫得圖3-8,

圖 3-8 轉阻放大器閉迴路雜訊模型(1)

在上圖中  $V_{n,a}$  和  $I_{n,a}$ 分別代表不包含反用換流器雜訊電流的開迴路電路的輸入雜訊電壓和輸入雜訊電流,而反用換流器產生的雜訊電流源以  $I_{n,P3}$  、  $I_{n,N3}$  表示;與圖 3-7 類似,把雜訊源推回閉迴路的輸入端則可得到閉迴路的等效輸入雜訊電流  $I_{n,i}$  ,圖 3-8 等效為圖 3-9。

圖 3-9 轉阻放大器閉迴路雜訊模型(2)

其中把(3-14)等號右邊第二項,也就是回授電阻所產生的雜訊電流源替換成 反用換流器產生的雜訊電流,故可得下式:

$$I_{n,i}^{-2} = I_{n,a}^{-2} + \left(I_{n,P3}^{-2} + I_{n,N3}^{-2}\right) \Delta f = I_{n,a}^{-2} + \frac{8}{3}kT(g_{mP3} + g_{mN3}) \Delta f$$

(3.15)

(3.15)整理後如(3.16)

$$\frac{I_{n,i}^{-2}}{\Delta f} = \frac{I_{n,a}^{-2}}{\Delta f} + \frac{8}{3}kT(g_{mP3} + g_{mN3})$$

(3-16)

(3.16)中的  $i^2_{n,a}/\Delta f$  即為(3.12)中的  $i^2_{n,in}/\Delta f$ ,把(3.12)帶入(3.16)後可求得閉 迴路的等效輸入雜訊頻譜密度。

輸入雜訊頻譜密度經過積分得到總等效輸入雜訊電流(註[9])。

$$\overline{I_{i,total}} = \sqrt{\int_0^\infty S_{i0} df} \simeq \sqrt{\frac{I_{n,i}^{-2}}{\Delta f}} \cdot f_{3dB}$$

(3.17)

(3.17)中的  $f_{3dB}$ 是運算放大器的 3dB 頻率,而  $S_{i0}$ 是等效輸入雜訊頻譜密度,在低頻及中頻的情況下可視為一定值。將數據帶入(3.17),手算結果為  $281\times10^{-9}$  安培,H-spice 的模擬出來的數據是  $499\times10^{-9}$  安培,兩者數值相當接近,故藉由等效輸入雜訊的推導可大略推估出整體電路的輸入雜訊。

在推導出輸入雜訊之後進一步使用噪訊比(Signal to Noise Ratio, SNR)的觀念,

$$SNR = \frac{i_{\min}}{I_{i,total}} = 1 \Rightarrow i_{\min} = I_{i,total}$$

(3.18)

在噪訊比等於一時最小可偵測輸入電流等於雜訊輸入電流。然後再帶入(2.16)

重寫為

$$i_{min} = \frac{\Delta Q}{\Delta t} = \frac{2\varepsilon NAV_S \cdot \Delta x}{x_0^2 \cdot \Delta t}$$

(3.19)

即可得到最小可偵測的速度大小為 2.658m/s。

### 3.3 轉阻放大器的模擬結果

這節分別列出開閉迴路參數、雜訊頻譜和調變增益的外接偏壓的模擬結果。

#### 3.3.1 開迴路各參數

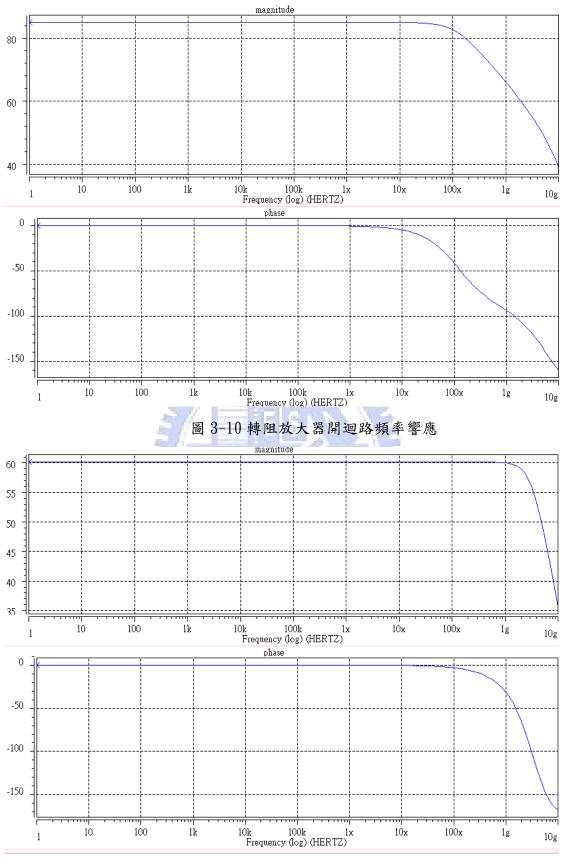

設可調的外接偏壓  $V_{\text{CN}}=-V_{\text{CP}}=0$ ,在此情況下其開迴路和閉迴路頻率響應圖形分別如圖 3-10、3.11 所示,而輸出輸入以及增益分別列於表 3.1。

表 3.1 轉阻放大器開迴路、閉迴路模擬結果

| 77     | 開迴路                     | 閉迴路                     |

|--------|-------------------------|-------------------------|

| 增益     | 85dB                    | 60. 2dB                 |

| 輸入組抗   | $1.6367$ k $\Omega$     | 94. 91 Ω                |

| 輸出組抗   | 190. $29\Omega$         | 12. 19 Ω                |

| 3dB 頻率 | 1.17×10 <sup>8</sup> Hz | 2.81×10 <sup>9</sup> Hz |

圖 3-11 轉阻放大器閉迴路頻率響應

由表 3.1 可以驗證由於負迴授的效應使得閉迴路的增益、輸出入阻抗都比開

迴路來的小,唯一不同的是 3dB 頻率,這是由於單位增益頻率(unit-gain frequency)是直流增益和 3dB 頻率的乘積,而單位增益頻率對一個有無迴授的開迴路或閉迴路電路來說都相同,閉迴路的直流增益因為負迴授效應較開迴路減小,故其 3dB 頻率上升。

#### 3.3.2 雜訊模擬圖形

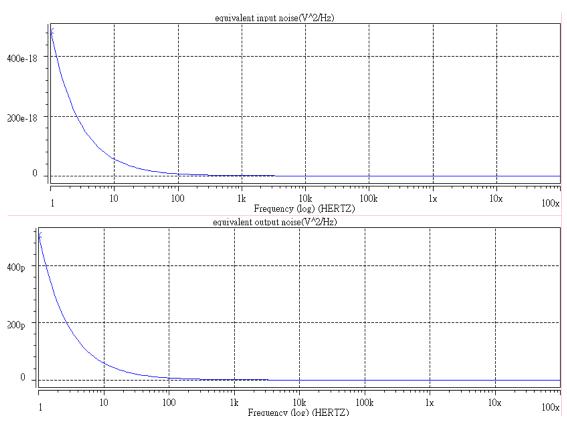

在前述的雜訊推導模型中只考慮熱雜訊而忽略閃爍雜訊,熱雜訊的雜訊頻譜不隨頻率改變,但閃爍雜訊(flicker noise)會隨頻率增大而減小。圖 3-12 是輸入和輸出閃爍雜訊的圖形。

圖 3-12 轉阻放大器雜訊頻譜圖

在本節的最後列出 Hspice 的模擬結果,如表 3.2 所示。

表 3.2 轉阻放大器參數規格列表

|        | 模擬結果      |

|--------|-----------|

| 增益     | 60. 2dBΩ  |

| 3dB 頻率 | 2.81GHz   |

| 輸入阻抗   | 94. 91 Ω  |

| 輸出阻抗   | 12. 19 Ω  |

| 消耗功率   | 8.1627mW  |

| 最小偵測信號 | 499 n-amp |

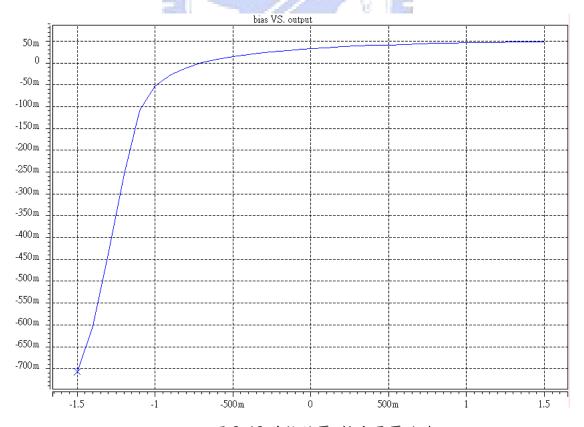

# 3.3.3 可調外接偏壓對增益的影響

前面已經敘述過為了因應製程的缺陷或是溫度的改變,可藉由外接偏壓來調變增益。因此在這小節中分別模擬在不同偏壓的情況下增益改變的情形。圖 3-13 是改變  $V_{CN}=-V_{CP}$ 從負 1.5 伏特到 1.5 伏特其輸出電壓的曲線圖。

圖 3-13 外接偏壓-輸出電壓曲線

表 3.3 列出外接偏壓從-1.5 伏特到 1.5 伏特每 0.5 伏特一區間的輸出電壓對輸入電流的增益變化。

| 偏壓 VcN=−VcP | 輸出電壓對輸入電流增益(Ω) |

|-------------|----------------|

| -1.5volt    | 3. 1106k       |

| -1. 0volt   | 1. 4509k       |

| -0.5volt    | 1. 0973k       |

| 0volt       | 1. 0213k       |

| 0.5volt     | 987. 7071      |

| 1.0volt     | 969. 3342      |

| 1.5volt     | 958. 276       |

表 3.3 外接偏壓與增益變化

# 3.4 單端輸入限制與誤差

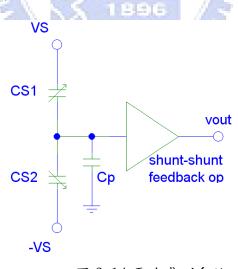

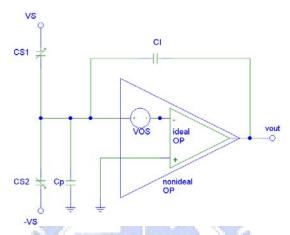

圖 3-14 電流感測系統

在第二章中討論了微定位器的架構,而在本章的前面幾節中詳述放大器電路的分析,本節把微定位器系統接於放大器的輸入端圖,微定位器電容不匹配形成電荷,單位時間的電荷變化產生電流直接輸入放大器,其示意圖如圖 3-14 所示,

±Vs為電壓測試信號,Cs1,2分別是兩個感應電容,右邊是單端輸入、單端輸出 (single-input single-output)的電流-電壓轉阻放大器,另外考慮了在輸入端寄生電容 Cp 的影響。

#### 3.4.1 誤差的造成

為了模擬兩個隨時間變動的感應電容,因此使用電壓控制電容 (voltage - control capacitor)(註[10]),其中控制電壓為正弦輸入 (sinusoidal input),當電容控制電壓隨時間變動時,電容的大小也隨時間改變,假設在時間 t 時兩電容大小分別為

$$C_{S1,2} = C_0 \pm \frac{\Delta C}{2} \sin \omega_m t \tag{3.20}$$

$C_0$ 是微定位器沒有位移時的電容大小, $\Delta C$  是電容的最大變化量, $\omega_m$ 為控制電壓的頻率,也就是實際上微定位器震動的頻率。而因為電容不匹配形成的淨電荷 Q

$$Q = Q_1 + Q_2 = \left(C_0 + \frac{\Delta C}{2}\sin\omega_m t\right)\left(V_S - v_{in}\right) + \left(C_0 - \frac{\Delta C}{2}\sin\omega_m t\right)\left(-V_S - v_{in}\right)$$

$$= 2\left(\frac{1}{2}V_S\Delta C\sin\omega_m t - C_0v_{in}\right)$$

(3.21)

單位時間內電荷的改變就是流入的電流,因此對(3.19)間微分可得到電流關係式:

$$i = \frac{dQ}{dt} = 2\left(\frac{1}{2}V_S\Delta C\omega_m\cos\omega_m t - c_0\frac{dv_{in}}{dt}\right)$$

(3.22)

若 Vin 的變化幅度很小,則(3.20)第二項可被忽略掉,可寫為

$$i = \frac{dQ}{dt} = V_S \Delta C \omega_m \cos \omega_m t \tag{3.23}$$

但事實上由於單端輸入的限制無法使用虛擬短路(virtual ground)來抑制輸入端點電壓的變動,造成輸入端電壓位準的飄移。若再加上輸入端上寄生電容的影響,則流入寄生電容 Cp 的電流大小為

$$i_{Cp} = C_P \frac{dv_{in}}{dt} \tag{3.24}$$

由(3,20)、(3,22), 流入放大器的輸入電流 in可寫作

$$i_{in} = i - i_{Cp} = V_S \Delta C \omega_m \cos \omega_m t - (2C_0 + C_P) \frac{dv_{in}}{dt}$$

(3.25)

若將數據帶入(3.23)可得

$$i_{in} = 6.95 \times 10^{-11} \cos \omega_m t - 7.81 \times 10^{-13} \frac{dv_{in}}{dt} = 6.95 \times 10^{-11} \cos \omega_m t - 1.963 \times 10^{-10} \sin \omega_m t$$

輸入電流不再與位移的微分成正比,造成誤差的產生。

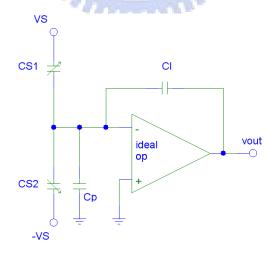

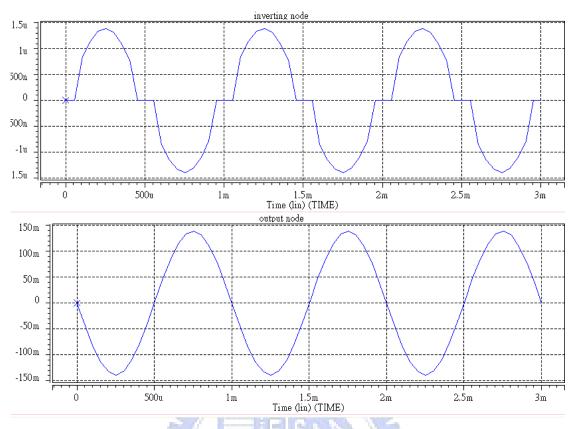

#### 3.4.2 積分器

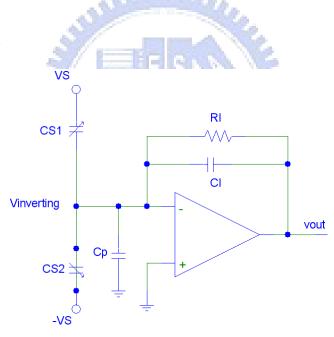

在上一小節裡面我們知道因為單端輸入的限制使得輸入端位準會產生飄移的情況,因此若我們使用差動輸入的放大器,並將其中一個輸入端接地,則可利用虛擬接地的效應抑制另一個輸入端點的位準變化。所以除了前述的單端輸入的轉阻放大器外,我們再另外考慮差動輸入的放大器,在Hspice模擬時為了方便觀察其特性,先使用高增益的電壓控制電壓源代替運算放大器的內部電路。如圖3-15 所示由電容不匹配所造成的電荷經由電容 Cı 產生輸出,形成類似積分器的架構,Cp 為寄生電容。

圖 3-15 無輸入偏移電壓的電荷感測系統

實際上即使差動輸入對兩端輸入皆為零其輸出電壓也不等於零,這是來自於製程缺陷造成原本應該一致的電晶體產生不匹配、或是設計上的不縝密使得其中

一端必須串連一微小的偏壓方能使輸出電壓等於零,這偏壓值定義為輸入偏移電壓(input offset voltage)。

圖 3-15 不考慮輸入偏移電壓,但是對於一個真實的放大器來說,輸入偏移電壓必然存在。因此為了觀察輸入偏移電壓造成的影響在反相輸入節點再加上一個直流電壓源 Vos 來模擬之。圖 3-16 為其示意圖。

圖 3-16 有輸入偏移電壓的電荷感測系統

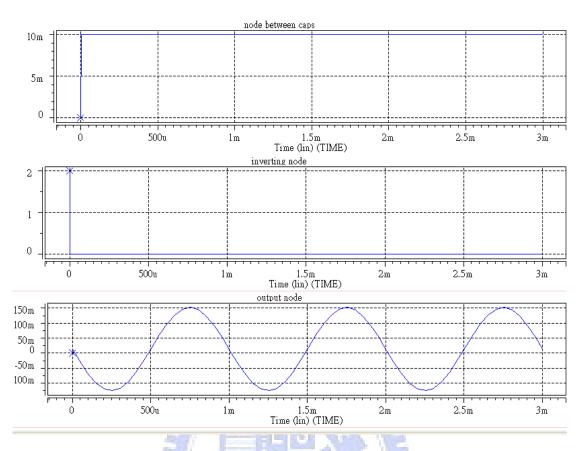

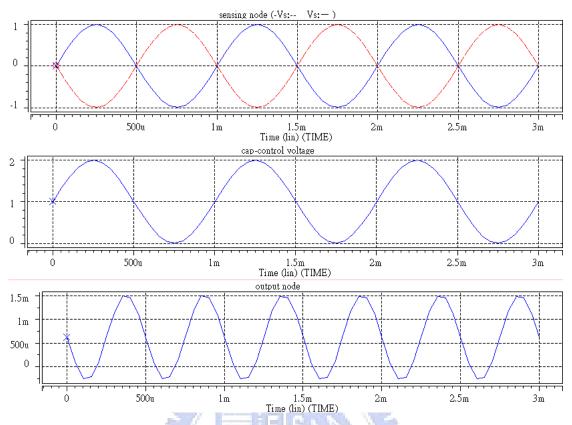

以下各圖要說明因為差動輸入的虛擬接地造成的影響。先就有無輸入偏移電壓的情形下(圖 3-15 和圖 3-16),觀察其分別在反相輸入節點和輸出節點的電壓變化曲線,圖形分別如圖 3-17、圖 3-18 所示。

Maria Contraction of the last of the last

圖 3-17 無輸入偏移電壓下電荷感測系統各節點電壓變化曲線(1)

圖 3-18 無輸入偏移電壓下電荷感測系統各節點電壓變化曲線(2)

圖 3-19、3.20 分別為偏移電壓不等於零、反相端節點初始電壓等於零和不等於

零的電壓變化曲線圖形。由於尺度的關係使圖 3-19 兩電容間節點電壓看起來是 一直線,但實際上仍為弦波。

圖 3-19 有輸入偏移電壓下電荷感測系統各節點電壓變化曲線(1)

South Printers

圖 3-20 有輸入偏移電壓下電荷感測系統各節點電壓變化曲線(2)

由圖 3-17、圖 3-18、圖 3-19 和圖 3-20 可以觀察出無論偏移電壓是否等於零以及反向端初始電壓為是否為零的情況下,反向端與非反相端節點都會因為受到虛擬接地效應的抑制使得電壓差值很小。

# 第四章 電荷感測電路

電流和電荷分別是微定位器速度和位移的函數,在前述幾章中已詳述過用來 做電流感測的轉阻放大器的電路架構,也敘述了由於單端輸入的限制造成輸入節 點位準飄移,使得輸入電流無法完全正比於微定位器改變的速度進而產生誤差; 因此需要差動輸入的放大器來抑制位準的飄移。故本章將探討電荷放大器內部電 路的設計,包括內部運算放大器的架構、閉迴路系統輸出與輸入之間的關係以及 後續的信號放大電路。

# 4.1 電荷感測之運算放大器

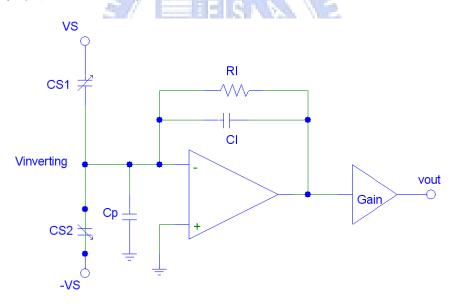

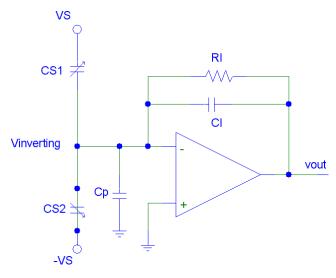

電荷感測器的整體架構如圖 4-1。

圖 4-1 電荷感測器的整體架構

其中±Vs為測試電壓信號,一般而言測試電壓信號為方波或正弦波,但在模擬時為了方便起見將測試信號設為固定的直流電壓。感測電容 Cs1.2 隨時間改變,Cs1 變大時 Cs2 減小,反之亦然;兩電容大小改變時會產生一正比於兩電容不匹配的電荷,由反向輸入端通過電容 Ci 形成類似積分器的效果;電阻 Ri 形成負回授,用來設定非反向輸入端節點的偏壓;由於考量到輸出信號不夠大,因此在第一個

輸出端之後再加上一個放大級電路。

Cp為寄生電容,由於寄生電容的存在,使得運算放大器的輸入偏移電壓會對輸出信號造成誤差,因此在選擇運算放大器時必須要選擇輸入偏移電壓小的運算放大器。

在運算放大器中偏移電壓可以分成兩種:1. 隨機偏移電壓(random offset), 2. 系統偏移電壓(systematic offset)。

隨機偏移電壓是由於製程的缺陷造成,使得原本需要完全一致的電晶體產生不匹配,造成偏壓電流、轉導、起點電壓(threshold voltage)、通道長度調變係數(channel length modulation)等參數間的差異。系統偏移電壓則是由於電路設計的不周延所產生。

### 4.1.1 隨機偏移電壓與電晶體不匹配

在此先就隨機偏移電壓來討論。對於隨機偏移電壓來說,雖然無法確實避免 製程的缺陷,但是可以藉由設計時調大差動輸入對的電晶體和負載電晶體的長 度、寬度來縮減隨機偏移電壓(註[11])。

圖 4-2 NMOS 差動輸入

就一個 NMOS 的差動輸入對如圖 4-2,若兩個電晶體 M<sub>1</sub>、M<sub>2</sub>存在不匹配,流過兩電晶體的偏壓電流分別為 I<sub>D1</sub>、I<sub>D2</sub>

$$I_{D1} = \frac{1}{2} \left( \beta_n + \frac{\Delta \beta_n}{2} \right) \left( V_{GSn} + \frac{\Delta V_{GSn}}{2} - V_{tn} - \frac{\Delta V_{tn}}{2} \right)^2 \left( 1 + \left( \lambda_n + \frac{\Delta \lambda_n}{2} \right) \left( V_{DSn} + \frac{\Delta V_{DSn}}{2} \right) \right)$$

$$I_{D2} = \frac{1}{2} \left( \beta_n - \frac{\Delta \beta_n}{2} \right) \left( V_{GSn} - \frac{\Delta V_{GSn}}{2} - V_{tn} + \frac{\Delta V_{tn}}{2} \right)^2 \left( 1 + \left( \lambda_n - \frac{\Delta \lambda_n}{2} \right) \left( V_{DSn} - \frac{\Delta V_{DSn}}{2} \right) \right)$$

$$(4.1)$$

$eta_n$ 為  $\mu_n C_{ox} W/L$  乘積的常數, $V_t$ 為起點電壓, $\lambda$  為通道長度調變係數。兩偏壓電流的差  $\Delta$   $I_D$ 為  $I_{DI}-I_{D2}$ 。假設  $I_D$ 為兩電晶體完全一致下流過電晶體的偏壓電流,

$$I_{D} = \frac{\beta_{n}}{2} (V_{GSn} - V_{m})^{2} (1 + \lambda_{n} V_{DSn})$$

(4.2)

對 NMOS 的差動輸入對來說,△I□除以 I□可寫為

$$\frac{\Delta I_D}{I_D} = \frac{\Delta \beta_n}{\beta_n} - 2 \frac{\Delta V_{tn}}{V_{GSn} - V_{tn}} + V_{DS,n} \frac{\Delta \lambda_n}{1 + \lambda_n V_{DSn}} + 2 \frac{\Delta V_{GSn}}{V_{GSn} - V_{tn}} + \lambda_n \frac{\Delta V_{DSn}}{1 + \lambda_n V_{DSn}}$$

(4.3)

因為  $V_3 = V_{out}$  (即  $\Delta V_{DSn} = 0$ ),由(4.3)可以整理得到

$$V_{OS,\text{random}} = \Delta V_{GSn} = \Delta V_{tn} - \frac{V_{GSn} - V_{tn}}{2\beta_n} \Delta \beta_n - \frac{V_{GSn} - V_{tn}}{2(1 + \lambda_n V_{DSn})} V_{DSn} \Delta \lambda_n - \frac{V_{GSn} - V_{tn}}{I_{SS}} \Delta I_D$$

$$(4.4)$$

而對 PMOS 的負載來說,因為  $\Delta V_{SG,p}$  等於零,故(4.3)可以改寫為

$$\frac{\Delta I_D}{I_D} = \frac{\Delta I_D}{I_{SS}/2} = \frac{\Delta \beta_p}{\beta_p} - 2\frac{\Delta V_{tp}}{V_{SGp} - V_{tp}} + V_{SDp} \frac{\Delta \lambda_p}{1 + \lambda_p V_{SDp}}$$

$$(4.5)$$

把(4.5)帶回(4.4)的最後一項可得到隨機偏移電壓 Vos, random

$$V_{OS} = \Delta V_{tn} - \frac{V_{GSn} - V_{tn}}{V_{SGp} - V_{tp}} \Delta V_{tp} - \frac{V_{GSn} - V_{tn}}{2} \left( \frac{\Delta \beta_n}{\beta_n} - \frac{\Delta \beta_p}{\beta_p} + \frac{V_{DSn}}{1 + \lambda_n V_{DSn}} \Delta \lambda_n - \frac{V_{SDp}}{1 + \lambda_p V_{SDp}} \Delta \lambda_p \right)$$

$$(4.6)$$

對(4.6)取變異量(variance)可得

$$\sigma^{2}(V_{OS}) = \sigma^{2}(\Delta V_{tn}) + \left(\frac{V_{GSn} - V_{tn}}{V_{SGp} - V_{tp}}\right)^{2} \sigma^{2}(\Delta V_{tp})$$

$$+ \left(\frac{V_{GSn} - V_{tn}}{2}\right)^{2} \left[\frac{\sigma^{2}(\Delta \beta_{n})}{\beta_{n}^{2}} + \frac{\sigma^{2}(\Delta \beta_{p})}{\beta_{p}^{2}} + \left(\frac{V_{DSn}}{1 + \lambda_{n}V_{DSn}}\right)^{2} \sigma^{2}(\Delta \lambda_{n}) + \left(\frac{V_{SDp}}{1 + \lambda_{p}V_{SDp}}\right)^{2} \sigma^{2}(\Delta \lambda_{p})\right]$$

$$(4.7)$$

圖 4-3 PMOS 差動輸入

同(4.7),依同樣的方法可推得如圖 4-3 的 PMOS 差動輸入對的隨機偏移電壓的變異量。

$$\sigma^{2}(V_{OS}) = \sigma^{2}(\Delta V_{tp}) + \left(\frac{V_{SGp} - V_{tp}}{V_{GSn} - V_{tn}}\right)^{2} \sigma^{2}(\Delta V_{tn})$$

$$+ \left(\frac{V_{SGp} - V_{tp}}{2}\right)^{2} \left[\frac{\sigma^{2}(\Delta \beta_{p})}{\beta_{p}^{2}} + \frac{\sigma^{2}(\Delta \beta_{n})}{\beta_{n}^{2}} + \left(\frac{V_{SDp}}{1 + \lambda_{p}V_{SDp}}\right)^{2} \sigma^{2}(\Delta \lambda_{p}) + \left(\frac{V_{DSn}}{1 + \lambda_{n}V_{DSn}}\right)^{2} \sigma^{2}(\Delta \lambda_{n})\right]$$

$$= \sigma^{2}(\Delta V_{tp}) + \frac{\beta_{n}}{\beta_{p}} \sigma^{2}(\Delta V_{tn}) + \frac{I_{D}}{2\beta_{p}} \left(\frac{\sigma^{2}(\Delta \beta_{p})}{\beta_{p}^{2}} + \frac{\sigma^{2}(\Delta \beta_{n})}{\beta_{n}^{2}}\right)$$

$$+ \frac{I_{D}}{2\beta_{p}} \left[\left(\frac{V_{SDp}}{1 + \lambda_{p}V_{SDp}}\right)^{2} \sigma^{2}(\Delta \lambda_{p}) + \left(\frac{V_{DSn}}{1 + \lambda_{n}V_{DSn}}\right)^{2} \sigma^{2}(\Delta \lambda_{n})\right]$$

$$(4.8)$$

由(4.8)中可以得知縮小偏壓電流可以使得第三項減小;而由於長通道負載電晶體的使用,加上為了減小雜訊故差動對的轉導通常很大,因此第二項也可以被忽略掉。若是對應的電晶體其通道長度不是製程所限制的極端邊緣長度,那麼第四項和第五項也都可以被忽略。因此第一項也就是差動輸入的起點電壓不匹配主要影響偏移電壓。

#### 4.1.2 選擇抑制系統偏移電壓的放大器電路

在推導出影響隨機偏移電壓的主要不匹配因素後,接著考慮系統偏移電壓。若製程沒有使得兩電晶體不匹配,那麼差動輸入對的兩負載電晶體汲極電壓必然相同;但是實際上因為不匹配使得兩負載電晶體間的汲極和源級產生偏壓差 $\Delta V_{DS}$ ,而  $\Delta V_{DS}$ 是造成系統偏移電壓的主要原因,所以在選擇適合的運算放大器

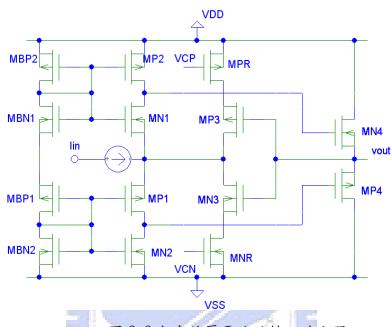

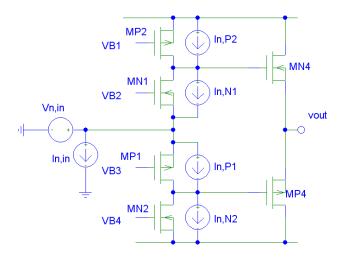

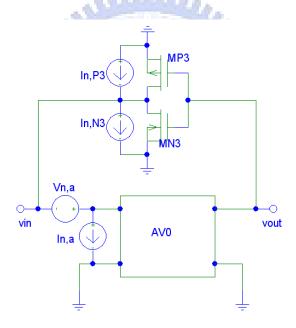

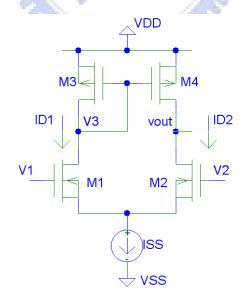

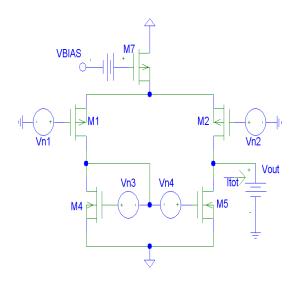

時要優先考慮這一點。在此我們所選擇的運算放大器如圖 4-4 所示(註[12])。

圖 4-4 原始低偏移電壓放大器

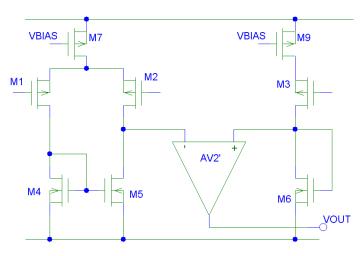

此運算放大器分為四個部分:差動輸入級,複製增益級(replica-gain stage),輸出級和偏壓電路(bias stage)。

差動輸入級由 M1、M2、M4、M5 和 M7 五顆電晶體構成,選擇 PMOS 的 M1、M2 為輸入對和 NMOS 的 M4、M5 為負載電晶體。

複製增益級分為複製偏壓電路(replica-biasing generator)和全差動放大電路(fully differential amplifier)。複製偏壓電路其實是差動輸入級的左半電路,由 M3、M6、M9 三顆電晶體組成,與 M1、M4、M7 對稱。由於半電路的緣故,在設計時若把 M7 的長寬比值(aspect ratio)設為 M9 長寬比值的兩倍,會使得流過 M4 和 M6 的偏壓電流相等,再藉由電晶體操作在飽和區的電流公式:

$$I_{D} = \frac{1}{2} \mu_{n} c_{OX} \frac{W}{L} (V_{GS} - V_{tn})^{2}$$

(4.9)

把(4.9)改寫可寫成

$$I_D = \frac{1}{2} \mu_n c_{OX} \frac{W}{L} V_{OD}^2 \tag{4.10}$$

其中 VoD=VGS-VtN稱為過度驅使電壓(overdrive voltage), M4 和 M6 由於偏壓電流相同故過度驅使電壓也相同,這使得 M6 汲極電壓 VD6 和 M4 汲極電壓 VD4 相同。

接著考慮複製增益級的全差動放大電路,由 M11、M12、M13、M14 和 M8 五顆電晶體構成。藉由其中的差動輸入把 M11、M12 的閘級電壓鎖住,使得 M5 和 M6

的汲極電壓 V<sub>D5</sub>、V<sub>D6</sub>保持相同,因此可確保差動輸入級的負載電晶體 M4、M5 的汲級電壓一致,抑制系統偏移電壓。複製增益級的全差動放大電路其負載電晶體的 間級和汲極短路,形成二極體連接(diode-connected)形式,這使得該級輸出電阻小造成增益不足,但靠著差動輸出稍稍彌補其增益的不足。

全差動放大電路的差動輸出用來驅動輸出級,輸出級是由 M15、M16、M17和 M18 四顆電晶體構成;改善輸出功率、提高開迴路增益以及驅動能力都是使用輸出級的原因。

最後說明偏壓電路。偏壓電路中設定一電流源,經由 M10 利用電流鏡 (current mirror)的方式依長寬比比值分別映射到 M7、M8 和 M9 三顆電晶體以提供運算放大器內各級電路運作。Cc為用來改善頻率響應增進相位邊限(phase margin)的米勒電容(Miller capacitor),Rc則用來調整頻率響應的右半平面零點,使右半平面零點移到左半平面與非主極點(nondominant pole)相消增進系統穩定性。

## 4.2 放大器電路修改

由上一節我們已經明白該運算放大器抑制系統輸入偏移電壓的原理,但若試圖要進一步減小其系統輸入偏移電壓那該如何著手?

1896

圖 4-5 低偏移電壓放大器略圖

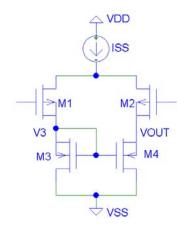

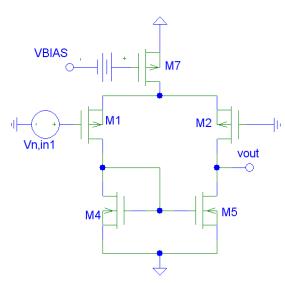

### 4.2.1 改善後之電路

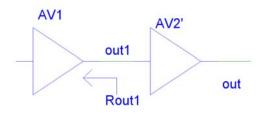

圖 4-5 為原始電路的簡略示意圖, 差動輸入級和複製偏壓電路中間的放大器代表全差動放大電路和輸出級, 複製偏壓電路中的 M3、M6 和 M1、M4 完全對稱, 故在偏壓電流相同情況下,  $V_{D4}$  必然等於  $V_{D6}$ 。而  $V_{D6}$  和  $V_{D5}$  分別就像是運算放大器的兩個輸入。就一個理想的運算放大器(圖 4-6)而言,增益為無窮大且兩輸入電壓大小相同,因此藉由增大第二級(包含全差動放大電路和輸出級)增益,放大器增益越大兩端電壓越接近。

圖 4-6 一般運算放大器

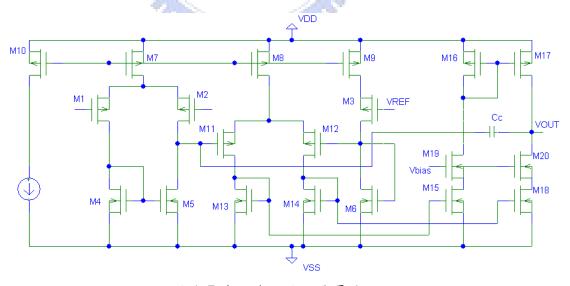

故修改電路如圖 4-7,在輸出級內加上兩個由外接偏壓控制的電晶體,藉以增加輸出級的輸出組抗進而達到增大第二級增益的目的,亦可藉由調整外接偏壓調整輸出級增益增益。由於積分器的外部電路還有電容和電阻的存在,電容和電阻可以當作用來穩定系統的負迴授路徑,因此省略 Rc。

圖 4-7 修改後低偏移電壓放大器

圖 4-4 的原始放大器其系統輸入偏移電壓為  $6.72\times10^{-4}$ volt, 而圖 4-7 修改 後的放大器系統輸入偏移電壓則為  $5.65\times10^{-4}$ volt。

#### 4.2.2 放大器電路輸出入組抗、增益

原始電路和修改後的電路最大的不同是輸出級多加上了兩個由外接偏壓控制的電晶體 M19、M20,修改過後的電路我們依然可以概略分為兩級:第一級仍然為差動輸入級,第二級是全差動放大級和修改過後的輸出級。

先就第一級的各個參數作探討。差動輸入由 M1、M2 的閘級輸入,故輸入組抗為無窮大,而輸出組抗 Routi=ro2//ro5,而第一級增益

$$|A_{V1}| = g_{m1,2} (r_{o2} // r_{o5}) \tag{4.11}$$

而第二級因為包含全差動放大電路和修改後的輸出級,故需要分別探 討。全差動放大電路其輸入組抗亦為無窮大,輸出組抗為

$$R_{out2} = r_{o11,12} // \frac{1}{g_{m13,14}} \simeq \frac{1}{g_{m13,14}}$$

(4.12)

因為差動輸出,故其增益為

$$A_{V2} = -\frac{g_{m11,12}}{g_{m13,14}} \tag{4.13}$$

修改後的輸出級其輸出組抗為

$$R_{out3} = r_{o17} // g_{m20} r_{o20} r_{o18}$$

(4.14)

故增益為

$$A_{V3} = g_{m18} \left( g_{m20} r_{o20} r_{o18} // r_{o17} \right) \tag{4.15}$$

整個第二級的增益為全差動放大電路增益與輸出級增益相乘

$$A_{V2}' = A_{V2} \cdot A_{V3} = -\frac{g_{m11,12}}{g_{m13,14}} \cdot g_{m18} \left( g_{m20} r_{o20} r_{o18} // r_{o17} \right)$$

(4.16)

而整體電路電路增益就是第一級和第二級增益相乘

$$A_{V} = A_{V1} \cdot A_{V2}^{'} \tag{4.17}$$

#### 4.2.3 放大器電路頻率響應

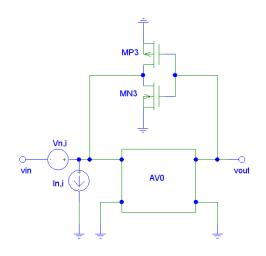

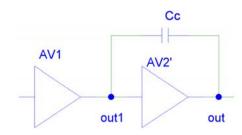

圖 4-8 兩級放大器示意圖

圖 4-9 加上 CC 之兩級放大器示意圖

有無頻率補償電容的示意電路圖分別如圖 4-8、圖 4-9 所示。頻率響應部份分別就有無加上頻率補償電容 Cc 的情況作說明。在沒加上頻率補償電容的情況下,若輸出端亦無負載電容則頻率響應的主極點位置位於第一級輸出端;若輸出端加上負載電容,則主極點位於整個電路的輸出端。

接著考慮輸出端無負載電容、有頻率補償電容 Cc 的情形。加上頻率補償電容後由於米勒效應(Miller effect)的影響,使得第一級輸出端的極點位置由  $\omega_{\rm pl}$  移到  $\omega_{\rm pl}$  , $\omega_{\rm pl}$  和  $\omega_{\rm pl}$  分別為

$$\omega_{p1} = \frac{1}{R_{out1}C_{out1}} = \frac{1}{(r_{o2}//r_{o5}) \cdot C_{out1}}$$

(4.18)

$$\omega_{p1'} = \frac{1}{R_{out1} \left[ C_{out1} + (1 - A_{V2}) C_C \right]}$$

(4.19)

把(4.16)帶入(4.19)那麼(4.19)可以改寫為

$$\omega_{p1'} = \frac{1}{\left(r_{o2} // r_{o5}\right) \cdot \left[C_{out1} + \left(1 + \frac{g_{m11,12}}{g_{m13,14}} \cdot g_{m18} \left(g_{m20} r_{o20} r_{o18} // r_{o17}\right)\right) C_C\right]}$$

(4.20)

比較(4.18)和(4.20)即可發現在頻率補償電容 Cc加入後,系統主極點位置移 往較低頻的頻率,而藉由控制 Cc的大小即可提高相位邊限、改善穩定度。

單位增益頻率(unit gain frequency)為 3db 頻率(約略等於主極點頻率)和 直流增益(dc gain)的乘積,

$$\omega_t = \omega_{p1} \cdot A_V \tag{4.21}$$

故帶入(4.17)和(4.20)可得

$$\omega_{t} = \omega_{p1} \cdot A_{V} =$$

$$\frac{1}{\left(r_{o2} // r_{o5}\right) \cdot \left[C_{out1} + \left(1 + \frac{g_{m11,12}}{g_{m13,14}} \cdot g_{m18} \left(g_{m20} r_{o20} r_{o18} // r_{o17}\right)\right) C_{C}\right]} \cdot \left[g_{m1,2} \left(r_{o2} // r_{o5}\right) \frac{g_{m11,12}}{g_{m13,14}} g_{m18} \left(g_{m20} r_{o20} r_{o18} // r_{o17}\right)\right]$$

$$(4.22)$$

(4.22)中 Coutl 遠小於 Cc和(1-Av2')的乘積,所以 Coutl 可以被忽略,(4.22)可 簡化為

$$\omega_t \simeq \frac{g_{m1}}{C_C} \tag{4.23}$$

意即單位增益頻率約等於 MI 的轉導除以頻率補償電容。

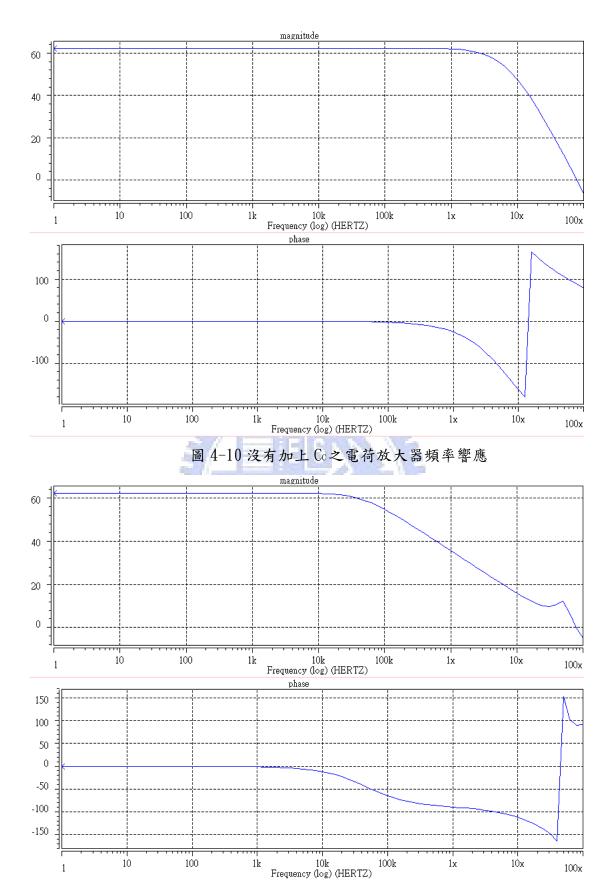

圖 4-10、4.11 分別為沒有頻率補償電容和有頻率補償電容的頻率響應圖形,觀察兩圖比較可發現加上頻率補償電容後主級點位置大幅往原點靠近;但即使如此圖 4-11 的相位圖中對應單位增益頻率的角度仍然小於-180°,表示電路不穩定。但即使電路不穩定,在第五章會介紹依然可以利用閉迴路系統的負迴授效應,使其迴路增益(loop gain)為穩定。

圖 4-11 加上 Cc 電荷放大器頻率響應

表 4.1 分別列出其各項規格。

表 4.1 電荷放大器參數模擬結果

| 參數                            | 模擬結果                       |  |

|-------------------------------|----------------------------|--|

| $(V_{DD}=2.5v, V_{SS}=-2.5v)$ |                            |  |

| 直流增益                          | 62. 3dB                    |  |

| 3dB 頻率(@Cc=1pF)               | 46. 6kHz                   |  |

| 單位增益頻率                        | 79.3megHz                  |  |

| 輸入偏移電壓                        | 5.65×10 <sup>-4</sup> volt |  |

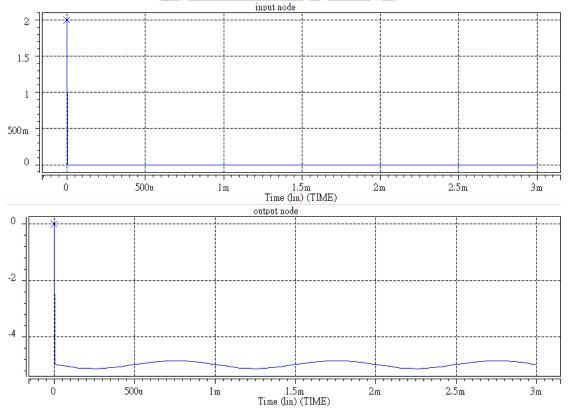

# 4.3 閉迴路系統

在設計完電荷感測的運算放大器內部電路、電路各參數探討完之後,再 回頭探討整個閉迴路系統輸入與輸出的關係。放大器的輸入信號來自於微定位器 的電容變化,由於電容變化量只有數十  $femto(10^{-14} \, \chi \, f)$ ,輸入信號為很小的值, 因此即使經過運算放大器的放大後輸出端的信號可能也沒有大到不足以觀察,因 此有必要的話需要在輸出端後面再串上一個放大級電路。

CHILD SE

#### 4.3.1 輸出信號與輸入信號

如圖 4-12 所示,信號由  $V_{inverting}$ 輸入,由  $V_{out}$ 輸出。首先假設微定位器擺動頻率為  $\omega_{III}$ ,電壓測試信號 $\pm V_{S}$ 為固定的直流電壓,雖然 $\pm V_{S}$ 為固定的直流電壓,但由於電容  $C_{S1,S2}$  因微定位器擺動產生了電荷變化  $Q_{I}$ 、 $Q_{2}$ , $C_{0}$  是微定位器沒有位移時的電容大小, $\Delta C$  是電容的最大變化量,而電容  $C_{S1,S2}$  的不匹配造成淨電荷  $Q_{0}$ 。電容  $C_{S1,S2}$ 、電荷  $Q_{I}$ 、 $Q_{2}$ 以及淨電荷  $Q_{I}$  分別表示如下

圖 4-12 電荷感測系統

$$C_{S1,2} = C_0 \pm \frac{\Delta C}{2} \sin \omega_m t \tag{4.24}$$

$$Q_{1} = \left(C_{0} + \frac{\Delta C}{2}\sin\omega_{m}t\right)\left(V_{S} - v_{inv}\right)$$

$$Q_{2} = \left(C_{0} - \frac{\Delta C}{2}\sin\omega_{m}t\right)\left(-V_{S} - v_{inv}\right)$$

$$Q = Q_{1} + Q_{2} = 2\left(\frac{1}{2}V_{S}\Delta C\sin\omega_{m}t - C_{0}v_{inv}\right)$$

$$(4.25)$$

電流為電荷的微分,因此將淨電荷對時間微分可得到電流關係式:

$$i = \frac{dQ}{dt} = 2\left(\frac{1}{2}V_S\Delta C\omega_m\cos\omega_m t - c_0\frac{dv_{inv}}{dt}\right)$$

(4.26)

對開迴路的放大器來說,

$$A_{V}(v_{inv} - 0) = v_{out}$$

$$v_{inv} = -\frac{v_{out}}{A_{V}}$$

(4.27)

依照科西和夫定律在單一節點上總流入電流加上總流出電流為零,所以對整個系統可寫出下列關係式:

$$i - \frac{v_{inv} - v_{out}}{R_I} - C_I \frac{d\left(v_{inv} - v_{out}\right)}{dt} = 0$$

$$(4.28)$$

結合(4.26)、(4.27)、(4.28)可得到輸出的一階微分方程式

$$C_I \frac{dv_{out}}{dt} + \frac{1}{R_I} v_{out} = -2\Delta C V_S \omega_m \cos \omega_m t$$

(4.28)

(4.28)是非齊次微分方程式,所以假設輸出信號  $v_{\text{out}}(t)$ 是正弦函數項和餘弦 含數項分別乘上常數的重疊(superposition),即  $v_{out}(t) = A\cos\omega_m t + B\sin\omega_m t$ (4.29)

把(4.29)帶入(4.28)可解得常數項 A、B,

$$A = \frac{-2\Delta C V_S \omega_m R_I}{1 + R_I^2 C_I^2 \omega_m^2}, B = R_I C_I \omega_m \cdot \frac{-2\Delta C V_S \omega_m R_I}{1 + R_I^2 C_I^2 \omega_m^2}$$

(4.30)

把(4.30)帶回(4.29)得到輸出信號

$$v_{out}(t) = \frac{-2\Delta C V_S \omega_m R_I}{1 + R_I^2 C_I^2 \omega_m^2} \left(\cos \omega_m t + R_I C_I \omega_m \cdot \sin \omega_m t\right)$$

(4.31)

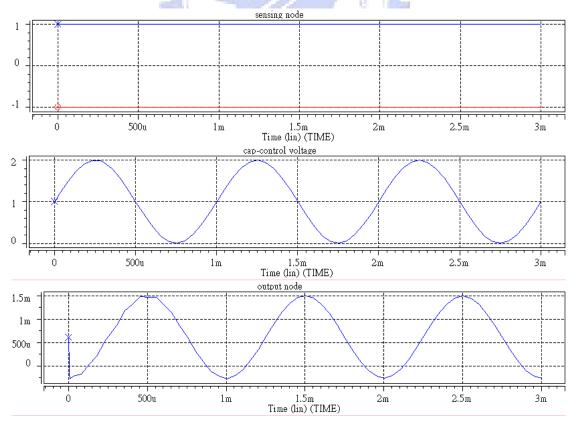

(4.31)是在測試電壓信號±VS 為固定直流電壓的情況下所推得,圖 4-13 分別是 其測試電壓信號、電容控制電壓和輸出節點的電壓變化曲線。

圖 4-13 電荷感測系統各節點電壓曲線(1)

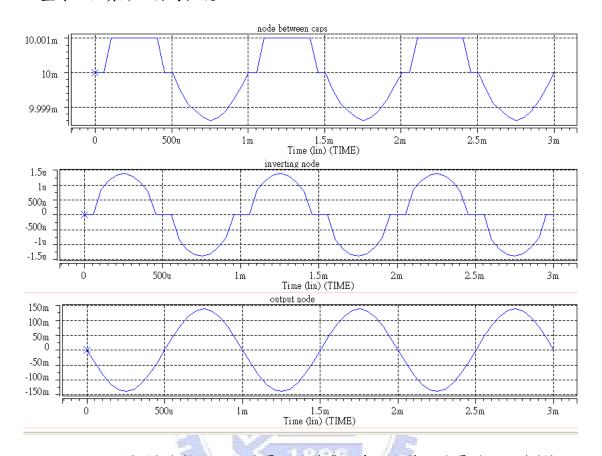

接下來考慮測試電壓信號±Vs為相位差 180 度的弦波,弦波頻率為 ωs,其他條件皆保持不變,則(4.28)的一階微分方程式改寫如下:

$$C_{I}\frac{dv_{out}}{dt} + \frac{1}{R_{I}}v_{out} = V_{S}\Delta C\Big[(\omega_{s} - \omega_{m})\sin(\omega_{s} - \omega_{m})t - (\omega_{s} + \omega_{m})\sin(\omega_{s} + \omega_{m})t\Big]$$

(4.32)

在解(4.32)依然使用重疊原理,但是在非齊次項有  $\sin(\omega_s-\omega_m)$ 和  $\sin(\omega_s+\omega_m)$ 兩個不同項,所以必須使用兩次重疊原理,

$$v_{out}(t) = v_{out1}(t) + v_{out2}(t)$$

$$v_{out1}(t) = A\cos(\omega_s - \omega_m)t + B\sin(\omega_s - \omega_m)t$$

$$v_{out2}(t) = p\cos(\omega_s + \omega_m)t + q\sin(\omega_s + \omega_m)t$$

(4.33)

$$\begin{cases}

A = -R_I \left(\omega_s - \omega_m\right) C_I \cdot \frac{V_S \Delta C \left(\omega_s - \omega_m\right) \cdot R_I}{\left(\omega_s - \omega_m\right)^2 C_I^2 R_I^2 + 1}, B = \frac{V_S \Delta C \left(\omega_s - \omega_m\right) \cdot R_I}{\left(\omega_s - \omega_m\right)^2 C_I^2 R_I^2 + 1} \\

p = R_I \left(\omega_s + \omega_m\right) C_I \cdot \frac{V_S \Delta C \left(\omega_s + \omega_m\right) \cdot R_I}{\left(\omega_s + \omega_m\right)^2 C_I^2 R_I^2 + 1}, q = -\frac{V_S \Delta C \left(\omega_s + \omega_m\right) \cdot R_I}{\left(\omega_s + \omega_m\right)^2 C_I^2 R_I^2 + 1}

\end{cases} (4.34)$$

把(4.34)的各常數項帶回(4.33)可以得到測試電壓信號為弦波時的輸出信號表示式。圖 4-14 分別是電壓測試信號、電容控制電壓和輸出節點的電壓變化曲線。

圖 4-14 電荷感測系統各節點電壓曲線(2)

## 4.3.2 放大級電路設計

#### 1996

在放大級電路,需要優先考慮的是放大增益大小以及輸出擺幅(output swing),在此需要將第一級輸出信號放大至  $10^3$ 次方伏特左右,故放大倍率要在 100 倍以上,輸出擺幅則以不切掉(cut off)輸出信號為原則即可。

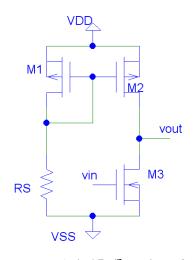

圖 4-15 單級放大電路

首先放大級電路設計以簡單的共源級組態(common source stage)實

現,如圖 4-15 所示。整體電路的第一級輸出由電晶體 M3 的閘級輸入,經過共源 極組態放大由 M3 的汲極輸出,其中 M2 為 M3 的負載電晶體,偏壓電流經由 M1 依 M1、M2 的長寬比比值映射到 M2, 而電阻 Rs作為定義電流大小的電流源。共源級 放大器增益為

$$A_{V} = -g_{m2} (r_{o2} // r_{o3}) \tag{4.35}$$

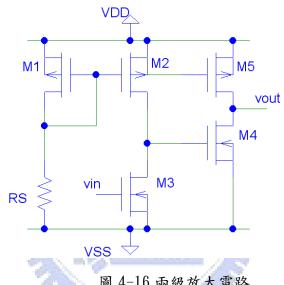

但共源級放大為單級放大,難以達到所要求規格超過100倍的增益。因此在圖 4-15 的輸出後面再串上一級,放大級電路如圖 4-16 所示。

圖 4-16 兩級放大電路

M4 亦為共源級組態, M5 是 M4 的負載, M4、M5 架構與 M2、M3 雷同。M3 的汲 極與 M4 的閘級相接,因此整體增益就等於兩個共源級組態增益相乘,

$$A_{V} = g_{m2}g_{m4} (r_{o2} // r_{o3}) (r_{o4} // r_{o5})$$

$$(4.36)$$

即可輕易達到增益超過100倍以上的要求。表4.2為放大級電路各電晶體長 寬比。

| transistor | aspect ratio | transistor | aspect ratio |

|------------|--------------|------------|--------------|

| M1 · M2    | 10/1         | M4         | 1.6/1        |

| M3         | 3/1          | M5         | 5/1          |

表 4.2 放大級電路各電晶體長寬比

# 第五章 解析度與雜訊

在第上一章中詳述了用來感測電荷的運算放大器電路各項規格、閉迴路系統輸出輸入信號間的關係以及後續的放大級電路,接著在本章中要討論電荷感測電路的雜訊及微定位器最小可偵測到位移(即解析度)的關係。

本論文中希望能藉由抑制雜訊使得微定位器的位移在只有數十個奈米等級 的微小量情況下還能測得輸出信號,因此在本章中亦會推導第四章所設計的放大 器電路的等效雜訊,以期能在設計電路之初便能概略估算雜訊大小,並藉由改變 放大器電路內各電晶體的長寬比以抑制雜訊大小。

# 5.1 最小位移

圖 5-1 電荷感測系統

噪訊比(signal to noise ratio)定義為輸出雜訊和信號的比值。考慮 5-1 的電荷感測系統,其雜訊來自於運算放大器內部電路和負迴授電阻 RI,在 輸出節點處同時存在輸出信號與輸出雜訊。當輸出雜訊過大甚至大於輸出信號時,信號就被雜訊給蓋掉,因此最小可量得信號的情況就是噪訊比等於一,亦即輸出信號等於輸出雜訊,此時輸出雜訊為最大可容忍雜訊,用數學式可以表示為

$$v_o / \sqrt{v_{n,out}^2} = 1 \tag{5.1}$$

回顧第二章,輸出信號可用電容不匹配量  $\Delta C_s$ 、積分電容  $C_I$  和測試電壓信號  $V_s$  表示,重寫如下

$$v_o = \frac{\Delta C}{C_I} V_S \tag{5.2}$$

整體系統的輸出的雜訊取決於放大器和設定反相端輸入節點偏壓的電阻 R<sub>1</sub>,輸出節點的雜訊可寫作

$$\frac{\overline{v_{on}^2}}{\Delta f} = \left(\frac{2C_S + C_I + C_P + C_{IP}}{C_I}\right)^2 \cdot \frac{\overline{v_n^2}}{\Delta f} + \left|\frac{1}{j\omega C_I}\right|^2 \cdot \frac{4kT}{R_I}$$

(5.3)

在這邊  $v_n^2/\Delta f$  是放大器熱雜訊的輸入頻譜密度(input-referred spectral density),單位是  $V^2/Hz$ , $C_{IP}$ 是放大器的輸入電容。合併(5.1)、(5.2),則電容不匹配量可以輸出雜訊表示

$$\sqrt{v_{n,out}^2} = v_o = \frac{\Delta C}{C_I} V_S$$

$$\Rightarrow \Delta C = \frac{\sqrt{v_{n,out}^2}}{V_S} C_I$$

(5.3)

再回顧第二章橫向梳狀結構兩個感應電容變化與電容不匹配的關係式分別 重寫如下

$$C_{S1,2} = C_0 \pm \frac{\Delta C}{2} \tag{5.4}$$

$$\Delta C = C_{S1} - C_{S2} = \frac{2\varepsilon NtL}{x_0} \left[ \left( \frac{\Delta x}{x_0} \right) + \left( \frac{\Delta x}{x_0} \right)^3 + \left( \frac{\Delta x}{x_0} \right)^5 + \dots \right]$$

(5.5)

(5.5)中的高次項可被忽略,故結合(5.3)、(5.5)可求出在噪訊比等於一情况下之解析度,也就是可量測得到的最小位移量  $\Delta x$ 。

## 5.2 等效輸出輸入雜訊推導

把第四章的電荷放大器電路再重複為圖 5-2,由於是多級組態的電路,所以在做雜訊推導時必須一級一級拆開疊加上去;以下分別就差動輸入級、全差動放大級和輸出級分別推算其個別雜訊,然後再把各級雜訊加總以得到等效輸出雜訊。此部分的雜訊推導亦只考慮熱雜訊而忽略閃爍雜訊。

### 5.2.1 差動輸入級雜訊

1896

圖 5-3 是差動輸入級每個電晶體的雜訊都以電壓源形式串接於閘級的 圖形,而電流源 M7 所貢獻的雜訊可以被忽略。為了方便起見假設其輸出接地, 每顆電晶體雜訊電壓乘上各自的轉導相加即為總輸出電流雜訊(註[13]),

$$I_{tot}^{2} = g_{m1}^{2} v_{n1}^{2} + g_{m2}^{2} v_{n2}^{2} + g_{m4}^{2} v_{n4}^{2} + g_{m5}^{2} v_{n5}^{2}$$

(5.5)

圖 5-3 差動輸入級雜訊模型

等效輸出電流可用等效輸入雜訊表示,故可寫為

$$\bar{I}_{tot}^{2} = g_{m1}^{2} v_{n,eq}^{2} = g_{m1}^{2} v_{n,in1}^{2}$$

比較(5.5)和(5.6)得到

$$\overline{v_{n,in1}^{2}} = \overline{v_{n1}^{2}} + \overline{v_{n2}^{2}} + \left(\frac{g_{m4}}{g_{m1}}\right)^{2} \left(\overline{v_{n4}^{2}} + \overline{v_{n5}^{2}}\right) \\

= 2\overline{v_{n1}^{2}} + 2\frac{g_{m4}^{2}}{g_{m1}^{2}} \overline{v_{n4}^{2}} \\

(5.7)$$

在此假設 M1、M2 以及 M4、M5 皆完全對稱。等效的輸入雜訊模型如圖 5-4 所示,每顆電晶體雜訊皆被提到輸入端,M1、M2、M4、M5 和 M7 構成無雜訊(noise free)電路。

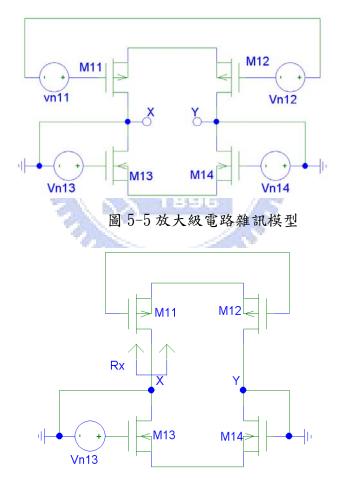

## 5.2.2 全差動放大級

圖 5-5 是全差動放大級每個電晶體的雜訊以電壓源形式串接於閘級的圖形。同前面所述,電流源 M8 所貢獻的雜訊可以被忽略。M11、M12 兩顆電晶體的雜訊仍然可以電壓源串接於閘級的方式來等效,但不同於差動輸入級的單端輸出,全差動放大級為差動輸出,M13、M14 都是閘級和汲級之間短路的二極體連接(diode connected)形式,因此無法使用同上一小節的推導方法來計算 M13、M14 貢獻到輸出的雜訊,需要另覓方法來推導。

圖 5-6 電晶體 M13 所貢獻的輸出雜訊圖形

M13、M14為對稱故我們只需要考慮 M13 貢獻到輸出的雜訊再乘兩倍即可。 如圖 5-6 所示(註[14]),設兩輸出節點分別為 X、Y,而從 X 節點往上看的組抗 Rx 為

$$R_X = 2r_{o11} + \frac{1}{g_{o14}} \tag{5.8}$$

從節點 X 往下看的組抗是  $1/g_{m13}=1/g_{m14}$ ,所以流經 M11、M12 和 M14 的雜訊電流  $I_{mY}$  可表示為

$$I_{nY} = g_{m13} v_{n13} \frac{\frac{1}{g_{m14}}}{2r_{o11} + \frac{2}{g_{m14}}}$$

(5.9)

故雜訊電流Iny在節點Y產生的電壓雜訊可寫作

$$v_{nY} = g_{m13}v_{n13} \frac{\frac{1}{g_{m14}}}{2r_{o11} + \frac{2}{g_{m14}}} \cdot \frac{1}{g_{m14}}$$

(5.10)

因為 M13 閘級汲級短路的緣故,節點 X 的雜訊電壓就等於 M13 的雜訊電壓,

$$v_{nX} = v_{n13} (5.11)$$

所以M13對節點X、Y貢獻的輸出雜訊電壓Vnx,y可寫作

$$v_{nXY} = v_{nX} - v_{nY} = v_{n13} \left( 1 - \frac{1}{2(g_{m13}r_{o11} + 1)} \right)$$

(5.12)

M14 對節點 X、Y 所貢獻雜訊的推導方式和 M13 完全相同,所以 M13、M14 兩 顆電晶體貢獻到差動輸出節點 X、Y 的雜訊為

$$v_{n,out}^{2} \bigg|_{M13,M14} = 2v_{n13}^{2} \left[ 1 - \frac{1}{2(g_{m13}r_{o11} + 1)} \right]^{2}$$

(5.13)

因此全差動放大級的等效輸入雜訊可寫作

$$v_{n,in2}^{\overline{2}} = v_{n,11}^{\overline{2}} + v_{n,12}^{\overline{2}} + \frac{v_{n,out}^{\overline{2}}}{g_{m11}^{2} \left(r_{o11} / \frac{1}{g_{m13}}\right)^{2}}$$

(5.14)

#### 5.2.3 輸出級雜訊推導

圖 5-7 輸出級雜訊模型

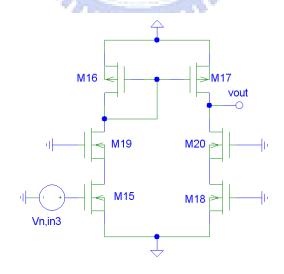

圖 5-7 是輸出級每個電晶體的雜訊都以電壓源形式串接於閘級的圖形,其等 效輸入雜訊推導方式與差動輸入級類似,故其等效輸入雜訊可表示為

$$v_{n,in3}^{2} = v_{n15}^{2} + \frac{1}{g_{m15}^{2}} \left( g_{m19}^{2} v_{n19}^{2} + g_{m16}^{2} v_{n16}^{2} + g_{m17}^{2} v_{n17}^{2} + g_{m20}^{2} v_{n20}^{2} + g_{m18}^{2} v_{n18}^{2} \right)$$

(5.15)

其中各電晶體雜訊電壓源

$$v_{nj}^2\Big|_{j=15\sim 19} = 4kT\frac{2}{3g_{mj}}$$

(5.16)

再把各電晶體的雜訊電壓提至輸入端後,M16、M17、M18、M19和 M20 構成無雜訊的電路,其等效輸入雜訊模型如圖 5-8。

圖 5-8 輸出級等效輸入雜訊與無雜訊電路

#### 5.2.4 電荷放大器總輸出雜訊

前面三小節分別推算出每一級的等效輸入雜訊,在這一小節中把前面各級的雜訊總和起來以得到總輸出雜訊。總輸出雜訊可表示如下

$$v_{n,out}^{2} = \left[ \left( A_{V1}^{2} v_{n,in1}^{2} + v_{n,in2}^{2} \right) A_{V2}^{2} + v_{n,in3}^{2} \right] \cdot A_{V3}^{2}$$

(5.17)

其單位為 V²/Hz,各級增益已在第四章詳述。

接著再回到整個閉迴路系統,若我們要微定位器的工作頻率操作在 20kHz 左右,同(3.17)方式,但在計算雜訊的時候就只需要考慮 20kHz 附近頻率的範圍。表 5.1 列出運算放大器內各電晶體的長寬比,考慮頻率從 19kHz 到 21kHz,雜訊亦只需要從 19kHz 積分至 21kHz,那麼在這段頻率範圍下若只單純考慮運算放大器,則其總輸出雜訊為 2.68mV;而整個電路輸出節點處之總輸出雜訊為 3.34mV,因此根據(5.3)、(5.5)兩式可得到最小可測得之位移約為 18 奈米,達到我們所要求的數十個奈米的解析度規格。

表 5.1 電荷放大器各電晶體長寬比

| 電品體          | 長寬比              |

|--------------|------------------|

| M1 · M2 · M3 | S1=S2=S3=200/1.5 |

| M4 \ M5 \ M6 | S4=S5=S6=16/8    |

| M7 · M8      | S7=S8=50/1.5     |

| M9 · M10     | S9=S10=25/1.5    |

| M11 \ M12    | S11=S12=20/8     |

| M13 · M14    | S13=S14=10/5     |

| M15          | S15=20/5         |

| M16 · M19    | S16=S19=20/1     |

| M17 · M20    | S17=S20=160/1    |

| M18          | S18=160/5        |

#### 5.3 迴路增益與穩定性

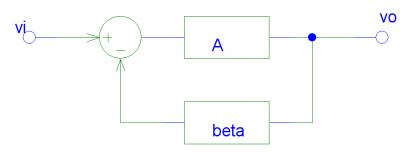

就一個加上負迴授的閉迴路系統而言,其方塊圖通常表示為圖 5-9,其中 A 為開迴路增益, B 為迴授因子(feedback factor)。

圖 5-9 負迴授系統方塊圖

整個閉迴路的轉移函數即輸出 Vo對輸入 Vi 的關係式為

$$\frac{v_o}{v_i} = \frac{A}{1 + A\beta} \tag{5.18}$$

而其中我們定義 A β 為迴路增益(loop gain),即開迴路增益乘上迴授因子的值,藉由迴路增益的波得圖(Bode plot)我們可以判斷系統穩定與否。波得圖包含大小圖(magnitude)和相位圖(phase),單位增益頻率(unit-gain bandwidth)定義為當大小圖的增益為單位增益(即 0dB)時的頻率;接著再定義相位邊限(phase margin)為相位圖中對應單位增益頻率的角度加上一百八十度。相位邊限大於零時系統為穩定;而若相位邊限小於零時系統是不穩定的。

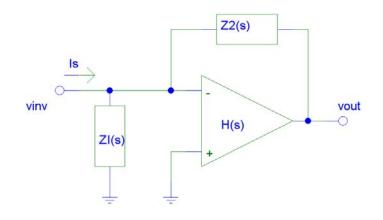

為了得到如圖 5-9 的方塊圖,我們忽略圖 5-1 左邊的測試電壓信號以及會變動的電容,寄生電容  $C_P$  視為組抗  $Z_I(s)$ ,電阻  $R_I$  和電容  $C_I$  一起視為組抗  $Z_2(s)$ ,放大器增益視為 H(s),各組抗和增益都以拉普拉斯 S 域的轉移函數 (Laplace S-domain)來表示,重書圖形為圖 5-10。

圖 5-10 S-domain 的負迴授、寄生電容和放大器增益表示圖

考慮輸出電壓 Vout 對輸入電流 is 的轉移函數,從科西和夫電流定律寫出下式

$$i_{S} - \frac{v_{inv}}{Z_{1}} - \frac{v_{inv} - v_{o}}{Z_{2}} = 0 ag{5.19}$$

再由放大器反相端和非反向端輸入對輸出的關係寫出

$$v_o = -H(s) \cdot v_{inv} \tag{5.20}$$

結合上述兩式得到 Vout 對 is 的轉移函數

$$\frac{v_o}{i_s}(s) = -\frac{1}{\frac{1}{Z_1(s)H(s)} + \frac{1}{Z_2(s)H(s)} + \frac{1}{Z_2(s)}}$$

(5.21)

$$\sharp \psi \begin{cases}

Z_1(s) = \frac{1}{C_P(s)} \\

Z_2(s) = R_I / \frac{1}{C_I s} = \frac{R_I}{1 + R_I C_I s}

\end{cases}$$

(5.22)

改寫(5.21)並與(5.18)對照可以得到開迴路增益A和迴授因子 $\beta$ 的表示式,

$$\begin{cases} A(s) = -\frac{Z_1(s)Z_2(s)H(s)}{Z_1(s) + Z_2(s)} \\ \beta(s) = -\frac{1}{Z_2(s)} \end{cases}$$

(5.23)

為了得到迴路增益的頻率響應圖形,(5.23)中的 s 用 j  $\omega$  代入,並把(5.22) 組抗  $Z_1$  、  $Z_2$  的參數代入,(5.23) 可重寫為

$$A(s)\Big|_{s=j\omega} = -\frac{R_I H(s)}{1 + R_I (C_I + C_P) s}\Big|_{s=j\omega}$$

$$= \frac{R_I |H(j\omega)|}{\sqrt{1 + R_I^2 (C_I + C_P)^2 \omega^2}} \angle \left(180^o + \angle H(j\omega) - \tan^{-1} \left[R_I (C_I + C_P) \omega\right]\right)$$

(5.24)

$$\beta(s)\Big|_{s=j\omega} = -\left(\frac{1}{R_I} + C_I s\right)\Big|_{s=j\omega}$$

$$= \sqrt{\frac{1}{R_I^2 + C_I^2 \omega^2}} \angle \left(180^o + \tan^{-1}\left(R_I C_I \omega\right)\right)$$

(5.25)

因此迴路增益的大小和相位分別可寫為

$mag = 20\log|A\beta| = 20\log|A| + 20\log|\beta|$

$$=20\log\left(\frac{R_{I}|H(j\omega)|}{\sqrt{1+R_{I}^{2}(C_{I}+C_{P})^{2}\omega^{2}}}\right)+20\log\left(\sqrt{\frac{1}{R_{I}^{2}+C_{I}^{2}\omega^{2}}}\right)$$

(5.26)

$$phase = \angle A\beta = \angle A + \angle \beta$$

$$= (180^{\circ} + \angle H(j\omega) - \tan^{-1}[R_I(C_I + C_P)\omega]) + (180^{\circ} + \tan^{-1}(R_IC_I\omega))$$

$$= 360^{\circ} + \angle H(j\omega) + \tan^{-1}(R_IC_I\omega) - \tan^{-1}[R_I(C_I + C_P)\omega]$$

(5.27)

開迴路 A、迴授因素  $\beta$  和迴路增益  $A\beta$  的大小圖以及相位圖分別如圖 5-11 和圖 5-12 所示。

圖 5-12 A、 $\beta$  和 A  $\beta$  的相位圖

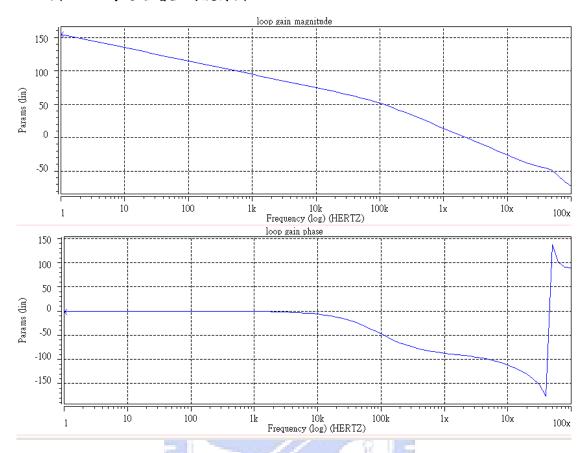

### 圖 5-13 為迴路增益的波得圖。

圖 5-13 迴路增益 Aβ 的頻率響應圖形

觀察圖 5-13,由大小圖的單位增益頻率對應到相位圖的角度可得知相 位邊限大於零,故系統穩定。再由圖 5-13 對照圖 4-11 可以發現,即使放大器本 身不穩定,但依然可藉由閉迴路的負迴授效應使得系統呈現穩定狀態。

# 第六章 結論

# 6.1 結果與討論

本論文首先在第二章裡面說明了微定位器的工作原理和其分類,並說明選擇橫向梳狀結構的原因。接著在第三章提到能夠感測電流的放大器電路,其優點為輸出信號是微定位器移動速度的函數;但是受限於單端輸入,使得其輸入端位準飄移,造成輸入放大器的電流大小無法完全正比於微定位器移動的速度而產生誤差。為了抑制輸入位準飄移的現象故在第四章中選擇差動輸入的運算放大器,但選擇差動輸入的同時也必須考慮輸入偏移電壓的影響,故設計上選擇了低輸入偏移電壓的電路。第五章則是第四章內容的延伸,建構於第四章的放大器之上,其微定位器可量得的最小位移量可從輸出信號以及等效輸出雜訊來推得。表6.1列出電流感測、電荷感測放大器特性的比較。

表 6.1 電流感測和電荷感測的比較

|         | 電流感測 11.111         | 電荷感測          |

|---------|---------------------|---------------|

| 測得微定位器之 | 速度                  | 位移            |

| 参數      | THE PERSON NAMED IN | (a)           |

| 誤差肇因    | 放大器為單端輸入使得電         | 製程缺陷等因素造成的輸入偏 |

|         | 流不正比微定位器變化速         | 移電壓、增益不為無窮大。  |

|         | 度。                  |               |

| 放大器雜訊   | 較小                  | 較大            |

| 最小偵測    | 2.658m/s            | 18 nm         |

| 位移/速度   |                     |               |

## 6.2 未來展望

在本論文的最後對於後續研究有幾項提議,第一個是在論文中有幾處設計的電路內包含電阻的部分,由於實體電阻在晶片裡面佔很大的面積,因此若真的使用實體電阻佈局會很不經濟,這部分可以用固定時脈的開關和電容(switch-capacitor)來代替實體電阻。在分別完成電流感測、電荷感測電路後,配合思源科技的 LAKER 這套佈局工具軟體畫出整個佈局電路,最後再委託國家晶片系統設計中心(CIC)代為製作。第二個是如果為了要能夠同時得到速度和位移資訊,就需要另外找出方法以徹底整合電流和電荷這兩種感測方式的電路,使整合後的電路能同時得到速度和位移資訊,定位微定位器,最後再委託國家晶片系統設計中心代為製作使之完成。

# 參考文獻

- [1] 楊龍杰,"認識微機電",滄海出版社,民國 90 年。

- [2] B. Minhang, W. Weiyuan, "Future of microelectromechanical systems(MEMS)", "Sensors and Actuators", A56, pp.135-141, 1996.

- [3] Naiyavudhi Wongkomet "Position sensing for electrostatic micropositioners" pp.1, 1998.

- [4] Naiyavudhi Wongkomet "Position sensing for electrostatic micropositioners" pp.6-13, 1998.

- [5] Ping-Hsing Lu, *Student Member*, *IEEE*, Chung-Yu Wu, *Member*, *IEEE*, and Ming-Kai *Tsai* "Design Techniques for Tunable Transresistance-C VHF Bandpass Filters" 1994.

- [6] Jung-Tang Huang, "Realization of Trans-impedance Amplifier for Particle Counting Chip" Institute of Mechatronic Engineering National Taipei University of Technology Taiwan.

- [7] Behzad Razavi, "Design of Analog CMOS Integrated Circuit" pp.207-220, 1999

- [8] 作者 Behzad Razavi, 譯者李峻員, 審閱劉深淵, "類比 CMOS 積體電路設計", pp.218-232, 2002.

- [9] Paul R. Gray, Paul J. Hurst, Stephen H. Lewis, Robert G. Meyer "Analysis and Design of Analog Integrated Circuits" pp776-798, 2001.

- [10] "Star-Hspice Manual", pp4-4, 1999.

- [11] M. Ismail and T. Fiez, "Analog VLSI Signal and Information Processing", McGraw Hill, Chapter 3, 1994.

- [12] P.K. Chan, L. Siek, H.C. Tay, J.H. Su, "A LOW-OFFSET CLASS-AB CMOS OPERATIONAL AMPILFIER" Naynyang Technological University.

- [13] Phillip E. Allen, Douglas R. Holberg, "CMOS Analog Circuit Design", pp193-194, 2002.

- [14] Behzad Razavi, "Design of Analog CMOS Integrated Circuit" pp.225-227, 1999