# 國立交通大學

## 光電工程系 顯示科技研究所

## 碩士論文

溶膠凝膠法沉積鋯摻雜氧化鋅薄膜電晶體之研究

Study on fundamental properties of ZrZnO-based TFT by Sol-Gel process

研究生:蕭秀娟 Shiou-Jiuan Shiau

指導教授:劉柏村 Dr. Po-Tsun Liu

中華民國九十六年六月

# 溶膠凝膠法沉積鋯摻雜氧化鋅薄膜電晶體之研究 Study on fundamental properties of ZrZnO-based TFT by Sol-Gel process

研究生:蕭秀娟 Student: Shiou-Jiuan Shiau

指導教授:劉柏村 Advisor: Po-Tsun Liu

國立交通大學 光電工程系 顯示科技所

Submitted to Department of Photonics & Display Institute

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master

in

**Photonics**

June 2007

S.J Shiau, Taiwan, Republic of China

中華民國九十六年六月

#### 溶膠凝膠法沉積鋯摻雜氧化鋅薄膜電晶體之研究

學生: 蕭秀娟 指導教授: 劉柏村

國立交通大學光電工程系 顯示科技所

#### 摘 要

半導體氧化鋅(ZnO)的能隙(~3.37eV)處於不易吸收可見光的能量範圍,且擁有較高的載子遷移率,將此透明半導體層應用於液晶顯示器時,將可降低薄膜電晶體對可見光的敏感性,以及增加顯示畫素的開口率。

本論文中之薄膜電晶體則是使用溶膠凝膠(sol-gel)的方式來製造,此方式是利用一種旋塗沉積的技術(spin-on-deposition)來形成鋯摻雜氧化鋅(ZrZnO)薄膜,並且可以在常壓常溫下形成鋯摻雜氧化鋅(ZrZnO)薄膜,而旋塗沉積的技術可以節省很多製程上面的成本以及時間。

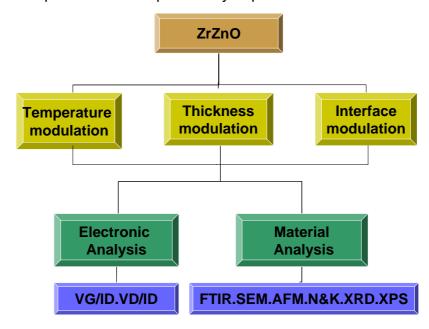

錯摻雜氧化鋅(ZrZnO)薄膜在旋塗沉積之後,我們使用退火方式來改善錯摻雜氧化鋅(ZrZnO)薄膜電晶體的特性,並且利用改變退火溫度、薄膜厚度的方式來找出最好條件。首先,我們使用不同的烘烤(Baking)方式來去除水氣和改善薄膜的均勻性,並且找出去除有機鍵的溫度。此外,我們使用雙層介電層的方式來改善介面特性,因而使得錯摻雜氧化鋅(ZrZnO)元件更能夠擁有半導體的特性。

最後,我們使用 SEM、AFM、N&K、FTIR、XRD、XPS 來分析溶膠凝膠沉積法之鋯摻雜氧化鋅(ZrZnO)薄膜的材料特性,並使用 I-V 量測裝置(4156)來探討鋯摻雜氧化鋅(ZrZnO)薄膜電晶體的電性趨勢。

Study on fundamental properties of ZrZnO-based

**TFT by Sol-Gel process**

Student: Shiou-Jiuan Shiau

Advisors: Dr.Po-Tsun Liu

Department of Photonics and Display Institute

National Chiao Tung University

ABSTRACT

ZnO (Zinc-oxide) is a wide bandgap (Eg~3.37ev) semiconductor material, it is

transparent in the visible region of the spectra and therefore, also less light sensitive. ZnO

based - TFT can increase the field mobility, improve the opening of AMLCD pixel and the

problem of photo-excited leakage current.

ZrZnO based - TFT was fabricated by sol-gel . Sol-Gel is a spin-on-deposition

technology. We can use this way to form ZrZnO thin film in the room temperature (RT) and

room pressure (RP) environment.

After spin-costing deposition, we improve the ZrZnO based -TFT character by the

method of different annealing temperature and different film thickness. Then, in order to

improve the channel / dielectric interface, we describe the introduction of a HfOx capping

layer onto the SiNx films to get a good ZrZnO baced -TFT devices.

Finally, the material analysis of ZrZnO film is discussed by SEM \ AFM \ N&K \

FTIR · XRD and XPS .The electrical characteristic was measured by the I-V measurement

system.

ii

首先感謝我的指導教授\_劉柏村老師,感謝老師悉心的教導並指引我正確的方向,使得我在碩士的生涯中獲益良多。另外,還要感謝中山物理系\_ 張鼎張教授,在學術研究上能給我最詳盡的指導,讓我的研究可以更為順利。

此外,還要感謝敏全、震鑠、泓緯、志宗、興華、皓彥、一德學長不厭其煩的指出,我研究中的缺失並給予我莫大的協助與建議,也感謝亞諭、柏宇、啟銘、崇維、唐豪、建名、又菁、宛芳同學的幫忙,以及學弟們誼明、逸侑、思維、尚祐、威廷、逸立、豫杰、繼聖、立煒、超駿、巍方,在碩士學習的日子中,有你們的陪伴,使得實驗室充滿了歡樂。在此,還要感謝的是已經畢業的黃千睿學長,不時地為我提供意見解決困難,使得本論文能夠更加完整而嚴謹地呈現。

最後,謹以此文獻給我最親愛的父母親\_蕭炎明先生、劉翠霞女士以及 我的弟弟妹妹\_蕭秀芬小姐、蕭建韋先生,感謝你們默默的支持與關懷著 我,並陪伴我共同地走過這一段甘苦的日子,還要特別感謝一直在我身邊 的摯友\_何彥勳先生,因為有你的支持與鼓勵,使得我能夠順利地得到碩士 學位,在此由衷地對你說聲謝謝。

蕭秀娟 2007 年 6 月

## **Contents**

| ABSTRACT(CHINESE)                           |

|---------------------------------------------|

| ABSTRACT(ENGLISH)                           |

| ACKNOWLEDGEMENTSIII                         |

| <u>CONTENTS</u> IV                          |

| TABLE CAPTIONSVI                            |

| FIGURE CAPTIONSVIII                         |

| CHAPTER 1. INTRODUCTION1                    |

| 1-1 General Background1                     |

| 1-2 Motivation2                             |

| CHAPTER 2. EXPERIMENTAL PROCEDURES5         |

| 2-1 TFT Fabrication5                        |

| 2-2 Experimental Procedures6                |

| 2-2-1 spin-coating deposition7              |

| 2-2-2 Changing Baking Temperature7          |

| 2-2-3 Patterning8                           |

| 2-2-4 Changing Annealing Temperature8       |

| 2-2-5 Changing Film Thickness10             |

| 2-2-6 Changing interface contact layer11    |

| CHAPTER 3 RESULTS AND DISCUSSIONS13         |

| 3-1 ZrZnO Film Analisys13                   |

| 3-1-1 The FTIR Measurement of ZrZnO Films13 |

| 3-1-2 The SEM Measurement of ZrZnO Films14  |

| 3-1-3 The AFM Measurement of ZrZnO Films16  |

| 3-1-4 The XRD Measurement of ZrZnO Films          | 17 |

|---------------------------------------------------|----|

| 3-1-5 The XPS Measurement of ZrZnO Films          | 18 |

| 3-2 The Electrical Characteristics of ZrZnO based |    |

| TFTs                                              | 19 |

| 3-2-1 Baking with various temperature             | 19 |

| 3-2-2 Annealing with various temperature          | 20 |

| 3-2-3 Spin-coating with various film thickness    | 21 |

| 3-2-4 Interface contact layer with various        |    |

| dielectric                                        | 23 |

| CHAPTER 4 CONCLUSION                              | 25 |

| References                                        | 27 |

| Vita B96                                          | 50 |

## **Table captions**

#### Chapter1

**Table 1** shows experimental flow path in my experiment.

## Chapter2

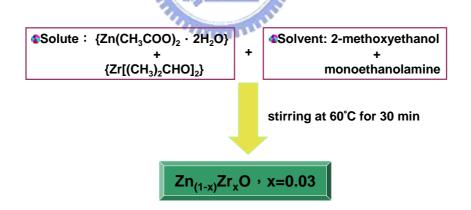

**Table 2** shows experimental flow chart of sol-gel precursor preparation.

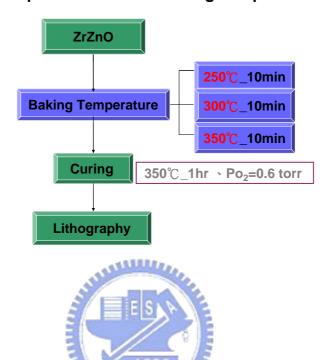

<u>Table 3</u> shows experimental flow path of changing baking temperature in my experiment.

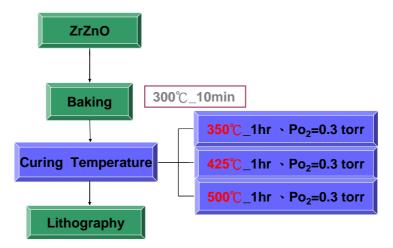

<u>Table 4</u> shows experimental flow path of changing curing temperature in my experiment.

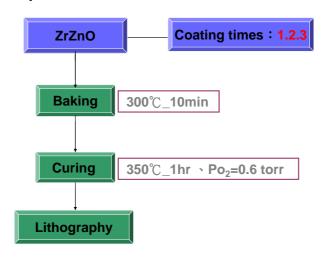

**Table 5** shows experimental flow path of changing film Thickness in my experiment.

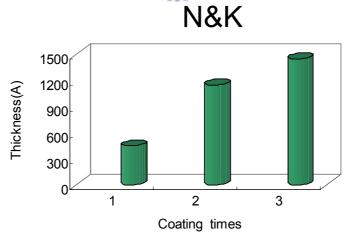

<u>Table 6</u> shows the N&K measurement result of varied thickness Zr<sub>0.03</sub>Zn<sub>0.97</sub>O film on a single crystalline Silicon substrate.

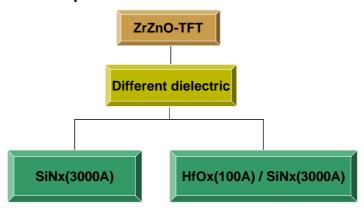

<u>Table 7</u> shows experimental flow path of changing interface contact layer in my experiment.

#### Chapter3

**Table 8** shows the binding evergy of varied element for the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films.

<u>Table 9</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different baking conditions but at the same 350°C curing temperature.

<u>Table 10</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different thickness of the film.

<u>Table 11</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different dielectric layer.

## Figure captions

#### Chapter1

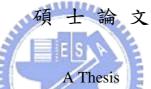

*Figure 1-1* shows the ID-VG of ZnO and Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs.

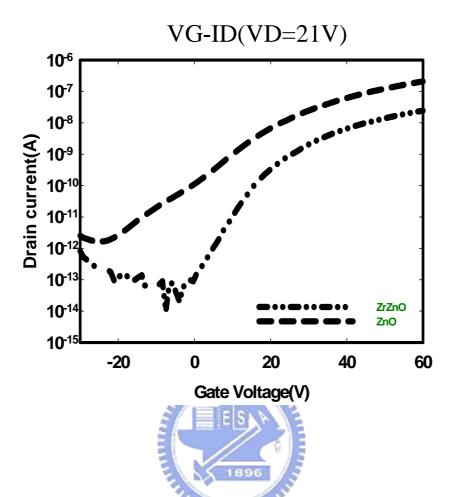

**Figure 1-2** shows the corresponding peaks of FTIR for  $Zr_{0.03}Zn_{0.97}O$ .

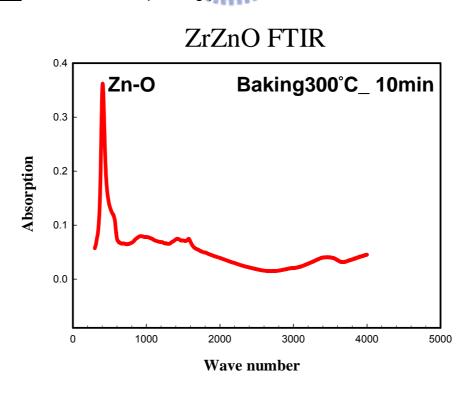

**Figure 1-3** shows the hexagonal wurtize structure of  $Zr_{0.03}Zn_{0.97}O$ .

#### Chapter2

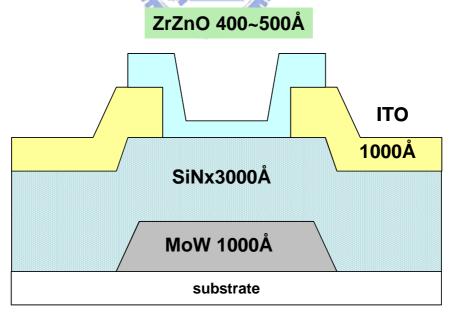

*Figure2-1* shows a device structure of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs.

#### Chapter3

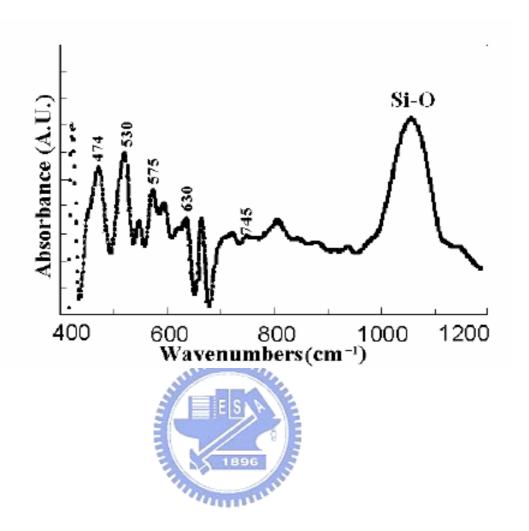

*Figure3-1* shows the corresponding peaks of FTIR for ZrO.

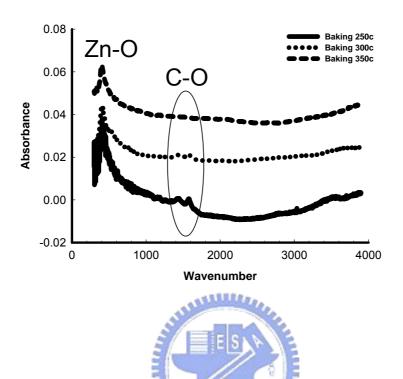

<u>Figure3-2</u> illustrates the FTIR measurement result of varied baking temperature  $Zr_{0.03}Zn_{0.97}O$  film on a single crystalline Silicon substrate.

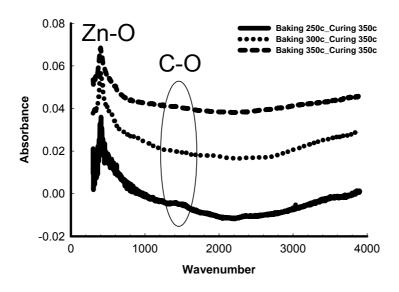

<u>Figure3-3</u> illustrates the FTIR measurement result of 350°C curing temperature  $Zr_{0.03}Zn_{0.97}O \text{ film on a single crystalline Silicon substrate at varied baking temperature}.$

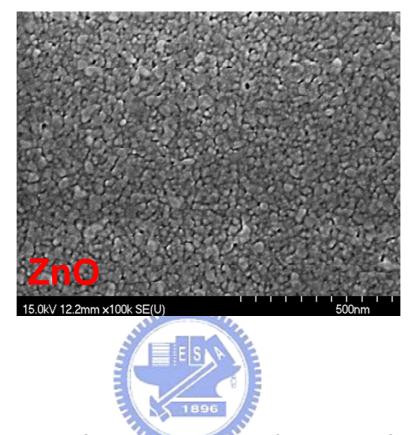

<u>Figure 3-4</u> illustrates the SEM measurement result of the ZnO thin films curing at 350°C under oxygen environment.

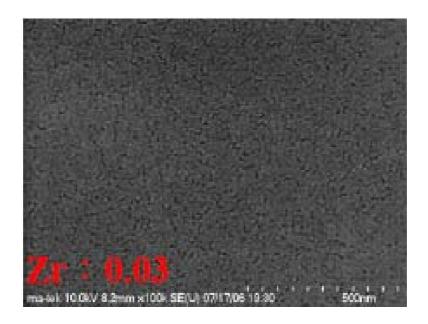

**Figure 3-5** illustrates the SEM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films curing at 350°C under oxygen environment.

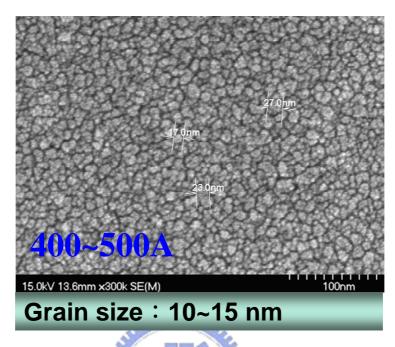

<u>Figure3-6</u> illustrates the SEM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films coating with 400~500A.

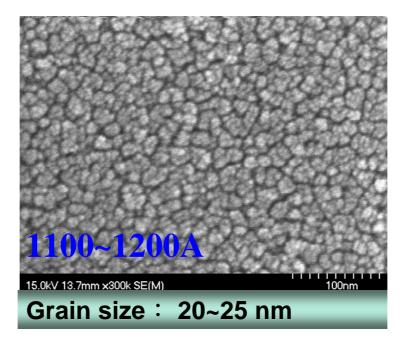

<u>Figure3-7</u> illustrates the SEM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films coating with 1100~1200A.

**Figure 3-8** shows the complicated structure of the thin films with the increases of  $Zr_{0.03}Zn_{0.97}O$  thin films thickness and crystallites size.

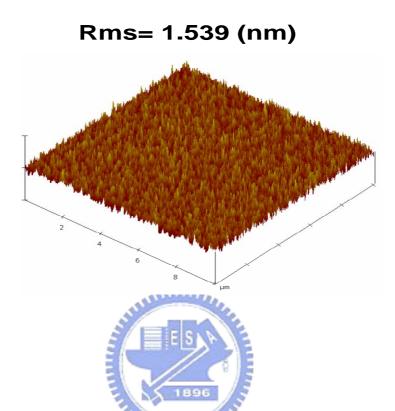

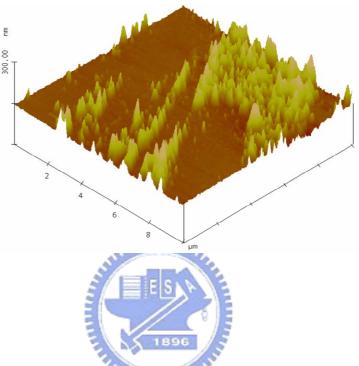

<u>Figure 3-9</u> illustrates the AFM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films baking at 250°C under oxygen environment.

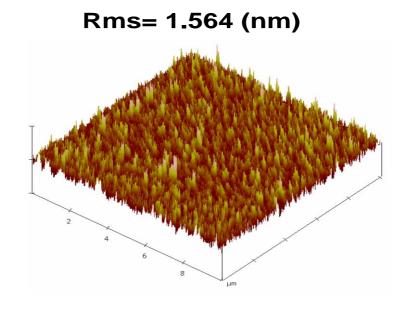

**Figure3-10** illustrates the AFM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films baking at 300°C under oxygen environment.

**<u>Figure3-11</u>** illustrates the AFM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films baking at 350°C under oxygen environment.

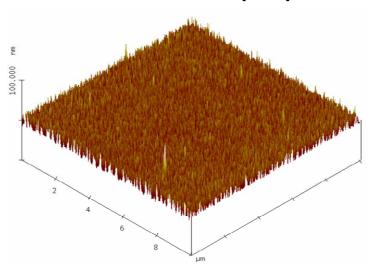

<u>Figure3-12</u> illustrates the AFM measurement result of the Interface contact layer with SiNx dielectric.

<u>Figure3-13</u> illustrates the AFM measurement result of the Interface contact layer with HfOx / SiNx dielectric.

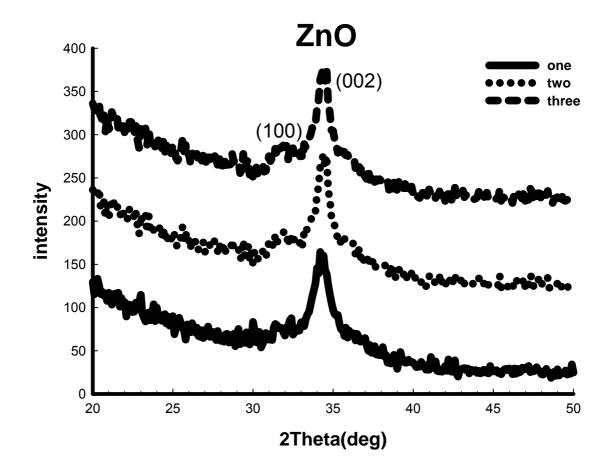

<u>Figure3-14</u> illustrates the XRD measurement result of varied thickness Zr<sub>0.03</sub>Zn<sub>0.97</sub>O films on a single crystalline Silicon substrate.

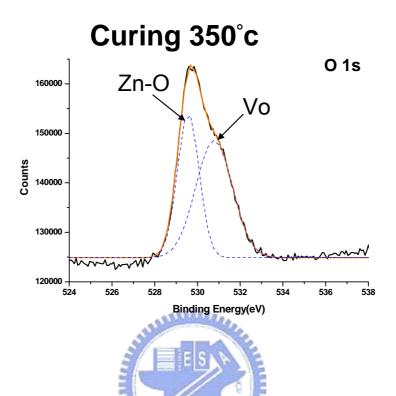

<u>Figure3-15</u> illustrates the XPS measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films curing at 350°C under oxygen environment.

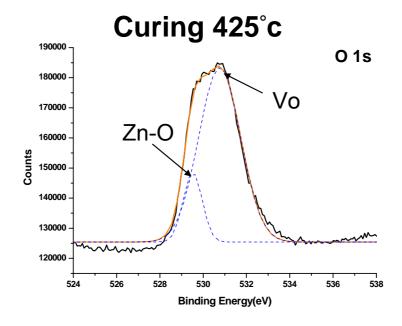

<u>Figure3-16</u> illustrates the XPS measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films curing at 425°C under oxygen environment.

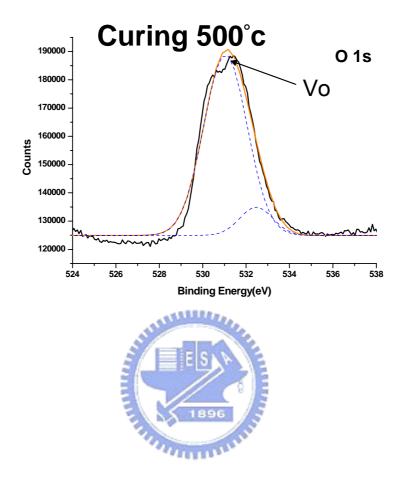

<u>Figure3-17</u> illustrates the XPS measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films curing at 500°C under oxygen environment.

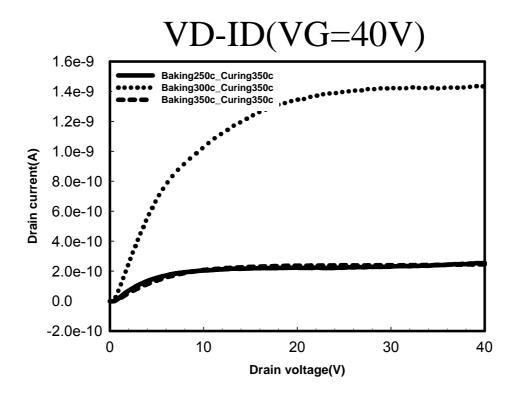

**Figure 3-18** shows the ID-VD of comparison between baking temperature 250~350°C by hot plate.

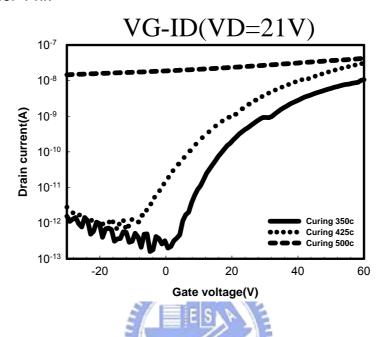

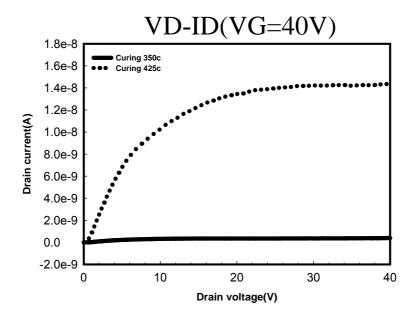

<u>Figure 3-19</u> show the ID-VG of our Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr.

<u>Figure3-20</u> shows the ID-VD of our Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr.

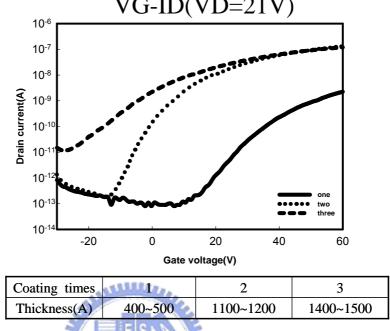

Figure 3-21 shows the ID-VG of our devices with the condition of thicknesses ranging 400~500A, 1100~1200A, 1400~1500A annealed at 350°C under oxygen ambient with for 1 hr.

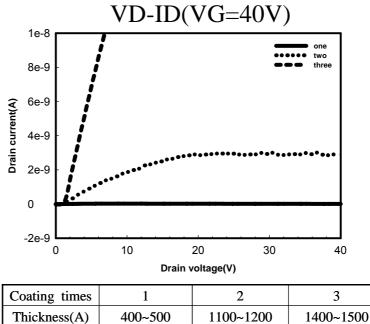

Figure 3-22 shows the ID-VD of our devices with the condition of thicknesses ranging 400~500A , 1100~1200A , 1400~1500A annealed at 350°C under oxygen ambient with for 1 hr.

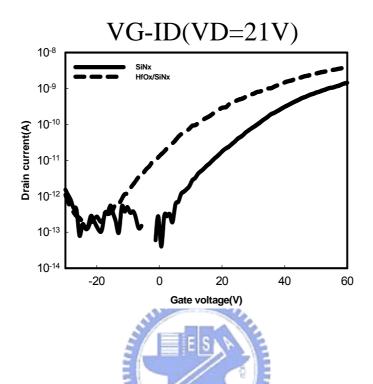

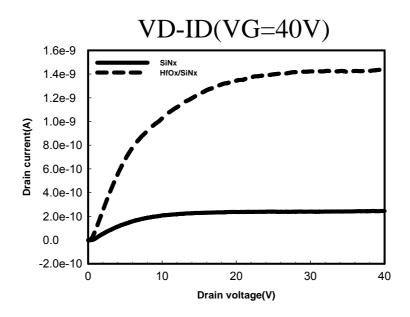

<u>Figure 3-23</u> shows the ID-VG of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx .

<u>Figure 3-24</u> shows the ID-VD of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx .

## **Chapter 1 Introduction**

## 1-1 General Background

ZnO-based thin-film transistors 〈TFTs〉 have attracted much attention over the last several years because of the following several potentials toward future electronic and optoelectronic applications: replacing conventional amorphous-Si TFT, realizing transparent electronics, and functioning as an efficient photodetector. Thin-film transistors TFTs made of transparent channel semiconductors such as ZnO are of great technological importance because their insensitivity to visible light makes device structures simple.

Sol-gel derived mixed oxide films also attracted attention of many researchers working in this field due to its simplicity, cost effectiveness and advantage for large area deposition.

The mixed oxide of Zn and Zr are very rarely studied and might be interesting from the point of view of application. With this understanding , we have fabricated mixed oxide of Zn and Zr films using sol–gel method . It is an attractive technique for obtaining thin films and has the advantages of easy control of the film composition and fabrication of a large area thin film with low cost.  $Zn_{1-x}Zr_xO$  films with oxygen deficiency are n-type semiconductors . We have synthesized transparent conducting

ZnO films doped with Zr atoms, the content of Zr atoms is 3 at %.

However ,  $Zn_{1-x}Zr_xO$ -based TFTs appear large off-state current , because the channel is conductive without applying gate bias . This phenomenon may be attributed to the as-deposited  $Zn_{1-x}Zr_xO$  thin films containing high carrier densities , thus increasing the conductivity in the channel. Therefore , the most important work in  $Zn_{1-x}Zr_xO$ -based TFTs research efforts at the moment is to reduce the carrier concentration in  $Zn_{1-x}Zr_xO$  thin films . Since it has been demonstrated that the  $Zn_{1-x}Zr_xO$  films exhibited a lower carrier concentration with a lower annealing temperature . In this study , we investigated the properties of sol-gel derived Zr-doped ZnO films at a low annealing temperature of  $350^{\circ}C$ .

In the present study , the electrical and structural properties of Sol-gel derived  $Zn_{1-x}Zr_xO \text{ films and thin-film transistors TFTs have been studied and discussed.}$

#### 1-2 Motivation

Zinc oxide (ZnO), a transparent film, is very popularly used due to its unique optical and electronic properties in solar cells, photo detectors, light emitting devices, gas sensor elements, and surface acoustic wave guides. Also, ZnO films have recently been studied as the active channel layers (ACLs) in thin-film transistors (TFTs)

development because of its exhibiting n-type semiconductive characteristic with wide band gap of 3.3 eV, excellent chemical and thermal stability, and can be well-oriented crystalline on various substrate.

<u>Figure 1-1</u> shows electronic properties of ZnO and  $Zr_{0.03}Zn_{0.97}O$  based -TFTs, we get low off-state current to by Zr-doped ZnO films TFTs. However,we use the material of Zr-doped ZnO  $\langle Zr_{0.03}Zn_{0.97}O \rangle$  films as the active channel layers (ACLs).

Several methods are applied to prepare  $Zr_{0.03}Zn_{0.97}O$  films, both physical and chemical deposition technologies including sputtering , pulsed laser deposition (PLD) , chemical vapor deposition (CVD) , molecular beam epitaxy ,and the mobilities ranging from 0.05 to 70 cm2/Vs were obtained with these studies. Besides the fabrication of  $Zr_{0.03}Zn_{0.97}O$  ACLs in TFTs involving vacuum facilities mentioned above, some studies demonstrated another deposition method, Sol-Gel, to fabricate  $Zr_{0.03}Zn_{0.97}O$  ACL in TFTs. Some one reported that  $Zr_{0.03}Zn_{0.97}O$  -TFTs had been prepared by the sol-gel process through spin-coating deposition method. Therefore, the Sol-Gel process has been an attractive technology which is simple and low cost for depositing device components and low cost than vacuum techniques.

The Zr-O bonding is not found in  $Zr_{0.03}Zn_{0.97}O$  thin films by the FTIR measurement in <u>Figure 1-2</u> So,  $Zr_{0.03}Zn_{0.97}O$  having a hexagonal wurtize structure as shown in <u>Figure 1-3</u> has a variety of optical and electrical properties depending on deposition

condition. In general, the structure, electrical properties,  $Zr_{0.03}Zn_{0.97}O$  composition are strongly affected by various processing conditions such as the geometry of the apparatus, plasma conditions, gas phase composition, processing temperature and annealing temperature.

In the present article, we decided the patterning method of  $Zr_{0.03}Zn_{0.97}O$  films and performed the bottom-gate type TFT device with a patterned active channel  $Zr_{0.03}Zn_{0.97}O$  film on that used the Sol-Gel proces method. By considering the carrier concentration, the properties of films and characteristics of  $Zr_{0.03}Zn_{0.97}O$  -TFTs were studied . Finally , in order to get a good  $Zr_{0.03}Zn_{0.97}O$  -TFT devices , we describe the introduction of a HfOx capping layer onto the SiNx films.

## Chapter 2 Experimental Procedure

<u>Table 1</u> shows experimental flow path in my experiment. There were seldom papers about this deposition method for depositing  $Zn_{1-x}Zr_xO$  film for TFTs utility. Because of the innovation of Sol-Gel , we got to reference lots of surveys on other deposition and treatment methods. Finally , we defined a suitable deposition condition.

Thin films deposited procedures have been studied for a long time. We can divide the thin film deposited procedures roughly in two parts. One is Physical Vapor Deposition (PVD), and another one is Chemical Vapor Deposition (CVD) Technique. In this study, we use a Chemical Vapor Deposition (CVD)—Spin Coater to deposit the  $Zn_{1-x}Zr_xO$  films as channel layer.

#### 2-1 TFT Fabrication

In order to making sure our  $Zn_{1-x}Zr_xO$  TFTs have lower off current , we demonstrated the  $Zn_{1-x}Zr_xO$ -based TFT with a conventional structure , to fabricating easily and efficiently.

The device structure of  $Zn_{1-x}Zr_xO$  based -TFTs as shown in <u>Figure2-1</u> is the

bottom-gate type and was fabricated by the following sequence of processes. The metal MoW was deposited on the glass substrate as a bottom gate electrode . Silicon Nitride served as the gate insulator with a thickness of 3000 Å. The source and drain electrodes were made up of indium-tin oxide (ITO) and channel width and length were 50 and 3  $\,\mu$  m , respectively . Finally , the Zn<sub>1-x</sub>Zr<sub>x</sub>O thin films were deposited by spin coating with the processing parameters.

Device structure of  $Zn_{1-x}Zr_xO$  -TFTs in bottom-gate type were fabricated by the Taiwan TFT LCD Association (TTLA). The  $Zn_{1-x}Zr_xO$  film were fabricated by spin coater in the National Nano Device Laboratories (NDL).

## 2-2 Experimental Procedures

After spin-coating  $Zn_{1-x}Zr_xO$  thin films , it will be treated with varied methods. However , we had controlled its temperature , oxygen pressure and gas flowing in high vacuum atmosphere by Backend Vacuum Annealing Furnace. In addition ,  $Zn_{1-x}Zr_xO$  -TFTs with active layer thicknesses ranging from 400 nm to 1500 nm were produced at room temperature using spin-coating. Then , in order to get good interface characteristics , we describe the introduction of a HfOx capping layer onto the SiNx films.

Finally, the material analysis and the electrical characteristic of our devices had been measured and discussed.

#### 2-2-1 spin-coating deposition

<u>Table 2</u> shows experimental flow chart of sol-gel precursor preparation . The  $Zn_{1-x}Zr_xO$  sol-gel precursors were synthesized by the mixing of zinc Acetate  $\{Zn(CH_3COO)_2 \cdot 2H_2O\}$  and zirconium isopropoxide  $\{Zr[(CH_3)_2CHO]_2\}$  dissolved in 2-methoxyethanol and monoethanolamine (MEA), and the solutions were stirring at 60°C for 30 min. The nominal x value for  $Zn_{1-x}Zr_xO$  is 0.03.  $Zr_{0.03}Zn_{0.97}O$  thin films were deposited using the sol-gel solution by the spin-coating method. After coating , the films were immediately baked at 300°C for 10 min on the Hot-plate.

The rotation rate of the spin coater is 400 rpm 15 seconds for step1 and 2000 rpm 20 seconds for step 2.

## 2-2-2 Changing Baking Temperature

<u>Table 3</u> shows experimental flow path of changing baking temperature in my experiment. After deposited by spin coating, the films were dried at three conditions

ranged from 250 ~350°C for 10 min over a hot plate to evaporate the solvent and remove organic residuals. The procedures from coating to drying were only one times until the desired thickness of the sintered films was reached. Then we discussed the effect of removal solvent , the influence of crystallinity and uniformity of  $Zr_{0.03}Zn_{0.97}O$  thin film.

#### 2-2-3 Patterning

There are many scientific or technical literature which report HCl and HNO $_3$  can etch  $Zr_{0.03}Zn_{0.97}O$ . But we find the solution's etching rate is too fast . It will damage the  $Zr_{0.03}Zn_{0.97}O$  pattern and exhibit a lateral etching phenomenon . So , we use the  $CH_3COOH$  as buffer solution to reduce the etching rate . In our studies , we find out the optimal solution rate as  $H_2O$ :  $CH_3COOH$ :  $HCl/HNO_3$ : = 1 : 2 : 40 .  $HNO_3$  is main etching solution.  $CH_3COOH$  is buffer solution for reducing the etching rate. In our study ,  $Zr_{0.03}Zn_{0.97}O$  films are patterned by photolithography and wet-etching with the solution mention above.

#### 2-2-4 Changing Annealing Temperature

<u>Table 4</u> shows experimental flow path of changing curing temperature in my experiment . The electrical properties of  $Zr_{0.03}Zn_{0.97}O$  -TFTs are closely related to its crystal structure and oxygen vacancies (Vo) , which can be controlled by doping or annealing conditions in oxygen atmosphere. In general , the intrinsic defects in ZnO films include oxygen vacancy (Vo) , interstitial zinc (Zni) , etc. However , these defects can effect the electron concentration . The influence of oxygen vacancies (Vo) on the conductivity of the  $Zr_{0.03}Zn_{0.97}O$  has been confirmed in this experiment . For  $Zr_{0.03}Zn_{0.97}O$  thin film , the change in the concentration of the oxygen vacancy (Vo) could lead to the change of the electron concentration and hence make the system change from semiconductor to conductor. In this section , we adjusted the annealing temperature for  $Zr_{0.03}Zn_{0.97}O$  films to find out the optimal conditions for TTFTs.

In our studies , Vacuum Annealing Furnace was used as annealing equipment , when we wanted to add the temperature conditions to improve the properties of  $Zr_{0.03}Zn_{0.97}O$  films. Samples could be studied with only temperature influence in high vacuum atmosphere , or in a pure oxygen or nitrogen atmosphere by using vacuum Annealing Furnace.

After spin-coating ,  $Zr_{0.03}Zn_{0.97}O$  films were immediately dried , and then annealed in a Back-end vacuum annealing furnace at 350 425 500°C for 1 hr under oxygen ambient.

#### 2-2-5 Changing Film Thickness

<u>Table 5</u> shows experimental flow path of changing film Thickness in my experiment. In general, the physical characteristics of polycrystalline semiconductors are easily modified by their crystallite sizes and boundary effects. The electrical properties are much more easily disturbed as long as the band structure altered inside the crystallites from the optical properties. The size of crystallites and the magnitude of the associated grain-boundary effects are dependent upon the preparation and treatment method, such as temperature in deposition or annealing, sputtering process, and deposition technique. In this section, we adjusted the annealing temperature for  $Zr_{0.03}Zn_{0.97}O$  films to find out the optimal conditions for TTFTs.

When we wanted to change the thickness of the thin film to improve the properties of  $Zr_{0.03}Zn_{0.97}O$  films , samples could be studied with only thickness influence by using spin-coating times. Because the rotation rate of the spin coater is const , We coat films with 1~3 times on the Hot-plate.

Among a number of deposition conditions which can obviously influence the properties of  $Zr_{0.03}Zn_{0.97}O$  films , by the material analysis and electrical characteristic to establish a database of  $Zr_{0.03}Zn_{0.97}O$  thin films. And we can choose to an optimal deposition condition for TFTs. We use N&K analyzer to measure the thickness and SCANNING ELECTRON MICROSCOPE (SEM) to analysis the grain size of

$Zr_{0.03}Zn_{0.97}O$  . All those films were examined by Fourier Transform Infra-Red (FTIR) to check the bonding (AFM PL XRD XPS) .The N&K measurement result of varied thickness  $Zr_{0.03}Zn_{0.97}O$  film on a single crystalline Silicon substrate as shown in **Table 6**.

#### 2-2-6 Changing interface contact layer

<u>Table 7</u> shows experimental flow path of changing interface contact layer in my experiment . We report on the role of HfOx capping layers in notably improving mobility in  $Zr_{0.03}Zn_{0.97}O$  thin film transistors (TFTs) utilizing compatible SiNx gate insulators . Moreove , we hope that all room temperature processed  $Zr_{0.03}Zn_{0.97}O$  based TFTs with stacked HfOx / SiNx gate insulator can exhibit a much enhanced field effect mobility and excellent saturation characteristics by good interface characteristics

Therefore , in order to get good interface characteristics , we describe the introduction of a HfOx capping layer onto the SiNx films . The HfOx thin films of 100 nm thickness were then deposited by dc sputtering with the following operating conditions : power\_150 (W) , sputtering rate\_0.3 (A/sec) , and Ar/O<sub>2</sub>\_24/3 [SCCM(SCCM denotes cubic centimeter per minute at STP)] atmosphere at room

temperature.

The microstructure and roughness of the SiNx and  $\ HfOx/SiNx$  films were investigated by AFM (Atomic Force Microscopy). Among a number of interface conditions which can obviously influence the properties of channel/dielectric interface by the electrical characteristic. Finally, we use I-V systems to analysis the channel/dielectric interface efficiency for  $Zr_{0.03}Zn_{0.97}O$  thin films.

## Chapter 3 Results and Discussions

## 3-1 ZrZnO Film Analisys

#### 3-1-1 The FTIR Measurement of ZrZnO Films

The principle of FTIR is that the energy of the molecules of our samples in unoccupied excited rotational and vibrational states , which is different from the ground-states , can correspond to photon energies found in the infrared. These can be detected and identified by FTIR. *Figure 1-2* shows the corresponding peaks of FTIR for  $Zr_{0.03}Zn_{0.97}O$  thin films. There are three peaks in the wavelength (cm<sup>-1</sup>) of 437 , 617 and 675. These peaks belonged to ZnO. There is one peak in the wavelength (cm<sup>-1</sup>) of 3500. These peaks belonged to O-H bonding . *Figure 3-1* shows the corresponding peaks of FTIR for ZrO. There are five peaks in the wavelength (cm<sup>-1</sup>) of 474, 530, 575, 630, 645. These peaks belonged to ZrO<sub>2</sub>. The Zr-O bonding is not found in  $Zr_{0.03}Zn_{0.97}O$  thin films by the FTIR measurement.

<u>Figure 3-2</u> illustrates the FTIR measurement result of varied baking temperature  $Zr_{0.03}Zn_{0.97}O$  film on a single crystalline Silicon substrate. In this studies , we find out that the organic bonding can be removed completely by baking procedures.

**Figure 3-3** illustrates the FTIR measurement result of  $350^{\circ}$ C curing temperature  $Zr_{0.03}Zn_{0.97}O$  film on a single crystalline Silicon substrate at varied baking temperature. In this studies , we find out that the organic bonding can be removed completely at  $350^{\circ}$ C.

In other words , no organic peaks were detected in the  $Zr_{0.03}Zn_{0.97}O$  thin films by FTIR where the curing temperature is higher than 350°C.

## 3-1-2 The SEM Measurement of ZrZnO Films

The Scanning Electron Microscope (SEM) is a microscope that uses electrons rather than light to form an image. There are many advantages to using the SEM instead of a light microscope.

The SEM has a large depth of field, which allows a large amount of the sample to be in focus at one time. The SEM also produces images of high resolution, which means that closely spaced features can be examined at a high magnification. Preparation of the samples is relatively easy since most SEMs on require the sample to be conductive. The combination of higher magnification, larger depth of focus, greater resolution, and ease of sample observation makes the SEM one of the most heavily used instruments in research areas today.

We can check the grain size of ZnO and  $Zr_{0.03}Zn_{0.97}O$  thin films by SEM measurement . *Figure3-4* illustrates the SEM measurement result of the ZnO thin films curing at 350°C under oxygen environment. *Figure3-5* illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 350°C under oxygen environment. , Before, we used SEM to analysis the ZnO and  $Zr_{0.03}Zn_{0.97}O$  films.

Now , We want to find out the grain size of  $Zr_{0.03}Zn_{0.97}O$  thin films with different spin-coating times by SEM measurement. In our studies, we use SEM to analysis the  $Zr_{0.03}Zn_{0.97}O$  films which are  $400\sim500A$  and  $1100\sim1200A$ . *Figure3-6* illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films coating with active layer thicknesses ranging from 400A to 500A. *Figure3-7* illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films coating with active layer thicknesses ranging from 1100A to 1200A.

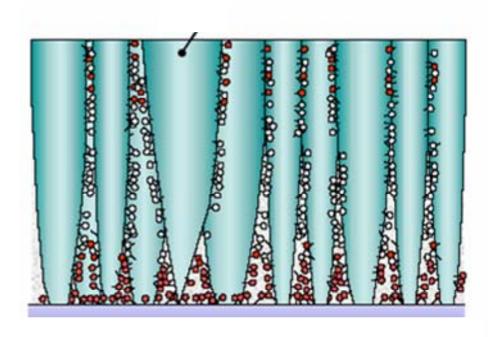

From the analysis by SEM, we can conclude that  $Zr_{0.03}Zn_{0.97}O$  thin film contained an amorphous incubation layer at the substrate interface and increased grain at the top of the film. As thickness of the thin film increases its grain size also increases, the complicated structure of  $Zr_{0.03}Zn_{0.97}O$  thin films can be schematized as shown in

#### Figure 3-8

#### 3-1-3 The AFM Measurement of ZrZnO Films

In my studies, I use Atomic Force Microscopy  $\langle$  AFM $\rangle$  to analysis the roughness of the  $Zr_{0.03}Zn_{0.97}O$  thin film. The atomic force microscope  $\langle$  AFM $\rangle$  is a very high-resolution type of scanning probe microscope, with demonstrated resolution of fractions of an Angstrom, more than 1000 times better than the optical diffraction limit. The AFM was invented by Binnig,Quate and Gerber in 1986, and is one of the foremost tools for imaging, measuring and manipulating matter at the nanoscale.

<u>Figure3-9</u> illustrates the AFM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films baking at 250°C under oxygen environment. <u>Figure3-10</u> illustrates the AFM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films baking at 300°C under oxygen environment. <u>Figure3-11</u> illustrates the AFM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films baking at 350°C under oxygen environment.

From the analysis by AFM , we can conclude that the uniformity decrease with higher temperature. The best roughness is baking at 250°C. But we can not remove organic bond at 250°C , so we use two-step baking to solve this problem. First , we put the  $Zr_{0.03}Zn_{0.97}O$  -TFTs on the hotplate at low temperature to get an uniform thin films and then we put the  $Zr_{0.03}Zn_{0.97}O$  -TFTs in the Furnace at 350 °C to remove organic bonding.

*Figure3-12* illustrates the AFM measurement result of the Interface contact layer

with SiNx dielectric . <u>Figure3-13</u> illustrates the AFM measurement result of the Interface contact layer with HfOx / SiNx dielectric.

From the analysis by AFM, we can conclude that the uniformity of HfOx / SiNx dielectric layer is the best. On the other hand, it can improve effectively roughness of the interface between the semiconducting layer and the gate insulator.

#### 3-1-4 The XRD Measurement of ZrZnO Films

X-ray Diffraction  $\langle$  XRD $\rangle$  measurement result can indicate that preferred orientation of the  $Zr_{0.03}Zn_{0.97}O$  film is c-axis perpendicular to the substrate. X-ray Diffraction  $\langle$  XRD $\rangle$  is one of the most important non-destructive tools to analyse all kinds of matter - ranging from fluids , to powders and crystals. From research to production and engineering , XRD is an indispensible method for materials characterization and quality control. Rigaku has developed a range of diffractometers , in co-operation with academic and industrial users , which provide the most technically advanced , versatile and cost-effective diffraction solutions available today.

<u>Figure 3-14</u> illustrates the XRD measurement result of varied thickness  $Zr_{0.03}Zn_{0.97}O$  films on a single crystalline Silicon substrate. It can be seen that all of the compositions exhibited (002) peak at  $2\theta$ =34.2 degree and belonged to the hexagonal wurtzite structure of  $Zr_{0.03}Zn_{9.97}O$ . And the (100) peak was appeared and it

also belonged to the hexagonal wurtzite structure of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O.

In this studies , we find out that the varied thickness can not effect the orientation of the  $Zr_{0.03}Zn_{0.97}O$  films by spin-coating times.

#### 3-1-5 The XPS Measurement of ZrZnO Films

The X-ray Photoelectron Spectroscopy (XPS) technique is highly surface specific due to the short range of the photoelectrons that are excited from the solid. The energy of the photoelectrons leaving the sample are determined using a Concentric Hemispherical Analyser and this gives a spectrum with a series of photoelectron peaks. The binding energy of the peaks are characteristic of each element. The peak areas can be used (with appropriate sensitivity factors) to determine the composition of the materials surface. The shape of each peak and the binding energy can be slightly altered by the chemical state of the emitting atom. Hence XPS can provide chemical bonding information as well.

First , we rose the temperature from 350°C to 500°C to analysis the oxygen vacancy (Vo) of the  $Zr_{0.03}Zn_{0.97}O$  thin films. We can have different full lines for O 1s from 350°C to 500°C . Then , it get two main peak in banding evergy for three different

figure by fitting . The binding evergy of varied element can be observed for the  $Zr_{0.03}Zn_{0.97}O$  thin films as shown in <u>Table 8</u>. One is Zn-O binding evergy  $\langle$  530.15 eV $\rangle$ , another is oxygen vacancies binding evergy  $\langle$  531.25 eV $\rangle$ . <u>Figure 3-15</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 350°C under oxygen environment. <u>Figure 3-16</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 425°C under oxygen environment. <u>Figure 3-17</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 500°C under oxygen environment.

In this studies , we find out that an peak at oxygen vacancies (Vo) is observed clearly than Zn-O by the analysis of XPS with higher temperature . In the words , it reveals that oxygen vacancy (Vo) increase for the  $Zr_{0.03}Zn_{0.97}O$  thin films with higher temperature.

# 3-2 The Electrical Characteristics of ZrZnO based TFTs

#### 3-2-1 Baking with various temperature

We put  $Zr_{0.03}Zn_{0.97}O$  thin films on hotplate to remove the solvent and organic residuals bonding. The temperatures were 250, 300 and 350°C. *Figure3-18* shows the ID-VD of comparison between baking temperature 250~350°C by hot plate. And the annealing temperature is 350°C and pressure is 0.6 torr with W/L=50/3  $\mu$ m.

From the electrical characteristic , we can conclude that The condition of baking 300°C for 10 min shows a maximum saturated current (I<sub>sat</sub>). The condition of baking 300°C for 10 min shows the best semiconducting property.

## 3-2-2 Annealing with various temperature

We put  $Zr_{0.03}Zn_{0.97}O$  thin films in Vacuum Annealing Furnace under 0.3 torr oxygen ambient and the temperature are 350 425 500°C. When we annealed  $Zr_{0.03}Zn_{0.97}O$  TFTs with 500°C for 1 hr, it shows a normally on phenomenon. This result attribute to bigger grain size and higher carrier concentration. *Figure3-19* show the ID-VG of our  $Zr_{0.03}Zn_{0.97}O$  based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr. *Figure3-20* shows the ID-VD of our  $Zr_{0.03}Zn_{0.97}O$  based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr.

**Table 9** shows electronic properties of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs with different

baking conditions but at the same 350°C curing temperature . The maximum mobility ( $\mu$ ) of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs is 1.5\*10<sup>-4</sup> V<sup>-1</sup>.s<sup>-1</sup>, where the curing temperature is 425°C. The minimum threshold voltage (Vt) of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs is 21.3 volt, where the curing temperature is 425°C. According to the *Table 9*, the threshold voltage (Vt) decreased with higher curing temperature.

So , It can be deduced that oxygen vacancy (Vo) increases with higher temperature when the samples were annealed in oxygen atmosphere. For  $Zr_{0.03}Zn_{0.97}O \text{ thin films , the change in the concentration of the oxygen vacancy(Vo)}$  could lead to the change of the electron concentration. It reveals that oxygen vacancy (Vo) increase with higher curing temperature to have more carrier concentration.

From the electrical characteristic , we can conclude that oxygen vacancy (Vo) and free carrier increase with higher temperature. Therefore , when we annealed at  $500^{\circ}$ C , the electronic characteristic exhibited normally-on characteristic for  $Zr_{0.03}Zn_{0.97}O$  based-TFTs.

#### 3-2-3 Spin-coating with various film thickness

We put Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films with varied thickness in Vacuum Annealing Furnace at 350°C under oxygen ambient 0.6 torr. *Figure 3-21* shows the ID-VG of our devices

with the condition of thicknesses ranging 400~500A, 1100~1200A, 1400~1500A annealed at 350°C under oxygen ambient with for 1 hr. *Figure 3-22* shows the ID-VD of our devices with the condition of thicknesses ranging 400~500A, 1100~1200A, 1400~1500A annealed at 350°C under oxygen ambient with for 1 hr.

*Table 10* shows the threshold voltage (Vt) , mobility (μ) and on/off current (I<sub>on/off</sub>) of the varied thickness. It can be seen that the threshold voltage (Vt) decreased dramatically with thickness of the thin film. The mobility (μ) increased dramatically with thickness of the thin film. The maximum mobility (μ) of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs was  $6.0X10^{-4}~V^{-1}.s^{-1}$ , where the thickness of the thin film is between 1100A  $\sim 1200$ A. The minimum threshold voltage (Vt) of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs was 18.6 volt , where the thickness of the thin film is between 1100A  $\sim 1200$ A. The maximum on/off current (I<sub>on/off</sub>) of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs was 7.4\*10<sup>5</sup> , where the thickness of the thin film is between 1100A  $\sim 1200$ A.

From the electrical characteristic , we can conclude that it is clearly visible that increasing the active layer thickness, leads to higher on-current . off-current and lower Vt.

Concerning the variation of the on-current , It can be deduced that carrier concentration increases with thickness , leading to an higher flow of electrons pass through the channel layer until 1100A  $\sim$  1200A . Concerning the variation of the

off-current , it surely is related that more carrier can not be controlled with increasing thickness for gate electrode , leading to the leakage current is oversized where the thickness of the thin film is between 1400A  $\sim 1500 A$ . Concerning the decrease of Vt with increasing thickness , The grain size increase with thickness of the thin film.one can possible consider that result a consequence of the higher number of free carrier in the bulk of the thicker semiconductor because of the grain size , thus conducting to an easier accumulation of charges in the semiconductor / dielectric interface than in thinner films . The characteristic of thickness of the  $Zr_{0.03}Zn_{0.97}O$  thin films between  $1100A \sim 1200A$  is the most suitable at present.

## 3-2-4 Interface contact layer with various dielectric

In this chapter, we use two kinds of dielectric layer, SiNx and HfOx / SiNx. <u>Figure</u>

3-23 shows the ID-VG of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx. <u>Figure 3-24</u> shows the ID-VD of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx.

<u>Table 11</u> shows the threshold voltage (Vt) , mobility ( $\mu$ ) and saturated current (I<sub>sat</sub>) of the varied Interface. It can be seen that the threshold voltage (Vt) decreased dramatically with dielectric layer HfOx / SiNx . The mobility ( $\mu$ ) increased dramatically

with dielectric layer HfOx / SiNx . The saturated current ( $I_{sat}$ ) increased slightly with dielectric layer HfOx / SiNx . The mobility ( $\mu$ ) of  $Zr_{0.03}Zn_{0.97}O$  thin film transistor was  $9.0 \times 10^{-5} \ V^{-1}.s^{-1}$  with dielectric layer HfOx / SiNx. The threshold voltage (Vt) of  $Zr_{0.03}Zn_{0.97}O$  thin film transistor was 19.5 volt with dielectric layer HfOx / SiNx. The saturated current ( $I_{sat}$ ) of  $Zr_{0.03}Zn_{0.97}O$  thin film transistor was 1.4X10<sup>-9</sup> A with dielectric layer HfOx / SiNx.

From the electrical characteristic , we can conclude that with dielectric layer HfOx / SiNx. The very smooth HfOx / SiNx films ensure both high-quality  $Zr_{0.03}Zn_{0.97}O$  layers and  $Zr_{0.03}Zn_{0.97}O$  / HfOx interfaces, resulting in improved carrier mobility due potentially to both reduced disorder in the  $Zr_{0.03}Zn_{0.97}O$  film as well as reduced interfacial scattering.

# **Chapter 4 Conclusion**

We have developed an optimized deposition condition for Sol-Gel Zr<sub>0.03</sub>Zn<sub>0.97</sub>O semiconductor film and succeeded to fabricate a Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based - transparent thin film transistor with bottom-gate structure . The optimal conditions for depositing the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O film by Spin Coater at room temperature is baking 300°C on the Hotplate. With the development of wet etchants,  $Zr_{0.03}Zn_{0.97}O$  active regions can be patterned exactly and completing TFT device fabrication. Followed by the implementation of thermal annealing at different temperature, the mechanism and the effect of thermal treatment on Zr<sub>0.03</sub>Zn<sub>0.97</sub>O films also were studied in detail. High temperature annealing process seems to cause the high carrier concentration, and increase the conductivity dramatically. The most suitable deposition condition for Zr<sub>0.03</sub>Zn<sub>0.97</sub>O films with sol-gel system have been successfully established by annealing ZnO at 425°C and with 30 sccm oxygen flow at 0.3 torr. Then, the experiment of thickness on Zr<sub>0.03</sub>Zn<sub>0.97</sub>O films at spin-coating procedures, the mechanism and the effect of thickness on Zr<sub>0.03</sub>Zn<sub>0.97</sub>O films also were studied particularly. It confirms the high carrier concentration with thickness because of the size of grain. It has be demonstrated that we can obtain the best characteristic when thickness of the film is between 1100A  $\sim$  1200A . Since the improved mobility is suspected to be related to the decreased roughness of the

interface between the semiconducting layer and the gate insulator . This phenomenon may be attributed to rough channel/dielectric interface with SiNx dielectric layer , thus , we describe the introduction of a HfOx capping layer onto the SiNx films. In other words , in order to get a good device , we replace SiNx with HfOx / SiNx as dielectric layer.

For large area flat-panel display fabrication , the chemical solution deposition process provides a more efficient way for depositing device components than vacuum techniques. In conclusion , We also successfully demonstrated  $Zr_{0.03}Zn_{0.97}O$  based - TFT on glass substrate with low annealing temperature.

In the future,  $Zr_{0.03}Zn_{0.97}O$  -based transparent thin-film transistors ( TTFT ) can be fabricated because of its unique optical and we also can replace Spin-Coating with Ink-Jetting as deposition technique to reduce the process step.

# References

- [1] S. Masuda et al. "Transparent thin film transistors using ZnO as an active channel layer and their electrical properties." J. Appl. Phys. Vol.93, No.3, p.1624 (2003)

- [2] J. Nishii et al. "High mobility thin film transistor with transparent ZnO channels," Jpn. J. Appl. Phys. Vol. 42, p. L347 (2003)

- [3] Hsing-Hung Hsieh and Chung-Chih Wu, APPLIED PHYSICS LETTERS **89**, 041109 (2006)

- [4] P. Barquinha \*, A. Pimentel, A. Marques, L. Pereira, R. Martins, E. Fortunato, Journal of Non-Crystalline Solids 352 (2006) 1749–1752

- [5] S. Walsh, Wetch Etching fo Semiconductor Fabrication, Janus Ventures Inc.]

- [6] Jen Hao Lee, Pang Lin, Jia Chong Ho, and Cheng Chung Lee, Electrochemical and Solid-State Letters, 9 (4) G117-G120 (2006)

- [7] R E Presley, C L Munsee, C-H Park, D Hong, J F Wager and D A Keszler J. Phys. D: Appl. Phys. 37 (2004) 2810–2813

- [8] Mi-Hwa Lim, KyongTae Kang, and Ho-Gi Kim, APPLIED PHYSICS LETTERS 89, 202908 (2006)

- [9] Masanobu Izakia, and Junichi Katayama Journal of The Electrochemical Society, 147 (1) 210-213 (2000)

- [10] R E Presley, C L Munsee, C-H Park, D Hong, J F Wager and D A Keszler J. Phys. D: Appl. Phys. 37 (2004) 2810–2813

- [11] B J Norris, J Anderson, J F Wager and D A Keszler, J. Phys. D: Appl. Phys. 36 (2003) L105–L107

- [12] Kimoon Lee, Jae Hoon Kim, and Seongil Im, APPLIED PHYSICS LETTERS **89**, 133507 (2006)

- [13] Ü. Özgür, Ya. I. Alivov, C. Liu, A. Teke, M. A. Reshchikov, S. Doðan, V. Avrutin, S.-J. Cho, and H. Morkoç JOURNAL OF APPLIED PHYSICS 98, 041301 (2005)

- [14] B J Norris, J Anderson, J F Wager and D A Keszler, J. Phys. D: Appl. Phys. 36 (2003) L105–L107

*Figure 1-1* shows the ID-VG of ZnO and  $Zr_{0.03}Zn_{0.97}O$  based –TFTs.

*Figure 1-2* shows the corresponding peaks of FTIR for Zr<sub>0.03</sub>Zn<sub>0.97</sub>O.

*Figure 1-3* shows the hexagonal wurtize structure of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O.

*Figure2-1* shows a device structure of Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based –TFTs.

**Bottom Gate Bottom contact**

**<u>Figure3-1</u>** shows the corresponding peaks of FTIR for ZrO.

**Figure 3-2** illustrates the FTIR measurement result of varied baking temperature

Zr<sub>0.03</sub>Zn<sub>0.97</sub>O film on a single crystalline Silicon substrate.

Figure 3-3 illustrates the FTIR measurement result of 350°C curing temperature

Zr<sub>0.03</sub>Zn<sub>0.97</sub>O film on a single crystalline Silicon substrate at varied baking temperature.

**Figure 3-4** illustrates the SEM measurement result of the ZnO thin films curing at 350°C under oxygen environment.

<u>Figure 3-5</u> illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 350°C under oxygen environment.

<u>Figure 3-6</u> illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films coating with 400~500A.

<u>Figure 3-7</u> illustrates the SEM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films coating with 1100~1200A.

<u>Figure 3-9</u> illustrates the AFM measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films baking at 250°C under oxygen environment.

*Figure3-10* illustrates the AFM measurement result of the Zr<sub>0.03</sub>Zn<sub>0.97</sub>O thin films baking at 300°C under oxygen environment.

Rms= 3.499 (nm)

<u>Figure3-12</u> illustrates the AFM measurement result of the Interface contact layer with SiNx dielectric.

<u>Figure3-13</u> illustrates the AFM measurement result of the Interface contact layer with HfOx / SiNx dielectric.

Rms= 4.441 (nm)

| Coating times | 1       | 2         | 3         |

|---------------|---------|-----------|-----------|

| Thickness(A)  | 400~500 | 1100~1200 | 1400~1500 |

<u>Figure 3-15</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 350°C under oxygen environment.

<u>Figure 3-16</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 425°C under oxygen environment.

<u>Figure 3-17</u> illustrates the XPS measurement result of the  $Zr_{0.03}Zn_{0.97}O$  thin films curing at 500°C under oxygen environment.

*Figure3-18* shows the ID-VD of comparison between baking temperature 250~350°C by hot plate.

<u>Figure 3-19</u> show the ID-VG of our  $Zr_{0.03}Zn_{0.97}O$  based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr.

*Figure3-20* shows the ID-VD of our Zr<sub>0.03</sub>Zn<sub>0.97</sub>O based-TFTs devices with the condition of annealed under 0.3 torr oxygen ambient with different temperature 350 425 500°C for 1 hr.

Figure 3-21 shows the ID-VG of our devices with the condition of thickness 400~500A, 1100~1200A, 1400~1500A annealed at 350°C under oxygen ambient VG-ID(VD=21V) with for 1 hr.

| Coating times | Willian. | 2         | 3         |

|---------------|----------|-----------|-----------|

| Thickness(A)  | 400~500  | 1100~1200 | 1400~1500 |

Figure 3-22 shows the ID-VD of our devices with the condition of thickness 400~500A, 1100~1200A, 1400~1500A annealed at 350°C under oxygen ambient

with for 1 hr.

**Figure 3-23** shows the ID-VG of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx .

<u>Figure 3-24</u> shows the ID-VD of our devices with the condition of Interface by different dielectric layer SiNx and HfOx / SiNx .

**Table 1** shows experimental flow path in my experiment.

<u>Table 2</u> shows experimental flow chart of sol-gel precursor preparation.

<u>Table 3</u> shows experimental flow path of changing baking temperature in my experiment.

### **Experiment Flow of Baking Temperature**

<u>Table 4</u> shows experimental flow path of changing curing temperature in my experiment.

#### **Experiment Flow of Curing Temperature**

<u>Table 5</u> shows experimental flow path of changing film Thickness in my experiment.

## **Experiment Flow of Film Thickness**

<u>Table 6</u> shows the N&K measurement result of varied thickness Zr<sub>0.03</sub>Zn<sub>0.97</sub>O film on a single crystalline Silicon substrate.

| Coating times | 1       | 2         | 3         |

|---------------|---------|-----------|-----------|

| Thickness(A)  | 400~500 | 1100~1200 | 1400~1500 |

<u>Table 7</u> shows experimental flow path of changing interface contact layer in my experiment.

## **Experiment Flow of Film Interface**

<u>Table 8</u> shows the binding evergy of varied element for the  $Zr_{0.03}Zn_{0.97}O$  thin films.

# **Binding Energy(eV)**

Zn-O = 530.15 eV

Vo(Oxygen vacancy) ≒531.25 eV

<u>Table 9</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different curing conditions.

|          | Curing 350°C         | Curing 425°C | Curing 500°C |

|----------|----------------------|--------------|--------------|

| Vt       | 33.0                 | 21.3         | X            |

| Mobility | 1.5*10 <sup>-5</sup> | 1.5*10-4     | X            |

<u>Table 10</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different thickness of the film.

AND DELLAR

| Coating times | 2 Es 2                                  | 3        |

|---------------|-----------------------------------------|----------|

| Vt            | 33.0                                    | -2.1     |

| Mobility      | 1.5*10 <sup>-5</sup> 6*10 <sup>-4</sup> | 4.5*10-4 |

| Ion/Ioff      | $2.8*10^4$ $7.4*10^5$                   | 1*104    |

<u>Table 11</u> shows electronic properties of  $Zr_{0.03}Zn_{0.97}O$  based-TFTs with different dielectric layer.

|                  | SiNx                  | HfOx/SiNx            |

|------------------|-----------------------|----------------------|

| Vt               | 33.0                  | 19.5                 |

| Mobility         | 1.2*10 <sup>-5</sup>  | 9*10 <sup>-5</sup>   |

| I <sub>sat</sub> | 2.0*10 <sup>-10</sup> | 1.4*10 <sup>-9</sup> |

#### 簡歷

姓 名:蕭 秀 娟 (Shiou-Jiuan Shiau )

性 別:女

出生年月日:民國 71 年 8 月 18 日

住 址:宜蘭市東港路66巷17弄10號之一

學 歷:

國立中山大學物理學系學士 (90.9-94.6)

國立交通大學光電工程學系顯示科技研究所碩士 (94.9-96.6)

#### 碩士論文題目:

溶膠凝膠法沉積鋯摻雜氧化鋅薄膜電晶體之研究

Study on fundamental properties of ZrZnO-based TFT by Sol-Gel process