# 第 1 章、簡介與研究動機

依照摩爾定律(Moore's Law)所預測的半導體成長趨勢，每十八個月電路的密度將會增加一倍。且隨著現今消費性電子產品要求輕、薄、短、小的特性，電子產品尺寸的持續縮小使得電子構裝技術面臨許多挑戰。電子構裝主要的功能有四，分別是電能傳送(power distribution)、訊號傳送(signal distribution)、熱的散失(heat dissipation)與保護支持(protection and support)。

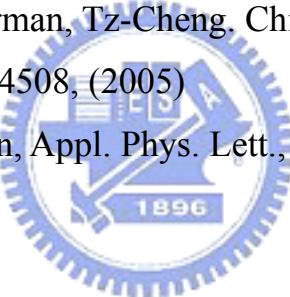

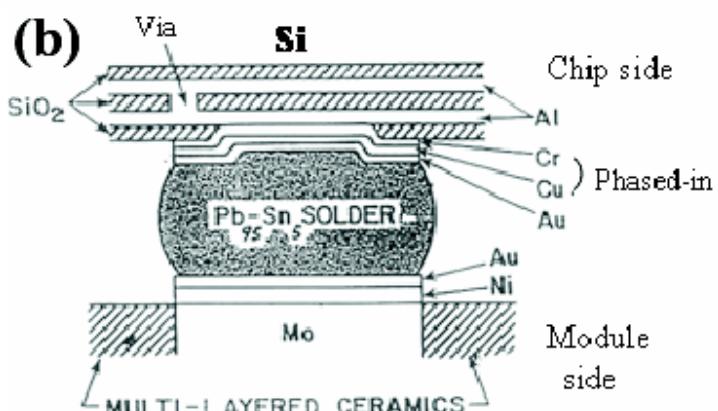

電子構裝又可依照與積體電路的遠近，分層不同的層次如圖 1.1 所示，第一層次的構裝(1<sup>st</sup> level packaging)，又稱晶圓層次的構裝(chip level packaging)，主要是將晶片與構裝結構組合行成模組(module)的製程。第二層次的構裝(2<sup>nd</sup> level packaging)則是將經第一層次構裝後與其它的電子元件組合於電路板上，形成電路卡或電路板；在第二層次的構裝中，最常見的考量是印刷電路板的製作及模組元件與電路板的組裝技術，如插件式技術(pin through hole, PTH)與表面黏著技術(surface mount technology, SMT)。第三層次構裝(third level packaging)與第四層次構裝(fourth level packaging)，是指將電路板與電路卡組合，形成次系統與系統的製程。

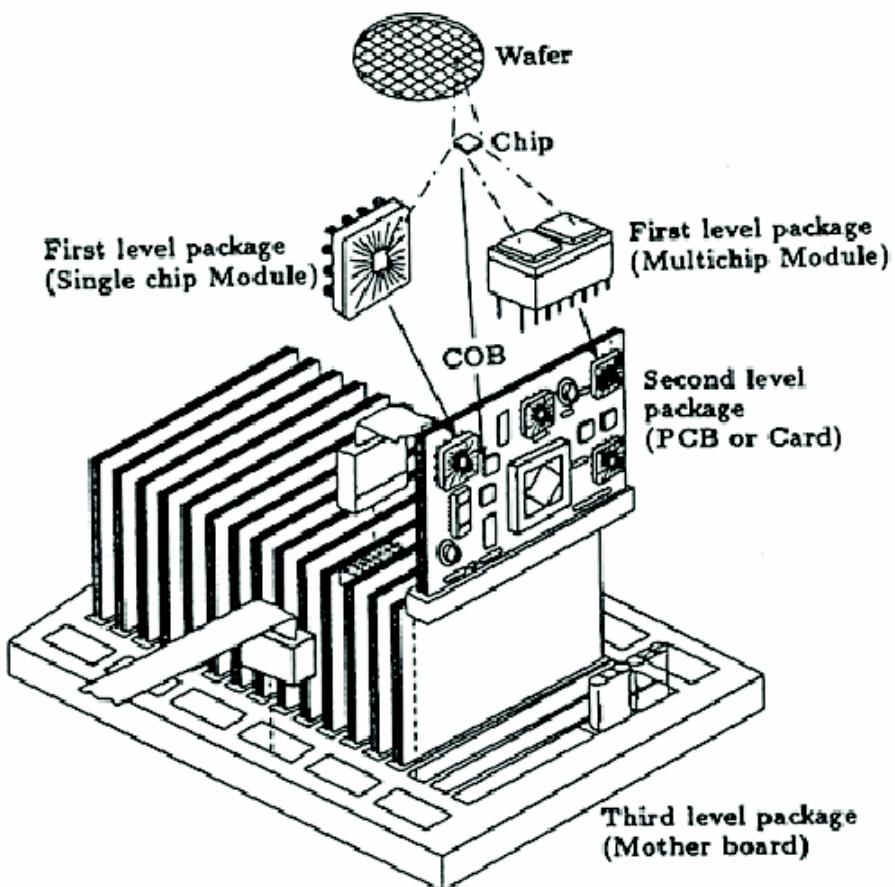

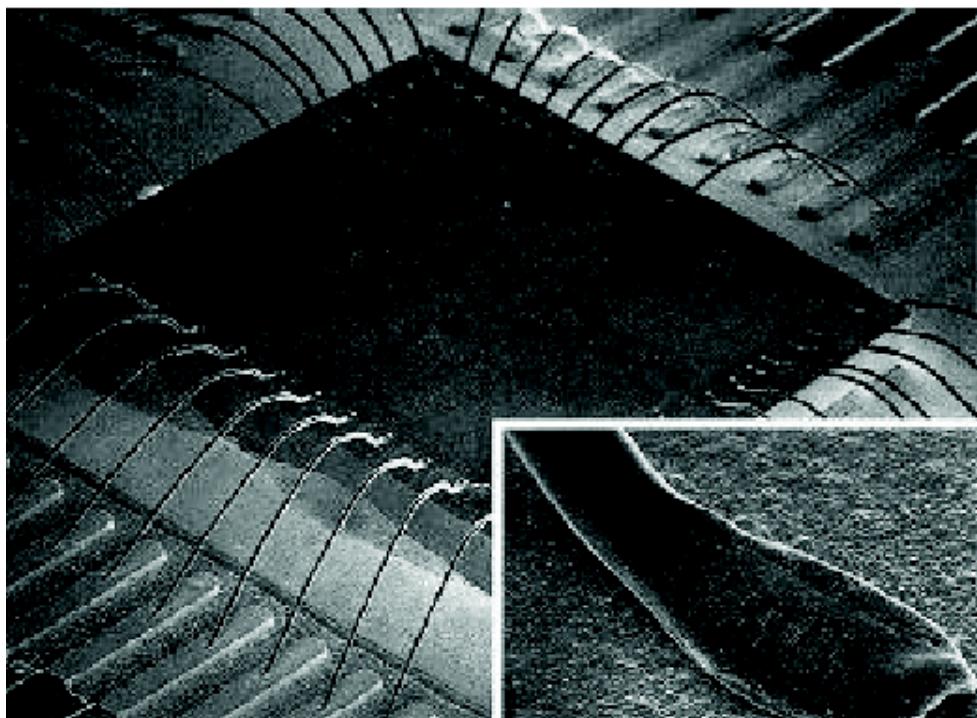

電子構裝第一層次的構裝(chip level packaging)中，晶片與基板間的電路導通方式主要可以分為：打線接合(wire bonding) 圖 1.2、捲帶式自動接合(tape automatic bonding) 圖 1.3 與覆晶接合(flip chip bonding) 圖 1.4。分別簡述如下：

## (1) 打線接合：

打線接合是最早亦是目前應用最廣的技術，此技術首先將晶片固定於

導線架或基板上，再以細金屬線將晶片上與導線架或基板上的鍍墊(pad)相連接。而隨著近年來其他技術的興起，打線接合技術正受到挑戰，但由於打線接合技術之簡易性及便捷性，加上長久以來與之相配合之機具與相關技術皆已十分成熟，因此短期內打線接合技術仍不大會為其他技術所淘汰。

### (2) 捲帶式自動接合：

捲帶式自動接合技術首先於 1960 年代由通用電子(General Electric,GE)提出。捲帶式自動接合即是將晶片與高分子捲帶上的金屬電路相連接。而高分子捲帶之材料則以聚亞醯胺(polyimide)為主，捲帶上之金屬層則以銅箔使用最多。捲帶式自動接合具有厚度薄、接腳間距小且能提供高輸出/入接腳數等優點，適用於需要重量輕、體積小之 IC 產品上。

### (3) 覆晶接合：

覆晶式接合為 IBM 於 1960 年代開發的 C4 (controlled collapse chip connect) 技術。其技術乃於金屬鍍墊上生成鍍錫凸塊(solder bump)，並於基板上生成與鍍錫凸塊相對應之接點，接著將翻轉之鍍錫球對準基板上之接點將之接合。其優點具有最佳構裝效益(packaging efficiency)、最佳電氣特性、最高輸出/入接點密度且能縮小 IC 尺寸，已被看好為未來極具潛力之封裝方式。

但由於覆晶式接合在可靠度上議題上仍有許多有待解決的問題，如熱應力、冶金反應、電遷移、熱遷移等，且隨著鍍錫接點的縮小，IC 功率的增加，電遷移將會是個重要的議題，也是本篇研究所要探討的主題。

## 研究動機

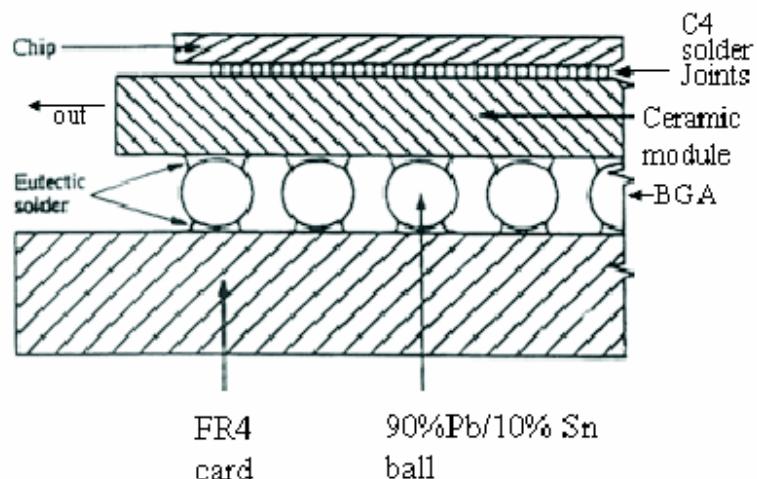

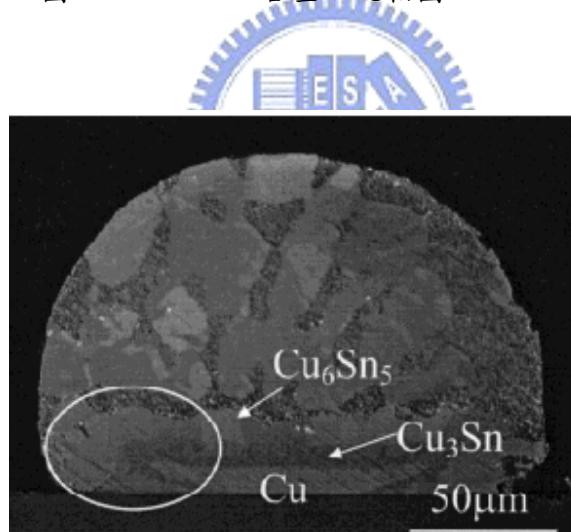

由於在目前大部分的銻料合金與 UBM 的冶金反應中都會生成介金屬化合物(IMCs, intermetallic compounds )  $Cu_6Sn_5$ ，且為了因應消費電子產品微小化與可攜帶性的趨勢，銻錫接點的尺寸勢必隨之縮小，因此電遷移(electromigration)在可靠度的議題上將扮演重要的角色。然而隨著銻錫接點的縮小，IMC 在 bump 中所佔的比例將隨之上升，例如於 copper column UBM 與銻料合金接合後於通電測試的條件下，我們可以發現 IMC 變厚且佔了相當大的比例[ 1 ]，如圖 1.5 所示。且由於 IMC 有較好的抗電遷移性質，因此 IMC 的存在將對 bump 的 lifetime 有重要的影響。

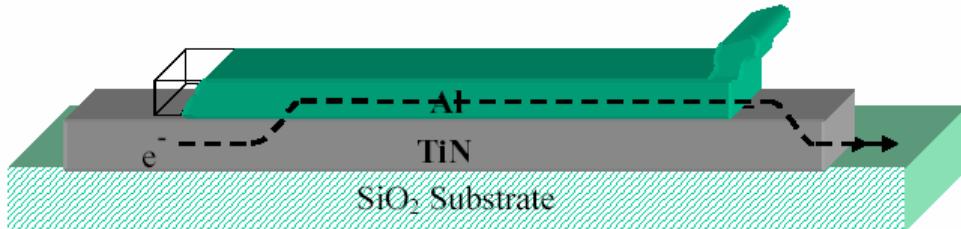

目前已經有許多研究報導銻料合金的電遷移性質，然而卻少有研究專注於 IMC 電遷移的基本特性，這可能是由於 IMC Blech 型式的電遷移測試試片準備困難的關係，由於 IMC 無法由蒸鍍(evaporation)、濺鍍(sputtering)與電鍍(electroplating)等方式來進行沉積，且在 IMC stripe 在數十微米(micrometer)的長度下無法利用迴銻(reflow)的方式製作與厚度的控制上也是個困難點。儘管如此，在此篇研究中，我們將利用 FIB (focus ion beam) 在 IMC 薄膜上精確的製作出各種不同的 stripes 長度，並且利用 AFM(atomic force microscopy)去量測 IMC 薄膜厚度，再於薄膜兩端施加不同的電流密度，經由直接的觀察其受電遷移破壞的情形我們可以得到 IMC 的臨界成積(critical product)、漂移速度(drift velocity)等電遷移參數。

圖 1.1、封裝層級示意圖。

圖 1.2、打線接合(wire bonding) SEM 圖。

圖 1.3、捲帶式自動接合(tape automatic bonding) SEM 圖。

**(a) Chip → Ceramic → polymer module board**

圖 1.4、(a)(b) 覆晶接合( flip chip bonding) 示意圖。

圖 1.5.、Cu column 與 SnPb solder bump 的光學顯微鏡影像。(a)通電前。(b)以  $3.4 \times 10^3 \text{ A/cm}^2$ 、 $100^\circ\text{C}$  通電 1 個月後。(c) 以  $4.7 \times 10^3 \text{ A/cm}^2$ 、 $100^\circ\text{C}$  通電 1 個月後。(d) 以  $1 \times 10^4 \text{ A/cm}^2$ 、 $100^\circ\text{C}$  通電 1 個月後。

## 第 2 章、文獻回顧

### 2.1 電遷移理論

#### 2.1.1 電遷移的通量方程式

電遷移( electromigration )效應是一種當金屬導線在承受高電流密度的情況下，金屬原子擴散而產生質量傳輸的一種現象。這種質量傳輸的現象主要是來自於兩種對立的作用力交互影響金屬原子所造成：第一種是導體在外加電場時，靜電力對帶正電荷的金屬離子所造成的庫倫力(coulomb force)，另一種是所謂的電子風力(electron wind force)，其主要是來自於電子和金屬原子間動量轉換的結果。

在電遷移時原子質量傳輸的情形下，固態金屬原子的擴散通量方程式可以表示為[2]：

$$J = -D \frac{\partial C}{\partial X} + \sum_i CM_i F_i \quad (2.1)$$

上述式子中第一項所表示的是因為化學勢差(chemical potential gradient)的存在而造成的擴散通量，而第二項所代表的是各種促使原子擴散的外加力量。倘若我們只探討純物質的電遷移擴散機制，則第一項化學勢差所造成的通量將可以被忽略。因此只剩下電場對金屬離子的庫倫力和電子和金屬原子間動量轉換的電子風力。如此一來，我們便可以將第二項改寫為[2]：

$$\sum_i CM_i F_i = F_{el} + F_{wd} \quad (2.2)$$

其中電子風力較庫倫力的影響顯著，進而促使金屬原子從導體的陰極端(cathode side)被推向陽極端(anode side)而產生遷移。對於主

在電遷移效應的電子風力我們習慣上將它表示為電場 E 和有效電荷(effective charge)  $Z^*e$  的乘積：

$$F_{wd} = EZ^*e \quad (2.3)$$

其中 e 是基本電荷量， $Z^*$ 為有效電荷數，其值是指受電遷移的作用下遷移的能力的參數。因此對不同種類的金屬而言，將擁有不同的有效電荷數。

將電子風力導入電遷移的原子通量式中，我們可以得到電遷移通量式為[2]：

$$J_{EM} = NmF_{EM} \quad (2.4)$$

其中 N 為原子濃度(atomic concentration)，m 為原子的遷移率(mobility)，而依照愛因斯坦方程式(Einstein equation)我們可以將原子遷移率表示成：

$$m = D/kT \quad (2.5)$$

上式中，D 代表擴散係數(diffusivity)，k 為波茲曼常數(Boltzmann's constant)、T 為絕對溫度(absolute temperature)。因此，電遷移的原子通量方程式可以表示為：

$$J_{EM} = N \frac{D}{kT} Z^*e E = N \frac{D}{kT} Z^* e \rho j \quad (2.6)$$

其中， $\rho$  是電阻係數(resistivity)、j 是電流密度(current density)。

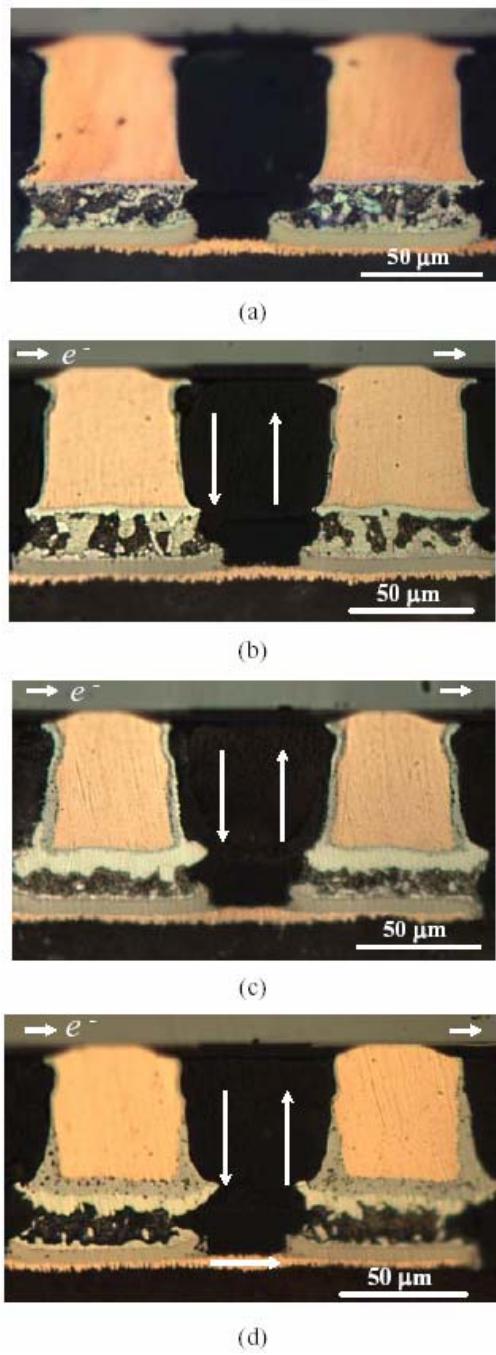

### 2.1.1 電遷移產生的應力

我們可以利用邊緣移動(edge displacement)效應來研究電遷移行為，其中，Blech 是首位導入此實驗方法者[ 3-4 ]。其當時所用的測試結構如圖 2.1 所示。

圖 2.1、在電遷移測試下的 Blech 結構示意圖。

Blech 將許多不同長度的鋁薄膜沉積在具有高電阻係數的材質 TiN 上，於此結構中，由於鋁薄膜導線具有較小的電阻值。因此，當在 TiN 的兩端施以高電流量時，鋁薄膜導線將成為主要的電流路徑而承受高電流密度進而產生電遷移破壞。因此，我們便可觀察到鋁薄膜導線在陰極(cathode)產生消耗(depletion)，且在陽極(anode)產生凸起(hillock)。藉由觀察上述的現象我們可以了解電遷移中質量傳輸的情形。

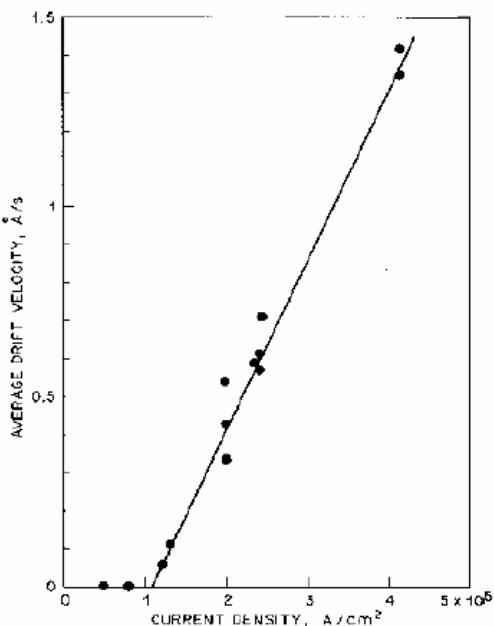

Blech 藉由不同的通電時間，計算因電遷移效應所導致的遷移量，進而求得飄移速度(drift velocity)。圖 2.2 顯示長  $115\mu\text{m}$ 、寬  $25\mu\text{m}$ 、厚  $115\mu\text{m}$  之鋁薄膜導線所呈現的電流密度(current density)與飄移速度(drift velocity)的函數圖形。由圖 2.2 中我們可以觀察到，

鋁薄膜導線的飄移速度與電流密度呈現線性關係，但此直線並無通過原點。此現象代表著，對於一特定長度的鋁薄膜導線而言，

所施加的電流密度(current density)必須

圖 2.2、經  $500^\circ\text{C}$ 、0.5hrs 热處理之鋁薄膜導線，在不同電流密之飄移速度[4]。

大於一特定的臨界值(threshold current density,  $J_{th}$ )電遷移效應才能產生原子的遷移而造成毀壞。此電流密度的臨界值(threshold current density,  $J_{th}$ )將與鋁薄膜導線的長度有關，因此在相同的條件下，一固定的鋁薄膜導線長度將會有一相對應的電流密度臨界值。然而，此現象是由於應力所產生的 backflux 抑制了電遷移效應[5]。當電流流經鋁薄膜導線時陰極端的金屬原子將會擴散到陽極端累積。在這過程中，若有鋁薄膜導線有一曾原生氧化層(native oxide)，將導致薄膜導線內部產生一機械應力。這是因為當空位(vacancy)沿著晶界平衡的狀態下，鋁薄膜導線內部的晶界(grain boundary)仍然是有效的空位(vacancy)來源，儘管此部分的化學勢(chemical potential)小於  $10^{-4}\text{ eV}$ [6]。這表示鋁薄膜導線內部須存在

$\sigma=10^{-4}$  eV/ $\Omega \approx 1$  MPa ( $\Omega=1.66\times 10^{-29} \text{ m}^3$ )。因此當擴散發生時，金屬原子將會累積在陽極端，進而增加晶格(lattice site)數目，如此一來便會造成陽極端壓縮應力(compressive stress)的生成。同理，鋁薄膜之陰極端亦將會生成拉伸應力(tensile stress)。此種應力梯度(stress gradient)的存在將會導致 backflux 的產生。此 backflux 的表示方式可寫成[7]:

$$J_\sigma = C \frac{D}{KT} \frac{\partial}{\partial x} (\mu_a - \mu_v) \quad (2.7)$$

上述的式子中， $\mu_a$  代表的是原子本身的化學勢(chemical potential of atoms)， $\mu_v$  代表的是空位的化學勢(chemical potential of vacancies)。

在熱平衡的條件下，其化學勢(chemical potential)可改寫成[7]:

$$\mu = \mu_a - \mu_v = \mu_0 - \Omega \sigma_n \quad (2.8)$$

上式中， $\Omega$  為原子體積  $\mu_0$  為原子處於無應力晶體中的化勢(chemical potential)、 $\sigma_n$  為在晶界(grain boundary)上的正向應力(normal stress)。結合上述的式子，便可將 backflux 改寫為：

$$J_\sigma = C \frac{D\Omega}{KT} \frac{\partial \sigma_n}{\partial x} \quad (2.9)$$

### 2.1.2 反作用力與臨界乘積

如同上面所提到，對一特定長度的導線而言將有一相對的臨界電流密度，在此臨界電流密度下，電遷移造成的原子通量( $J_{EM}$ )將會等於應力造成的 backflux ( $J_\sigma$ )：

$$J_{EM} = J_\sigma \quad (2.10)$$

若將式子(2.6)和(2.9)帶入方程式(2.10)中，我們便可以得到：

$$eZ^* \rho j = \Omega \frac{\partial \sigma_n}{\partial x} \quad (2.11)$$

上式又可被改寫成

$$(j \cdot l)_{crit} = \frac{\Omega \Delta \sigma_{th}}{eZ^* \rho} \quad (2.12)$$

其中  $\partial \sigma_n / \partial x = \Delta \sigma_{th} / \Delta x$ ，且  $\Delta x =$  薄膜導線的長度(L)、 $\Delta \sigma_{th}$  是在一定溫下，特定材料之薄膜導線之陽極端與陰極端所能承受的最大正向應力(normal stress)差。此方程式(2.12)即所謂的臨界乘積(critical product)，其首先被 Blech[ 4 ]所提出。由實驗得知鋁金屬導線於 225°C 下其臨界乘積(critical product)介於 500[ 8 ]到 2000Amp/cm[ 7 ]之間。

### 2.1.3 電遷移對鋅料的影響

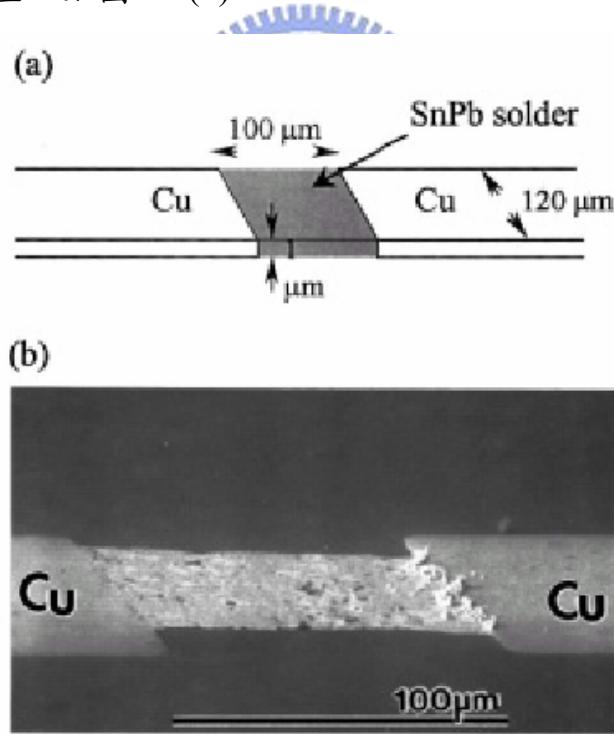

近年來由於積體電路(integrated circuit)的微小化，使得不僅內層導線(interconnect)會面臨到電遷移的問題，覆晶接點亦將會面臨到相同的問題，因此有越來越多的鋅料研究朝向電遷移效應的影響。封裝接點使用之合金鋅料在電遷移(electromigration)效應的作用下所產生的毀壞機制與部分行為與鋁或銅導線類似。例如，C.Y.Liu等人於1999年利用三明治結構對Sn-Pb鋅料合金做電遷移測試發現，Sn-Pb鋅料合金於室溫、電流密度 $1\times 10^5\text{Amp/cm}^2$ 下，通電19天後發現，於鋅料陰極端有孔洞形成，且在陽極端發現到有凸起現象的產生，如圖2.3(b)。

圖2.3、(a) Sn-Pb鋅料合金電遷移實驗之三明治結構圖。(b) Pb鋅料合金於室溫下、電流密度 $1\times 10^5\text{Amp/cm}^2$ 通電19天之SEM圖[9]。

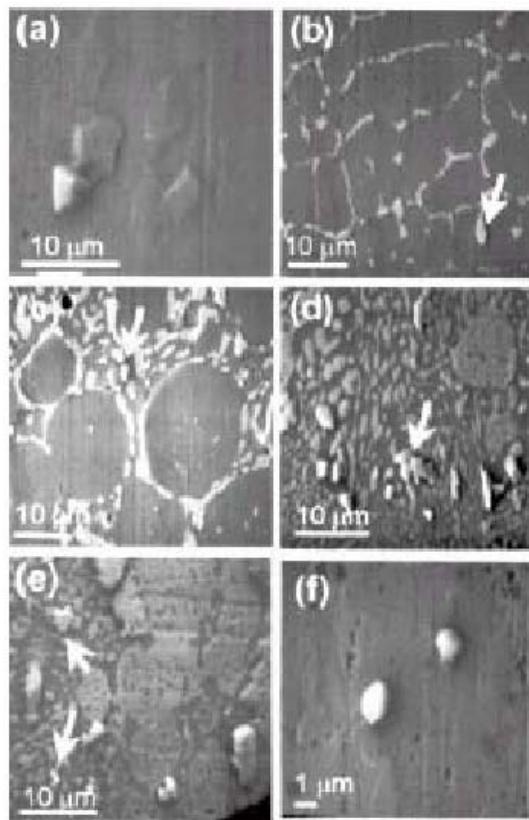

由於構裝接點之銻料組成大都為雙成分以上的合金型態，因此電遷移的擴散機制與鋁或銅為主的內層導線相比將有所差別。圖 2.4 顯示純 Sn、Sn<sub>80</sub>Pb<sub>20</sub>、Sn<sub>70</sub>Pb<sub>30</sub>、Sn<sub>63</sub>Pb<sub>37</sub>、Sn<sub>40</sub>Pb<sub>60</sub>、Sn<sub>5</sub>Pb<sub>95</sub> 六種不同組成之合金，分別於電流密度  $1 \times 10^5 \text{ Amp/cm}^2$  下、通電 40 小時後，表面凸起的 SEM 圖。於 SEM 中發現凸起容易發生在鉛的晶粒(grain)。且當合金的表面為共晶相時，由於此區域提供了較高密度的擴散介面，因此於此處有比較明顯的擴散行為。故於富錫(tin rich)的合金中，容易在共晶相區(eutectic phase region)中

如圖 2.4、不同成分的 Sn-Pb 合金於電流密度  $1 \times 10^5 \text{ Amp/cm}^2$  下、通電 40 小時後表面凸起(hillock)的 SEM 圖：(a) pure Sn ; (b) Sn<sub>80</sub>Pb<sub>20</sub> (c) Sn<sub>70</sub>Pb<sub>30</sub> (d) Sn<sub>63</sub>Pb<sub>37</sub>(e) Sn<sub>40</sub>Pb<sub>60</sub> (f) Sn<sub>5</sub>Pb<sub>95</sub> [ 10 ] 。

發現凸起的產生，如圖 2.4(b)、(c)所示。倘若將圖 2.4 (a)-(f)做比較，我們可以發現於相同條線下進行電遷移測試，富鉛(Lead rich)合金具有較好的抗電遷移性質。也就是說，對 Sn、Pb 為主的雙成分鋅料合金而言，雖然說 Sn 為主要的擴散載子，但決定對電遷移的阻抗能力而言仍然是取決於鋅料的微結構。

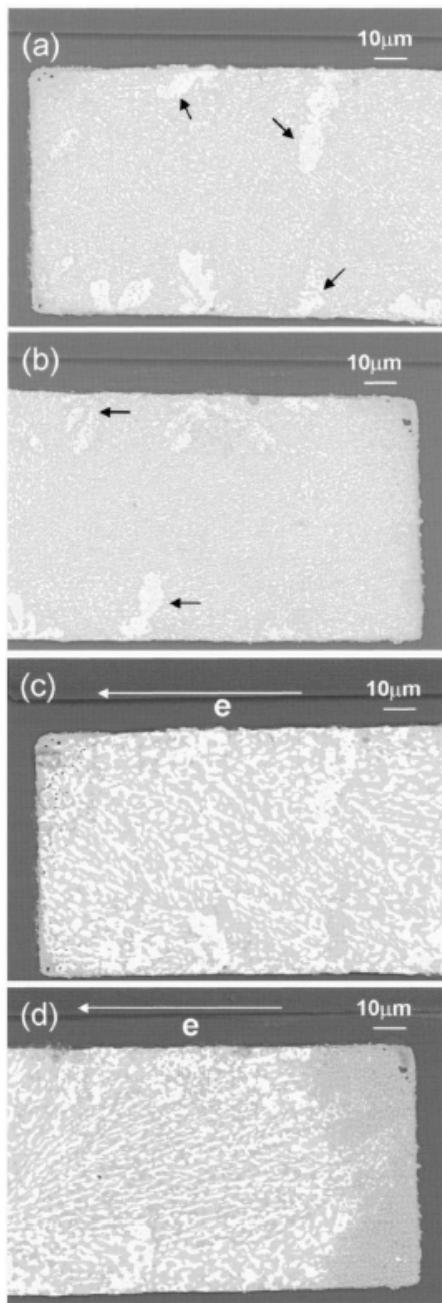

此外，在 Chih Chen 等人利用 Blech 結構進行共晶 SnPb 鋅料的電遷移測試中，亦發現富鉛(lead rich)相將順著電子流方向排列以降低整體的總電阻。如圖 2.5 所示，在電流密度  $1.1 \times 10^5 \text{ Amp/cm}^2$ 、 $100^\circ\text{C}$  的通電條件下，原本位通電前圖 2.5(a)、(b)中細小且散佈的富鉛相將隨著通電時間成長且趨向於排列成平行於電子流方向如圖 2.5(c)、(d)以降低電流路徑的電阻值，且減少富鉛相和富錫相間的電流集中效應(current crowding)。此一現象隨著電流密度增大或通電時間增長將變得更明顯。

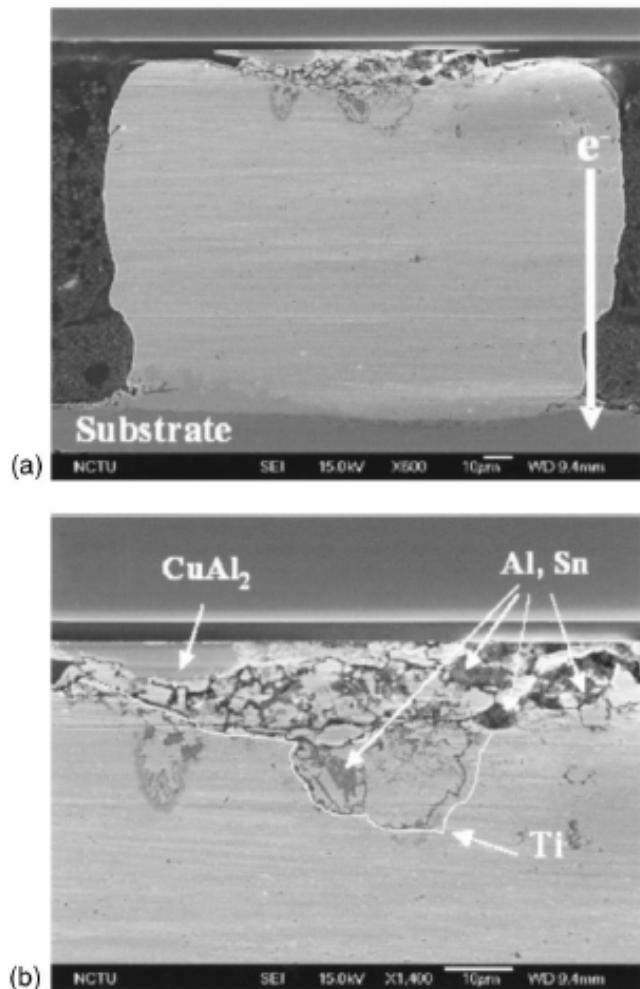

而對無鉛鋅料而言，Chih Chen 等人觀察到在  $1 \times 10^3 \text{ Amp/cm}^2$ 、 $150^\circ\text{C}$  的通電條件下，SnAg<sub>3.5</sub> 鋅錫球在陰極/晶片(chip)端產生破壞，如圖 2.6、(a)所示，其中我們可以看到鋁導線因遭受電子流的衝擊而鑲嵌到鋅錫球中，且和銅 UMB(under bump metallization)形成 CuAl<sub>2</sub> 的介金屬化合物，SnAg<sub>3.5</sub> 鋅錫合金也因為遭受到電子流的衝擊而產生破碎的現象進而造成鋅錫接點的失效，如圖 2.6、(a)所示。

圖 2.5、帶狀共晶 Sn-Pb 錠料在電流密度  $1.1 \times 10^5 \text{ Amp/cm}^2$ 、 $100^\circ\text{C}$  下的 SEM 圖 :(a) 通電前的陽極端 ;(b) 通電前的陰極端 ;(c) 通電 140 小時後的陽極端 ;(d) 通電 140 小時後的陰極端 [ 11 ] 。

圖 2.6、SnAg3.5 錫錫球在電流密度  $1 \times 10^3 \text{ Amp/cm}^2$ 、150°C 通電 218 小時後的 SEM 截面圖：(a)錫錠球的全貌，其電子流向；(b)陰極(cathode)/晶片(chip)端的局部放大圖[ 12 ]。

## 2.2 焦耳熱效應造成的熱遷移

近年來由於高功率元件的微小化，覆晶鋅錫接點的電遷移 (electromigration) 現象吸引了許多的注目。隨著鋅錫接點中的電流密度持續的上昇，電遷移已變成不可避免的議題，然而在通電的過程中，往往產生了焦耳熱效應(joule heating effect)，因此熱遷移(thermomigration, TM)的現象也伴隨著發生。因為大部分的電阻來自於金屬導線，因此其受到較大的焦耳熱效應(joule heating effect)，所以是主要的發熱源。因而造成在鋅錫接點中晶片端(chip side)的溫度將會比基板(substrate)端來的高，其中由於鋅錫接點的微小化，其 bump height 只有微米(micrometer)等級，因此儘管只有少許的溫差也能在接點的縱向上造成 $\sim 10^3 \text{ }^\circ\text{C/cm}$  的溫度梯度(thermal gradient)。

熱遷移的現象首先由Ludwig在1856年提出[13]。其驅動力(driving force)通常可以用此式來表示

$$F_{\text{TM}} = Q^*/N(dT/dx)/T, \quad (2.13)$$

其中  $Q^*$  表示莫耳熱流(molar heat flux), N 為亞佛加厥常數,  $dT/dx$  表示溫度梯度，我們可將 Nernst-Einstein 方程式  $v=D_A F/kT$  代入流量方程式  $J=nvF$ ，其中 n 表示原子濃度( $\text{atomic}/\text{cm}^3$ )，我們可以得到熱遷移造成的原子流為

$$J_{\text{TM}} = \frac{nD_A(Q^*/N)}{kT^2}(dT/dx) \quad (2.14)$$

$D_A$  為主要載子的擴散係數(diffusivity)，k 為 Boltzmann constant。

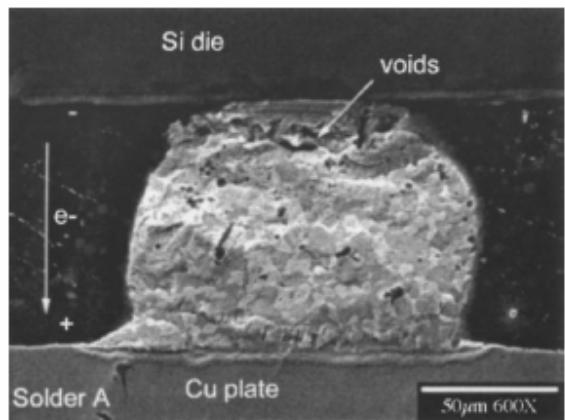

目前有許多研究指出熱遷移發生在銻錫接點，例如 Hua Ye 等人在 2003 發表[ 14 ]，在 Sn- Pb 銻錫合金中施加  $1.3 \times 10^4 \text{ A/cm}^2$  的電流密度 16 小時後發現空孔不僅形成於銻錫球 A 的陰極端如圖 2.7(a) 所示，在相鄰的銻錫球 B 發現空孔也形成於陽極端，如圖 2.7(b) 所示。此一結果單用電遷移是無法解釋的，因此 Hua Ye 等人相信因為溫度梯度的存在而在晶片往 Cu plate 的方向存在熱遷移，所以便可合理的解釋在錫球 A 的陰極端因為電遷移與熱遷移的加成而產生了嚴重的孔洞(void)生成，在錫球 B 的陽極端(anode side)因為熱遷移被電遷移抑制，所以生成的孔洞(void)較不劇烈。

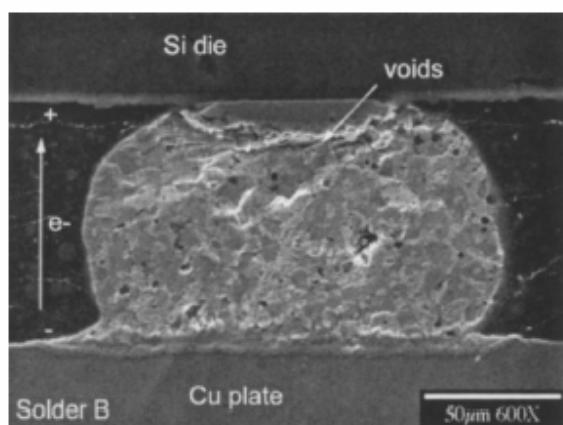

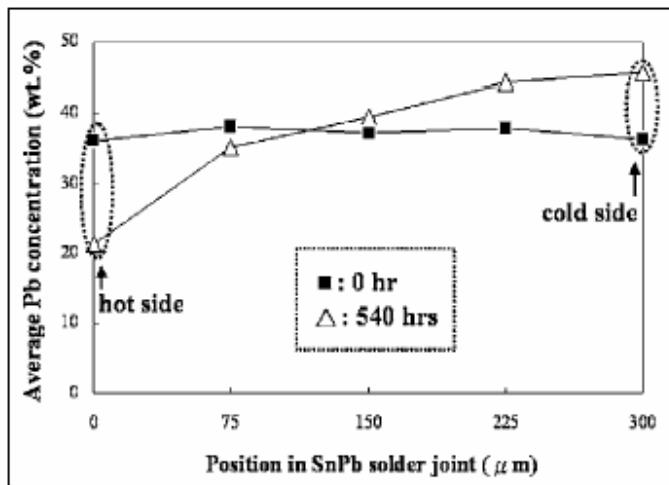

C. Y. Liu 等人在 2006 年利用穩定熱源加熱共晶 Sn-Pb 銻料，另一端用循環冷卻水在銻料內建立出一溫度梯度(thermogradient)[ 15 ]。其利用熱電偶(thermocouple)量測出熱端與冷端的溫度分別為  $111.2^\circ\text{C}$  與  $80.9^\circ\text{C}$  其溫差為  $30.3^\circ\text{C}$ ，將其除以銻料的間距將可得到  $1010^\circ\text{C}/\text{cm}$  的溫度梯度(thermogradient)。在沒有施加電流僅有此溫度梯度的條件下，利用觀察銻料拋光(polish)後在不同 annealing 時間下的表面形貌變化，我們可以發現拋光過程中人為造成的 marks “A”和“B”隨著 annealing 時間往熱端(hot end)移動如圖 2.8 所示，這代表著質量傳輸(mass transportation)的方向為沿著溫度梯度從熱端(hot end)向冷端(cold end)。此外，富鉛(lead rich)相，圖 2.8 中的 mark “C”，隨著時間消耗，因此相信在共晶 Sn-Pb 中，溫度  $80-110^\circ\text{C}$  的熱遷移中 Pb 是主要的擴散載子。如果再利用 EDS 沿著銻料的截面分析，我們可以發現在 TM 測試前的 Pb 成分分佈相當均勻，約 37wt%，然而在 TM 測試後 Pb 成分將

降冷端(cold end)的方向增加，如圖 2.9 所示。因此我們可以確定 Pb 較 Sn 在 TM 的過程中受到驅動。

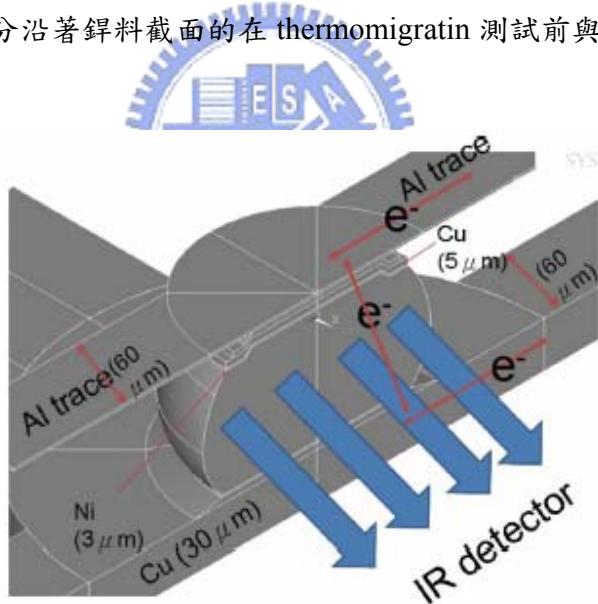

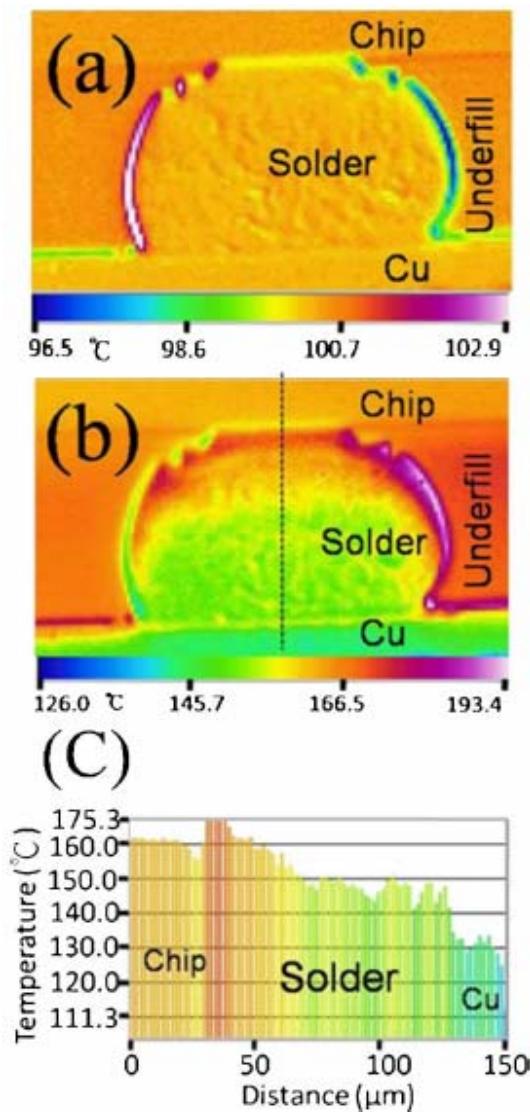

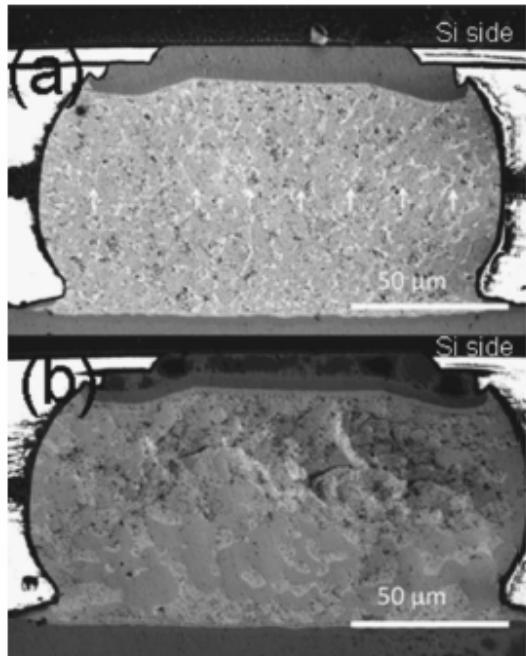

雖然在許多實驗中都有熱遷移的現象，但是仍沒有確切的實驗指出在真正的銻錫接點中確實存在著如此大的溫度梯度(thermal gradient)而造成熱遷移(thermomigration)。因此 Chih Chen 等人[16]在 2007 年發表利用交流電施加於銻錫球上，由於交流電的關係銻錫球並不會遭受電遷移，但卻仍然有焦耳熱效應(joule heating effect)，因此仍須考慮熱遷移。當施加 0.55A 頻率 45Hz 的交流電時，將會在銻錫此實驗的銻錫球中造成  $9.2 \times 10^4 \text{ A/cm}^2$  的電流密度。再利用紅外線感測儀如圖 2.10 的方式直接測出銻錫球各部份的溫度分佈，將可得到如圖 2.11(a)(b)通電前後的分佈情形，由圖 2.11(c)我們可以發現在此通電條件下有  $16^\circ\text{C}$  的溫差存在，再將其除以 bump height 可以得到高達  $2143^\circ\text{C}/\text{cm}$  的溫度梯度存在於銻錫球的晶片端與基板端。在 0.55A、 $100^\circ\text{C}$  通電 108h 之後在晶片端部分的銻料有往遷移的現象，此外也存在著相分離(phase segregation)的現象，其中富鉛相往冷端的基板端移動如圖 2.12 所示。在整各銻錫球中平均溫度約  $155^\circ\text{C}$ ，所以 Pb 是主要的擴散載子。因此較多 Pb 原子遷移到冷端的基板端，而較少的 Sn 原子遷移到熱端的晶片端因而造成了在靠近晶片端的銻料部份有消耗的現象。

圖 2.7(a)、鋅錫球 A 施加  $1.3 \times 10^4 \text{ A/cm}^2$  的電流密度 16 小時後的 SEM 圖。

圖 2.7(b)、鋅錫球 B 施加  $1.3 \times 10^4 \text{ A/cm}^2$  的電流密度 16 小時後的 SEM 圖。

圖 2.8、在不同 annealing times 下鋸料表面形貌的 SEM 圖。

圖 2.9、Pb 成分沿著鋅料截面的在 thermomigratin 測試前與測試後的分佈。

圖 2.10、IR 紅外線儀偵測 bump 的示意圖。

圖 2.11、(a)通電前 bump 的溫度分佈圖。(b)通電後 bump 的溫度分佈圖。

(c)沿著(b)圖中虛線方向的溫度分佈。

圖 2.12、(a)通電前的背向散射 SEM 圖。(b)施加  $0.55\text{A}$  的交流電  $100^\circ\text{C}$ 、 $108\text{h}$  後的背向散射 SEM 圖。

## 2. 3 Sn-Cu 的介面反應

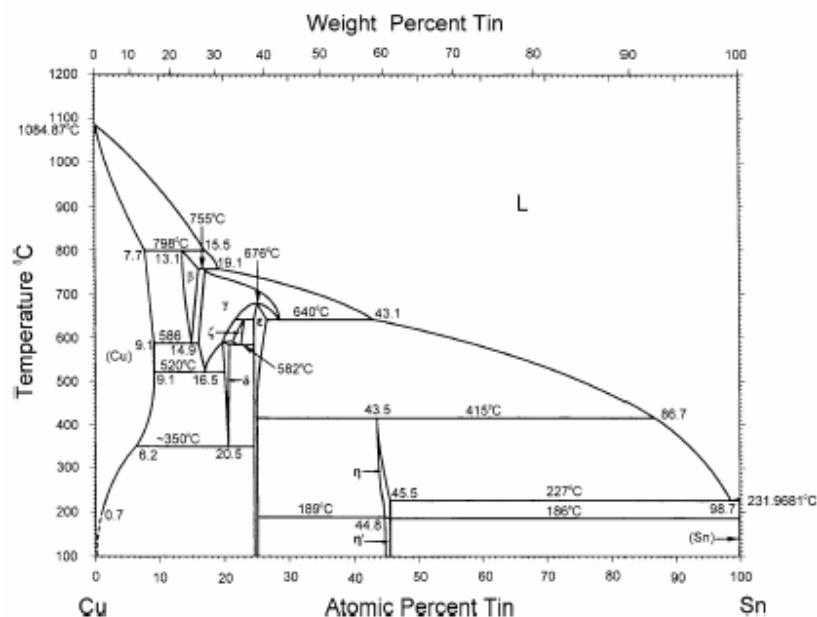

在二元合金系統下的 Sn-Cu 有七種介金屬相存在，分別為  $\alpha$ -Cu、 $\beta$ -Cu<sub>17</sub>Sn<sub>3</sub>、 $\gamma$ - Cu<sub>4</sub>Sn、 $\delta$ - Cu<sub>41</sub>Sn<sub>11</sub>、 $\varepsilon$ - Cu<sub>3</sub>Sn、 $\zeta$ -Cu<sub>10</sub>Sn<sub>3</sub>、 $\eta$ - Cu<sub>6</sub>Sn<sub>5</sub>，但就熱力學平衡來看，在室溫下僅有  $\varepsilon$ - Cu<sub>3</sub>Sn 與  $\eta$ - Cu<sub>6</sub>Sn<sub>5</sub> 為穩定存在的平衡相，如圖 2.13 所示。其中僅  $\varepsilon$ - Cu<sub>3</sub>Sn 與  $\eta$ -Cu<sub>6</sub>Sn<sub>5</sub> 組成範圍狹小，大約只有 1~2%的溶解度，趨近於線性化合物。但 Cu 對於 Sn 的溶解度約 0.01at%，同時於 99.3 at%的 Sn 會與 Cu 發生共晶反應。基於 Sn/Cu 在電子封裝上的廣泛使用，Sn/Cu 間的擴散與介面反應已有許多文獻[ 17-23 ] 。

Z.Meij,A.J.Sunwoo 等，在 20~220°C 下以 Sn/Cu 擴散偶來進行分析 Cu<sub>3</sub>Sn 與 Cu<sub>6</sub>Sn<sub>5</sub> 兩相的生成與擴散係數 [17] 。在研究中指出 Cu<sub>6</sub>Sn<sub>5</sub> 該項具有較高的擴散係數，因此在介面生成的相裡面 Cu<sub>6</sub>Sn<sub>5</sub> 為主要支配的成長相。但當反應溫度持續增加時，Cu<sub>3</sub>Sn 所佔的比例會在生成相裡增加。同時於 220°C 時，對 Cu<sub>6</sub>Sn<sub>5</sub> 相成長的主要擴散載子圍 Sn 。

而在 Tu 等人對於 Sn/Cu 薄膜結構的研究中[ 18 ]，發現在室溫下反應會有 Cu<sub>6</sub>Sn<sub>5</sub> 存在於 Sn/Cu 界面處，同時反應溫度在 115~150°C 的時候，在 Sn/Cu 界面處會先有 Cu<sub>6</sub>Sn<sub>5</sub> 的生成，才會在 Cu<sub>6</sub>Sn<sub>5</sub>/Cu 處生成 Cu<sub>3</sub>Sn。將其 Cu<sub>3</sub>Sn/Cu 的反應偶改置於 640°C 的環境下反應 20mins，再緩慢冷卻回室溫，可發現 Cu<sub>6</sub>Sn<sub>5</sub> 相的成長與時間呈線性；而由於 Cu<sub>3</sub>Sn 相的生成會導致 Cu<sub>6</sub>Sn<sub>5</sub> 的消耗

$(\text{Cu}_6\text{Sn}_5 \rightarrow 2\text{Cu}_3\text{Sn} + 3\text{Sn})$ ，其中  $\text{Cu}_6\text{Sn}_5$  相的消耗速率會與時間成拋物線關係。而在以鎢標記線的實驗裡面發現，在  $\text{Cu}_6\text{Sn}_5$  相的成長是以 Cu 為主要的擴散載子。

S. W. Chen, C. M. Chen 等人[19]將 Sn/Cu 的界面反應進行通電的與未通電的測試，在  $200^\circ\text{C}$ 。實驗指出在 Sn/Cu 的界面系統， $200^\circ\text{C}$  時，不管是否有通電，界面生成的相都生成  $\text{Cu}_3\text{Sn}$  與  $\text{Cu}_6\text{Sn}_5$  兩組，同時 Sn/Cu 界面並沒有因電遷移而發生明顯的影響。

從純錫與純銅的熔點分別是  $232^\circ\text{C}$  與  $1084^\circ\text{C}$  來看，當溫度高過  $232^\circ\text{C}$  時，此時界面反應是以液固形式存在。A. Hayashi, C. R. Kao 等人[20]與 S. Bader, W. Gust 等人[21]的實驗中，都在 Sn/Cu 的界面於  $240^\circ\text{C}$  時發現  $\text{Cu}_3\text{Sn}$  與  $\text{Cu}_6\text{Sn}_5$  相的存在，且於反應發生初期  $\text{Cu}_6\text{Sn}_5$  的成長速率較快，此時的生成厚度與反應時間關係也不符合拋物線，但是對於  $\text{Cu}_3\text{Sn}$  的成長厚度對應時間的部份，仍符合拋物線。而相似的結果也曾於 Kao 等人在 Cu 的飽和 Sn 溶液與純 Cu 的液固界面反應時，由於並未明顯溶解，所以結果與固態的 Sn 與純 Cu 的固態反應結果相似，介金屬相均以層狀存在且都為擴散控制；但液態的純 Sn 與純 Cu 反應中，液固界面因濃度插到製快速發生 Cu 溶入 Sn 中，造成生成相不會遵守拋物線，同時不規則的  $\text{Cu}_6\text{Sn}_5$  相產生。

至於在更高溫度的情況下，Su 等人[22]，在  $300^\circ\text{C}$  時的 Sn/Cu 反應中，發現界面有  $\text{Cu}_3\text{Sn}$  與  $\text{Cu}_6\text{Sn}_5$  相的生成。同時觀察發現，此時的 Sn/ $\text{Cu}_6\text{Sn}_5$  端的界面並非平整，而是  $\text{Cu}_6\text{Sn}_5$  為扇貝狀

(scallop)的形態存在;至於 Cu<sub>6</sub>Sn<sub>5</sub>/Cu<sub>3</sub>Sn 與 Cu<sub>3</sub>Sn/Cu 等界面均為平整層狀分布。Su 等人[ 23 ]提出出現該情況的理論，是由於 Cu<sub>6</sub>Sn<sub>5</sub> 相是產生在液固界面處，因液體有流動能力，且固態 Cu 溶入液態 Sn 的過程很顯著發生，造成 Sn/ Cu<sub>6</sub>Sn<sub>5</sub> 界面的不平整，生成相厚度不會遵守拋物線。其它界面部份，如 Cu<sub>6</sub>Sn<sub>5</sub>/Cu<sub>3</sub>Sn 與 Cu<sub>3</sub>Sn/Cu 等界面，由於屬於固/固界面的成長，所以維持界面平整層狀。此外 Su 等人[22]發現當反應發生在 450°C 時，Sn/Cu 界面不會有 Cu<sub>6</sub>Sn<sub>5</sub> 的生成，而是以 Cu<sub>4</sub>Sn 與 Cu<sub>3</sub>Sn 相的存在。

T. Y. Lee, W. J. Choi 等人發表在 JMR2002. [ 23 ]提出分別以共晶錫鉛、無鉛錫在 Cu UBM 接合後，於 125、150、170°C 下進行固態熱時效。從迴錫(reflow)的過程中，發現對於 e-SnPb 與 Sn-3.5Ag 其 Cu<sub>6</sub>Sn<sub>5</sub> 介金屬化合物形狀為 scallop-type 的結構，而 Sn-0.7Cu 與 Sn-3.8Ag-0.7Cu 的 scallop 狀的 Cu<sub>6</sub>Sn<sub>5</sub> 為多面狀。透過熱時效處理，其 IMC 界面處的形態會轉變成層狀(layered-type)，其中包括 Cu<sub>6</sub>Sn<sub>5</sub> 與 Cu<sub>3</sub>Sn 兩種。且其厚度變化可以發現 Cu<sub>3</sub>Sn 會成長到與 Cu<sub>6</sub>Sn<sub>5</sub> 一般厚度如圖 2.14 所示。

圖 2.13、Sn-Cu 合金二元相圖。

圖 2.14、共晶錫鉛經 170°C 热時效 1500 小時。

## 第 3 章、實驗方法與步驟

### 3.1 試片製備

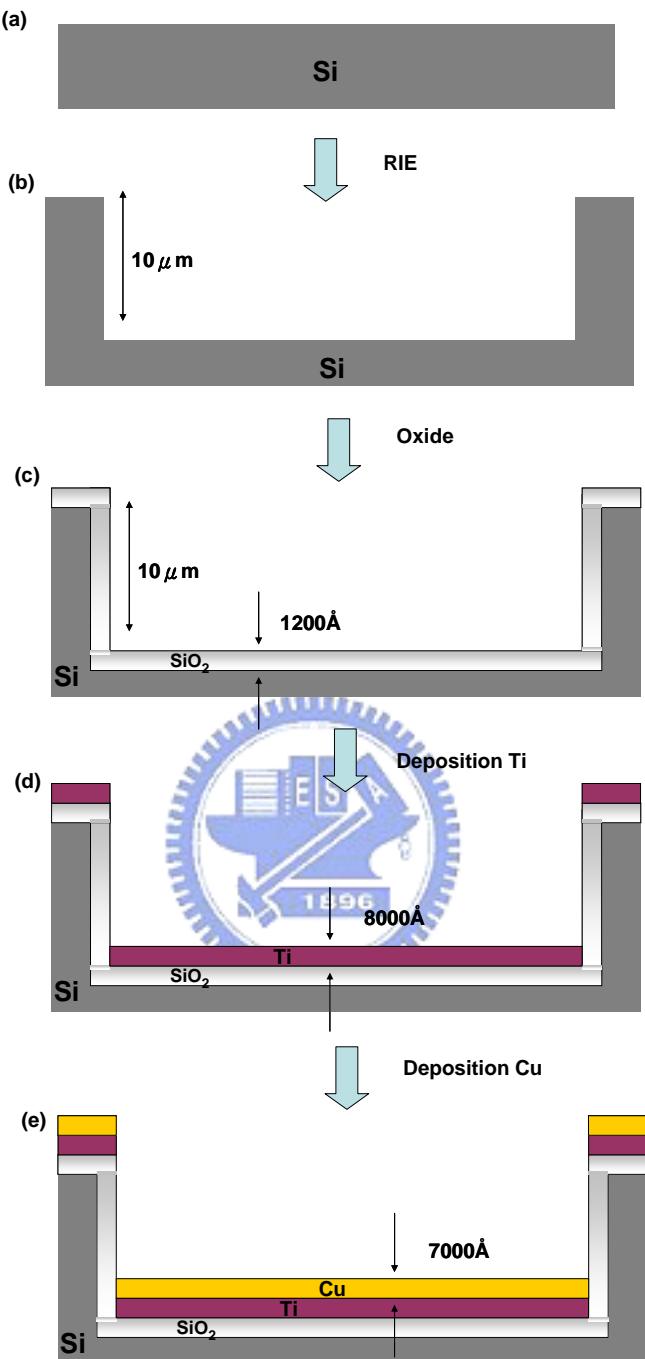

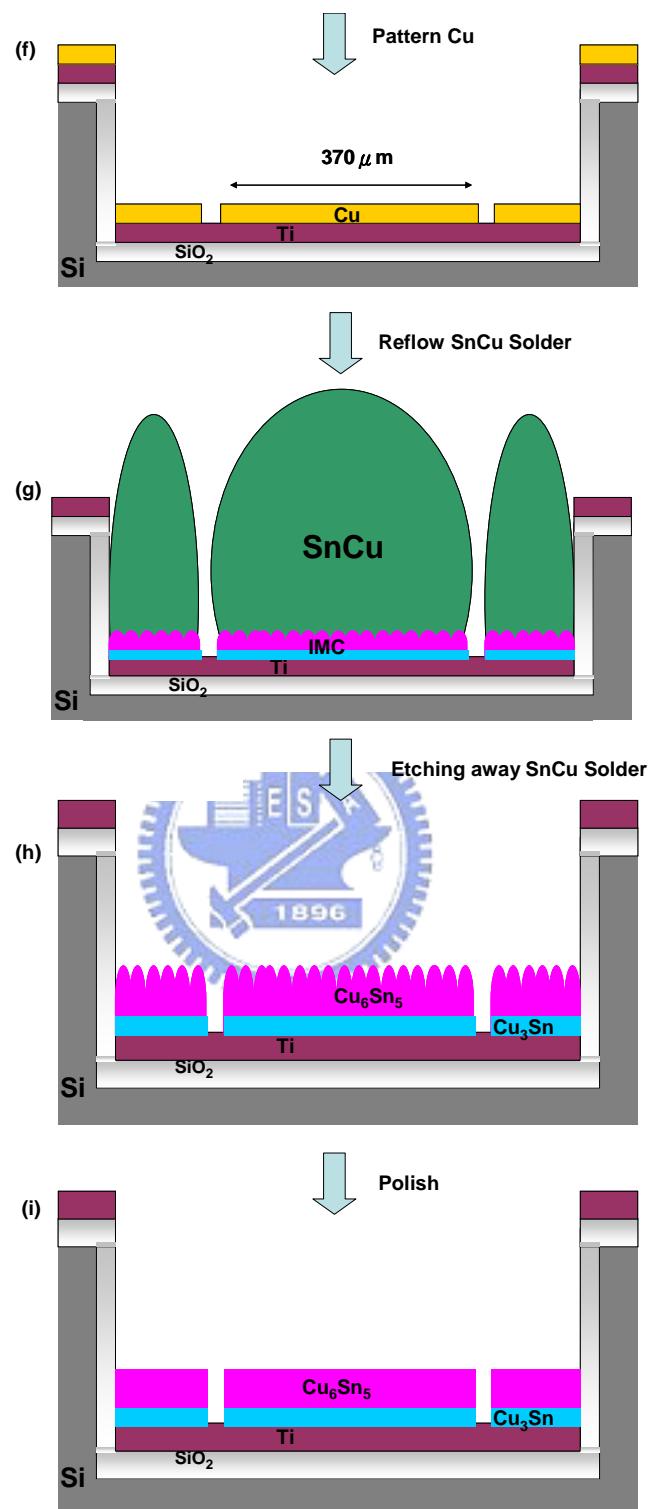

- a. 基板的準備：此實驗中所用到的基板是 n-type 的四吋(100)晶圓。

- b. 第 1 次黃光微影：首先我們利用第一道光罩來定義 stripe 的凹槽。首先將 AZ5214 光阻旋轉塗佈在試片上，接著在 100°C 軟烤(soft-baked)一分鐘然後曝光。利用 FDH5 顯影劑將曝光後的光阻去除，接著將試片在 120°C 硬烤(hard-baked)七分鐘。

- c. 砂晶片的乾蝕刻：我們利用 inductively coupled plasma-reactive ion etching(ICP-RIE)技術來乾蝕刻砂晶片。利用 α-stepper 與原子力顯微鏡(AFM)來量測凹槽的深度為 10μm。

- d. 沉積 SiO<sub>2</sub> 與金屬：為了防止漏電流，我們在砂晶片上利用溼式氧化的方式成長一層厚度為 1200 Å 的絕緣氧化層，然後再利用電子槍蒸鍍的方式依序沉積上 8000Å 的 Ti 與 7000Å 的 Cu。

- e. 第 2 次黃光微影：我們利用第二道光罩來定義 Cu 薄膜的形狀，使其能與銻錫合金潤濕(wetting)。

- f. 銅層的蝕刻：我們利用 1:200 的 FeCl<sub>3</sub>+D.I. water 的溶液來去除銅薄膜不要的部分。

- g. 銻錫合金的迴銻(reflow)與時效(aging)熱處理：利用加熱板將晶片加熱到 250°C 時將 SnCu<sub>0.7</sub> 銻料迴銻(reflow)四秒，由於銻料只會與銅潤濕(wetting)，所以我們可以製備出定義的長條狀的 Blech 結構，之後再將試片放到 150°C 的烘箱時效 600 分鐘將迴銻(reflow)剩餘的銅消耗完，且使 scallop-type 的 Cu<sub>6</sub>Sn<sub>5</sub> 平坦化。

h. 去除  $\text{SnCu}_{0.7}$  錠料:利用  $\text{HNO}_3$ 、 $\text{CH}_3\text{COOH}$ 、甘油分別為 3:2:4 的混合溶液只與  $\text{SnCu}_{0.7}$  錠料反應而不消耗  $\text{Cu}_6\text{Sn}_5$  的特性，將不要的  $\text{SnCu}_{0.7}$  錠料去除只留下  $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$ 。

- i. 抛光 IMC:將剩餘的 scallop-type 的  $\text{Cu}_6\text{Sn}_5$  抛光至平整。

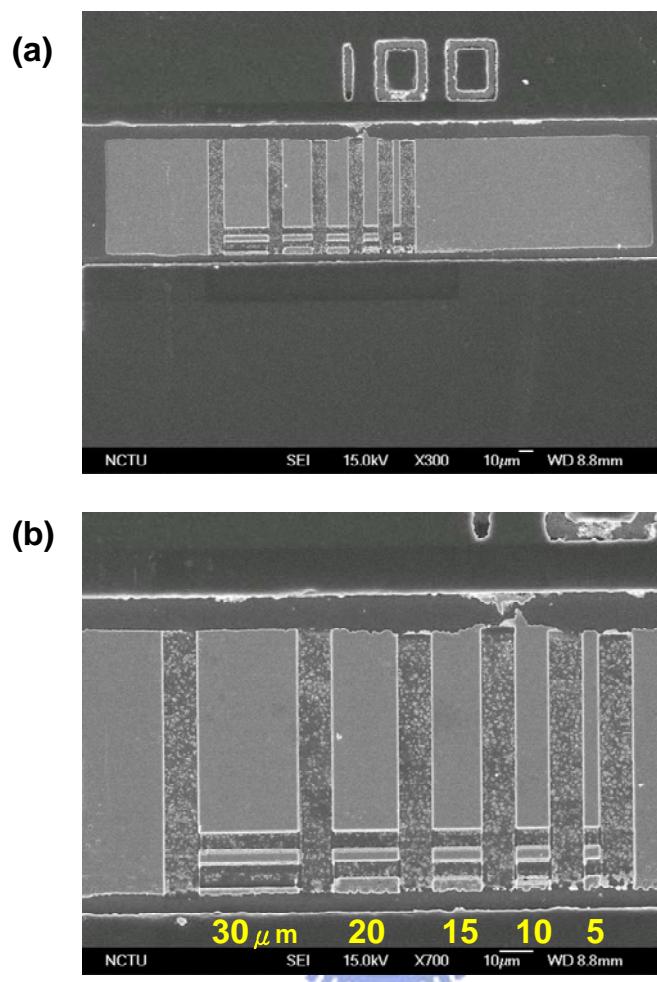

- j. 利用 FIB(focus ion beam)定義出圖形:將拋光平整的 IMC 薄膜利用 FIB 蝕刻出不同長度的 strip。試片製備的流程圖如圖 3.1、圖 3.2 所示。

圖 3.1、試片製備流程。

圖 3.1、試片製備流程。

(j)

圖 3.2、利用 FIB 蝕刻出不同長度的 stripe。

### 3.2 實驗方法

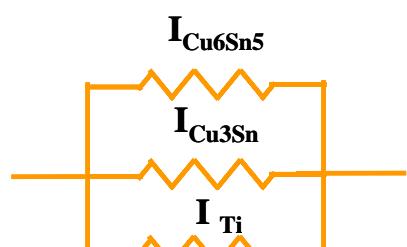

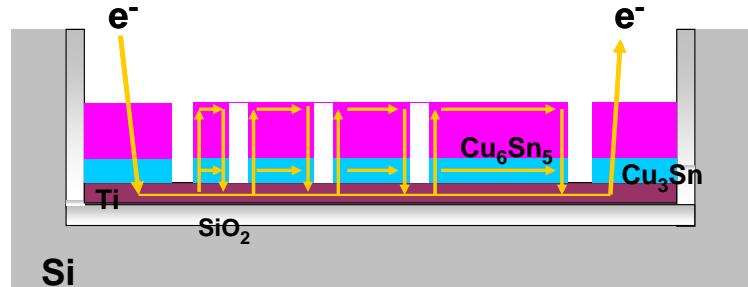

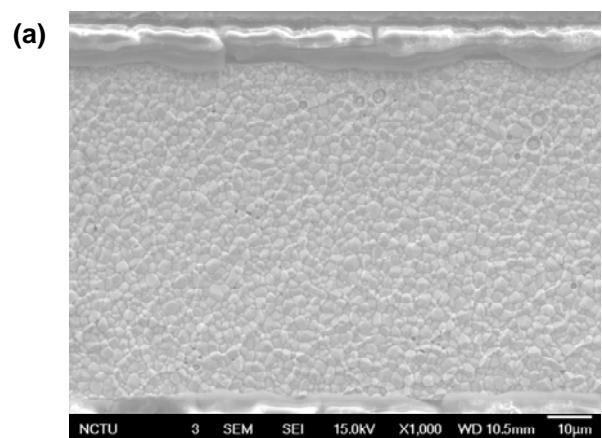

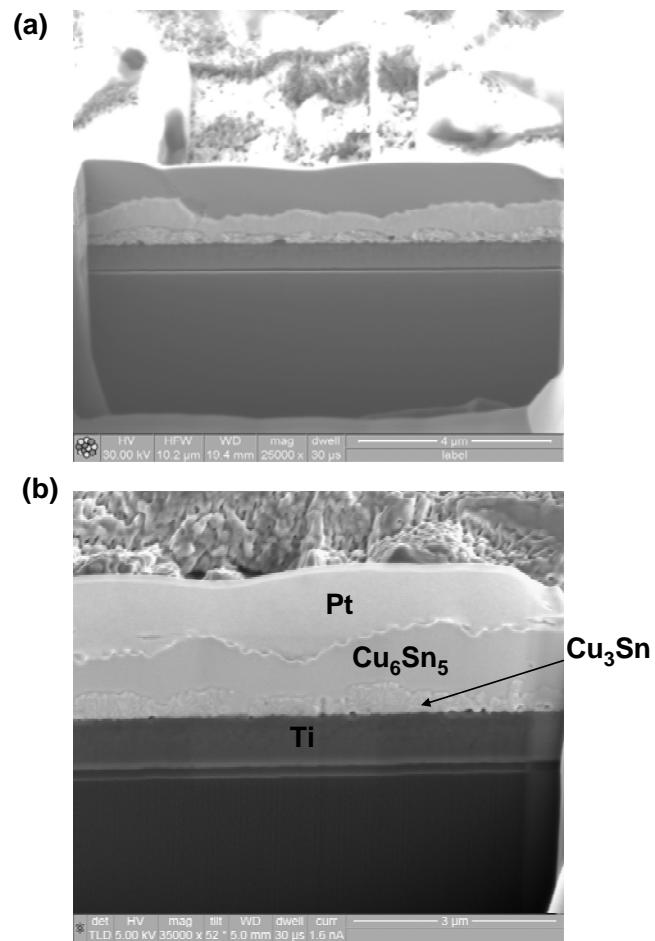

由於在相同的製程條件下，介金屬化合物  $\text{Cu}_3\text{Sn}$  的成長厚度將維持一固定值，經由我們利用 FIB 分析試片截面確定其平均厚度為  $0.37 \mu\text{m}$ 。而介金屬化合物  $\text{Cu}_6\text{Sn}_5$  的厚度我們可以利用 AFM 量測拋光後整各 IMCs (intermetallic compounds) 薄膜的厚度再減去  $\text{Cu}_3\text{Sn}$  的厚度。由於 IMC 薄膜拋光後的厚度會隨著拋光的過程而變，並非為一固定的厚度，所以每片試片都須經過 AFM 的量測來計算  $\text{Cu}_6\text{Sn}_5$  的厚度。而各層薄膜中的有效電流密度我們可以根據  $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  與 Ti 各層的厚度與其電阻率(resistivity)利用並聯電路的方式來求得，如圖 3.3 所示。各材料的電阻率(resistivity)如表一所示。因此，我們可以在通電前預先知道各層的電流密度再施加所需的電流。最後我們將已用 FIB 劃好各長度分別為  $5 \mu\text{m}$ 、 $10 \mu\text{m}$ 、 $15 \mu\text{m}$ 、 $20 \mu\text{m}$ 、 $30 \mu\text{m}$  的 stripes 的試片放到加熱板(hotplate)上加熱到所需的溫度，再將探針施加於試片的兩各 Pad。由於利並聯電路的方式，我們可以經由計算得知不同長度 stripe 中的  $\text{Cu}_6\text{Sn}_5$  相將承受相同的電流密度，同理  $\text{Cu}_3\text{Sn}$  相也是如此。我們所使用的電流源為 Agilent 6614c。於通電測試後再利用 SEM(scanning electron microscopy)、EDX(energy dispersive X-ray detector)、TEM(transmission electron microscopy)、OM(optical microscopy)來觀察試片的破壞情形。

圖 3.3、電流分流示意圖。

| Material                        | Resistivity( $\mu \Omega\text{-cm}$ ) |

|---------------------------------|---------------------------------------|

| Cu <sub>6</sub> Sn <sub>5</sub> | 17.5                                  |

| Cu <sub>3</sub> Sn              | 8.93                                  |

| Ti                              | 42                                    |

表一、各材料的電阻率。

## 第 4 章、結果與討論

### 4.1 試片的微結構分析

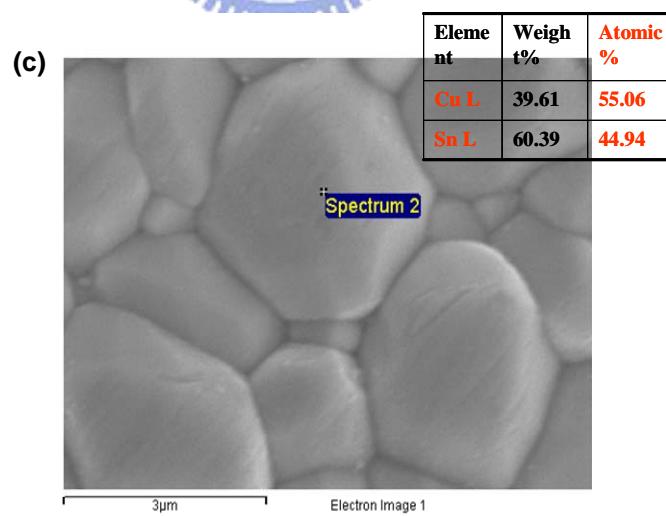

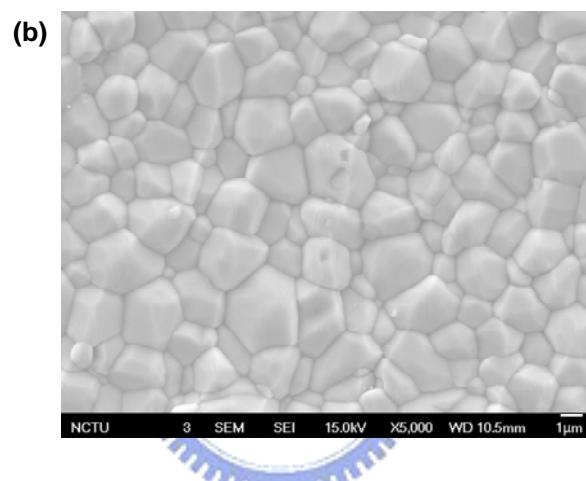

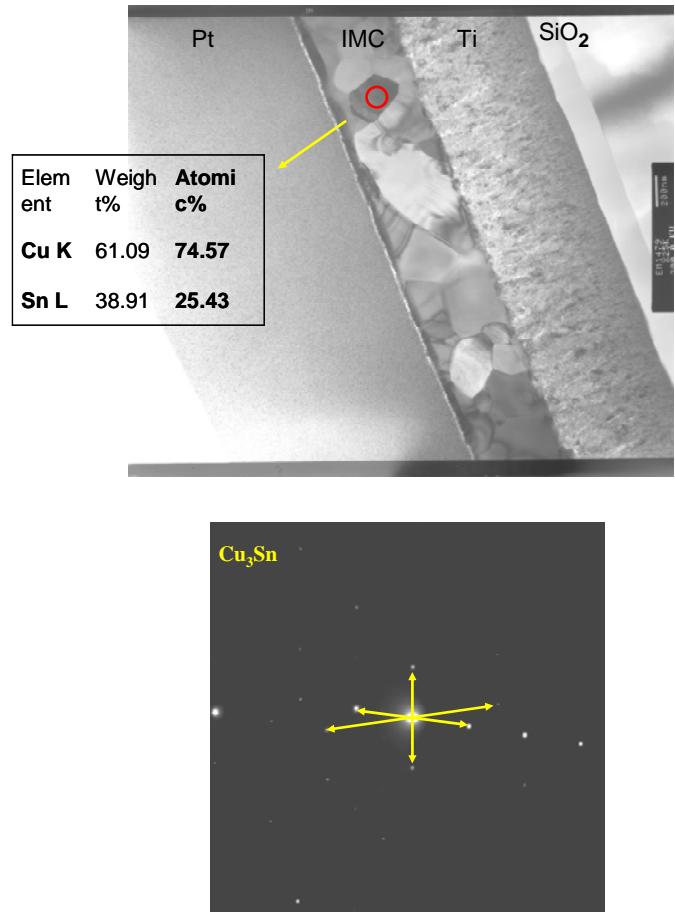

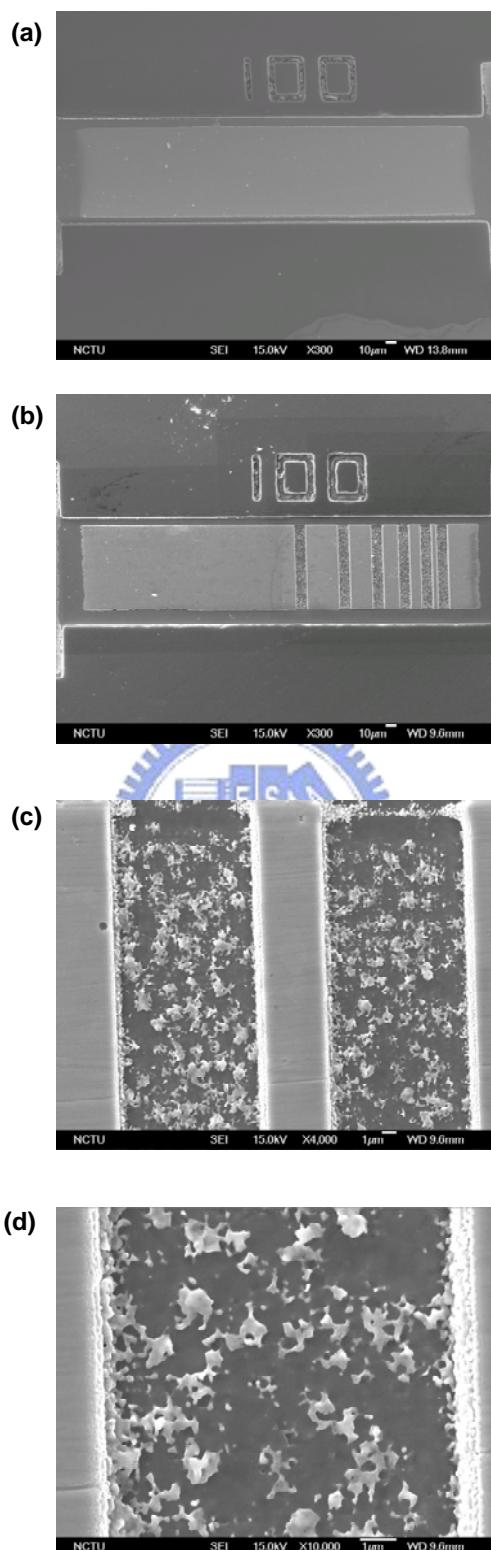

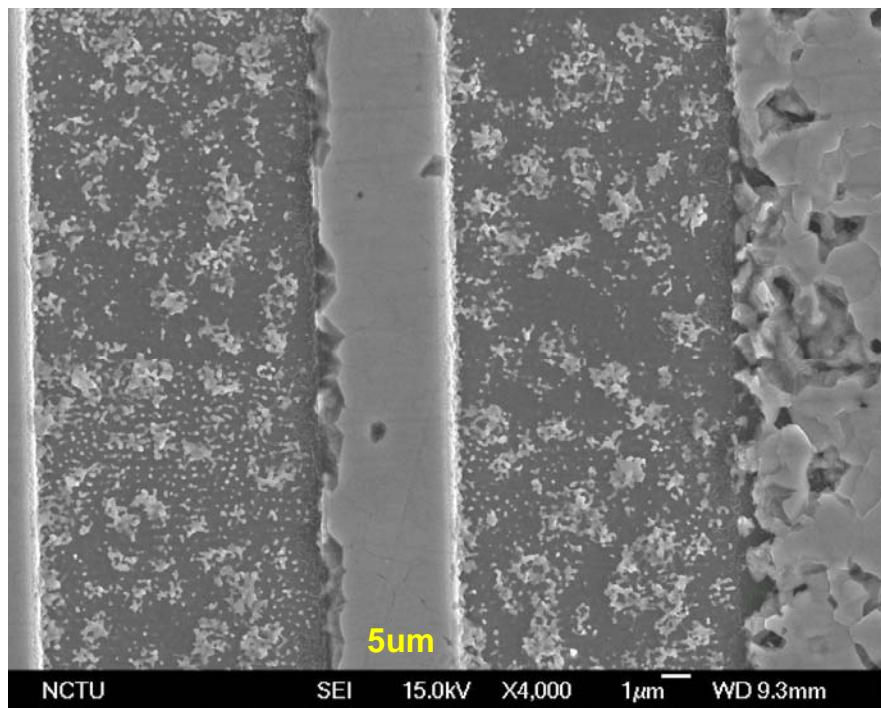

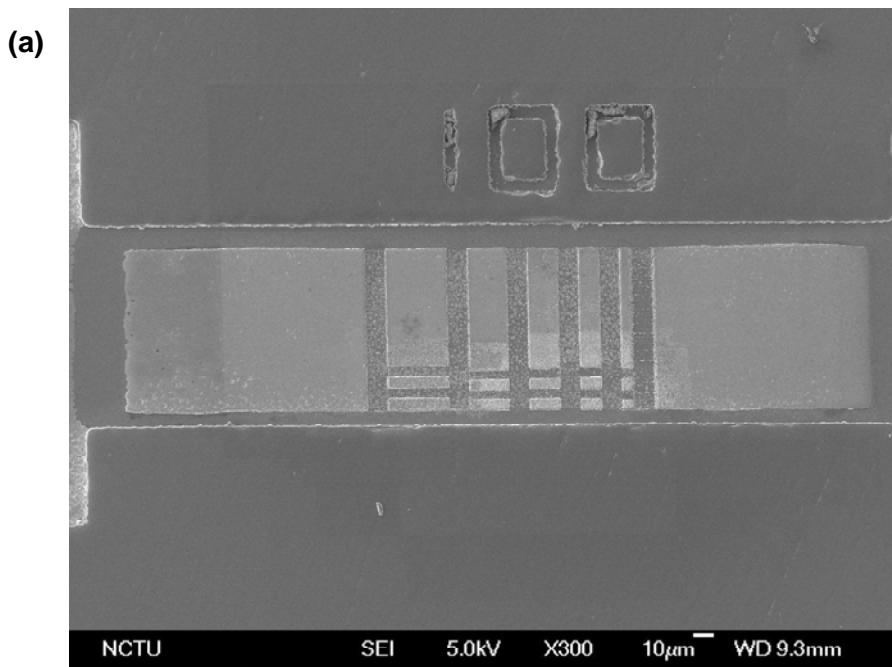

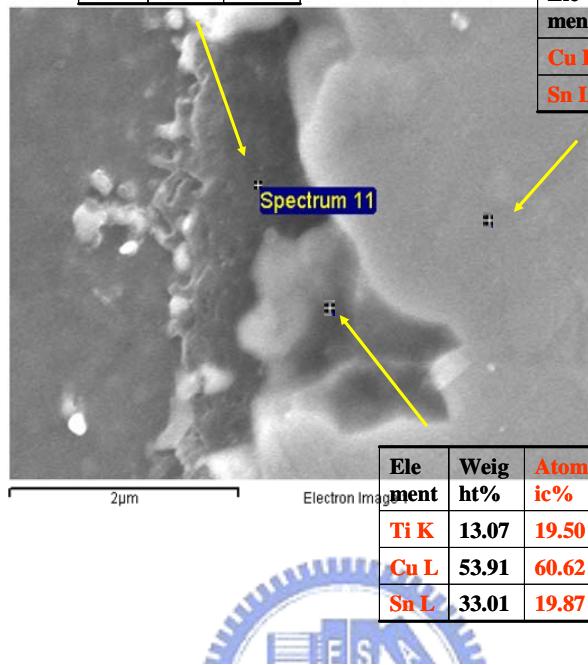

在試片經過第三章所介紹的製作流程後，為了確定 IMCs(intermetallic compounds)薄膜確實由  $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$  所組成，我們進行了以下的分析。當我們將 reflow(迴鋸)後不要的  $\text{SnCu}_{0.7}$  solder 利用酸性溶液蝕刻掉，我們可以發現其表面的形貌為扇貝狀 (scallop type) 晶粒分佈如同圖 4.1、(a)(b)所示，進一步利用 EDX 分析確認其成分為 Cu、Sn 6 比 5 左右的組成如圖 4.1(c)所示，因此確認其為介金屬化合物  $\text{Cu}_6\text{Sn}_5$ 。之後，我們再利用 FIB(focus ion beam) 將試片作縱向的截面分析，我們可以看到其截面如圖 4.2、(a)(b)所示的層狀分佈。首先，在最上層的部份是 Pt，其作用在於 FIB 蝕刻的過程保護試片本身的結構不被離子束所破壞，是後來鍍上去的並非試片本身的結構。第二層為利用 EDX 鑑定出來的  $\text{Cu}_6\text{Sn}_5$ ，而第三層預估將會是  $\text{Cu}_3\text{Sn}$ ，稍後將有 TEM 對其做成分分析，而最後一層為 Ti 層。其中我們對  $\text{Cu}_3\text{Sn}$  layer 做厚度量測，發現其平均厚度為  $0.37\mu\text{m}$ ，由於試片的製程保持固定，所以每片試片中的  $\text{Cu}_3\text{Sn}$  layer 厚度我們均視為  $0.37\mu\text{m}$ 。為了進一步分析在  $\text{Cu}_6\text{Sn}_5$  與 Ti 層之間是否生成  $\text{Cu}_3\text{Sn}$  layer，我們將試片作 TEM 分析。如圖 4.3 所示，在 IMC 薄膜中靠近 Ti 界面的部分我們選擇一顆晶粒來做 EDX 與擇區繞射分析，發現其 Cu、Sn 比例幾乎為 3:1 且經由繞射圖比對，確定其為  $\text{Cu}_3\text{Sn}$  相，因此我們確定 IMC 薄膜為  $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$  所組成。且由於  $7000\text{\AA}$  的 Cu 薄膜在 reflow 與後來  $150^\circ\text{C}$  的 aging 中

已消耗完，所以我們在 TEM 中並沒有看到有殘餘的 Cu 如圖 4.3，就算有剩下也將會在通電的過程中被消耗掉而不影響電流的路徑。

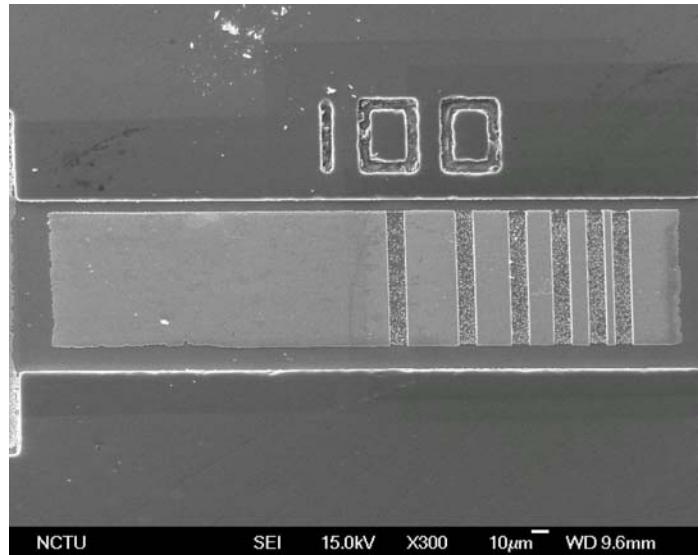

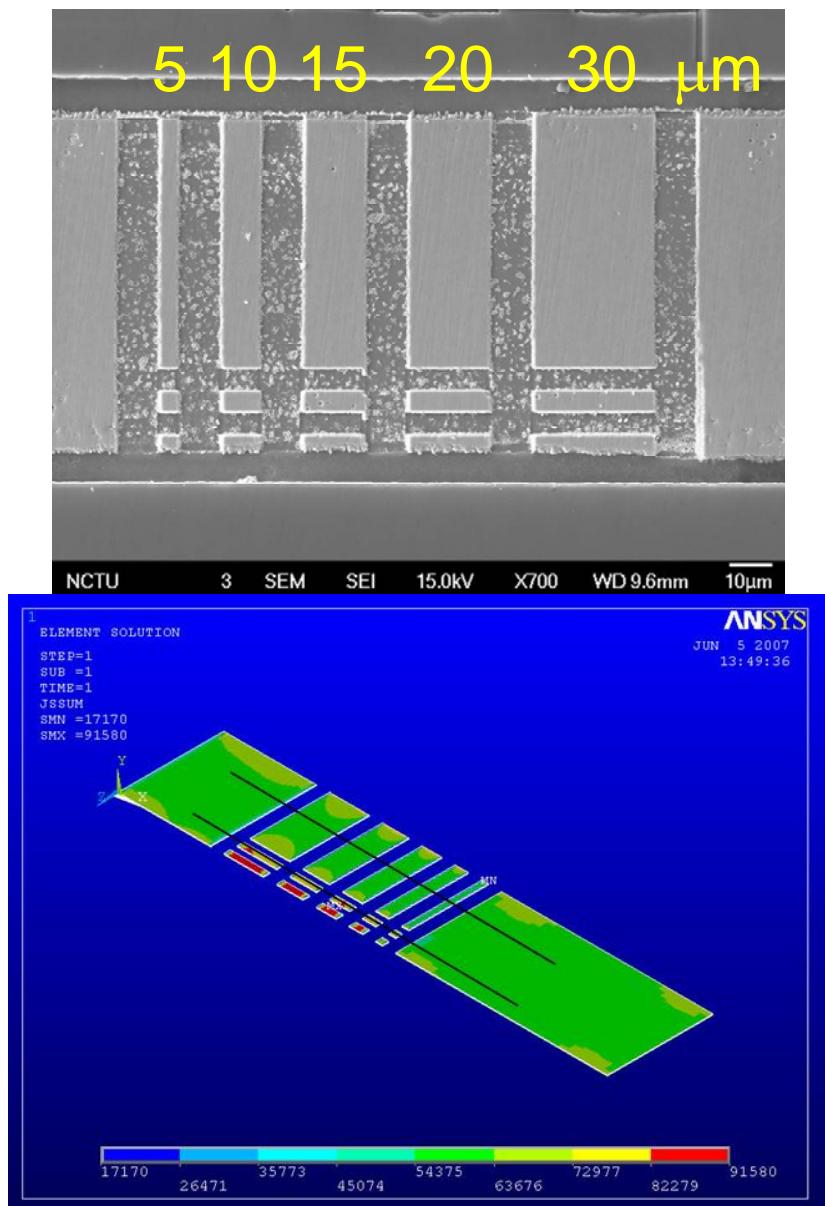

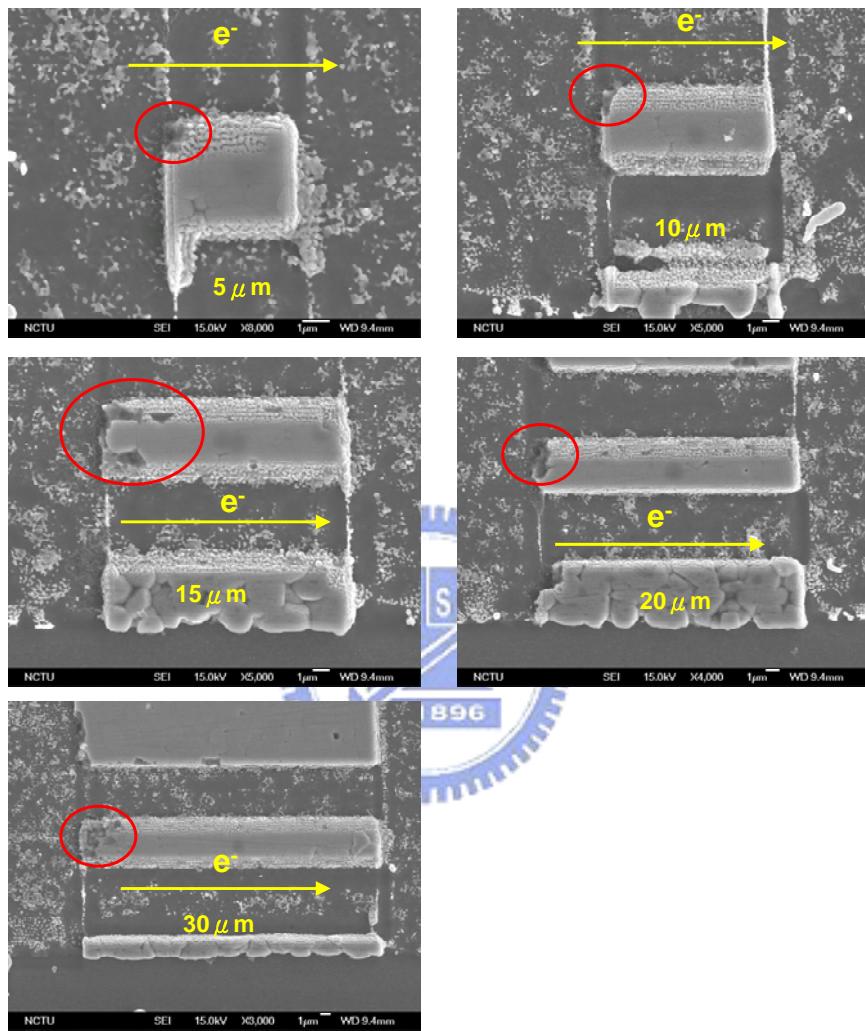

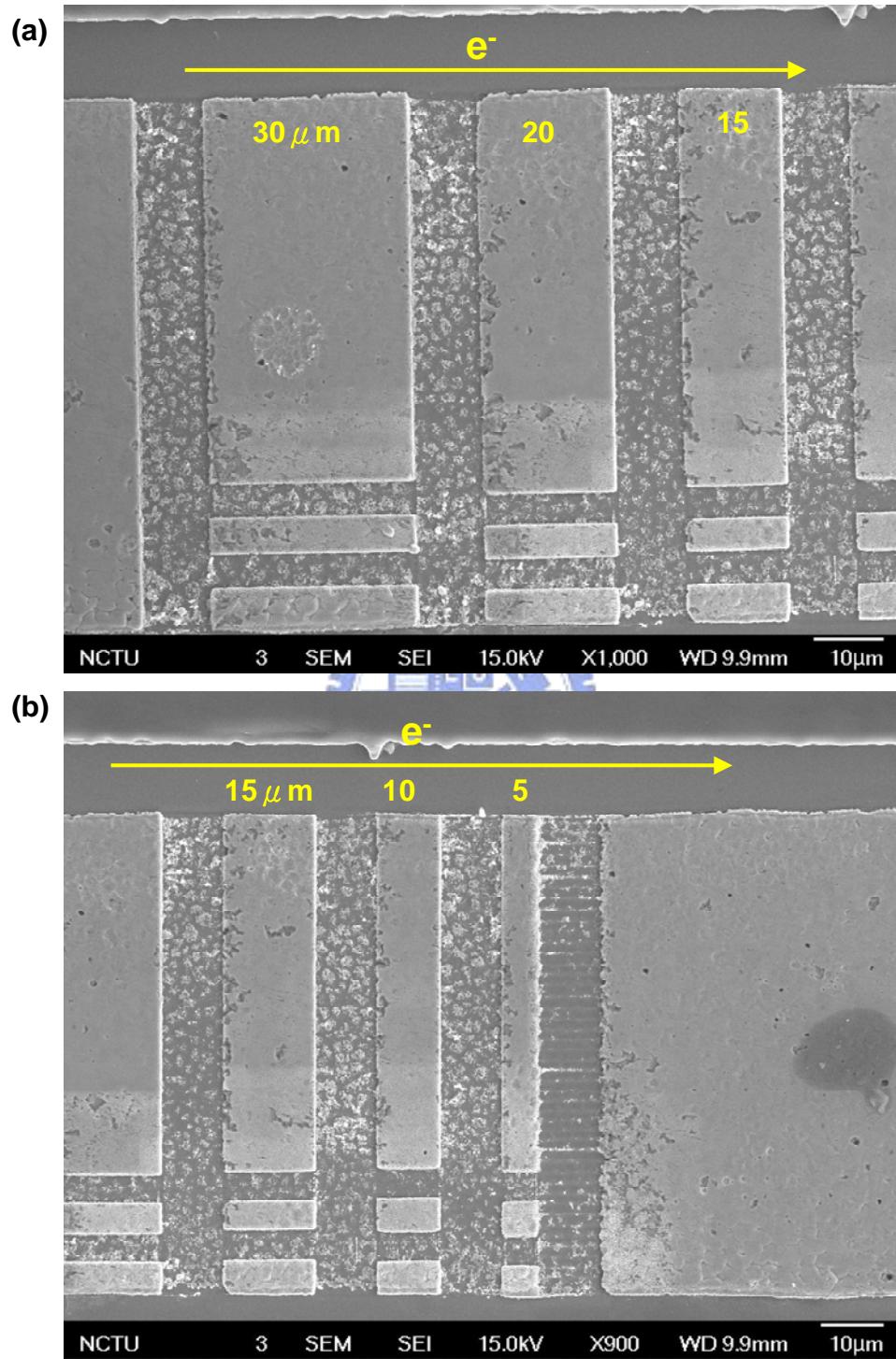

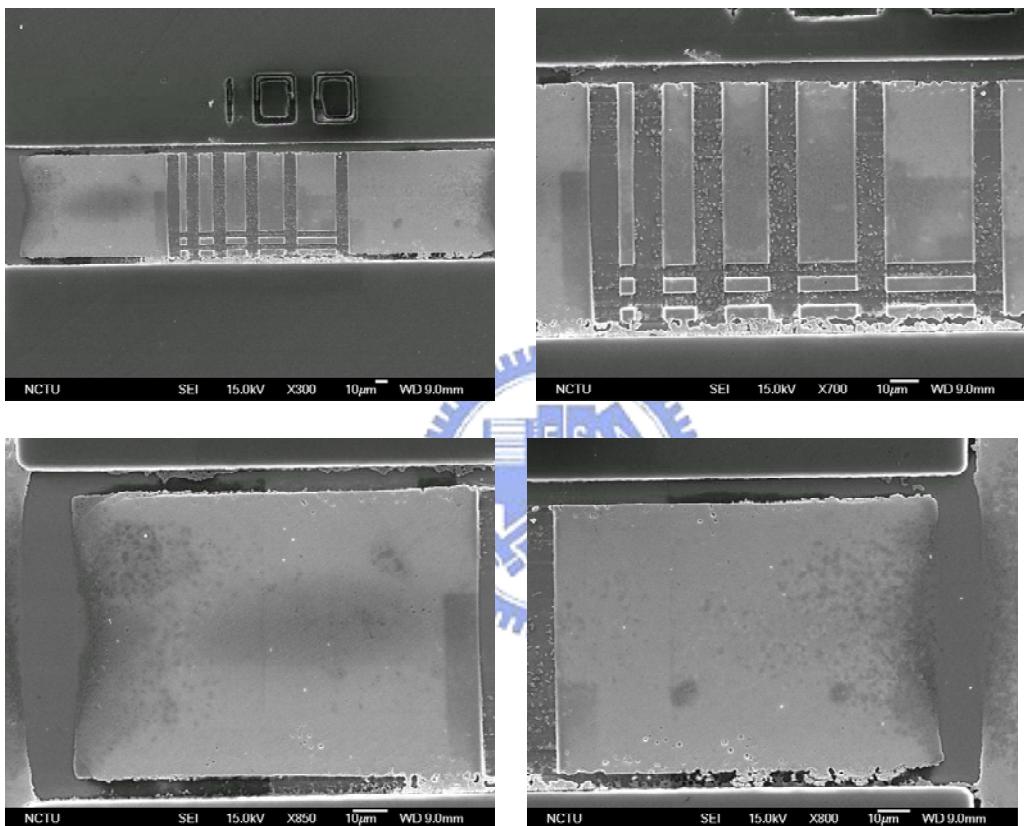

於 FIB pattern 試片圖形的部份，我們可以看到如圖 4.4 所示。於 IMC 薄膜上，利用 FIB 切出不同長度的 stripes 如圖 4.4、(b)所示，由左至右扣除兩端剩餘的 IMC 薄膜不計共有五條 stripes，其長度分別為  $5\mu\text{m}$ 、 $10\mu\text{m}$ 、 $15\mu\text{m}$ 、 $20\mu\text{m}$ 、 $30\mu\text{m}$ 。從圖 4.4、(d)我們可以觀察到，於 IMC stripes 間有 FIB 蝕刻剩下的 IMC island，由於其為不連續狀散佈，所以並不會導通電流。且其尺寸小於可發生電遷移(eletromigration)的臨界長度(critical length)，所以其並不會在電遷移性質的測試上有顯著的影響[22]。

圖 4.1、(a)(b) 蝕刻掉  $\text{SnCu}_{0.7}$  solder 後，試片表面形貌的 SEM 圖。

(c)利用 EDX 進行成分分析，確認為  $\text{Cu}_6\text{Sn}_5$ 。

圖 4.2、(a)試片經由 FIB 所切出的縱向截面 SEM 影像。

(b)為(a)的局部放大圖。

圖 4.3、試片的 TEM 分析與擇區繞射。

圖 4.4、(a)試片拋光後的 IMC 薄膜。(b)(c)利用 FIB 切出不同長度的 stripes。

(c)stripe 間剩餘的 IMC islands。

## 4.2 焦耳熱效應

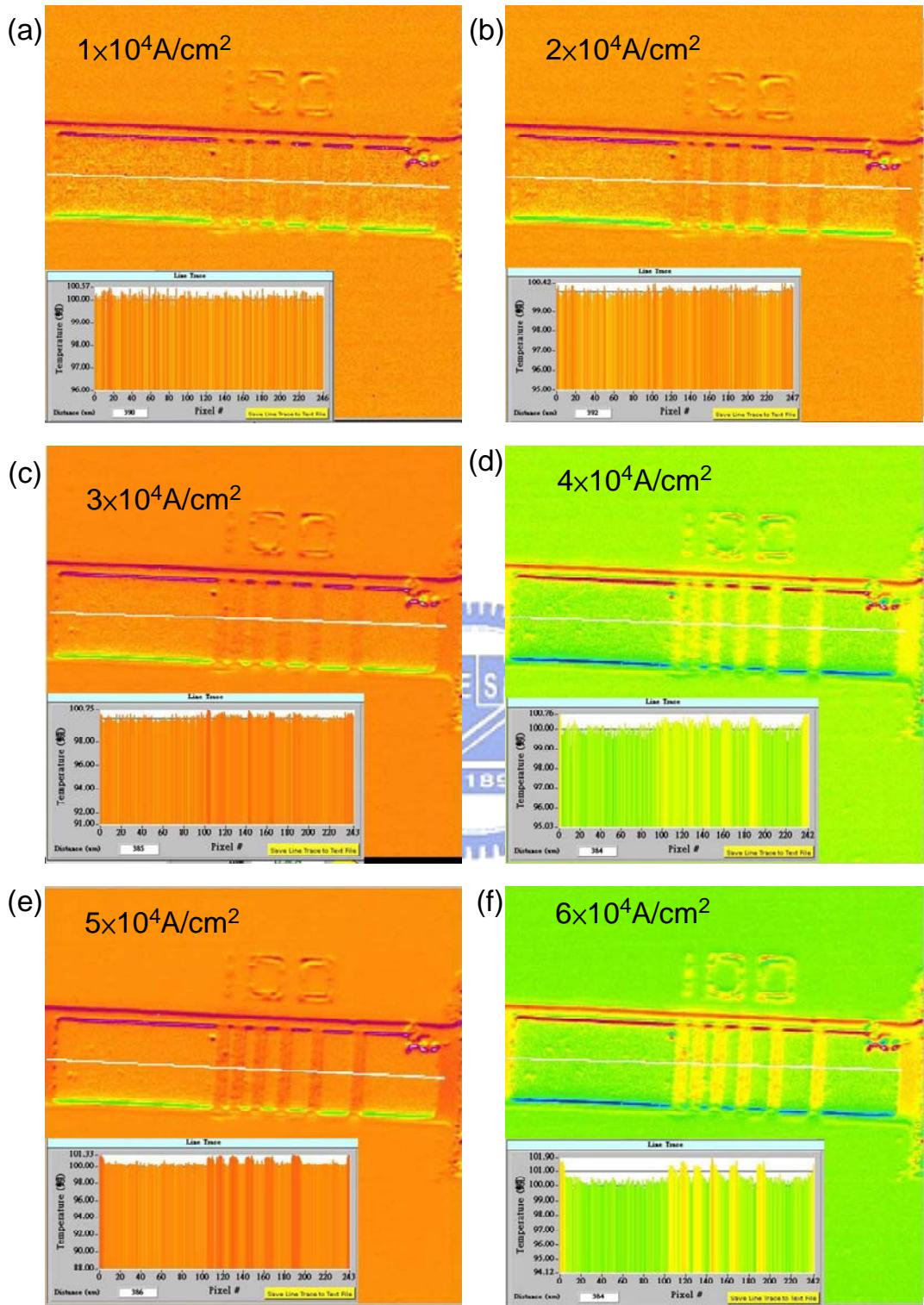

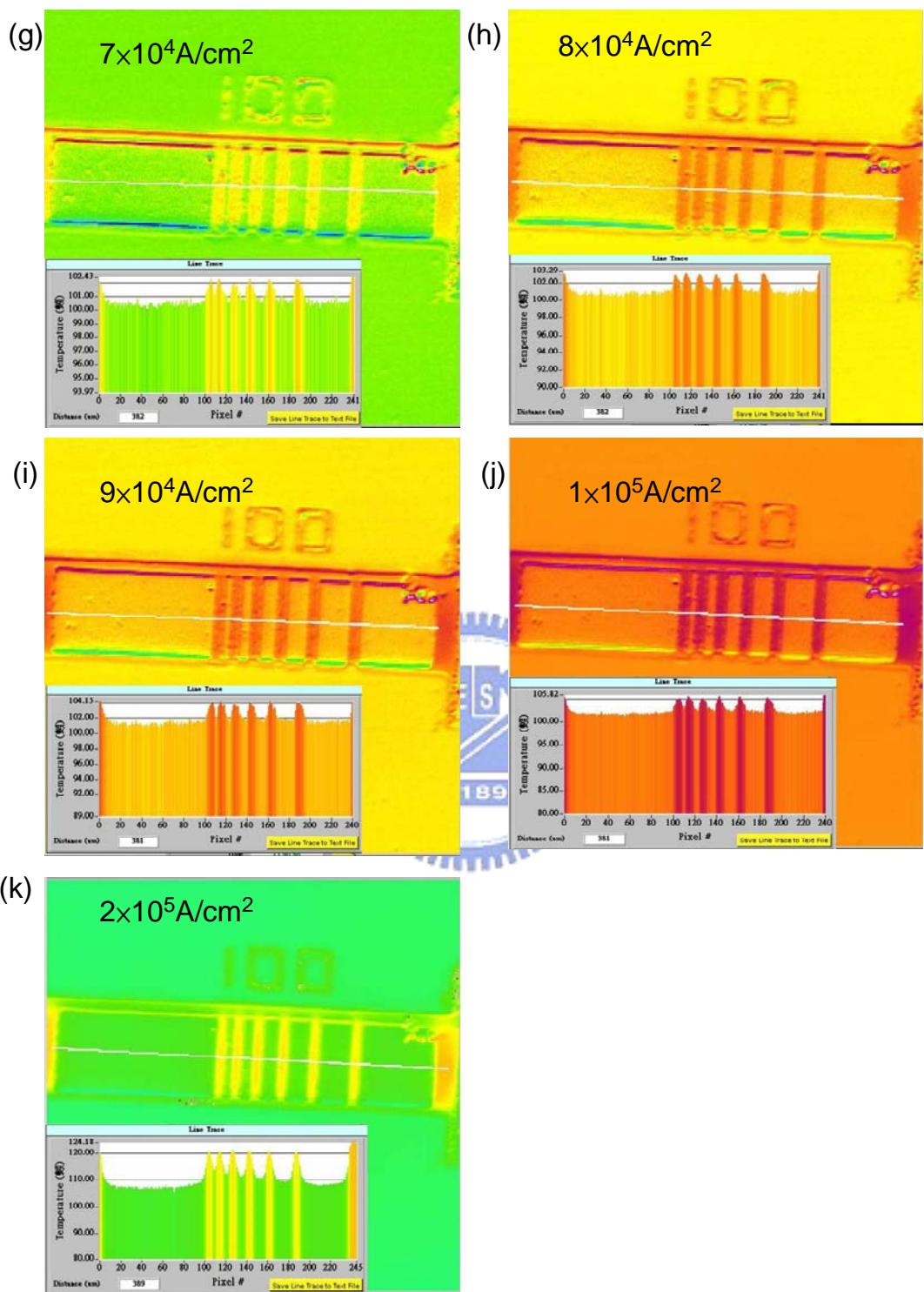

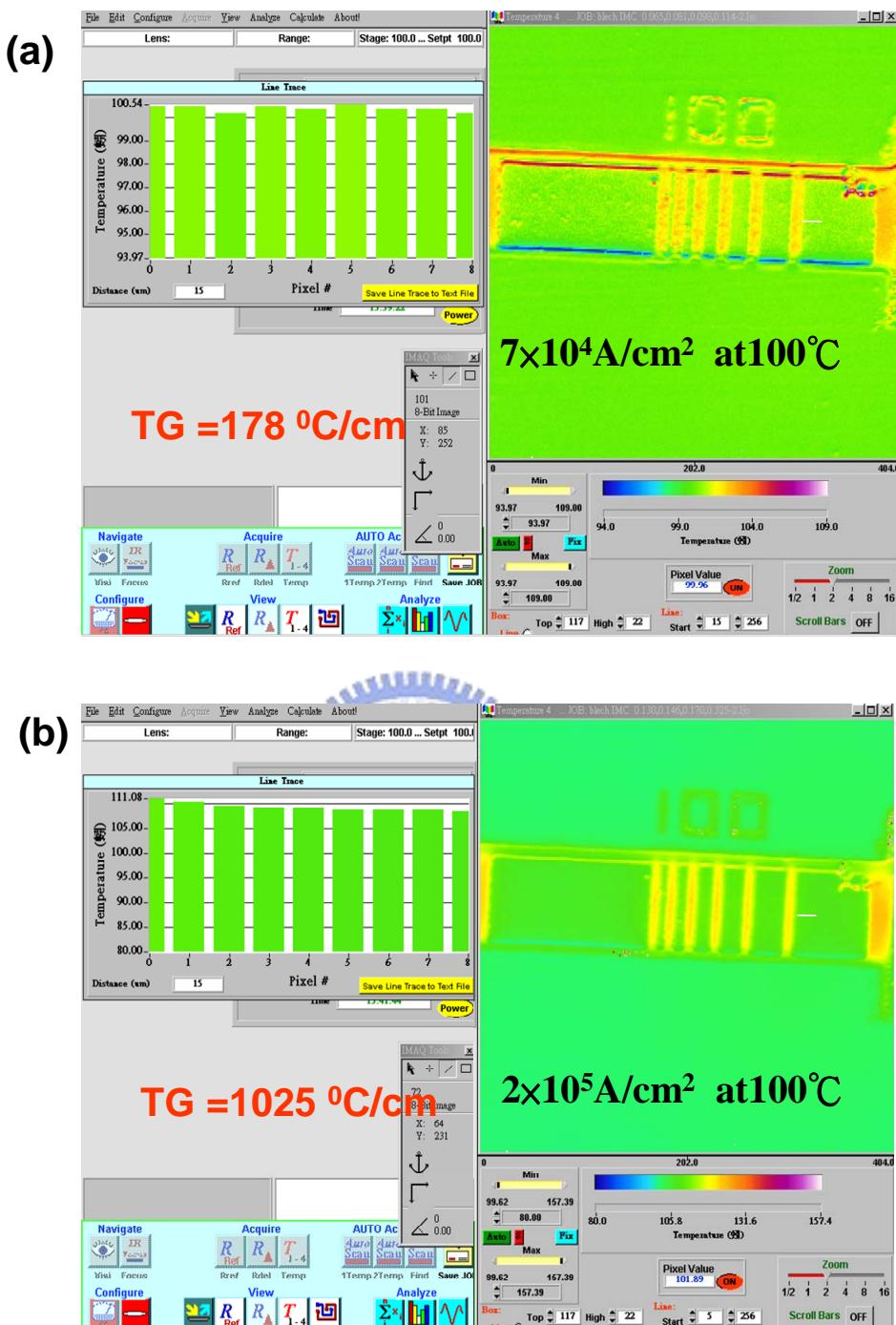

由於在通電的過程中，不同的材料會因焦耳熱效應而造成不同的溫升。因此我在背景溫度  $100^{\circ}\text{C}$  的條件下，將試片施以不同的電流密度分別是  $1 \times 10^4$ 、 $2 \times 10^4$ 、 $3 \times 10^4$ 、 $4 \times 10^4$ 、 $5 \times 10^4$ 、 $6 \times 10^4$ 、 $7 \times 10^4$ 、 $8 \times 10^4$ 、 $9 \times 10^4$ 、 $1 \times 10^5$  與  $2 \times 10^5 \text{ A/cm}^2$ ，經由紅外線量測儀(infrared microscopy)我們可以得到試片表面的溫度分佈如圖 4.5 所示。圖中白線所對應的溫度分別示於圖的左下方。我們可以發現在  $1 \times 10^4$ 、 $2 \times 10^4$ 、 $3 \times 10^4$ 、 $4 \times 10^4$ 、 $5 \times 10^4$ 、 $6 \times 10^4$ 、 $7 \times 10^4$ 、 $8 \times 10^4 \text{ A/cm}^2$  電流密度下 IMC stripes 只有少許不到  $1^{\circ}\text{C}$  的溫升而 Ti 層因為相較之下有比較高的電阻，因此溫升較 IMC stripes 高。當電流密度到達  $2 \times 10^5 \text{ A/cm}^2$  時 IMC stripes 的溫升接近  $8^{\circ}\text{C}$ ，而 Ti 層的溫升更是高達  $20^{\circ}\text{C}$  已有相當嚴重的焦耳熱效應，因此我們必須避免如此高的流密度以防止 Ti 層燒毀造成試片的斷路。且在較高的電流密度下，我們發現 IMC stripes 與 Ti 層接觸的地方，IMC 的溫度會較中間的部份高因此造成了一溫度梯度，如圖 4.6、(a)(b)  $7 \times 10^4$ 、 $2 \times 10^5 \text{ A/cm}^2$  所示，其中  $2 \times 10^5 \text{ A/cm}^2$  的電流密度下造成了  $1025^{\circ}\text{C}/\text{cm}$  溫度梯度。根據 C. Y. Liu [15] 所作的研究，Sn-Pb solder 在  $1010^{\circ}\text{C}/\text{cm}$  時便會產生熱遷移影響電遷移的原子流量，但由於研究的材料是較 Sn-Pb solder 融點高的 Sn-Cu 介金屬化合物且我們並沒有超過  $2 \times 10^5 \text{ A/cm}^2$  的電流密度實驗條件，因此在接下來的討論我們並不考慮熱遷移的影響。

圖 4.5、 $100^\circ\text{C}$ 下不同電流密度的溫度分佈圖。

圖 4.6、(a)100°C下，電流密度  $7 \times 10^4 \text{ A/cm}^2$  的溫度分佈圖與其溫度梯度。

(b)100°C下，電流密度  $2 \times 10^5 \text{ A/cm}^2$  的溫度分佈圖與其溫度梯度。

### 4.3 IMC stripes 電流密度分佈模擬

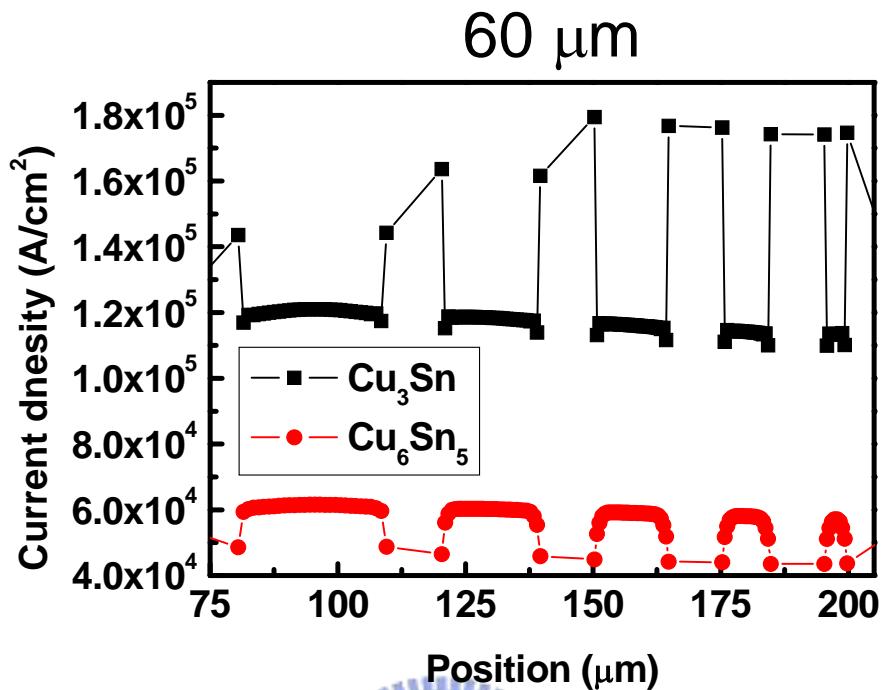

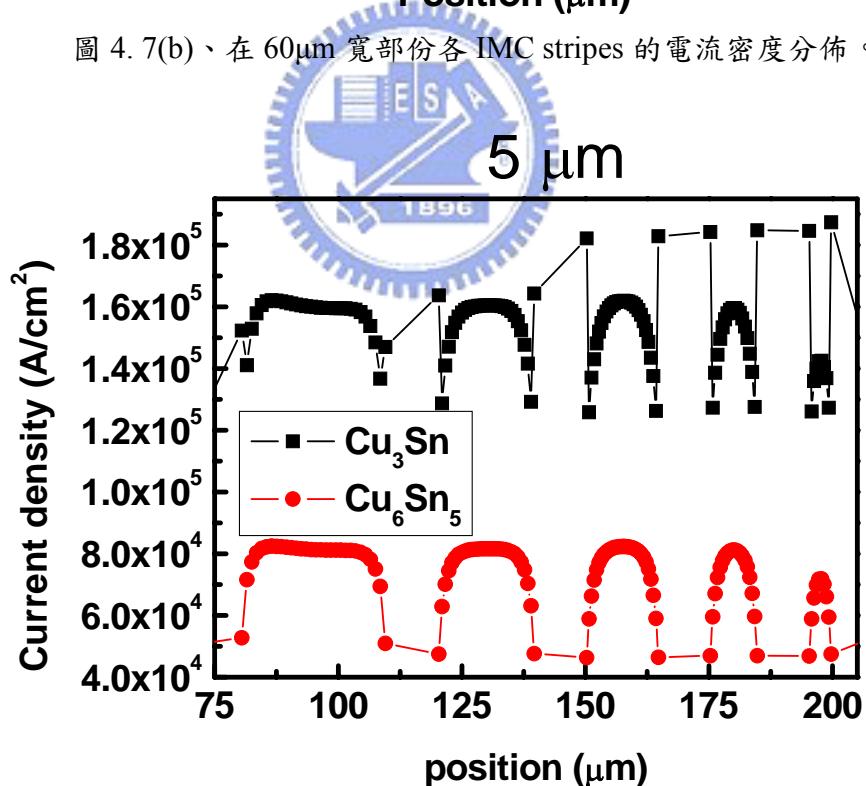

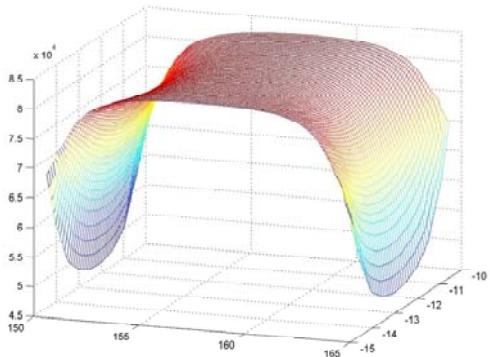

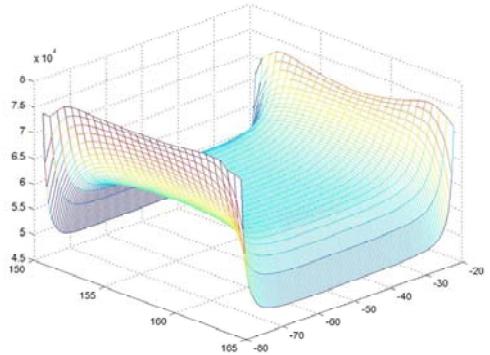

我們利用 Labview6i 來模擬電流密度在 IMC stripes 中的分佈情形，其中  $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  與 Ti 的電阻率分別為  $17.5$ 、 $8.93$  與  $42\mu\Omega\cdot\text{cm}$ 。我們取 IMC 薄膜為  $1\mu\text{m}$  厚，在相同的製程下  $\text{Cu}_3\text{Sn}$  有固定的厚度  $0.37\mu\text{m}$ ，因此我們可以得知  $\text{Cu}_6\text{Sn}_5$  的厚度為  $0.63\mu\text{m}(1-0.37)$  而 Ti 層為  $0.8\mu\text{m}$ 。我們輸入的電流值為  $0.09\text{Amp}$ ，試片結構如圖 4.7 (a)。扣除兩端不計，試片包含兩部份的圖形，寬度由小到大分別為  $5\times60$ 、 $10\times60$ 、 $15\times60$ 、 $20\times60$  與  $30\times60\mu\text{m}^2$  另一部份為  $5\times5$ 、 $10\times5$ 、 $15\times5$ 、 $20\times5$  與  $30\times5\mu\text{m}^2$ 。其電流密度分佈如 4.7(b)(c) 所示，圖 4.7 (b) 表示  $5\times60$ 、 $10\times60$ 、 $15\times60$ 、 $20\times60$  與  $30\times60\mu\text{m}^2$  IMC stripes 中  $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$  的電流密度，在  $\text{Cu}_6\text{Sn}_5$  的部份每段其值均為  $6\times10^4\text{A/cm}^2$  而  $\text{Cu}_3\text{Sn}$  的部份每段為  $1.2\times10^5\text{A/cm}^2$  與我們預估的相近。圖 4.7 (c) 表示  $5\times5$ 、 $10\times5$ 、 $15\times5$ 、 $20\times5$  與  $30\times5\mu\text{m}^2$  IMC stripes 中  $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$  的電流密度，其電流密度值不管是  $\text{Cu}_6\text{Sn}_5$  還是  $\text{Cu}_3\text{Sn}$  均較  $60\mu\text{m}$  者來的大且較預估的值來的大，但  $5\times5\mu\text{m}^2$  較其它的來的低。首先， $5\times5$ 、 $10\times5$ 、 $15\times5$ 、 $20\times5$  與  $30\times5\mu\text{m}^2$  IMC stripes 電流密度較預估值來的大的原因可能是 IMC 相較 Ti 為較低電阻，因此電流從側面流入 IMC 導致較預估值來的大。 $5\times5\mu\text{m}^2$  較其它  $5\mu\text{m}$  的來的低可能是因為側面的截面積較小，電流來不及進入 IMC。圖 4.8 是取  $15\mu\text{m}$  寬 IMC stripes 的 3D 電流密度分佈，我們可以較清楚的看到  $15\times60\mu\text{m}^2$  兩側的電流密度值較其它部份來的高，而  $15\times5\mu\text{m}^2$  的部分因為兩側的距離較窄並沒有兩側較中間高的情形。

圖 4.7(a)、施加 0.09Amp 厚度 1 $\mu\text{m}$  的電流密度分佈圖。

圖 4.7(b)、在 60  $\mu\text{m}$  寬部份各 IMC stripes 的電流密度分佈。

圖 4.7(c)、在 5  $\mu\text{m}$  寬部份各 IMC stripes 的電流密度分佈。

**15  $\mu\text{m}$**

圖 4.8、 $15\mu\text{m}$  寬 stripes 的 3D 電流密度分佈。

#### 4.4 各通電條件與其破壞行為

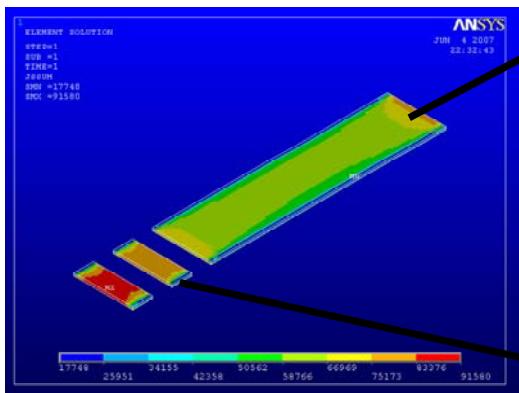

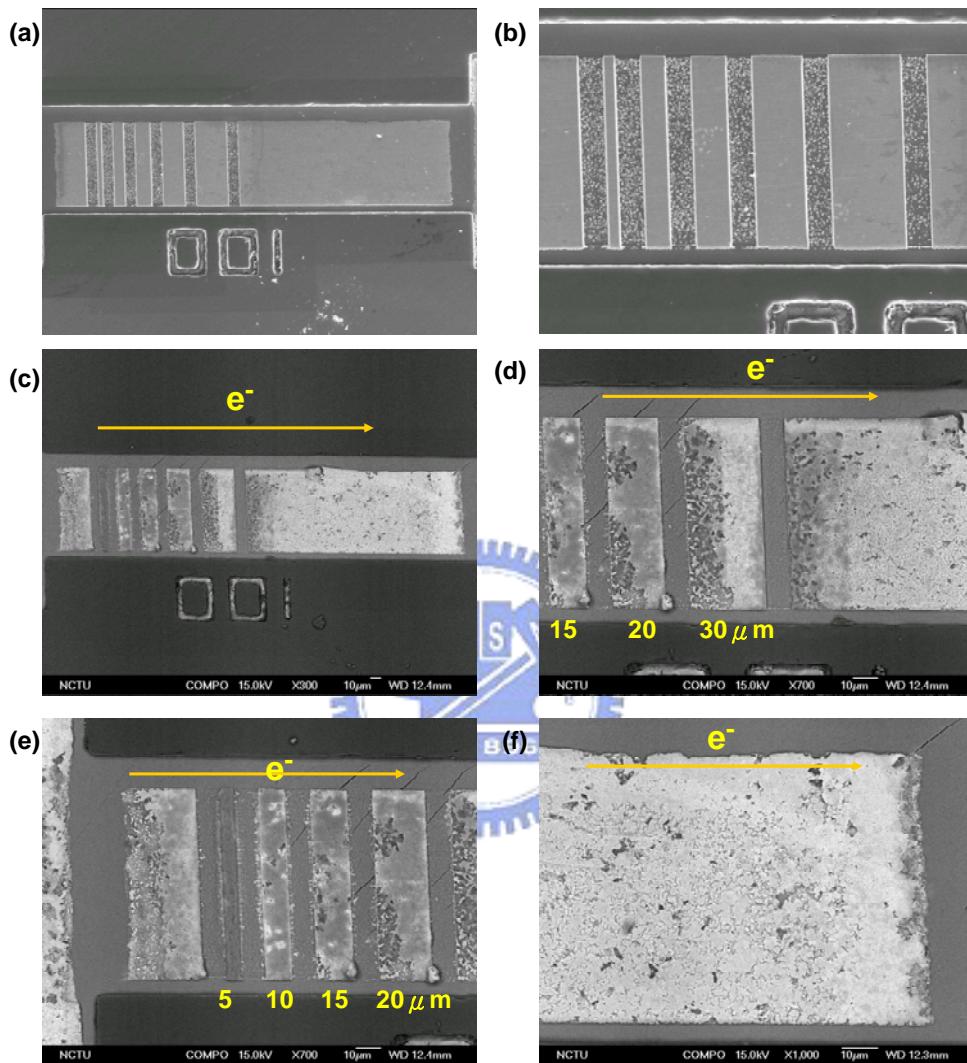

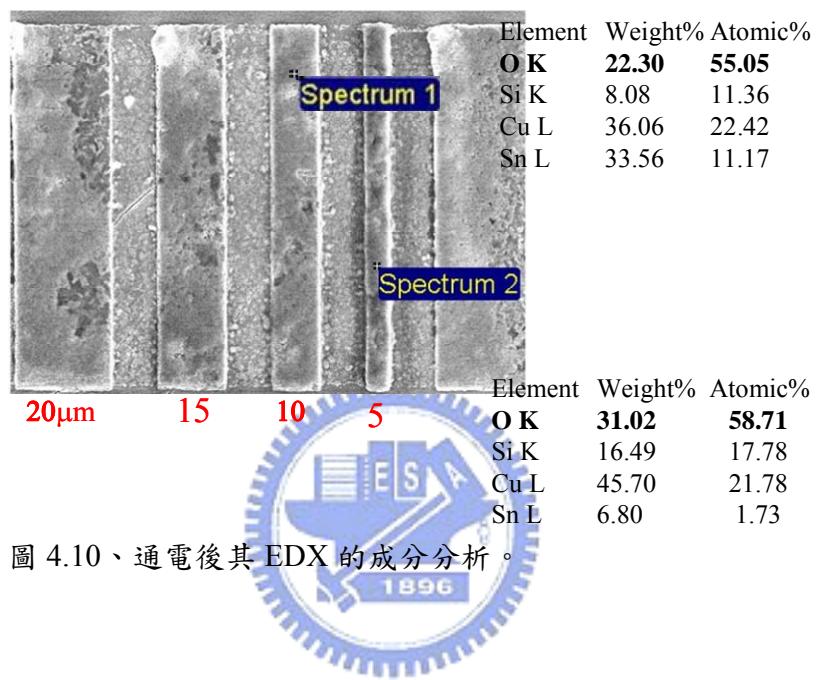

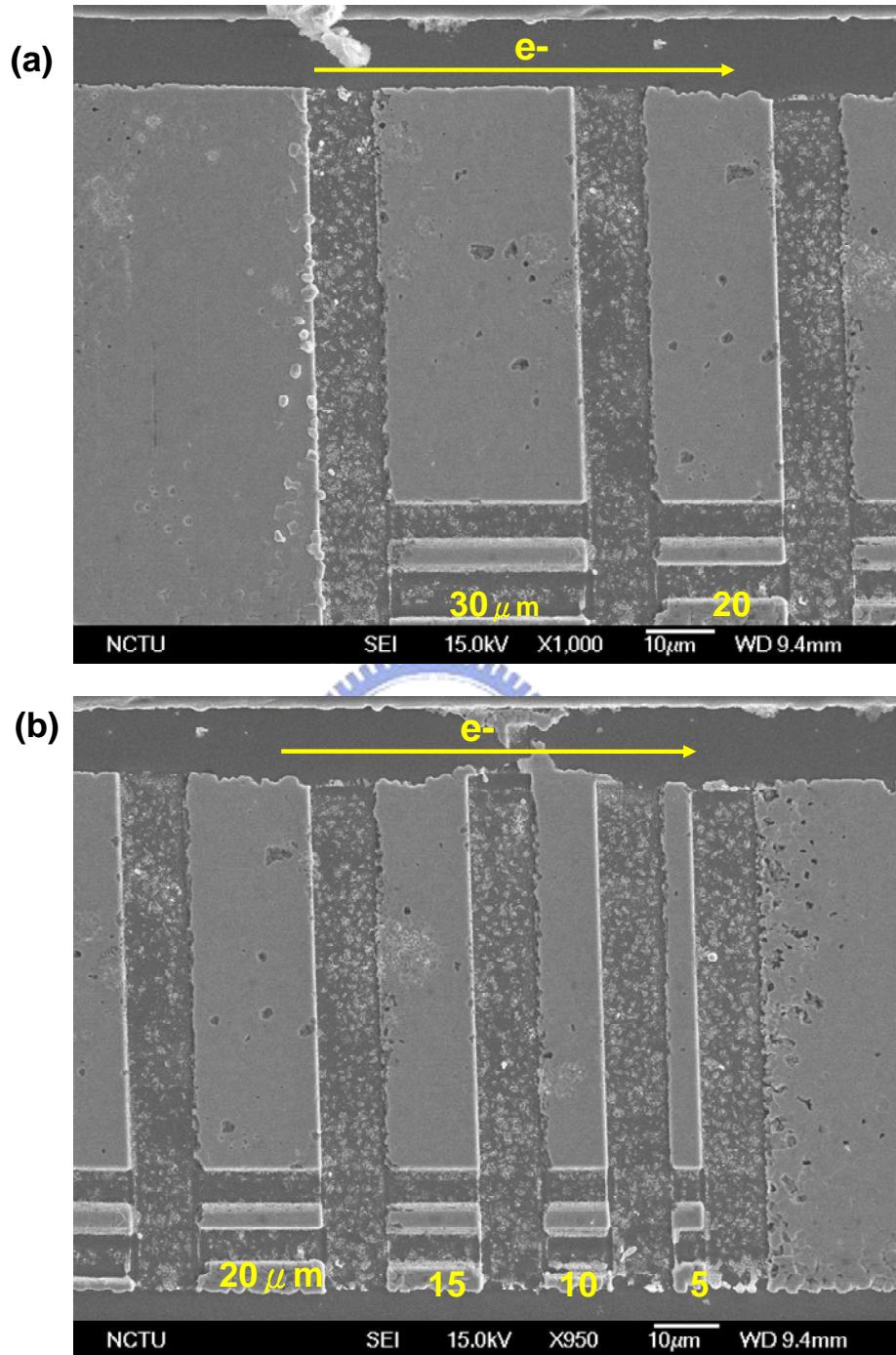

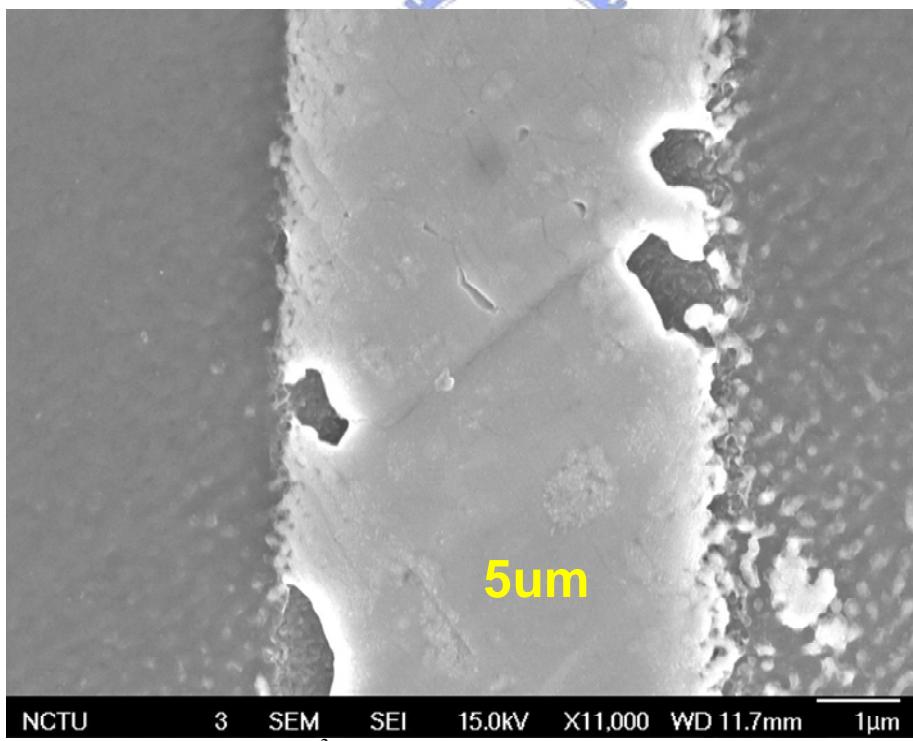

首先，我們在  $300^{\circ}\text{C}$ 、大氣的環境下將試片施以  $0.189\text{A}$  的電流， $\text{Cu}_6\text{Sn}_5$  與  $\text{Cu}_3\text{Sn}$  將分別承受  $1.39 \times 10^5$  與  $2.73 \times 10^5 \text{A/cm}^2$  的電流密度。在通電  $54\text{h}$  後，我們觀察其破壞形貌如圖 4.9、所示。發現在沿著電子流方向有長度相依性(length-dependent)的電遷移現象。此現象是由於愈短的 stripe 在電遷移的作用下，將產生愈大背向應力(backstress)來抵消電遷移的作用，因此愈長的 stripe 將遭受到愈嚴重的電遷移破壞，如圖 4.9、(d)(e)所示。並在長度  $15$ 、 $20\mu\text{m}$  的 stripe 邊緣產生了凸起。此外我們在右端剩餘的 IMC 薄膜上發現與電遷移方向相反的遷移，如圖 4.9、(f)所示。依據如先前所提到的焦耳熱效應的現象，由於 Ti 層為電阻較高的部份，所以 Ti 層相較於 IMC stripe 有較高的溫升，因此在 IMC stripe 與 Ti 層的交界處存在著一方向由 Ti 向 IMC stripe 溫度梯度，在熱遷移流量大於電遷移流量的情況下，造成了與電子流方向相反的遷移。然而不幸的是，經由 EDX 的分析發現，由於試片於高溫下( $300^{\circ}\text{C}$ )暴露於大氣中產生了嚴重的氧化現象，如圖 4.10、所示，其含有的氧原子超過了  $50 \text{ atomic\%}$ 。因此，此結果並非 Cu、Sn 化合物的本身的電遷移性質，且在圖 4.9、(d)(e)(f)，我們發現在 Ti 層因為溫度太高而造成的龜裂現象，期將影響我們原本預期的各層的電流密度，而導致求得不正確的電遷移參數。

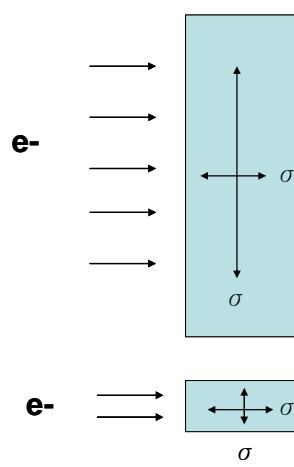

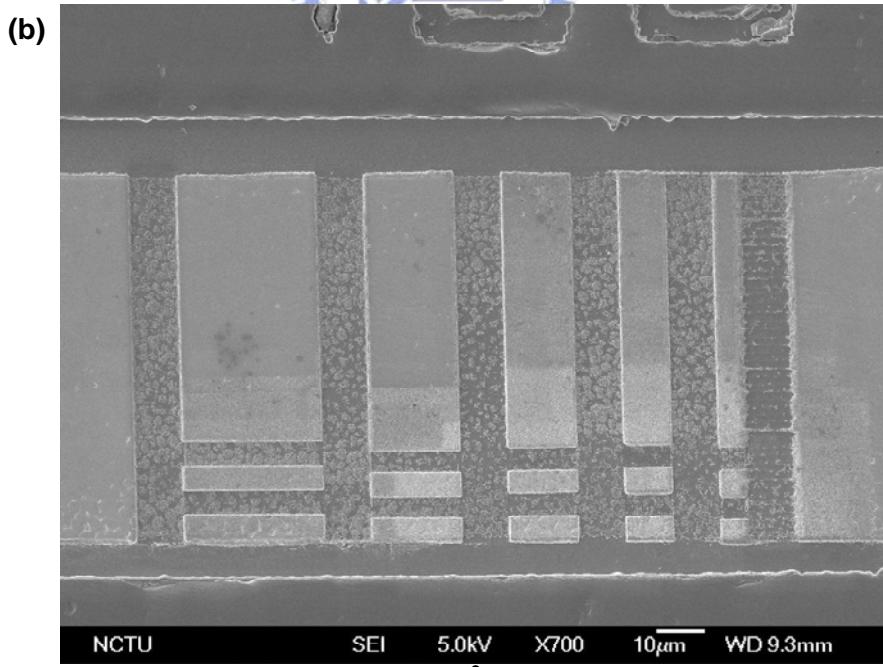

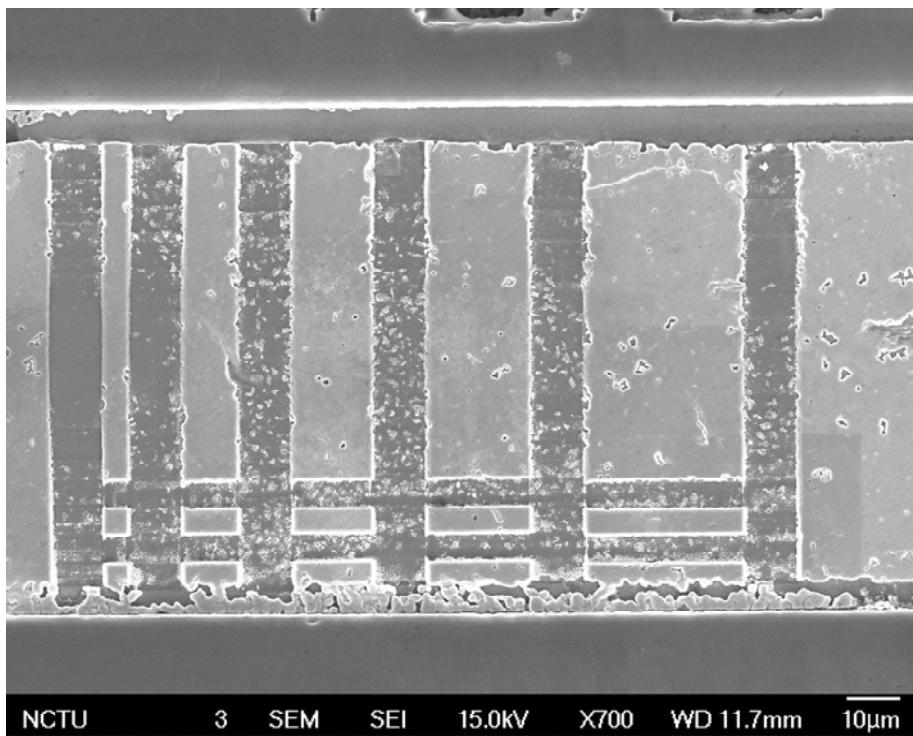

為了避免氧化與 Ti 層龜裂的問題，我們將試片放置在真空度  $2.3 \times 10^{-3}\text{torr}$  的爐管中，並將溫度降至  $225^{\circ}\text{C}$  的環境下通電，且測試新的圖形是否有不同的電遷移現象。由圖 4.11、(b)可知新的圖形包含兩部份，除了原有  $5\mu\text{m}$ 、 $10\mu\text{m}$ 、 $15\mu\text{m}$ 、 $20\mu\text{m}$ 、 $30\mu\text{m}$  寬的 stripes

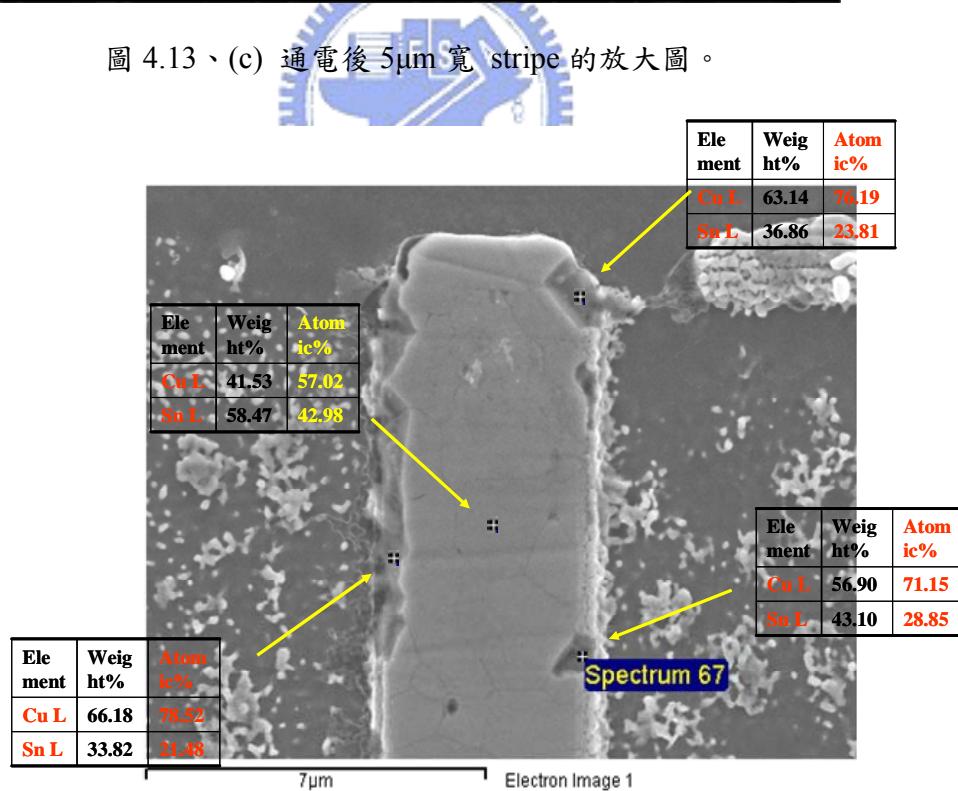

外，在下面的部份還多出了  $5 \times 5$ 、 $5 \times 10$ 、 $5 \times 15$ 、 $5 \times 20$ 、 $5 \times 30\mu\text{m}^2$  的 stripes。由於薄膜為雙軸向的平面應力，在原本的圖形中，其長軸應力方向與電子流方向垂直而短軸應力方向與電子流平行，然而下面的部分卻相反，長軸應力方向與電子流方向平行而短軸應力方向與電子流垂直如圖 4.12。當施於  $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別為  $1.47 \times 10^5$ 、 $2.89 \times 10^5 \text{ A/cm}^2$  的電流密度  $65.5\text{h}$  後，由圖 4.13、(a)(b)(c)我們可以看到每一條 stripe 在遭受電子流的邊緣都有電遷移造成的鋸齒狀破壞，且在 stripe 中間與另外一側的邊緣有不明的孔洞生成(這部份將在後面提出討論)，經由 EDX 分析電遷移所剩下的 IMC 發現，其大 Cu、Sn 的比例大多接近  $\text{Cu}_3\text{Sn}$  的成分如圖 4.13、(d) 所示。而在新圖形的部份，其所遭受的電遷移破壞也大多跟原本的圖形依樣，在遭受電子流的邊緣有電遷移的現象，並沒有如預期的因為軸向應力的不同而有不同的電遷移破壞情形如圖 4.13、所示。觀察試片電遷移測試後的形貌，發現溫度降至  $225^\circ\text{C}$  後並沒有發生 Ti 層龜裂的情形，且由於在真空爐管中進行測試，事後 EDX 分析並沒有氧化的情形。

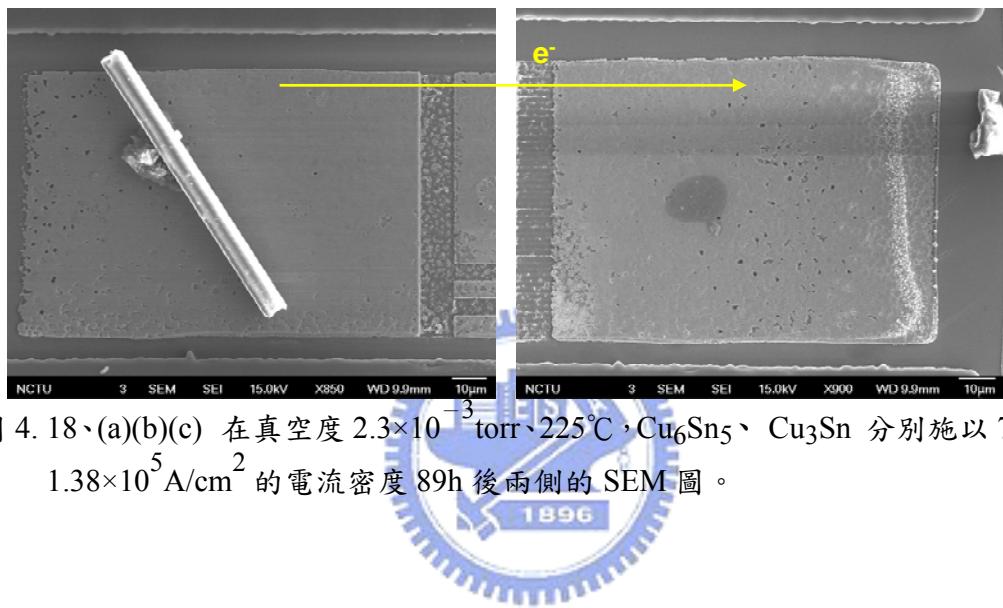

接下來，同樣在真空度  $2.3 \times 10^{-3}\text{ torr}$  的爐管中、 $225^\circ\text{C}$  下進行電遷移測試，這次  $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  的電流密度分別為  $7 \times 10^4 \text{ A/cm}^2$  與  $1.38 \times 10^5 \text{ A/cm}^2$ ，在通電  $89\text{h}$  後，由圖 4.16、我們可以看到由 5 到  $30\mu\text{m}$  的 stripes 在遭受電子流的邊緣均有受電遷移破壞的現象，而在新圖形的部份大致上也是跟原有的 stripes 一樣每一段都有電遷移的發生，除了  $5\mu\text{m} \times 5\mu\text{m}$  的部份，這可能是通電的時間不夠久而造成這一段沒有電遷移的現象，而 IMC 薄膜左右兩端剩下的部份，

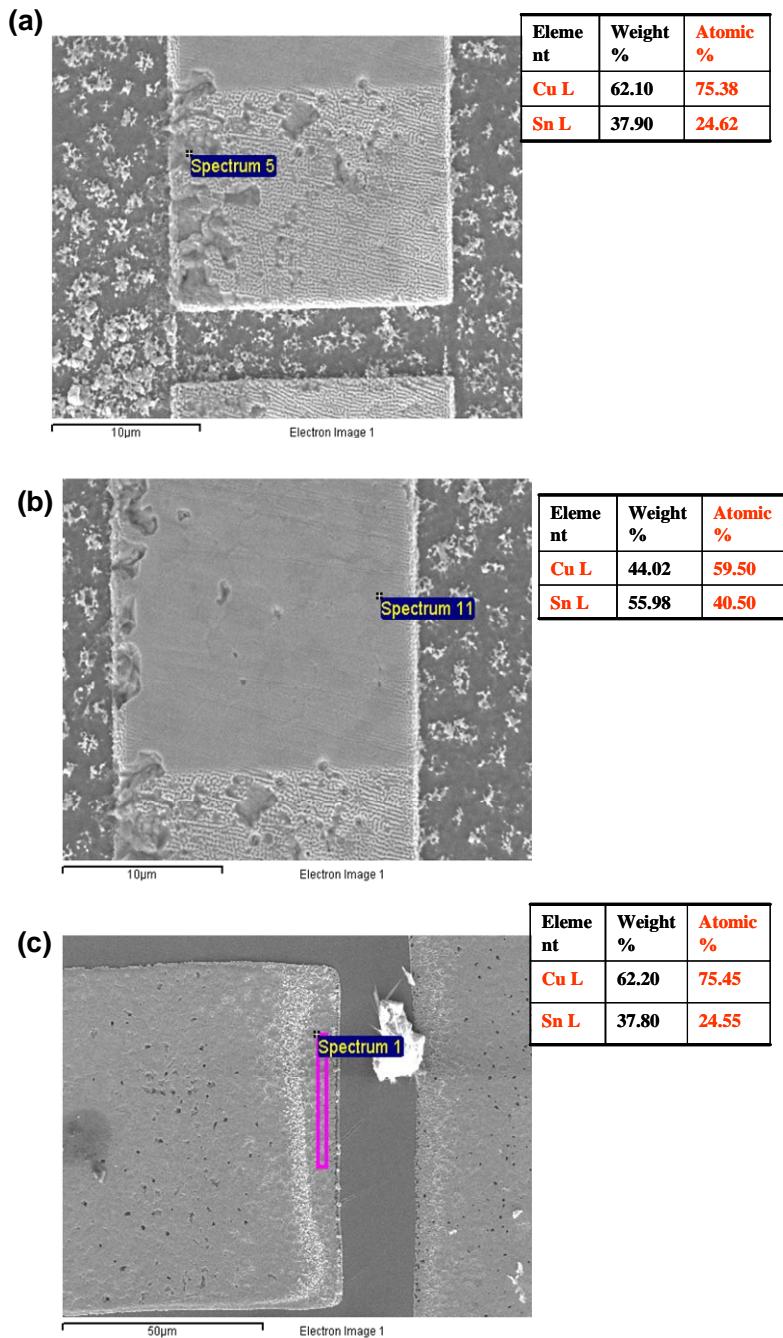

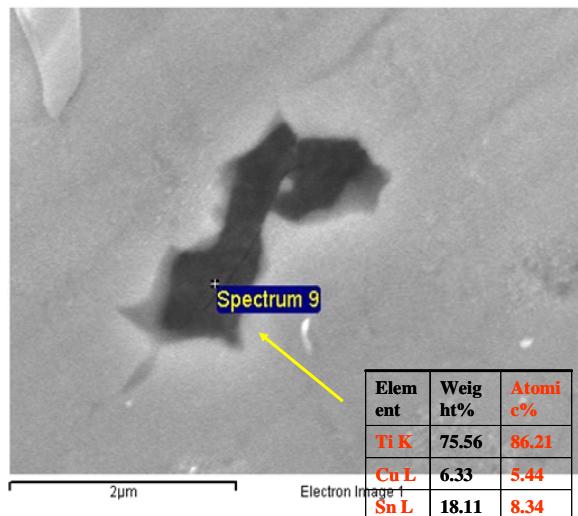

右邊有著和電子流不同方向的遷移，這可能是熱遷移的流量(flux)大於電遷移的結果，在左邊的部份除了圓柱狀的長條物是玻璃碎片非電遷移的結果外，在遭受電子流的邊緣有電遷移造成的破壞。但我們可以發現在每條 stripes 非邊緣的部份卻有許多不明原因的孔洞生成，這並非電遷移造成的效果，這部份將在後面做討論。利用 EDS 分析發現，電遷移後剩餘的 IMC 其成分大約 Cu:Sn 3:1 的  $\text{Cu}_3\text{Sn}$  而在遠離電遷移的部份其成分大致上為  $\text{Cu}_6\text{Sn}_5$  如圖 4.19 所示。

由於在先前的電遷移測試上，發現許多並非發生在 edge 的孔洞，這並不合乎電遷移破壞的模式。於是我們做了一對照組，將試片石英封管在真空度  $2.3 \times 10^{-3}$  torr 中，在  $231^\circ\text{C}$ (考慮 joule heating effect  $225+6^\circ\text{C}$ )不通電的情況下進行 anneal 測試，由圖 4.20 我們可以發現原本平整的 IMC 薄膜圖 4.20(before annealing)在 anneal 測試 85h 後，在 stripe 上產生了許多孔洞，不僅在 stripe 兩邊緣中間的部份，甚至在其邊緣的部份也有孔洞的生成如圖 4.21 所示，這將誤導我們對電遷移破壞的判斷。經由 EDS 分析生成的孔洞發現，剩餘的部分幾乎是裸露的 Ti 層和剩餘的  $\text{Cu}_3\text{Sn}$  或  $\text{Sn} \cdot \text{Cu}$  如圖 4.22 所示。這可能是因為在 anneal 測試時  $\text{Cu}_6\text{Sn}_5$  分解而轉換成  $\text{Cu}_3\text{Sn}$  ( $\text{Cu}_6\text{Sn}_5 \rightarrow 2\text{Cu}_3\text{Sn} + 3\text{Sn}$ ) [24]，在這過程中雖然生成了 2 莫耳的  $\text{Cu}_3\text{Sn}$  但其體積仍然小於 1 莫耳的  $\text{Cu}_6\text{Sn}_5$  而 Sn 很容易受到電遷移的作用而消耗，這可能是 IMC 薄膜生成孔洞的原因，但我們並沒有在測試後的 IMC 薄膜上發現 Sn 的堆積，這是比較奇怪的地方。

檢視所有的電遷移測試條件，我們初步可以知道在  $225^\circ\text{C}$  下  $\text{Cu}_6\text{Sn}_5$  的 critical product 小於  $35\text{Amp}/\text{cm}$  ( $7 \times 10^4 \text{ A}/\text{cm}^2 \times 5 \mu\text{m}$ )。且

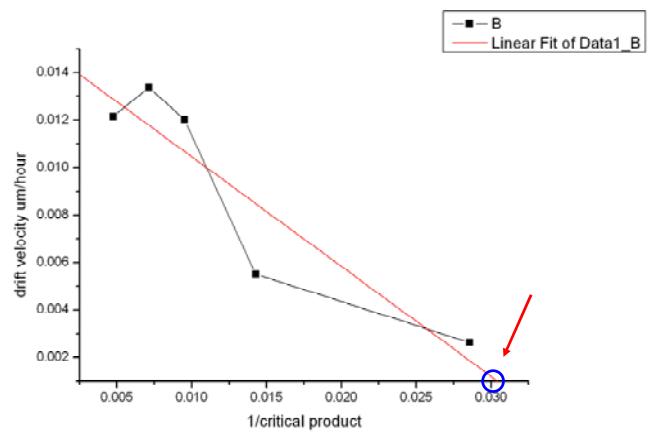

我們利用圖 4.15 電遷移造成的 depletion 依漂移速度( drift velocity) 與 1/critical product 作圖，如圖 4.23，依照 fitting 的結果我們可以得到 Cu<sub>6</sub>Sn<sub>5</sub> 的 critical product 約為 32Amp/cm。比較[25]C. C. Wei and Chih Chen 對 SnPb solder 在 100°C、 $2 \times 10^4$  A/cm<sup>2</sup> 所得到的 critical product 20~30 Amp/cm 而言，相對於 SnPb solder 而言，較高融點的 Cu<sub>6</sub>Sn<sub>5</sub> 有較佳的抗電遷移能力。

圖 4.9、(a)(b)通電前 SEM 影像。(c)(d)(e)(f)通電後 BEI 影像。

圖 4.10、通電後其 EDX 的成分分析。

圖 4.11、利用 FIB 劃出的新圖形。

圖 4.12、薄膜應力方向與電子流方向。

圖 4.13、(a)(b) 在真空度  $2.3 \times 10^{-3}$  torr、 $225^\circ\text{C}$ ， $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別施以  $1.47 \times 10^5$  、 $2.89 \times 10^5 \text{ A/cm}^2$  的電流密度 65.5h 後的 SEM 圖。

圖 4.13、(c) 通電後 5 $\mu$ m 寬 stripe 的放大圖。

圖 4.13、(d)EDX 分析電遷移所剩下的 IMC。

圖 4.14、新圖形各長度 depletion 的情形。

圖 4.15、在真空度  $2.3 \times 10^{-3}$  torr、225°C 通電前。

圖 4.16 (a)(b) 在真空度  $2.3 \times 10^{-3}$  torr、 $225^\circ\text{C}$ ， $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別施以  $7 \times 10^4$ 、 $1.38 \times 10^5 \text{ A/cm}^2$  的電流密度 89h 後的 SEM 圖。

圖 4.17、(a)(b)(c) 在真空度  $2.3 \times 10^{-3}$  torr、 $225^\circ\text{C}$ ， $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別施以  $7 \times 10^4$ 、 $1.38 \times 10^5 \text{ A/cm}^2$  的電流密度 89h 後新圖形的 SEM 圖。

圖 4.18、(a)(b)(c) 在真空度  $2.3 \times 10^{-3}$  torr、 $225^\circ\text{C}$ ， $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別施以  $7 \times 10^4$ 、 $1.38 \times 10^5 \text{ A/cm}^2$  的電流密度 89h 後兩側的 SEM 圖。

圖 4.19、(a)(b)(c) 在真空度  $2.3 \times 10^{-3}$  torr、 $225^\circ\text{C}$ ， $\text{Cu}_6\text{Sn}_5$ 、 $\text{Cu}_3\text{Sn}$  分別施以  $7 \times 10^4$ 、 $1.38 \times 10^5 \text{ A/cm}^2$  的電流密度 89h 後 EDS 的分析。

圖 4.20、anneal 測試前。

圖 4.21、在真空度  $2.3 \times 10^{-3}$  torr 中  $231^\circ\text{C}$  不通電的情況下進行 85h 的 anneal 測試。

| Element | Weig ht% | Atom ic% |

|---------|----------|----------|

| Si K    | 5.03     | 8.29     |

| Ti K    | 94.97    | 91.71    |

| Element | Weig ht% | Atom ic% |

|---------|----------|----------|

| Cu L    | 59.92    | 73.64    |

| Sn L    | 40.08    | 26.36    |

圖 4. 22、anneal 測試後的 EDX 分析。

圖 4.23、 $\text{Cu}_6\text{Sn}_5$  電流密度  $7 \times 10^4 \text{ A/cm}^2$  通電 89h 依 drift velocity and 1/critical product 做圖。

## 第 5 章、結論

由上述各通電條件結果，我們發現在 225°C 下因為 Cu 薄膜在時效之後已經消耗完，所以 Cu<sub>6</sub>Sn<sub>5</sub> 將會分解成 Cu<sub>3</sub>Sn 而造成 IMC stripes 體積的縮小，造成孔洞的生成。且經由通電後試片的 EDS 分析，IMC stripes 在電遷移測試後 Cu<sub>6</sub>Sn<sub>5</sub> 會 migrate 而剩下 Cu<sub>3</sub>Sn，因此 Cu<sub>6</sub>Sn<sub>5</sub> 的抗電遷移能力小於 Cu<sub>3</sub>Sn，相信這是合理的結果。因為 Cu<sub>3</sub>Sn 有較高的熔點 (676°C) 而 Cu<sub>6</sub>Sn<sub>5</sub> 的熔點卻只有 415°C，因此 Cu<sub>3</sub>Sn 理應有較好的抗電遷移。在固定的溫度下，材料的臨界成積(critical product)為一定值  $(J \times L)_{crit}$ ，而由 Cu<sub>6</sub>Sn<sub>5</sub> 在電流密度  $7 \times 10^4$  A/cm<sup>2</sup>、225°C 的電遷移破壞的結果發現最短 stripe (5μm) 也產生了電遷移破壞，因此我們可以推論 Cu<sub>6</sub>Sn<sub>5</sub> 的 critical product 小於 35 Amp/cm ( $7 \times 10^4$  A/cm<sup>2</sup> × 5μm) 且經過 fitting 之後其值大約為 32 Amp/cm，對 SnPb solder 而言，Cu<sub>6</sub>Sn<sub>5</sub> 對電遷移有較佳的抵抗。在通電的過程中，我們可以看到兩端剩下的 IMC stripes 會有與電遷移方向相反的遷移，因此我們在 Sn-Cu IMC 的電遷移中我們必須考慮交耳熱效應所造成的熱遷移。

## 參考文獻

1. Jae-Woong Nah, J. O. Suh, K. N. Tu., ECTC, (2006)

2. K. N. Tu , J. W. Mayer , and L. C. Feldman , Pearson Education POD ,355,(1996).

3. I. A. Blech. and E. Kinsbron. Thin solid films , 25.327,(1975).

4. I. A. Blech. J. Appl. Phys , 47:pp.1203 ,(1976)

5. I. A. Blech and C. Herring. Appl. Phys. Lett., 29 , 131,(1976)

6. C. Herring. Di. , J. Appl. Phys. , 21, 437, (1950)

7. K. N. Tu, J. W. Mayer, and L. C. ,New York, Ch. 14, (1992)

8. H.-U. Schreiber. Solid States Electronics, 28, 1153, (1984)

9. C. Y. Liu, C. Chen, C. N. Liao, and K. N. Tu, Appl. Phys. Lett. , 75, 58, (1999).

10. C. Y. Liu, and C. Chen, and K. N. Tu, J. Appl. Phys. , 88, 5703, (2000).

11. C. K. Chou, C. A. Chen, S. W. Liang, and Chih Chen, J. Appl. Phys., 99, 54502,(2006)

12. T. L. Shao, Y. H. Chen, S. H. Chiu, and Chih Chen, J. Appl. Phys., 96, 8, (2004)

13. C. Ludwig, Sitzungsber. Akad. Wiss. Wien., Math.–Naturw,K1, 20, 539, (1856)

14. Hua Ye, Cemal Basaran, and Douglas Hoopkins, Appl. Phys. Lett., 82, 7,(2003)

15. Y. C. Chuang, C. Y. Liu, Appl. Phys. Lett., 88, 174105, (2006)

16. Hsiang-Yao Hsiao and Chih Chen, Appl. Phys. Lett., 90,152105, (2007)

17. Z. Mei, A. J. Sunwoo and J. W. Morris, Jr., Metallurgical Transactions

A, 23A, 857, (1992)

18. K. N. Tu and R. D. Thompson, Acta Metall., 30, 947, (1981)

19. S. W. Chen, C. M. Chen and W. C. Liu, J. Electronic Materials, Vol. 27, No.11, pp.1393, (1998)

20. A. Hayashi, C. R. Kao and Y. A. Chang, Scripta Material, Vol.37, No.1, pp393,(1997)

21. S. Bader, W. Gust and H. Hieber, Acta Metall. Mater., Vol.43, No.1, pp329, (1995)

22. L. H. Su, Y. W. Yen, C. C. Lin, and S. W. Chen, Metallurgical and Materials Transaction B, Vol.28B, pp927, (1997)

23. T. Y. Lee, W.J. Choi, and K. N. Tu, JMR, V.17N. 2, Feb 2002

24. Kejun Zeng, Roger Stierman, Tz-Cheng. Chiu, and Darvin Edwards., J.Appl. Phys. ,Vol. 97, 24508, (2005)

25. C. C. Wei and Chih Chen, Appl. Phys. Lett., 88, 182105, (2006)