## The investigation of capture/emission mechanism in high- k gate dielectric soft breakdown by gate current random telegraph noise approach

Steve S. Chung and C. M. Chang

Citation: Applied Physics Letters 93, 213502 (2008); doi: 10.1063/1.3036681

View online: http://dx.doi.org/10.1063/1.3036681

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/93/21?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Charge detrapping and dielectric breakdown of nanocrystalline zinc oxide embedded zirconium-doped hafnium oxide high- k dielectrics for nonvolatile memories Appl. Phys. Lett. **96**, 192106 (2010); 10.1063/1.3429590

Time dependent dielectric breakdown of amorphous ZrAl x O y high- k dielectric used in dynamic random

J. Appl. Phys. 106, 044104 (2009); 10.1063/1.3204001

access memory metal-insulator-metal capacitor

Structural and electrical properties of neodymium oxide high- k gate dielectrics

Appl. Phys. Lett. 89, 232908 (2006); 10.1063/1.2402237

Charge trapping and dielectric relaxation in connection with breakdown of high- k gate dielectric stacks

Appl. Phys. Lett. 88, 202904 (2006); 10.1063/1.2203942

Soft breakdown fluctuation events in ultrathin SiO 2 layers

Appl. Phys. Lett. 73, 490 (1998); 10.1063/1.121910

## The investigation of capture/emission mechanism in high-k gate dielectric soft breakdown by gate current random telegraph noise approach

Steve S. Chungal and C. M. Chang

Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300 Taiwan

(Received 7 August 2008; accepted 5 November 2008; published online 24 November 2008)

In this paper, the trapping/detrapping in high-k gate dielectrics has been analyzed by gate current random telegraph noise  $(I_G)$  measurement. Gate current is suppressed when traps capture electrons and recovers for empty traps. By statistically extracting capture and emission times, we can understand the trap properties. Besides, the influence will be understood by observing the variation of Gate current fluctuation. Through the analysis of the device after soft-breakdown (SBD), the deterioration of the dielectric will change the capture cross section. Moreover, the traps in the SBD path have been identified as the cause of a huge increase in the gate leakage. © 2008 American Institute of Physics. [DOI: 10.1063/1.3036681]

High-k materials have received more attention in recent years for an attempt to replace the  $\mathrm{SiO}_2$ . However, one of those important issues in high-k materials is the trapping/detrapping behavior which gives rise to drain current and  $V_T$  instability during the measurement. Previous approaches in exploring high-k traps have been conducted mostly by transient related methods. These methods are used to look into the interface and near-interface property but the accuracy is challenged if gate dielectric is heavily destroyed.

In this paper, we will utilize the gate current random telegram noise ( $I_G$  RTN) method to study the trapping and detrapping in a high-k gate dielectric metal-oxide-semiconductor field effect transistor (MOSFET) device. Applications to observe the process-induced traps and post soft-breakdown (SBD) gate current fluctuation will be demonstrated. In the past,  $I_G$  RTN has been used in SiO<sub>2</sub> dielectric capacitors, while it has been used for the study of MOSFET with high-k dielectric in this work, from which the device SBD has been quantitatively analyzed.

For the experimental work, high-k gate dielectric nMOSFETs were fabricated using advanced complementary metal-oxide-semiconductor field effect transistor technology. The gate stack consists of a polycrystalline silicon gate electrode, HfSiO as the high-k layer, and a SiON interfacial layer. The transistors have an EOT of 1.2 nm, a gate length of 0.09  $\mu$ m, and a gate width of 0.2  $\mu$ m.

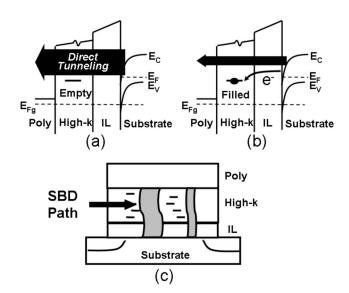

Figure 1 shows the band diagram of the device. Gate leakage current is considered as direct tunneling current from the substrate to the positively biased gate. When the traps in the dielectrics are empty, the gate leakage will maintain constant as in Fig. 1(a). As trap energy maintains at a level which is equal to that of channel carriers or below, traps will capture electrons from the channel. When the electrons are trapped, they will raise the nearby potential and lower the leakage, as shown in Fig. 1(b).

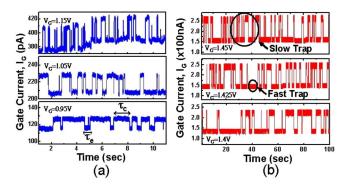

Figure 2 shows the gate current versus time, in which RTN signals due to traps in dielectrics before (left) and after SBD (right) were observed. For the measurement in Fig. 2(a) before the SBD, gate leakage is hundreds of picoamperes and exhibits a fluctuation with an order of tens of picoamperes.

The capture and/or emission is obviously dependent on the gate bias. Here,  $\tau_c$  is the capture time and  $\tau_e$  is the emission time. After SBD, Fig. 2(b), the  $I_G$  RTN is different from that observed in Fig. 2(a). As a result of the SBD path, we can see a huge increase in the leakage current (with a third-order increase) and a longer time for capture or emission. The SBD path performs as a channel to open or close one or more conductive paths across the dielectrics. As a consequence, electron trapping/detrapping in defects near (or inside) the SB weak spot will induce some local changes in the barrier height as well as the tunneling probability between two neighboring traps.<sup>3</sup> A single electron trapped in a site inside or very close to the conductive path could in principle blockade the majority of the current flowing through the path, as a result of Coulomb repulsion. In addition, a fraction of the conductive paths is not always available for conduction but can be switched on and off, giving rise to the large current fluctuations.

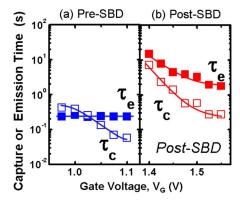

Figure 3 shows the average emission  $(\tau_e)$  and capture times  $(\tau_c)$  as a function of  $V_G$ . The average capture and

FIG. 1. The band diagram in high-k dielectrics (a) with empty trap state where electrons can be captured; (b) with filled trap state and the gate current is reduced. (c) The schematic of SBD paths in the gate dielectric.

a) Electronic mail: schung@cc.nctu.edu.tw.

FIG. 2. (Color online)  $I_G$  RTN measurement for the device (a) before SRD and (b) after SBD. Capture and emission times are defined in the plot. Note that the gate leakage shows a third-order difference in magnitude.

emission times are calculated by analyzing numerous switching events for each RTS trace. For pre-SBD, one can see that  $\tau_c$  for the dielectric traps is an exponential function of gate bias, given by<sup>4</sup>

$$\tau_c = 1/(n\nu_{\rm th}\sigma),\tag{1}$$

where n is the surface carrier concentration,  $v_{th}$  is the thermal velocity, and  $\sigma$  is the capture cross section of the trap involved. The surface potential  $\psi_s$  is a linear function of  $V_G$ and  $n \sim \exp(q\psi_s/kT)$ . Higher carrier concentration or larger  $V_G$  implies more electrons participation and reduces the time to capture. On the other hand, time constant of post-SBD is relatively longer than the case of pre-SBD, i.e.,  $\tau_c$  is much longer after device post-SBD. According to Eq. (1),  $v_{th}$  is  $V_G$ independent and n increases with gate bias. As a result, the possibility for the increase in capture time in post-SBD is attributed to a smaller  $\sigma$ ; i.e., after the formation of conduction path via the device SBD, the effective cross section of traps reduces since some of the traps have been used to built up the SBD conduction path, shown in Fig. 1(c). As a consequence, a smaller cross section for post-SBD gives rise to a longer capture time compared to the pre-SBD ones.

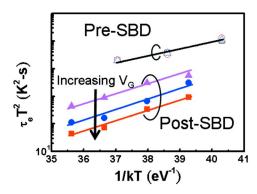

The capture time is influenced by not only capture cross section but also the electric field. Figure 4 shows the temperature dependence of  $\tau_c$ , which is obviously shorter at higher temperature. Channel carriers are heated at high temperature and more easily surpass the barrier of the capture. The activation energy of capture,  $E_a$ , i.e., the slope of  $\ln \tau_c$

FIG. 3. (Color online) Calculated capture and emission times as a function gate bias for the devices before and after SBD. Note that emission time, in

FIG. 4. (Color online) The dependence of capture time with temperature: (a) pre-SBD; (b) post-SBD. The activation energy  $E_a$  shows a huge change for devices after the SBD.

versus 1/kT plot, is calculated as shown in the plots. The cross section  $\sigma$  can be further related to  $E_a$  as<sup>4</sup>

$$\sigma = \sigma_0 \exp(-E_a/kT), \tag{2}$$

where  $\sigma_0$  is the prefactor of capture cross section. The activation energy is an index to reflect the capture cross section variation, as shown in Eq. (2). Before SBD, negligible change of  $E_a$  at different  $V_G$  can be seen, i.e.,  $\sigma$  is assumed a constant reasonably. After the SBD, Fig. 4(b), we can see a strong dependence of  $E_a$  on the gate bias. The main cause is that the capture probability has been enhanced via the SBD path. At high  $V_G$ ,  $E_a$  decreases and is believed to effectively increase the cross section, according to Eq. (2). This amounts to a decrease in the capture time. Hence, the activation energy shows a gate bias dependence feature after SBD.

One major difference can be seen from the comparison of  $\tau_e$  in Figs. 3(a) and 3(b), in which  $\tau_e$  shows completely different behavior for pre-SBD and post-SBD. For pre-SBD,  $\tau_e$  for the dielectric trap is completely independent of  $V_G$ . This accounts for the electron escaping through thermionic emission instead of the gate bias; i.e., it shows no field dependence and hence the possibility for direct tunneling back to the substrate or gate is ruled out. In comparison, emission of the electrons trapped within the conventional oxide is electric field dependent. The main difference is that high-k dielectric has larger physical thickness where the electrons captured cannot escape easily through direct tunneling. In other words, time to emission through thermionic emission is much shorter than the time through direct tunneling over the wide barrier. The emission time is given by  $^7$

$$\tau_e = \frac{\exp[(E_F - E_T)/k_B T]}{g\sigma \nu_{\text{th}} n}.$$

(3)

Here,  $E_F$ – $E_T$  is the distance from the Fermi energy level to the trap energy level and g is the degeneracy factor, which is usually considered as unity for electrons. Also, from the Arrhenius plot, <sup>8,9</sup> the emission time can be represented by

$$\ln \tau_e T^2 = -\ln \gamma \sigma + (E_{Cd} - E_T)/kT.$$

(4)

Here,  $E_{\rm Cd} - E_T$  is the distance from dielectric conduction band to trap energy level.  $\gamma = (v_{\rm th}/T^{1/2})(N_c/T^{3/2}) = 3.25 \times 10^{21} (m_n/m_0) \, {\rm cm}^{-2} \, {\rm s}^{-1} \, {\rm K}^{-2}$ , where  $m_n$  is the electron density-of-state effective mass. For the post-SBD, the emission time is no longer a constant but varies with gate bias as shown in Fig. 3(b). It was found that the root cause

FIG. 5. (Color online) Arrhenius plot for pre- and post-SBD. It shows no changes of  $\tau_e$  with gate bias, at a specific temperature in pre-SBD case. However, it shows gate bias dependent for post-SBD case. This is attributed to a decrease in the cross section as a result of the formation of a SBD induced conductive path.

is the field dependent property of the capture cross section. It can be justified from the plot in Fig. 5 and Eq. (4). Prior to SBD, the lines in  $\tau_e T^2 - 1/kT$  plots have the same slopes and interception with Y-axis, which means  $E_{\rm Cd} - E_T$  is fixed and capture cross section is independent of gate bias. After the formation of SBD path,  $E_{\rm Cd} - E_T$  is roughly identical at distinct gate bias. Nevertheless capture cross section varies with gate bias. It shows the capture cross section decreases with increasing gate bias, from Eq. (4). More importantly,  $\tau_e$  is largely increased for post-SBD, compared to pre-SBD, as a result of this decreased cross section,  $\sigma$ .

In summary,  $I_G$  RTN has been utilized for the study of high-k gate dielectric traps in MOSFETs. The capture and

emission mechanisms have been evaluated, especially for a study on the SBD. Several conclusions can be drawn from this study: (1) The gate leakage has been drastically increased as a result of the SBD with a formed conductive path; (2)  $\tau_e$  and  $\tau_c$  take longer time since the capture cross section becomes smaller; (3) the major difference between pre-SBD and post-SBD lies in the fact that cross section  $\sigma$  is field dependent for the latter and field independent for the former, shown in Fig. 5, while in most of the studies for SiO<sub>2</sub>,  $\sigma$  is considered to be a constant.

We would like to thank UMC, Taiwan for providing the devices used in this study. This work was supported by National Science Council, under contract No. NSC96-2628-E009-168.

<sup>1</sup>T. H. Hou, M. F. Wang, K. L. Mai, Y. M. Lin, M. H. Yang, L. G. Yao, Y. Jin, S. C. Chen, and M. S. Liang, Proceeding of the International Reliability Physical Symposium, 2004 (unpublished), p. 581.

<sup>2</sup>D. V. Singh, P. Soloman, E. P. Gusev, G. Sigco, and Z. Ren, Tech. Dig. - Int. Electron Devices Meet. **2004**, 863.

<sup>3</sup>F. Crupi, R. Degraeve, G. Groeseneken, T. Nigam, and H. E. Maes, IEEE Trans. Electron Devices **45**, 2329 (1998).

<sup>4</sup>M. J. Kirton and M. J. Uren, Appl. Phys. Lett. **48**, 1270 (1986).

<sup>5</sup>M. Schulz and N. M. Johnson, Solid State Commun. 25, 481 (1978).

<sup>6</sup>M. H. Tsai, H. Muto, and T. P. Ma, Appl. Phys. Lett. **61**, 1691 (1992).

<sup>7</sup>M. J. Kirton and M. J. Uren, Adv. Phys. **38**, 367 (1989).

<sup>8</sup>D. K. Schroder, *Semiconductor Material and Device Characterization*, 3rd ed. (Wiley, New York, 2006), p. 259.

<sup>9</sup>G. M. Martin, A. Mitonneau, and A. Mircea, Electron. Lett. **13**, 191 (1977).

<sup>10</sup>D. V. Lang, H. G. Grimmeiss, E. Meijier, and M. Jaros, Phys. Rev. B 22, 3917 (1980).