## 國立交通大學

## 光電工程學系 光電工程研究所

博士論文

多晶矽薄膜電晶體的空間與時間 變動性探討

Characterization of the Spatial and Temporal Variation of Poly-Si TFTs

196

研 究 生: 黄士哲

指 導 教 授: 戴亞翔 博士

中華民國九十八年六月

## 多晶矽薄膜電晶體的空間與時間 變動性探討

# Characterization of the Spatial and Temporal Variation of Poly-Si TFTs

研究生: 黄士哲 Student: Shih-Che Huang

指導教授: 戴亞翔 博士 Advisor: Dr. Ya-Hsiang Tai

國立交通大學

光電工程學系 光電工程研究所

博士論文

A Dissertation

Submitted to Institute of Electro-Optical Engineering

Department of Photonics

College of Electrical and Computer Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of Doctor of Philosophy

in

Electro-Optical Engineering June 2009

Hsinchu, Taiwan, Republic of China

中華民國 九十八 年 六 月

## 多晶矽薄膜電晶體的空間與時間 變動性探討

研究生: 黄士哲 指導教授: 戴亞翔博士

## 國立交通大學 光電工程研究所

#### 摘要

本論文探討多晶矽薄膜電晶體的在空間與時間上的特性變動。本論文雖然主要動機出發於主動式顯示器電路應用,但其結果則可擴大應用於顯示器以外的領域。本文首先討論在量產線上的元件特性變動,發現元件的變動特性除了有很嚴重變動範圍之外,其變動行為亦沒有模型能夠精確描述;這將在設計多晶矽薄膜電晶體電路時造成很大的問題。因此我們先參考在在金一氣一半導體電晶體(MOSFETs)結構中對於元件變動的討論,並且以類似的方式針對薄膜電晶體的變動性提出可能的變動因素。由此我們提出一"枕木型"布局方式並對此布局內的元件參數進行統計。此枕木型布局方式的特色是元件間的距離盡可能的縮到最小並且在此最小間距內,兩相鄰元件間的長距離變動(long-range variation)可以大幅降低。所量測到的元件參數呈現非對稱且不集中的分佈,與先前一般所預測的高斯分佈有明顯落差。利用電子學裡的小信號想法,我們可以將兩相鄰元件間的長距離變動與微觀變動(micro variation)區分開,並可以進一步探討元件間的最距離變動與微觀變動(micro variation)區分開,並可以進一步探討元件間的微觀變動模型。對元件的起始電壓與載子遷移率而言,N型與P型元件其微觀變動行為均呈現較集中與對稱的行為。我們提出兩個數學式以精確描述其微觀變動行為均呈現較集中與對稱的行為。我們提出兩個數學式以精確描述其微觀變動的參數分佈,並根據此兩模型探討元件的變動行為在數位與類比電路上造成的

影響。此外,我們亦利用此模型預測元件在不同元件尺寸下的變動行為。在論文研究方向上,利用枕木型元件布局可使元件的變動範圍大幅減小,以起始電壓為例,其標準差由 0.5~V 縮減至 0.03~V,這將有助於我們之後的元件時間變動性的討論,不會因元件空間上的變動行為而遮蓋住其在時間上的變動行為。

接下來我們討論元件在時間上的變動性。此處,元件的時間變動性可以單純的理解為其在直流與交流下的可靠度行為,並將於不同的章節裡個別討論。對於元件在直流操作下的可靠度行為,我們首先回顧元件在兩大劣化機制下,亦即為熱載子效應與自發熱效應,先前文獻已經發表的劣化行為。雖然已有很多文獻探討元件在這兩大劣化行為下所產生的元件特性改變,關於這兩個操作條件下元件的電容行為部份卻只有零星的文獻。我們討論在這兩個劣化行為下元件的電容特性變化,發現元件模擬軟體並不能很完整的描述元件的電容特性在不同量測頻率下的行為。因此我們採用另一個方法,利用相對較易取得的元件電流特性推論元件的電容特性,提出一由開極界電層電容與通道電阻所組成的元件模型,利用探討元件的電容特性,提出一由開極界電層電容與通道電阻所組成的元件模型,利用探討元件的電流特性去探討其電容特性。由於阻抗的電容項與量測頻率有關,Pc的位置亦與量測頻率有關。利用這個方式,我們探討元件在兩個主要劣化條件下的行為,同時也提出在這兩個操作條件下,元件在操作後的電路模型。對於兩個特別的電容特性在關閉區的行為,亦即N型元件在自發熱操作條件後與P型元件在熱數子操作條件後的現象,將會有一特別的討論。

接下來我們探討元件在閘極交流操作下的劣化行為。由應用端出發,我們發現元件在液晶顯示器面板內絕大部分時間處於閘極關閉區而其集極則持續給予交流訊號。然而,關於這個操作條件卻沒有任何已知的文獻探討其劣化行為。比較其閘極與源極電壓差以及閘極與集極電壓差,我們可以將其操作條件類比為閘極關閉區內的交流操作,而其源極與集極則均接地。N型元件在這樣的操作條件下,其電流特性出現了載子遷移率的下降,而電容則有扭曲(Distortion)的現象。對P型元件,其電流特性則出現了載子遷移率的上升,而電容則在關閉區出

現異常的上昇。我們亦探討元件的劣化行為與閘極電壓的參數,以及其電壓範 圍、頻率與工作週期(Duty cycle)的關聯。然而,由於其閘極電壓均低於其起始 電壓,在通道裡應該沒有通道載子,也因此這個劣化行為無法利用先前由 Uraoka 所提出的模型解釋。在此我們依然使用前文所使用的元件模型,並且同樣討論元 件在此操作條件下的阻抗行為。我們推論在此操作情況下元件的源極與集極接面 將會有很大的電場,並進一步造成元件的劣化。然而,這樣的推論無法被直接驗 證因為我們並沒辦法直接探測元件內的電壓分佈,因此我們使用一稱作 gated p-i-n 測試結構,其結構與 TFT 相似但其一端源極與集極的參雜經過更改,使其 横向結構類似一 p-i-n 元件。採用這種結構的特色是這樣的元件擁有和與 TFT 相似的結構,但其通道內的電壓可以由一端的接面控制,進而可以讓其另一接面 上形成大電場。這樣,經由比較交流操作後的 TFT 與直流操作後的 gated-p-i-n 元件,我們先前所提出的理論獲得證實一處於很大逆向偏壓源極與集極接面的劣 化是閘極關閉區下交流操作的劣化主因。關於 N 型與 P 型元件的不同劣化行為亦 有深入討論。此外,亦比較了幾個相似的劣化條件,發現不論載子的來源來自於 導通區的集極電流,或是關閉區的漏電流,抑或是由導通區切向關閉區時,由通 道區被空乏掉的載子,一但接面上有大電場的產生,均會出現類似熱載子效應的 劣化行為;由另一角度來看,其亦可被總結為一廣義的熱載子效應。總結而言, 本文所提出的模型與其劣化模型將會為元件的時間變動特性提供有用的資訊,也 可幫助評估元件的時間變動行為。

Characterization of the Spatial and Temporal Variation of Poly-Si TFTs

**Student: Shih-Che Huang**

Advisor: Dr. Ya-Hsiang Tai

Department of Photonics & Institute of Electro-optical Engineering,

College of Electrical and Computer Engineering

**National Chiao Tung University**

Abstract

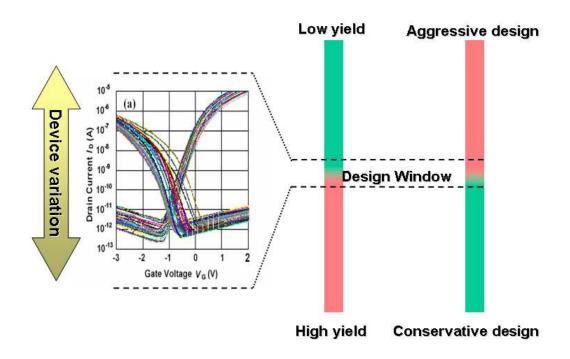

This work focuses on the variation behavior of poly-Si TFTs both spatially and

temporally. This work is mainly enlightened from, but not limited to, the display

electronics. First the spatial variation of the devices is studied for the devices from the

mass production line. The serious variation behavior and no description nor trend for

the device variation makes it rather difficult for designers to develop the circuits

composed of poly-Si TFTs. Thus we referred to the cases in MOSFETs and

analogically proposed factors for the variation behavior for poly-Si TFTs. Based on

the idea, the special layout called crosstie layout is proposed, measured and the device

parameters are extracted and statistically summarized. The feature of the crosstie

layout is that the devices are located as close as possible and in such case the

long-range variation can be greatly reduced for the two adjacent devices. The device

parameters show apparent asymmetric and non-centered distribution, which is much

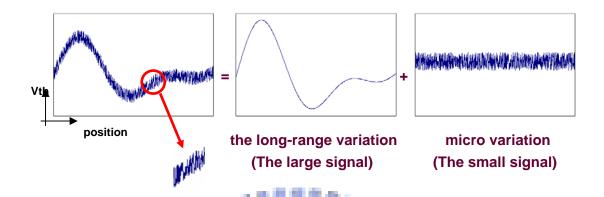

different from the usual Gaussian distribution assumption. A method enlightened

from the electronics is proposed to decouple the long-range and micro variation and

by finding the difference between the adjacent devices the true micro variation profile

- iv -

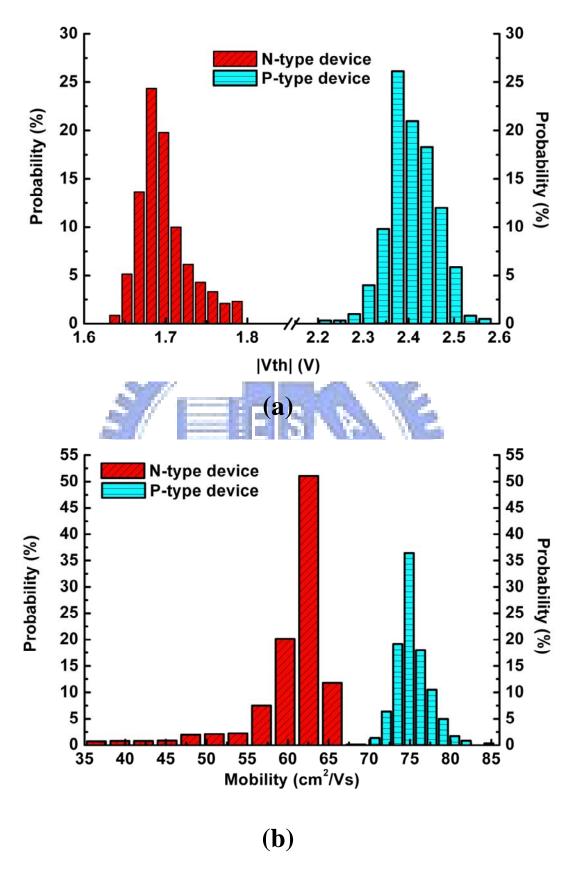

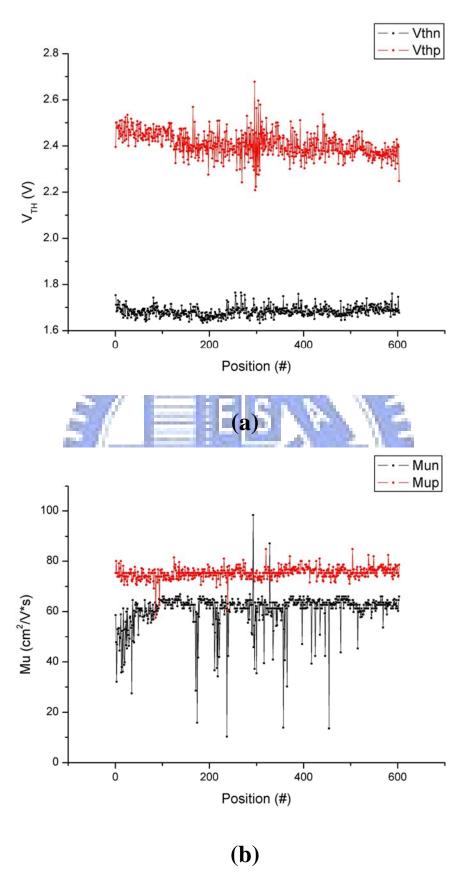

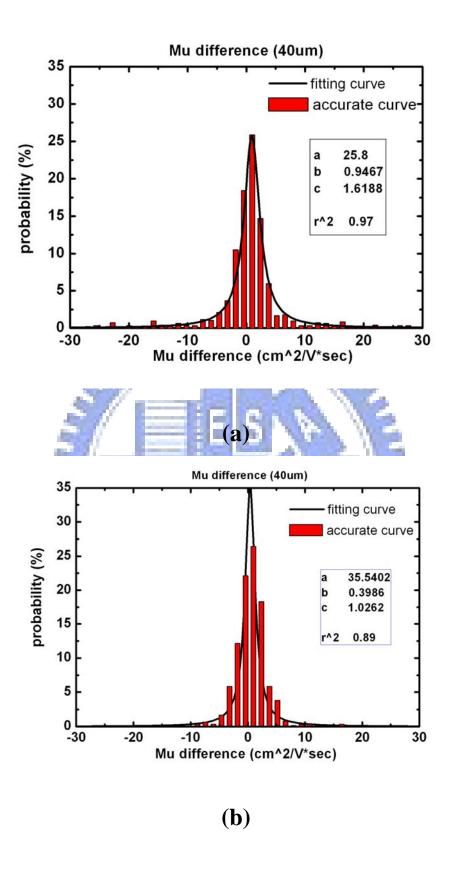

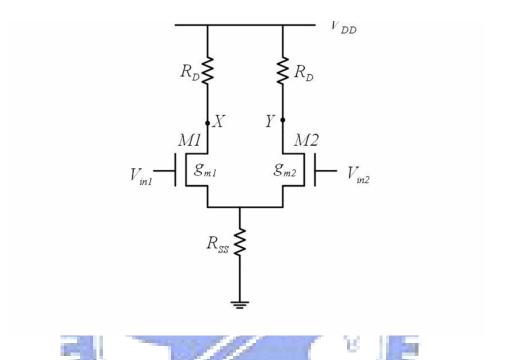

can be examined. The micro variation behaviors for the threshold voltage and mobility are found to be more centered and symmetric for both n-type and p-type devices. Two equations are proposed to well fit the micro variation and also based on the models the effects of device variation on the analog and digital circuits are simulated and discussed. In addition, based on the models, the projected device variation behavior for devices with different device dimension is also provided. By utilizing the crosstie layout, the variation behavior of the devices is greatly reduced, take the threshold voltage for instance, from 0.5 V to 0.03 V. The reduced variation also facilitates the following study of temporal variation, in which the effect of spatial variation can be greatly relieved and not to cover the effect of temporal variation.

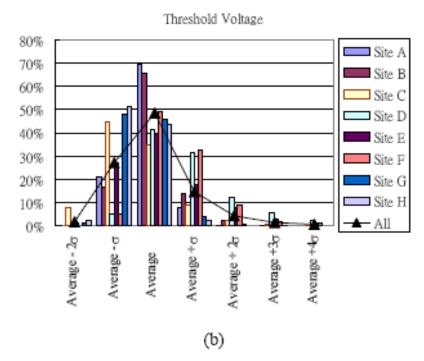

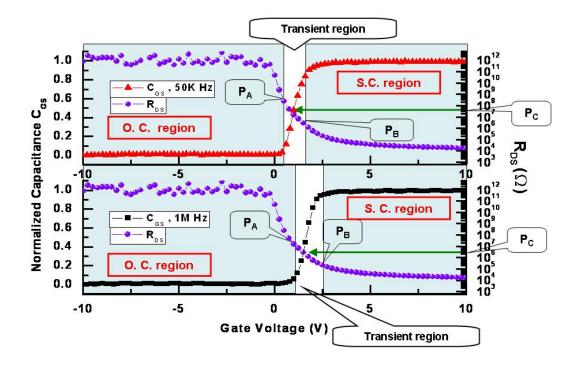

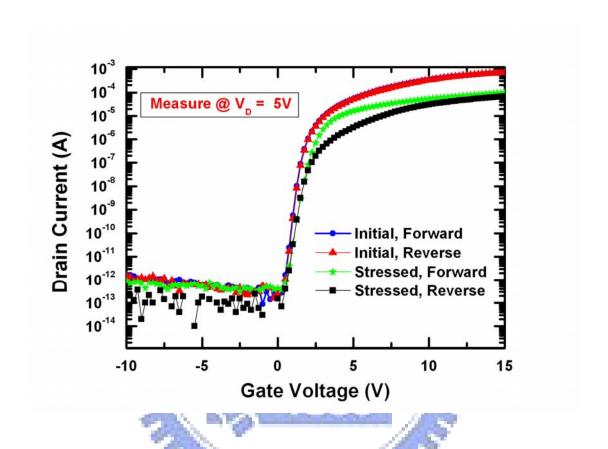

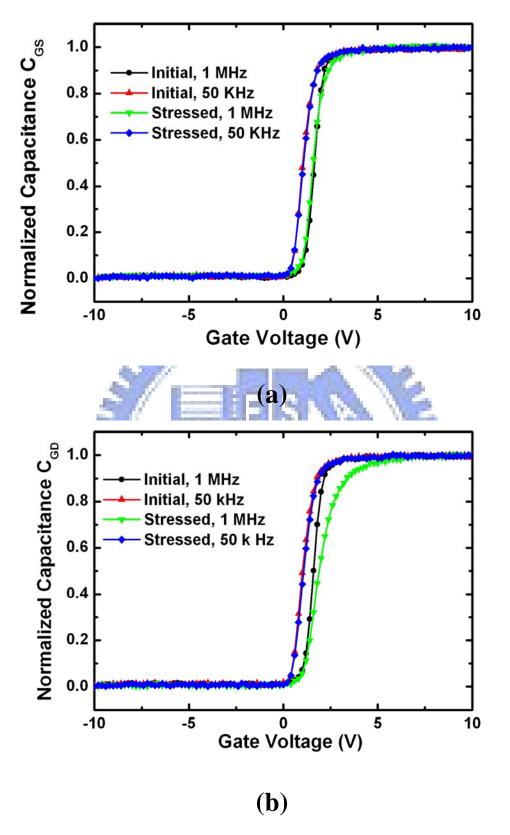

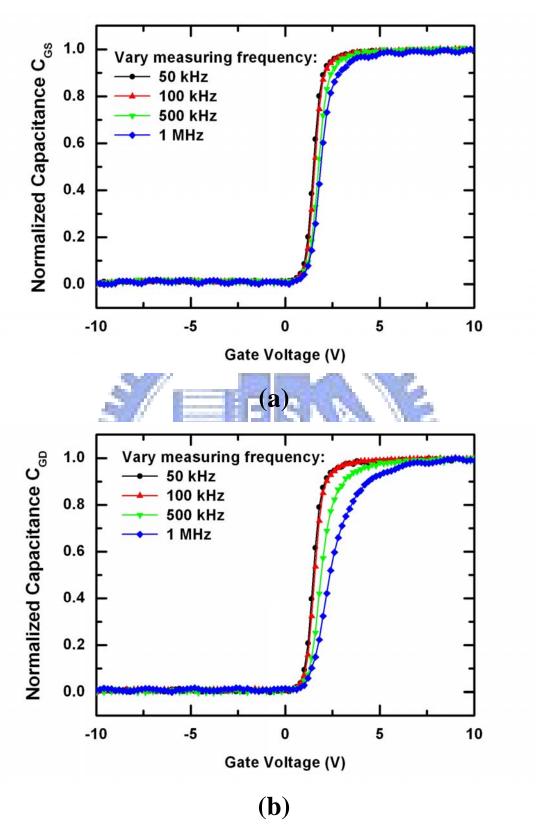

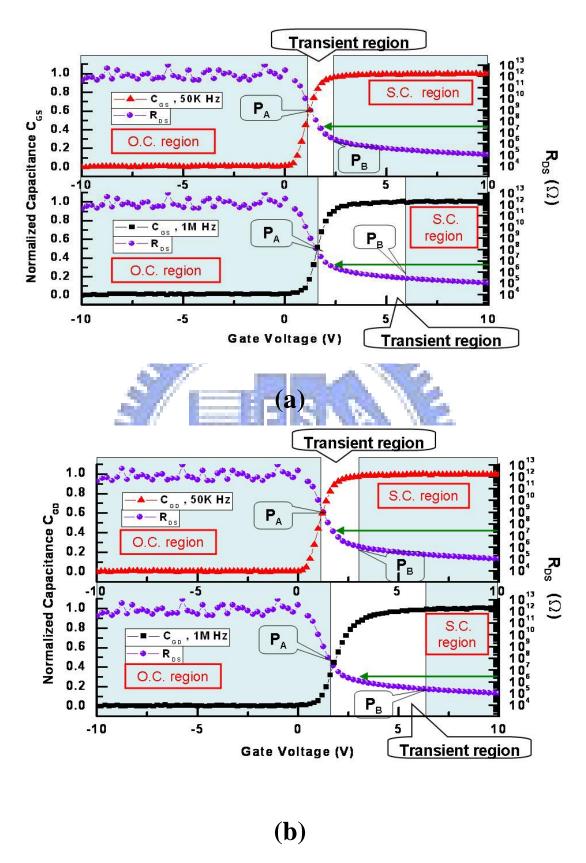

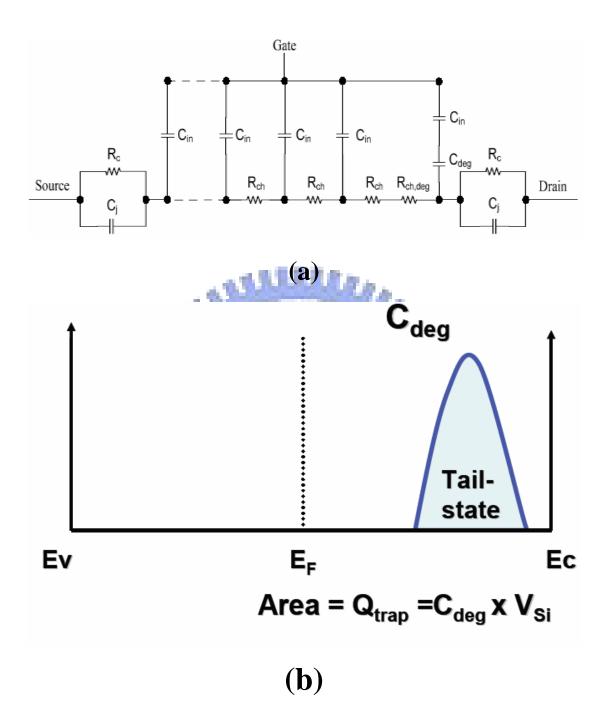

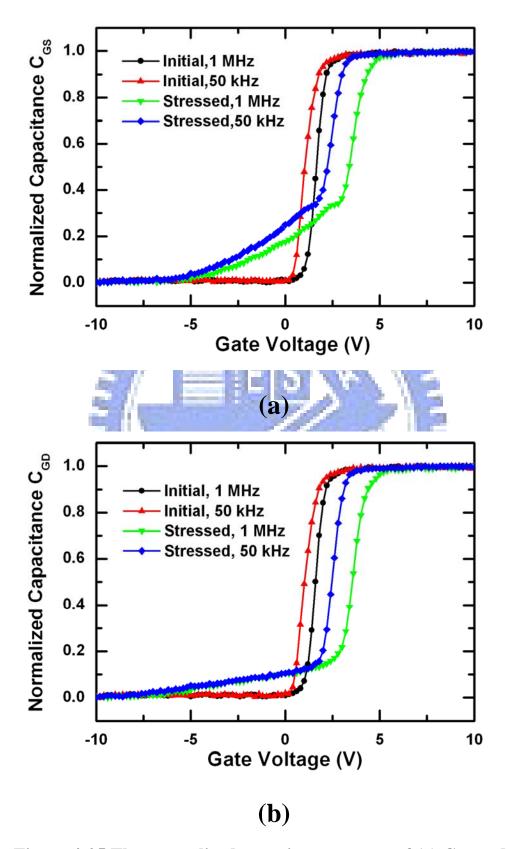

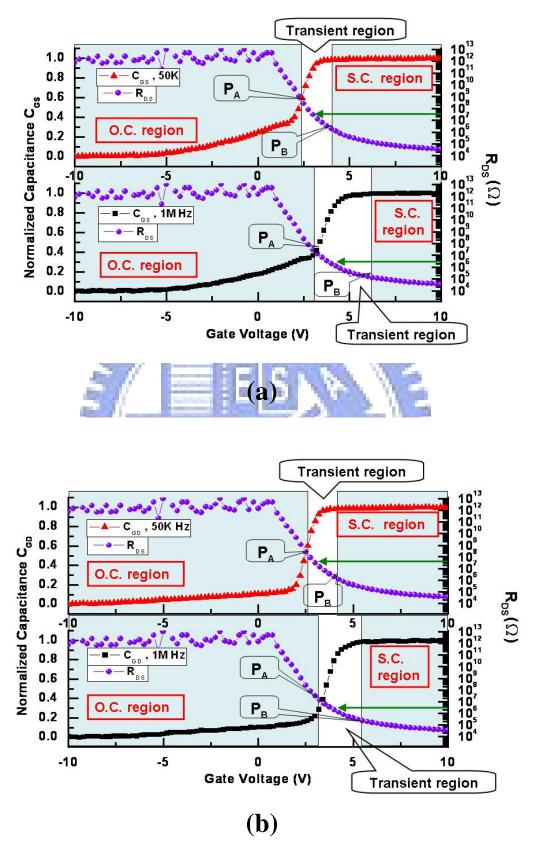

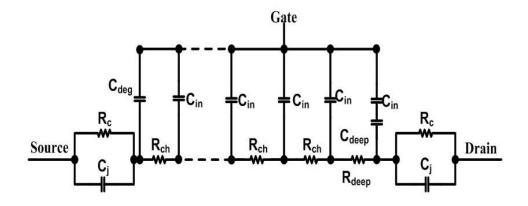

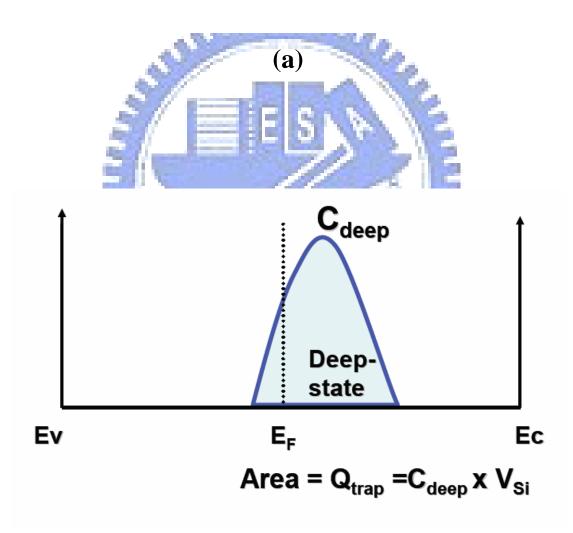

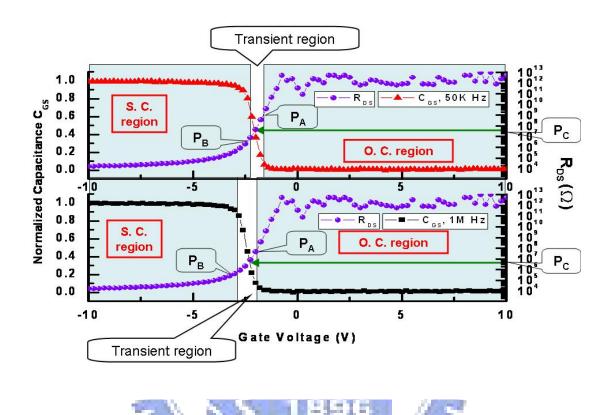

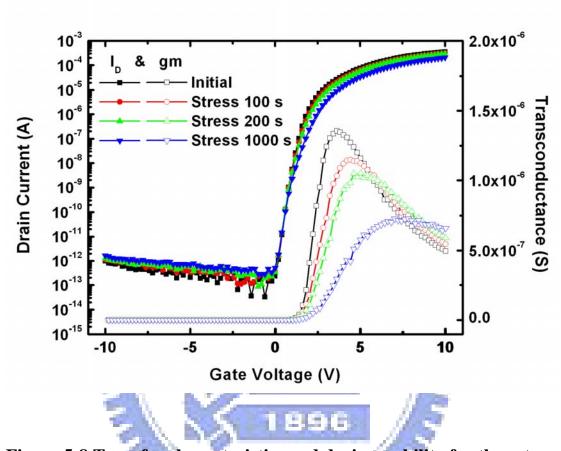

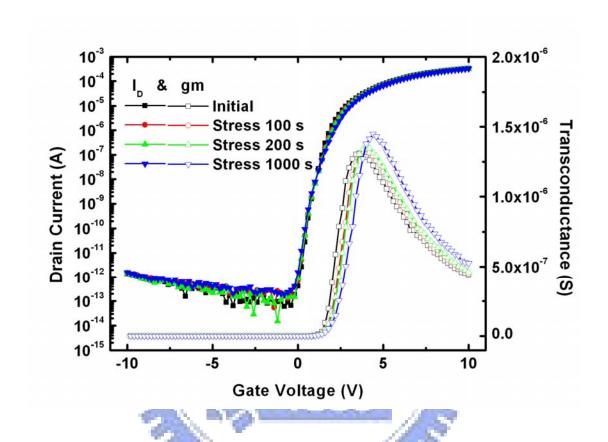

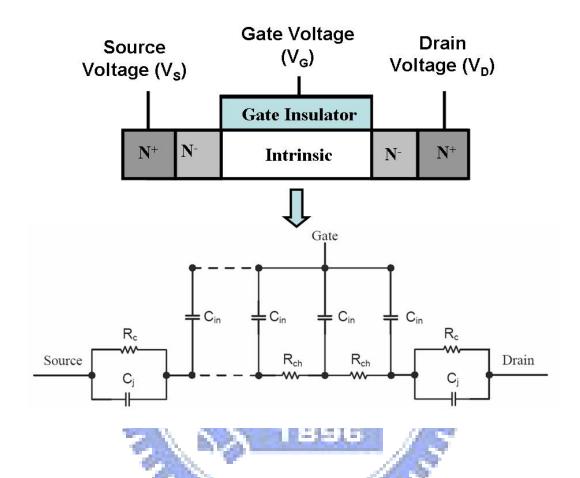

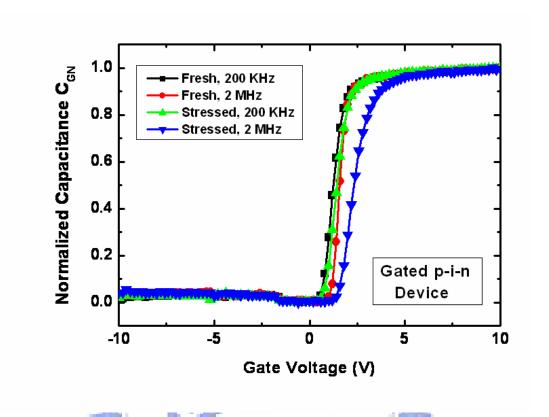

Then we focus on the temporal variation of poly-Si TFTs under various operation conditions. Here the temporal variation can simply correspond to the reliability issue under DC and AC operation, which would be respectively discussed in the separate chapters. For the DC operation section, we first review the two main degradation mechanisms for the poly-Si TFTs under DC operation, namely the hot carrier effect and the self heating effect. Though there have been so many papers on the device degradation behavior under these two stress conditions, there are very few papers about their capacitance behavior. We study the C-V behavior for the device after the two stress conditions and find that the simulation tool may be incomplete in properly describing the frequency dependence in the C-V curves. Thus we use another approach to infer the C-V curves from the readily-accessible I-V curves. Based on the proposed model composed of the gate insulator capacitance and channel resistance, we compare the magnitude of the capacitance term and the resistance term for the device's impedance and the critical point called P<sub>C</sub> is found to help distinguish the ON region and the OFF region in the C-V curves inferred from the I-V curves. Since the capacitance term is dependent on the measuring frequency, the position of the point P<sub>C</sub> also changes with the measuring frequency. Following the same manner, the C-V behavior for the device after the two stress conditions are examined and the corresponding circuit elements, possibly the capacitance or the resistance, are proposed respectively. Special discussion would be given on the capacitance behaviors for the n-type device after self-heating stress and the p-type after hot carrier stress since they both somehow show the increase of the capacitance for the lower gate voltage in C-V curves.

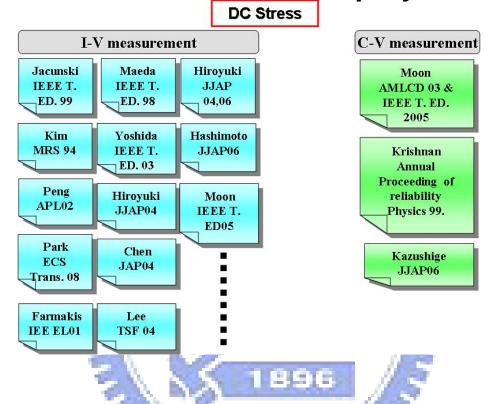

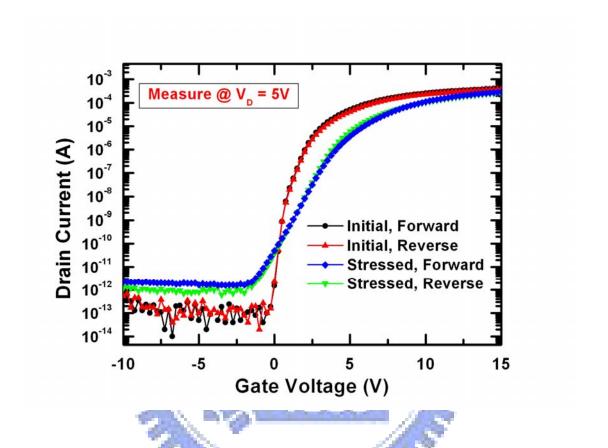

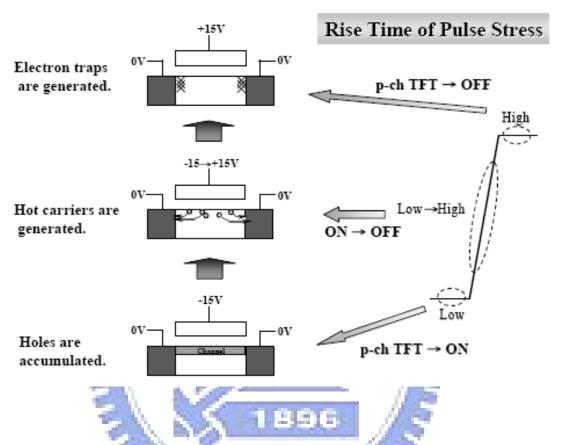

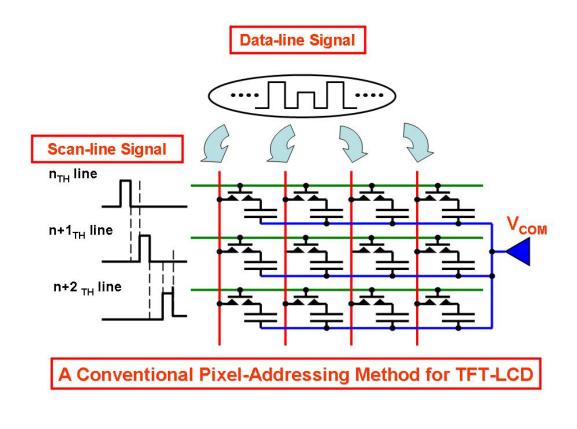

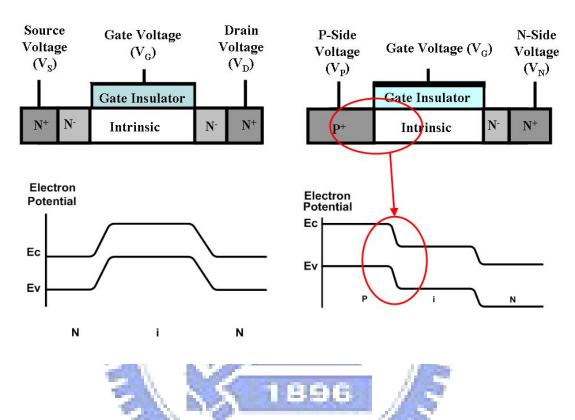

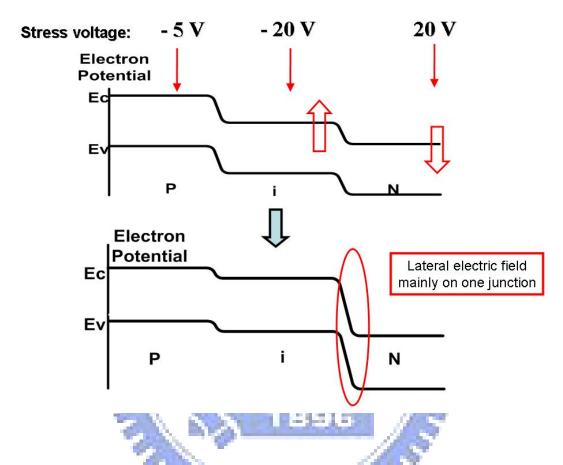

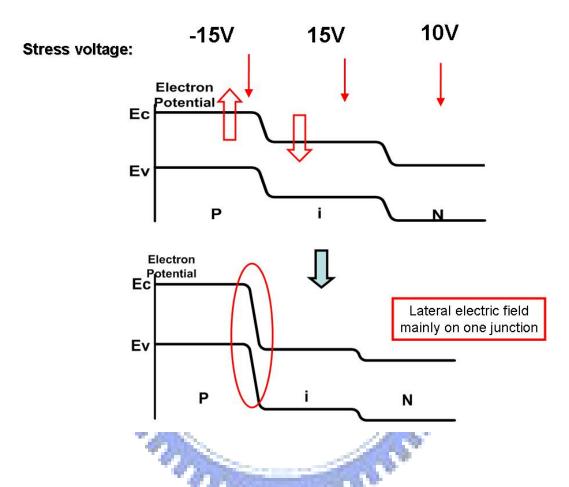

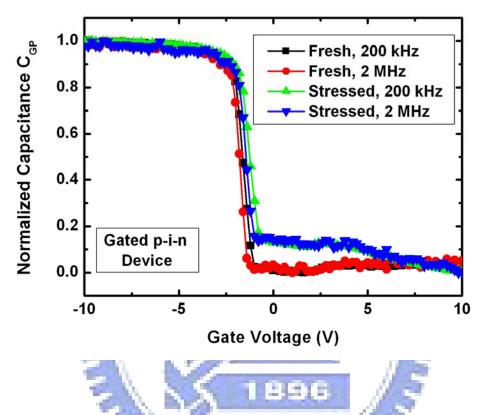

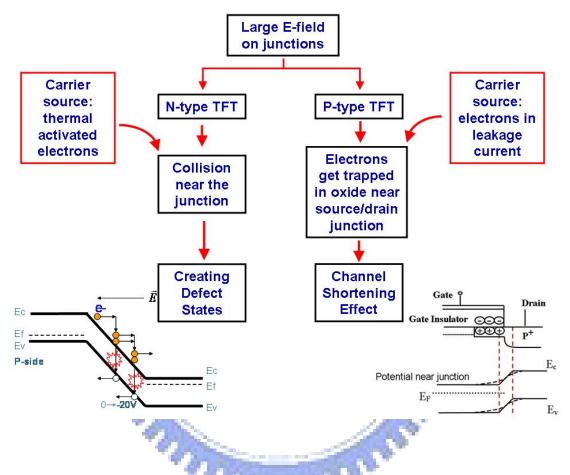

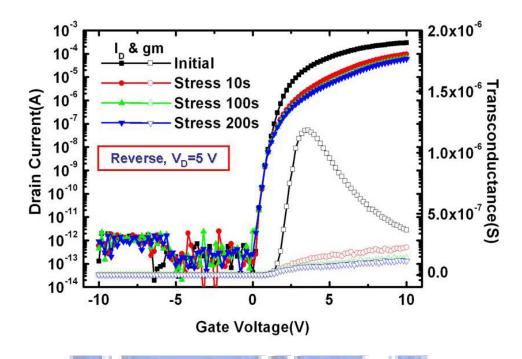

Next we study the reliability behavior for the device under gate dynamic operation. Started from the application, we find that in TFT-LCD applications the TFTs in the pixels mostly stay in the gate turned-off region with the drain signal dynamically toggling. However, there is almost no study of the reliability behavior on such operation condition. We consider the gate-to-source voltage difference V<sub>GS</sub> and the gate-to-drain voltage difference V<sub>GD</sub> and analogically study the reliability behavior for the gate voltage dynamically toggling in the OFF region while the source and drain electrodes are both grounded. The device shows mobility decrease in the I-V curves and shift as well as distortion in its C-V curves for the stressed n-type device, while for the p-type device the mobility increases and the OFF current decreases after stress. The dependency for the device degradation on the pulse parameters, namely the pulse range, the frequency and the duty ratio of the applied signal, is also studied. However, since the pulse voltage is all kept below its threshold voltage, there should be no channel carrier induced beneath the gate electrode and thus the degradation behavior could not be explained by the model proposed previously by Uraoka. At this point we resort to the circuit model again and one more time we discuss the impedance under such stress condition. It is then inferred that under the gate AC operation the channel resistance and the large electric field across the junctions could be the main degraded region. Nevertheless, such inference is hard

to probe and we use another test structure named the gated p-i-n device, in which the device has the similar structure to TFTs but one side of the doping is changed to make the device laterally resemble the p-i-n diodes. The feature for adopting such gated p-i-n device is that this device has the similar structure to the TFTs while the channel voltage can be set from one side of the electrodes. Thus, this enables us the capability of forming large electric field across one junction to simulate the condition of gate AC OFF region stress for poly-Si TFTs. Then, by examining the capacitance curves of the AC-stressed TFTs and the DC-stressed gated p-i-n devices after stress, the aforementioned mechanism is verified. The degradation in junction with the large electric field on it is thus found to be responsible for the degradation of gate dynamic operation in the OFF region and the discussion for the different behaviors for the n-type device and p-type device is also provided. Also the reliability behaviors under several other stress conditions are discussed. It is found that, no matter what the carrier source may be the inversion channel carriers, the leakage current or even the inversion channel carriers swept because the gate pulse is to be turned-off, once the large electric filed is across the junction, the carriers would more or less become the hot carrier and result in the similar degradation behavior. In other words, they can be categorized as the "generalized hot carrier effect." To summarize, the finding of the mechanism as well as the proposed circuit model should provide useful information for the understanding and evaluation of the temporal variation for poly-Si TFTs.

四年前的春天,2005 年四月底的一個凌晨,我一邊忙著準備博 士班入學口試的論文初稿,一邊看著王建民的大聯盟初登板。四年 來,王建民以自己的身手努力的在大聯盟裡可說是最毒舌最現實的洋 基隊裡掙得一席先發地位。其中有連勝,有連敗,也有長達十個月的 療傷。看著與自己年齡相當的人的奮鬥,也常讓我回想起過去這四年 的點滴。閉上雙眼,回想起許多過去在實驗室的時光,最先想起的, 是指導教授戴亞翔老師,感謝老師,雖然常常在研究上與我有不同意 見,但感謝老師尊重我的意見,也感謝老師器重我,讓我在研究生涯 裡也有出去看看實驗室外的世界的機會; 感謝老師鼓勵我, 勇敢挑戰 千里馬計畫與參加幾次的業界實習,讓我看到國外的學界的生活,也 看到自己的東西是可以如何的被應用於國內的業界。也感謝老師在學 業的指導之外,向我說明如何帶領學弟妹作研究,與如何看待、度過 在人生裡所面對的波折。

要感謝的老師還有同是在交大光電系所裡的冉曉雯老師與劉柏 村老師以及在中山物理系的張鼎張老師;冉老師與張老師是帶領我進 入TFT 研究的啟蒙者,而劉老師則是常向他請教關於 TFT 製程方面的 知識。感謝三位老師有耐心且詳盡的解說、不厭其煩的解答我許多問 題。此外,也要感謝在千里馬期間指導我很多的德州農工大學化工系 郭育教授,感謝您的指導並允許我使用實驗室裡的許多製程機台,雖 然時間只有短短十個月,但是實際的操作經驗已讓我受益良多。老師 在我離開德州前常向我提起的"眼界"問題,我也時時放在心上。

要感謝實驗室裡的許多學長:清大電子所的陳世青學長、交大光電所的顏國錫、黃震鑠、李弘緯及吳興華學長,感謝學長們的鼓勵與協助,讓我在實驗上感到迷惑時能順利找到研究的方向。此外,在德州農工化工系裡的許多學長姐,包含同是交大出來的林政漢(Alou)與楊佳翰學長。感謝 Alou 協助我處理了許多生活上的大小雜事,而佳翰學長,你的廚藝幫我解了不少鄉愁的時刻!很懷念過節時和大家一起聚在一起煮幾樣台灣菜再窩在一起打麻將的時光。也感謝實驗室裡的其他學長姐:雷雨(Rain)、Mary Coan、Helinda、Guojun等人在實驗上的協助。

同時也要感謝曾經一起同甘共苦的夥伴們,同實驗室的彥甫、隔 壁實驗室的一德與皓彥,冉老師實驗室的士欽、政偉等同學,一起分 享投稿與實驗的甘苦;也要感謝實驗室學弟妹在過去所提供的幫助: 感謝國烽、鈺函、可欽、建焜、彥邦、育德,感謝你們在課於能夠抽 空進行繁重的實驗,建立實驗室元件特性變動的資料庫,感謝婉萍支 援統計學以及程式編寫方面的知識。感謝鈺函、建焜、皓麟、虹娟、 俊文、偉倫、柏廷與騰瑞,感謝你們協助研究元件的可靠度模型。也 感謝過去曾和大家共同度過的歡樂時光。

最後,絕不能忘記的,要感謝我的父母多年來辛苦的栽培與教 誨,讓我自由的選擇,給我最大的關懷,無條件的支持我的決定,使 我無後顧之憂的完成我的博士學位,如果我有任何的榮耀,都是因為 有你們無可取代的存在,感謝你們的鼓勵、陪伴、尊重與信任。

這篇畢業論文雖然看似內容很多,但沒有大家的幫忙我一個人是無法完成這些內容的;感謝過去大家的陪伴與幫忙,這篇論文才得以完成。舞台的布幕即將降下,在交大的生活同時也代表我的學生生涯即將結束。感謝一切,才讓我的博士研究生涯如此順利而繽紛。

僅以此文獻給我的老師、家人與好友。

士哲 09 初夏 於風城新竹

## **Contents**

| Abstract (C | Chinese)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | i      |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Abstract (E | English)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | iv     |

| Acknowled   | gements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | viii   |

| Contents    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | xi     |

| Figure Cap  | tions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | xiii   |

|             | NAME OF THE PARTY | xxii   |

| Chapter 1   | 1-2 Review and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3<br>5 |

| Chapter 2   | 2-1 Device Fabrication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |

| Chapter 3   | Characterization of Spatial Variation of Poly-Si TFTs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

|             | 3-1 Review and Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20     |

|             | 3-2 Classification and Characterization of Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23     |

|             | 3-3 Impacts and Insights of Device Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

|             | 3-3-1 Impacts of Device Variation on Circuit Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 26     |

|             | 3-3-2 Insights of Device Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32     |

|             | 3-4 Summaries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38     |

| Chapter 4 Characterization of Temporal Variation of Poly-Si TFTs: under                                         |

|-----------------------------------------------------------------------------------------------------------------|

| DC Operation                                                                                                    |

| 4-1 Review and Motivation69                                                                                     |

| 4-2 Reliability Behavior under DC Operation: n-type Device73                                                    |

| 4-3 Reliability Behavior under DC Operation: p-type Device79                                                    |

| 4-4 Comparison and Discussion82                                                                                 |

| 4-5 Summaries83                                                                                                 |

| Chapter 5 Characterization of Temporal Variation of Poly-Si TFTs: under AC Operation  5-1 Review and Motivation |

| Chapter 6 Summaries and future work184                                                                          |

| References186                                                                                                   |

| Vita194                                                                                                         |

| Publication List195                                                                                             |

## **Figure Captions**

|  | Cha | pter | 1 |

|--|-----|------|---|

|--|-----|------|---|

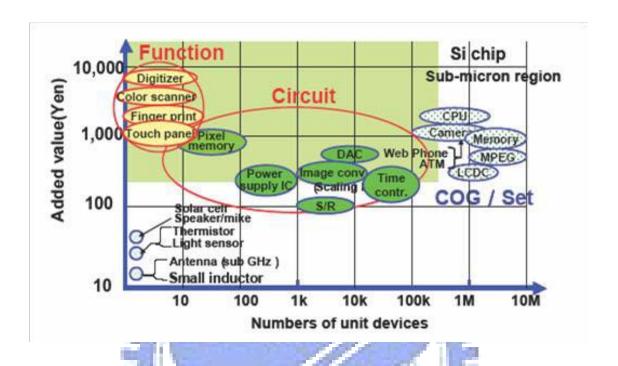

| Figure 1-1 The possible value-added functions for the poly-Si TFT circuits7            |

|----------------------------------------------------------------------------------------|

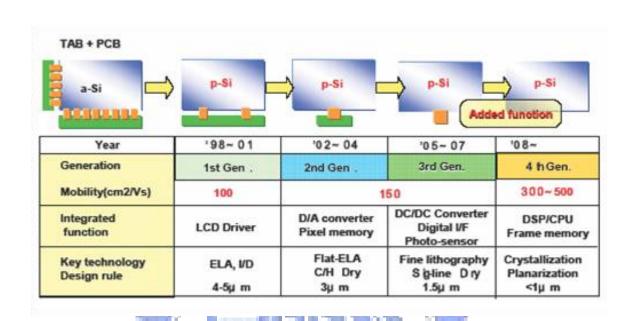

| Figure 1-2 The roadmap and the perspectives for the poly-Si TFT development8           |

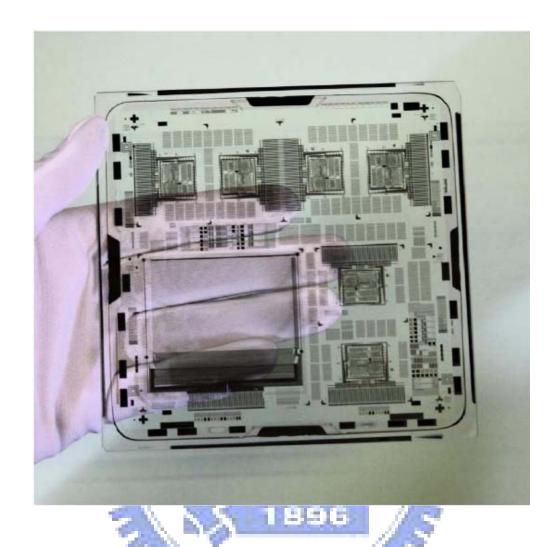

| Figure 1-3 The system on glass prototype with the poly-Si TFT technology from          |

| Sharp9                                                                                 |

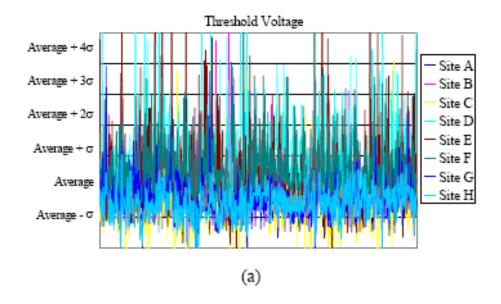

| Figure 1-4 Device parameters for poly-Si TFTs in which the serious variation           |

| occurs10                                                                               |

| Figure 1-5 Comparison and summary for the previous reliability works on the I-V and    |

| C-V behaviors for poly-Si TFTs11                                                       |

| Figure 1-6 Comparison and summary for the previous works on the reliability            |

| behaviors for poly-Si TFTs under DC and AC operation12                                 |

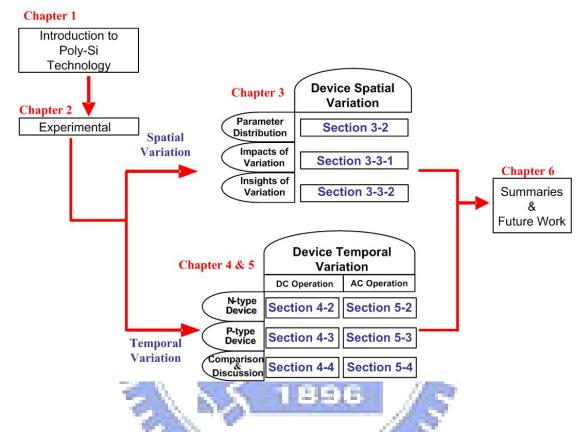

| Figure 1-7 The figure illustrating the structure of this dissertation                  |

|                                                                                        |

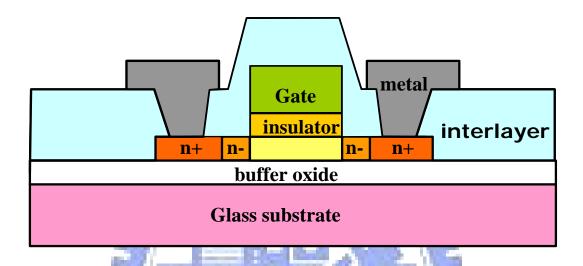

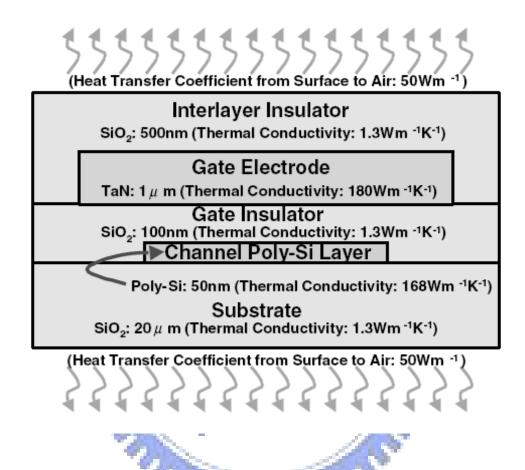

| Fig. 2-1 The cross section view of the n-type poly-Si TFTs used in this work18         |

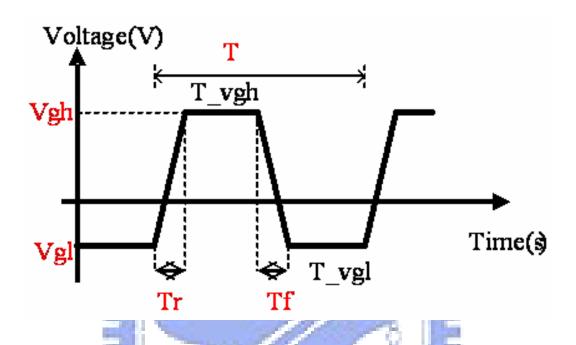

| Fig. 2-2 The figure illustrating the basic parameters of the AC pulse19                |

| Chapter 3                                                                              |

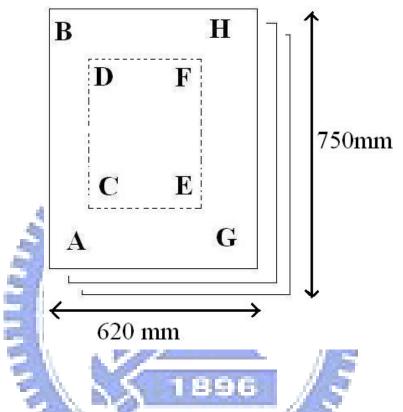

| Figure 3-1 The devices locate on the eight spots on different glasses are measured and |

| extracted for studying the variation39                                                 |

| Figure 3-2 The figure illustrating the design issues as well as the device variation   |

| issue40                                                                                |

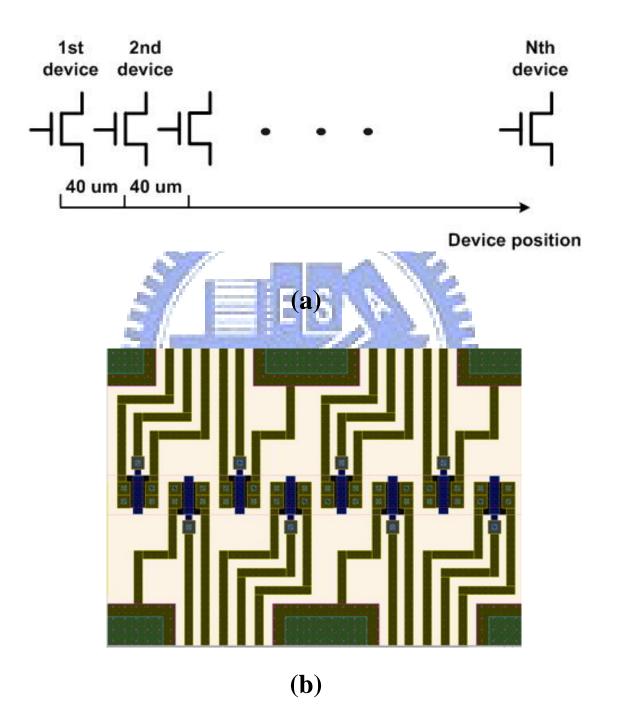

| Figure 3-3 (a) The figure illustrating the proposed crosstie layout. (b) The captured  |

| picture of the proposed layout41                                                       |

| Figure 3-4 (a) The $V_{TH}$ and (b) the mobility distribution of the measured crosstie             |

|----------------------------------------------------------------------------------------------------|

| devices for both n-type and p-type devices42                                                       |

| Figure 3-5 The distribution of the device parameters with distance for (a) $V_{\text{TH}}$ and (b) |

| mobility43                                                                                         |

| Figure 3-6 The figure illustrating the large signal (long-range variation) and the small           |

| signal (micro variation) of the device parameters44                                                |

| Figure 3-7 The data and proposed model describing the $V_{\text{TH}}$ variation for the (a)        |

| n-type and (b) p-type devices45                                                                    |

| Figure 3-8 The data and proposed model describing the mobility variation for the (a)               |

| n-type and (b) p-type devices46                                                                    |

| Figure 3-9 The conventional structure of the differential pair circuit47                           |

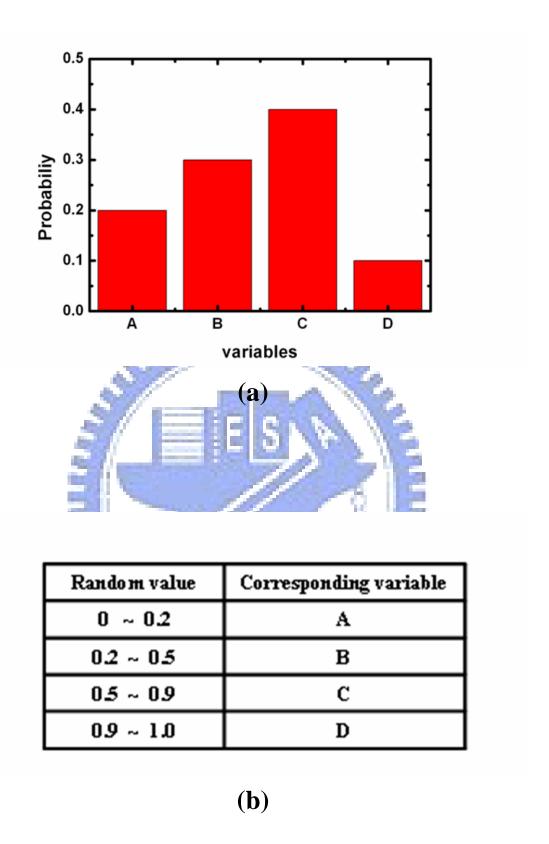

| Figure 3-10 (a) The simple distribution for the variable mapping. (b) A look up table              |

| for the variable mapping base48                                                                    |

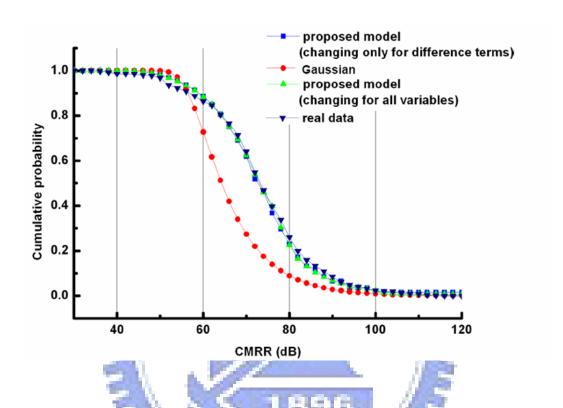

| Figure 3-11 The cumulative distribution for the CMRR value of differential pair with               |

| different device parameter model49                                                                 |

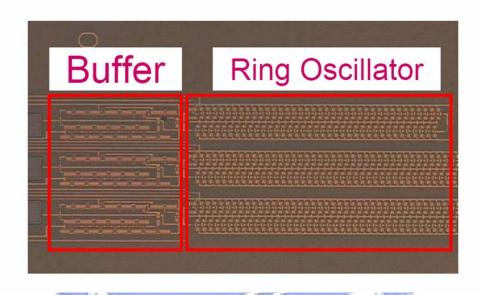

| Figure 3-12 The photograph of the fabricated ring oscillator circuits50                            |

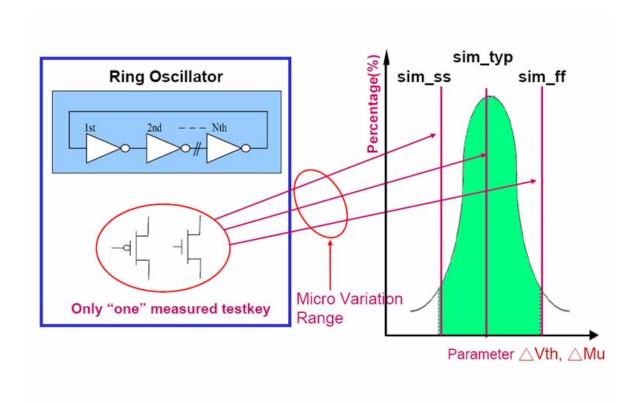

| Figure 3-13 The figure illustrating the upper and lower bound of the device variation              |

| model51                                                                                            |

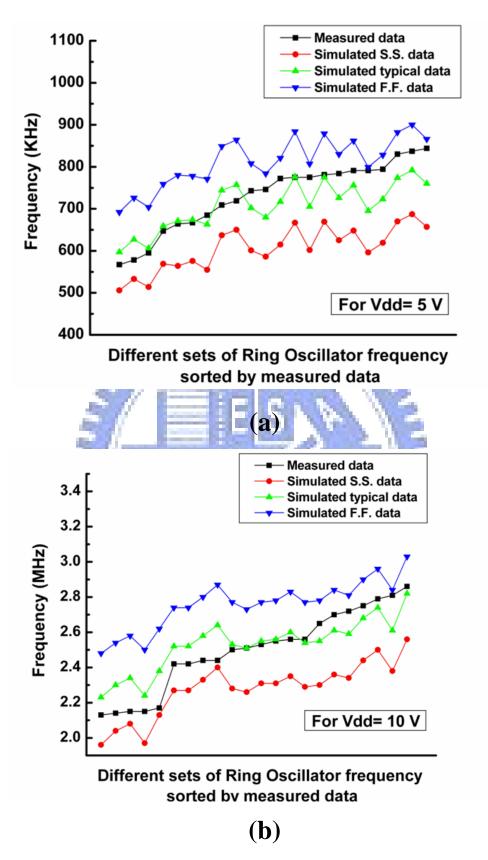

| Figure 3-14 The simulated and measured ring oscillator operating frequency with (a)                |

| operating voltage 5 V and (b) operating voltage 10 V52                                             |

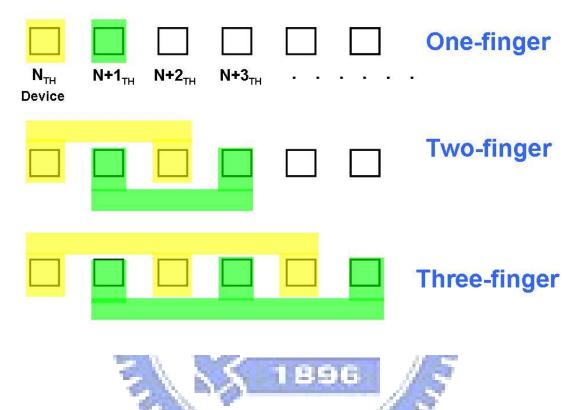

| Figure 3-15 The interdigitated connection with different finger numbers53                          |

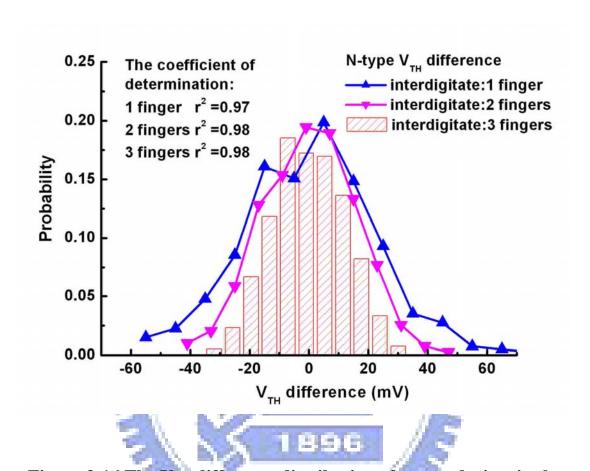

| Figure 3-16 The $V_{\text{TH}}$ difference distribution of n-type devices in the interdigitated    |

| layout with different finger numbers54                                                             |

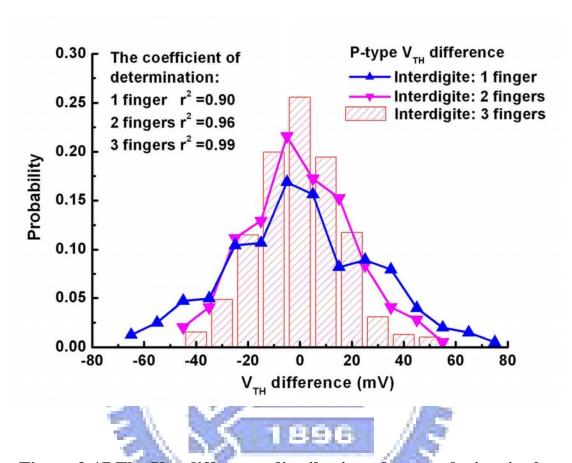

| Figure 3-17 The $V_{\text{TH}}$ difference distribution of p-type devices in the interdigitated    |

| layout with different finger numbers55                                                             |

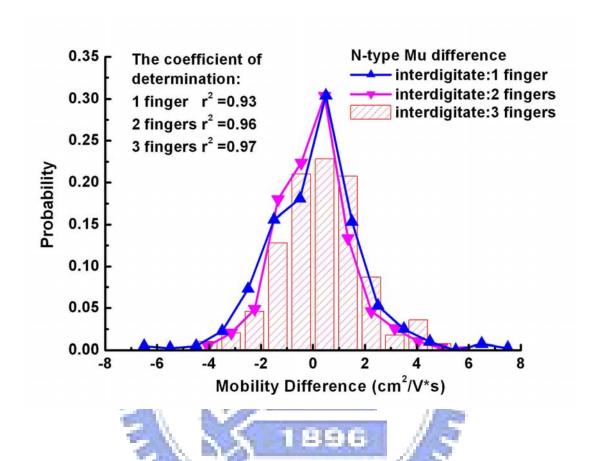

| Figure 3-18 The mobility difference distribution of n-type devices in the interdigitated           |

| layout with different finger numbers56                                                                                                                                                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

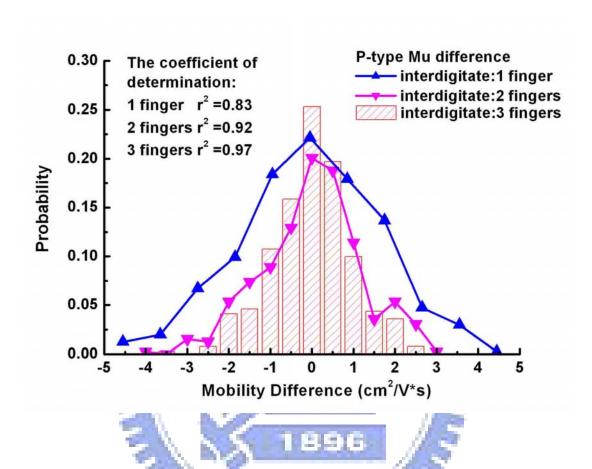

| Figure 3-19 The mobility difference distribution of p-type devices in the interdigitated                                                                                                 |

| layout with different finger numbers57                                                                                                                                                   |

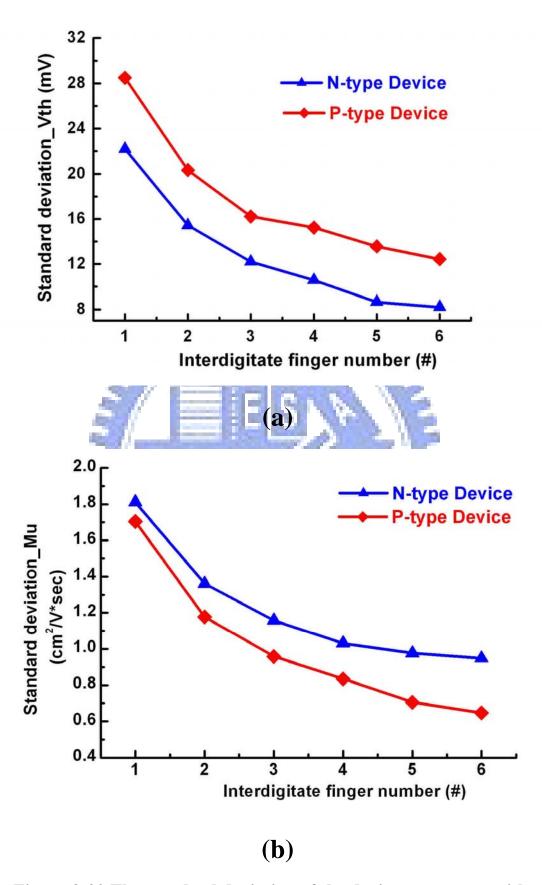

| Figure 3-20 The standard deviation of the device parameter with different interdigit                                                                                                     |

| finger number for (a) $V_{TH}$ and (b) mobility58                                                                                                                                        |

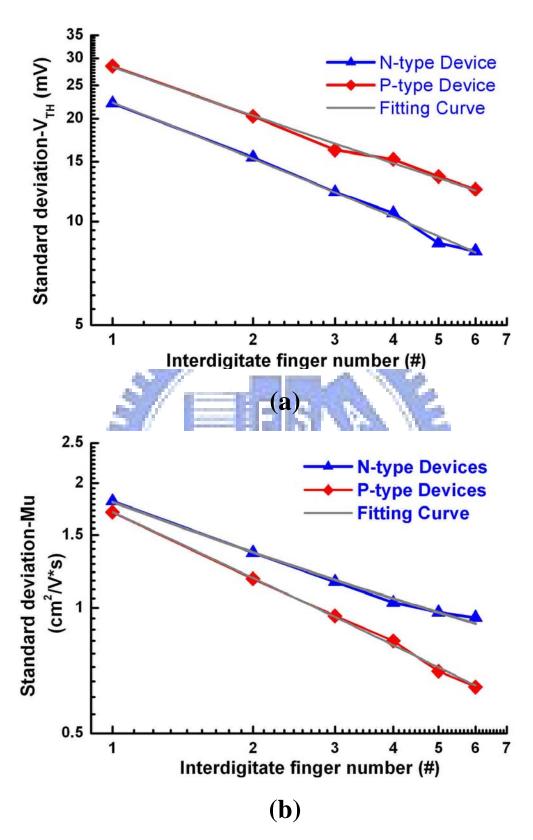

| Figure 3-21 The log-scale standard deviation of the device parameter with interdigit                                                                                                     |

| finger number and the fitting curve for (a) $V_{\text{TH}}$ and (b) mobility59                                                                                                           |

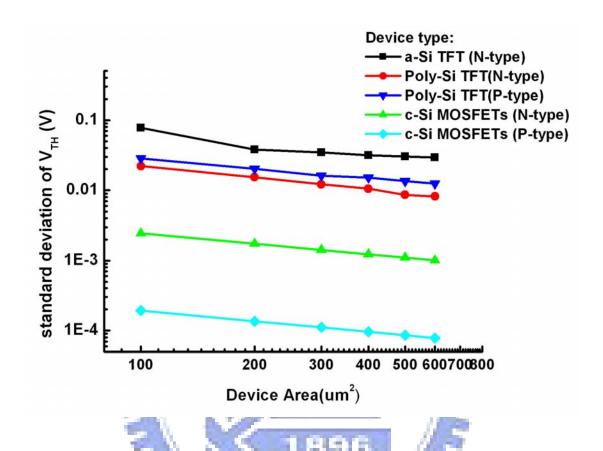

| Figure 3-22 The standard deviation of $V_{TH}$ for different types of devices and for both                                                                                               |

| n-type and p-type devices60                                                                                                                                                              |

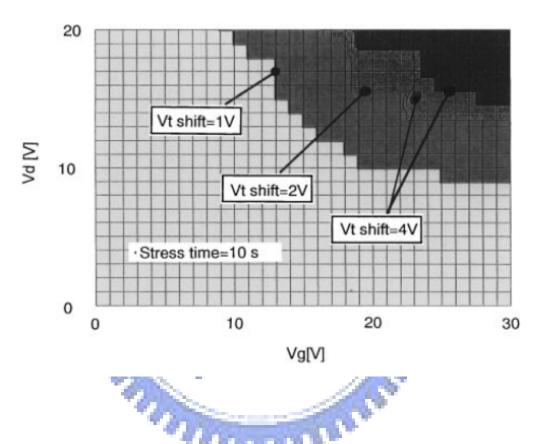

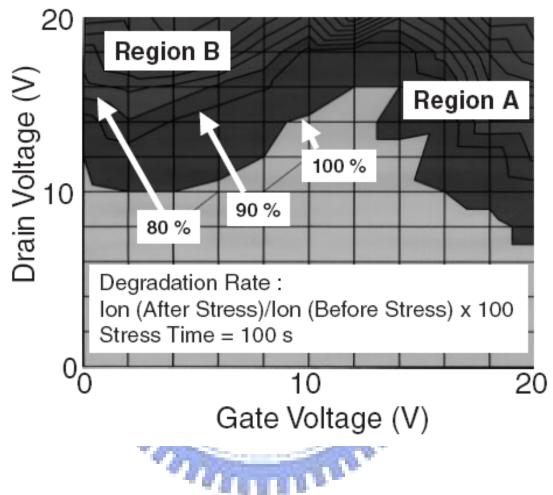

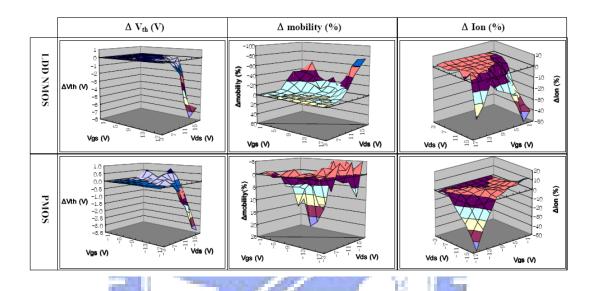

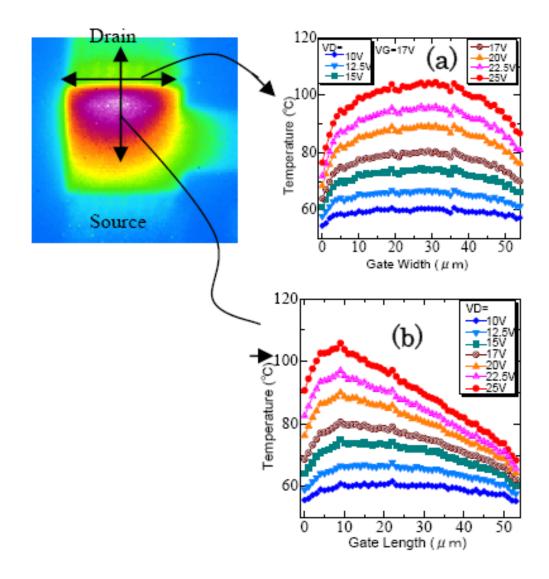

| Chapter 4  Figure 4-1 The threshold voltage shift under various stress conditions in the stress map                                                                                      |

| heating stress                                                                                                                                                                           |

| Si TFTs88                                                                                                                                                                                |

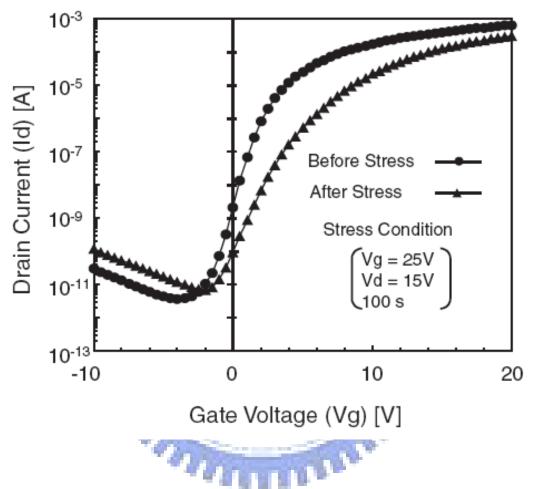

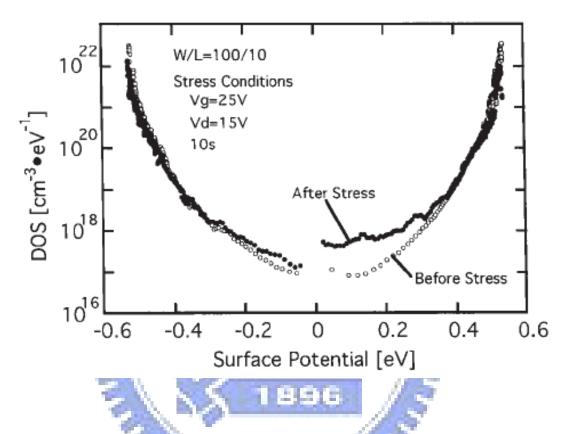

| Figure 4-6 The transfer characteristics for the n-type device after self heating stress-89  Figure 4-7 The density of states (DOS) for the device before and after self heating stress90 |

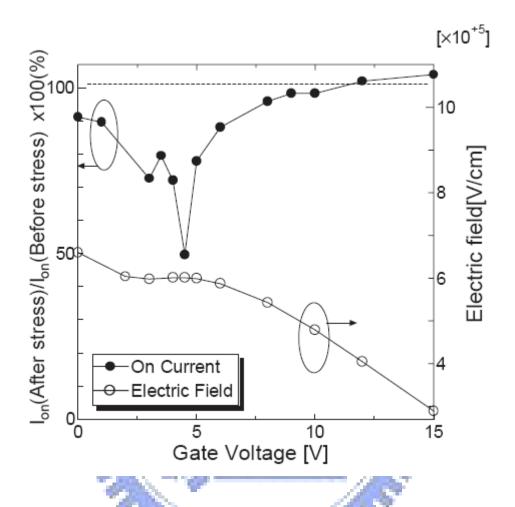

| Figure 4-8 The ON current degradation and the electric field for the device under hot                                                                                                    |

| carrier stress with various gate voltages91                                                                                                                                              |

| outilet buloob with various face voltages                                                                                                                                                |

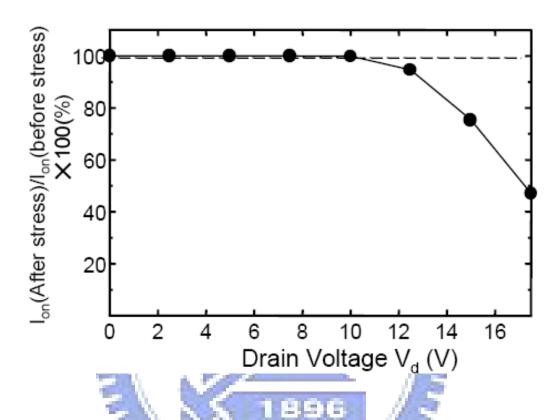

| Figure 4-9 The ON current degradation for the device under hot carrier stress with                          |

|-------------------------------------------------------------------------------------------------------------|

| various drain voltages92                                                                                    |

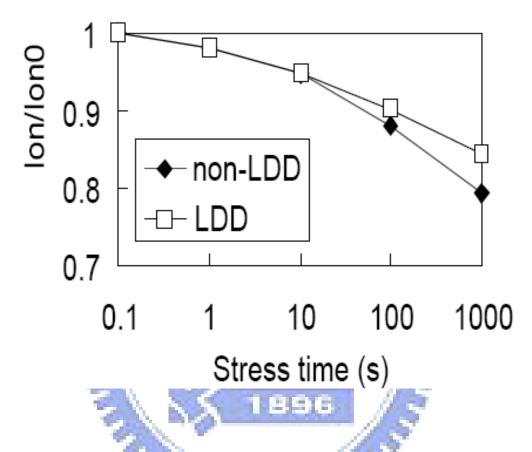

| Figure 4-10 The ON current degradation for the device under hot carrier stress with                         |

| and without the LDD structure93                                                                             |

| Figure 4-11 The transfer characteristics for the n-type device after hot carrier stress-94                  |

| Figure 4-12 The transfer characteristics for the p-type device after hot carrier stress-95                  |

| Figure 4-13 The proposed mechanism for the increase of the mobility96                                       |

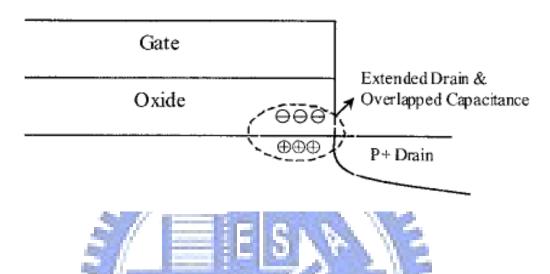

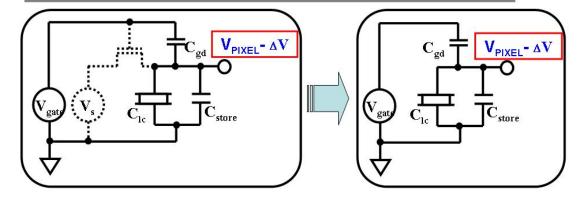

| Figure 4-14 The kick-back voltage in addressing the pixel voltage in TFT-LCD                                |

| panels97                                                                                                    |

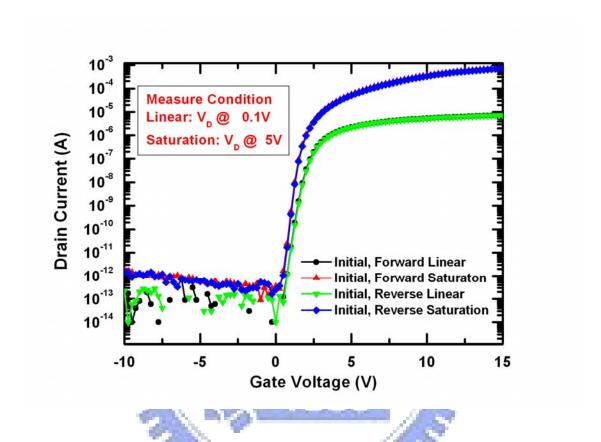

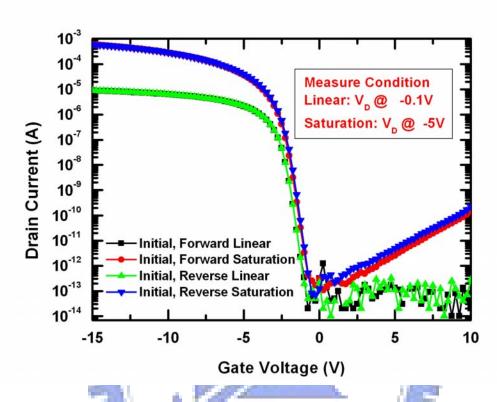

| Figure 4-15 The transfer characteristics for the fresh n-type device98                                      |

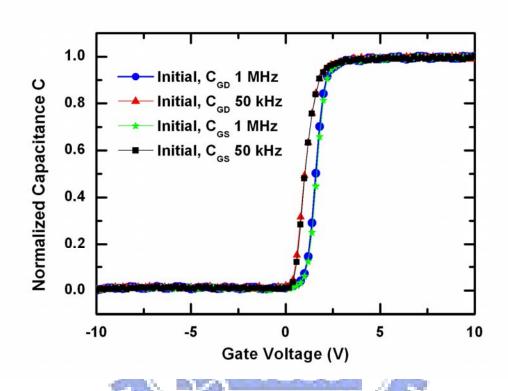

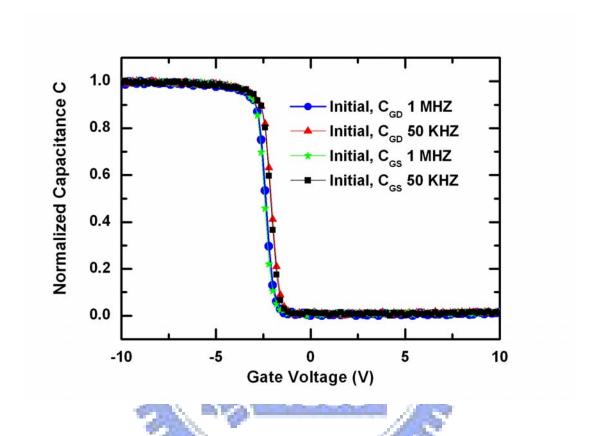

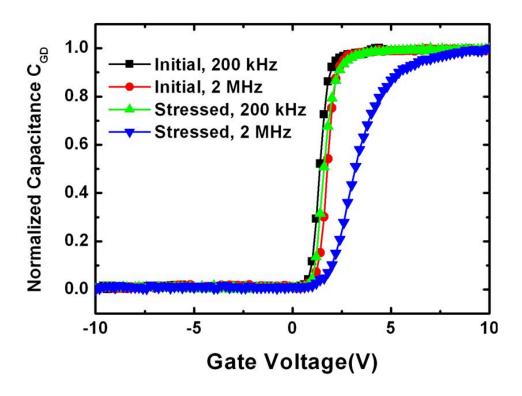

| Figure 4-16 The normalized capacitance curves for the fresh n-type device99                                 |

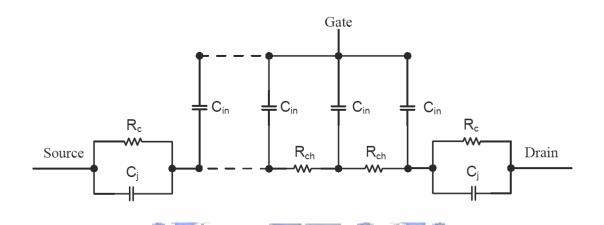

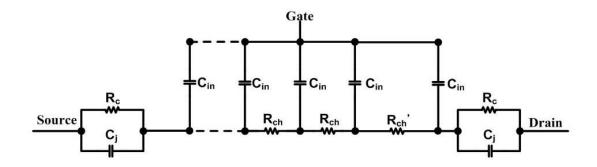

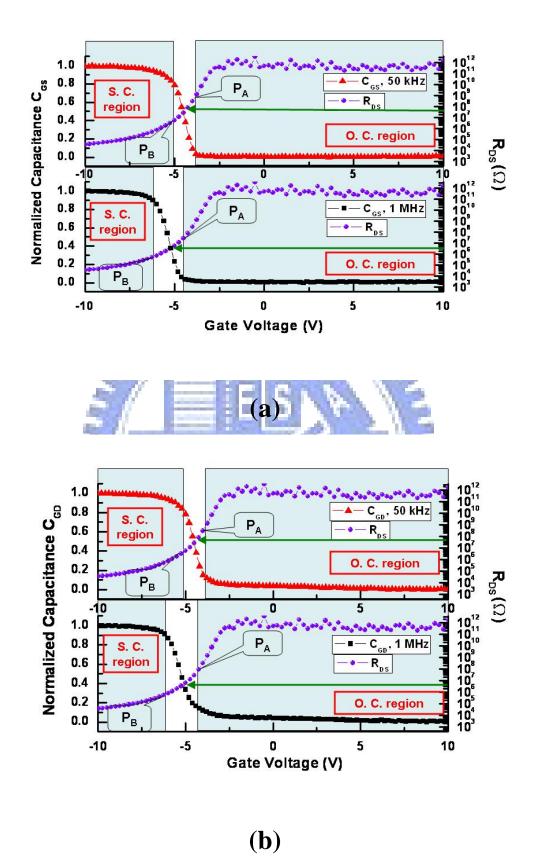

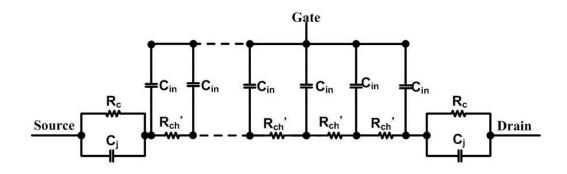

| Figure 4-17 The proposed circuit model for poly-Si TFTs100                                                  |

| Figure 4-18 The R <sub>DS</sub> curves V.S. capacitance curves for the fresh device101                      |

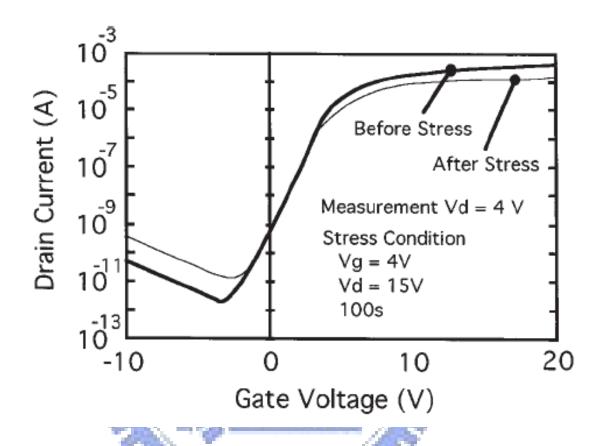

| Figure 4-19 The transfer characteristics for the n-type device before and after hot                         |

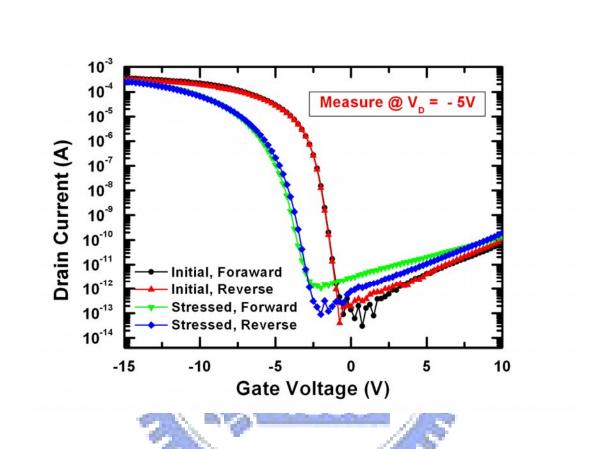

| carrier stress102                                                                                           |

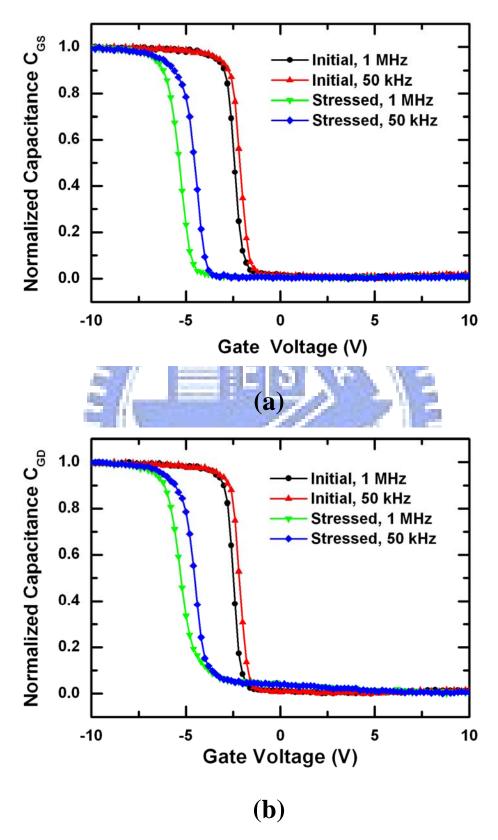

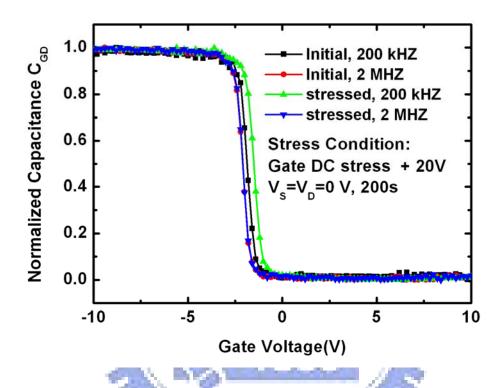

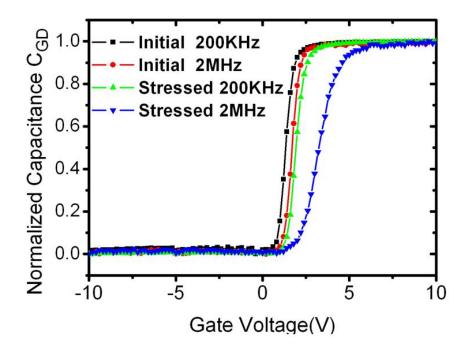

| Figure 4-20 The normalized capacitance curves of (a) $C_{GS}$ and (b) $C_{GD}$ curves for the               |

| device before and after hot carrier stress103                                                               |

| Figure 4-21 The normalized capacitance curves of (a) $C_{GS}$ and (b) $C_{GD}$ curves for the               |

| device after hot carrier stress with various measuring frequencies104                                       |

| Figure 4-22 The $R_{DS}$ curves V.S. the (a) $C_{GS}$ and (b) $C_{GD}$ curves for the device after          |

| hot carrier stress105                                                                                       |

| Figure 4-23 (a) the proposed circuit model for the device after hot carrier stress and (b)                  |

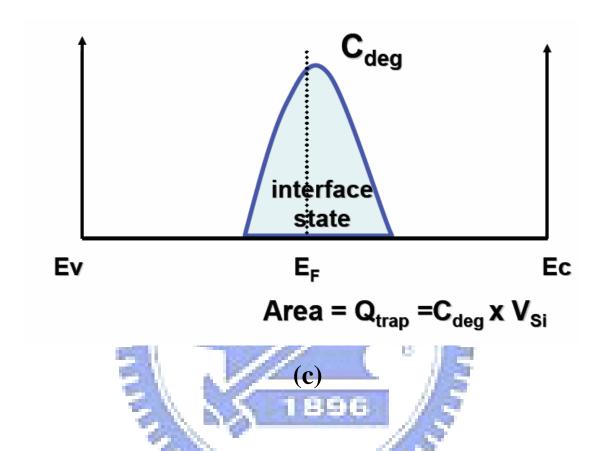

| the figure illustrating the corresponding location of $C_{\text{deg}}$ in the bandgap106                    |

| Figure 4-24 The transfer characteristics for the n-type device before and after self                        |

| heating stress107                                                                                           |

| Figure 4-25 The normalized capacitance curves of (a) C <sub>GS</sub> and (b) C <sub>GD</sub> curves for the |

| device before and after self heating stress108                                                         |

|--------------------------------------------------------------------------------------------------------|

| Figure 4-26 The $R_{DS}$ curves V.S. the (a) $C_{GS}$ and (b) $C_{GD}$ curves for the device after     |

| self heating stress109                                                                                 |

| Figure 4-27 (a) The proposed circuit model for the device after hot carrier stress and                 |

| (b) the figure illustrating the corresponding location of the $C_{\text{deep}}$ in the bandgap and (c) |

| the location of the $C_{\text{deg}}$ in the bandgap111                                                 |

| Figure 4-28 The transfer characteristics for the fresh p-type poly-Si TFT112                           |

| Figure 4-29 The normalized capacitance curves for the fresh p-type device113                           |

| Figure 4-30 The $R_{DS}$ curves V.S. capacitance curves for the fresh p-type device114                 |

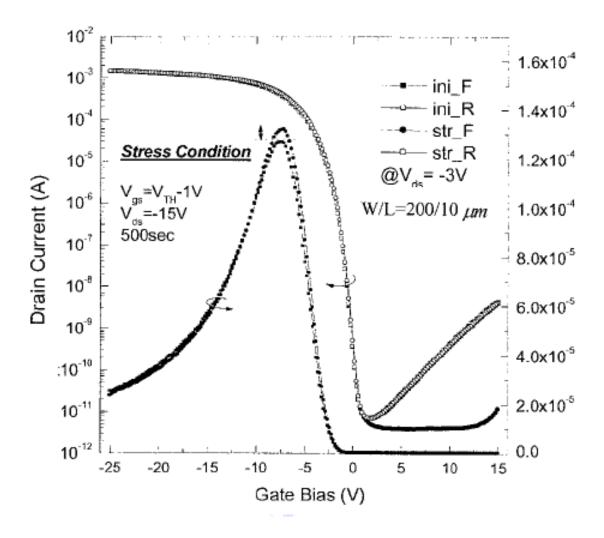

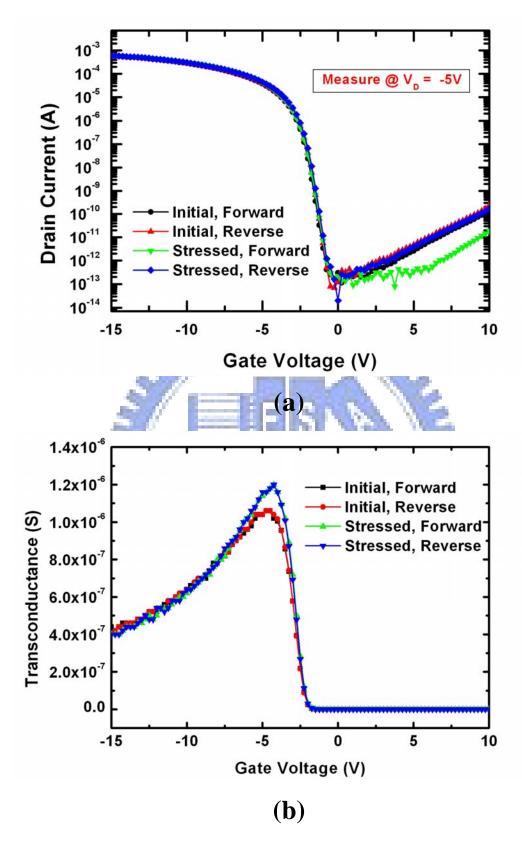

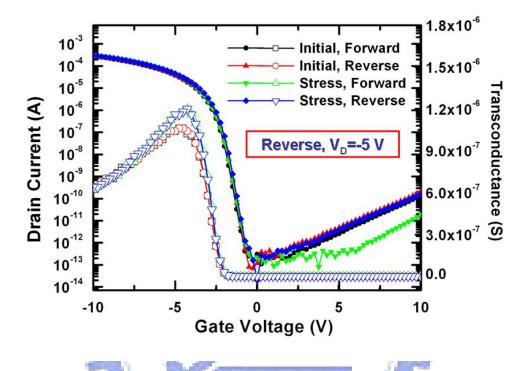

| Figure 4-31 (a) The transfer characteristics and (b) the transconductance curves for                   |

| the p-type device before and after hot carrier stress115                                               |

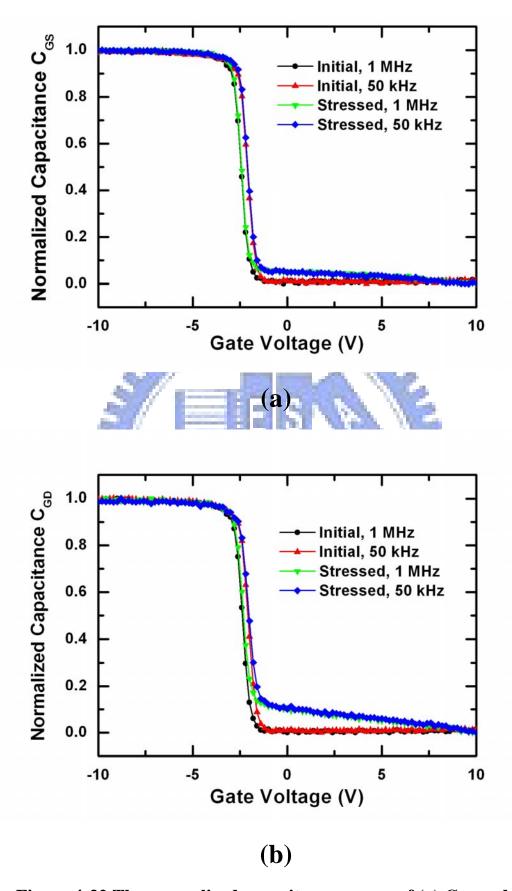

| Figure 4-32 The normalized capacitance curves of (a) $C_{GS}$ and (b) $C_{GD}$ curves for the          |

| p-type device before and after hot carrier stress116                                                   |

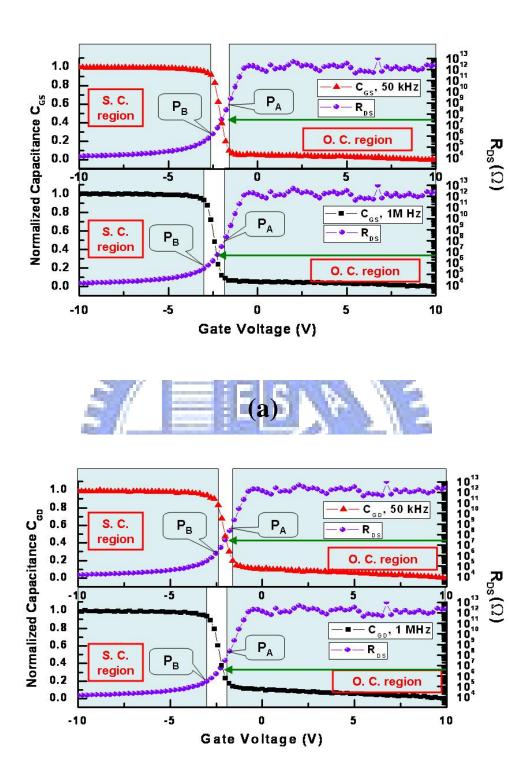

| Figure 4-33 The $R_{DS}$ curves V.S. the (a) $C_{GS}$ and (b) $C_{GD}$ curves for the p-type device    |

| after hot carrier stress117                                                                            |

| Figure 4-34 The proposed circuit model for the p-type device after hot carrier                         |

| stress118                                                                                              |

| Figure 4-35 The transfer characteristics for the p-type poly-Si TFT before and after                   |

| self heating stress119                                                                                 |

| Figure 4-36 The normalized capacitance curves of (a) $C_{GS}$ and (b) $C_{GD}$ curves for the          |

| device before and after self heating stress120                                                         |

| Figure 4-37 The $R_{DS}$ curves V.S. the (a) $C_{GS}$ and (b) $C_{GD}$ curves for the p-type device    |

| after self heating stress121                                                                           |

| Figure 4-38 The proposed circuit model for the p-type device after self heating                        |

| stress122                                                                                              |

### Chapter 5

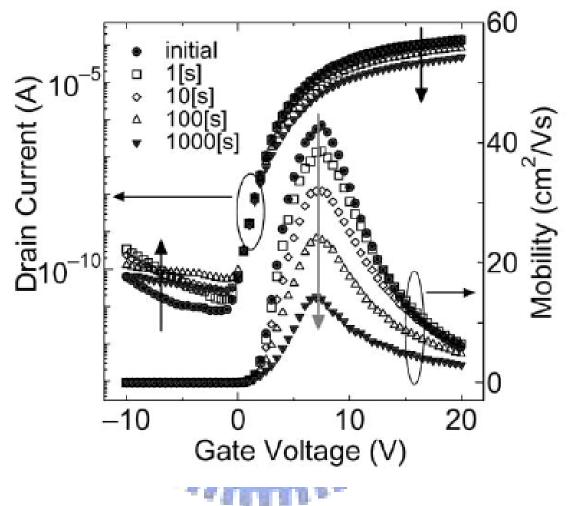

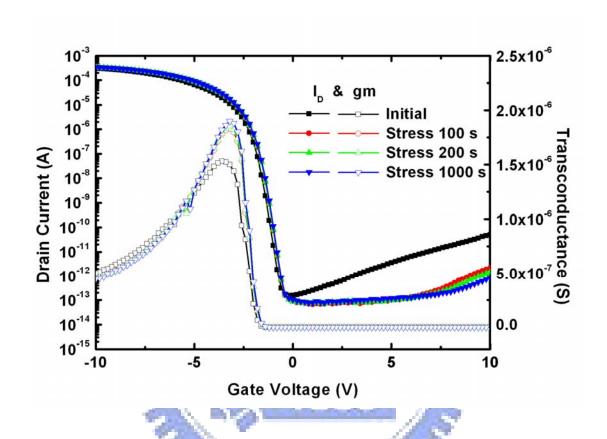

| Figure 5-1 Transfer characteristics and device mobility for the n-type device under the         |

|-------------------------------------------------------------------------------------------------|

| gate dynamic stress ranging between + 15 V and – 15 V 141                                       |

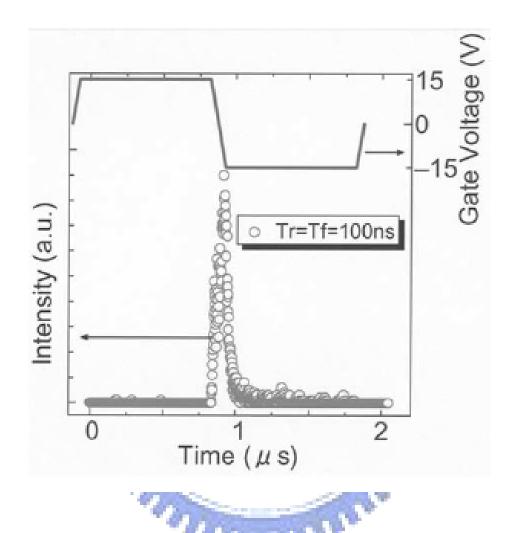

| Figure 5-2 The emission microscope data for the device under gate dynamic stress                |

| ranging between + 15 V and – 15 V142                                                            |

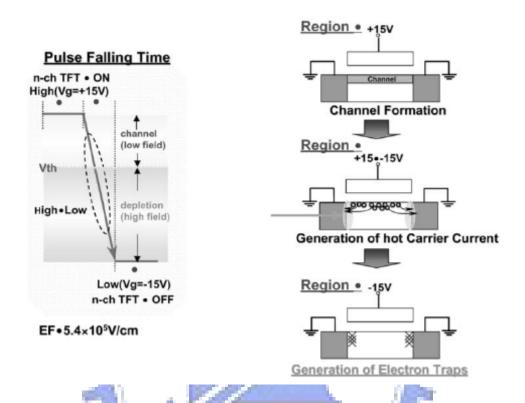

| Figure 5-3 The model describing the mechanism for the degradation of n-type device              |

| under the gate dynamic stress ranging between + 15 V and – 15 V143                              |

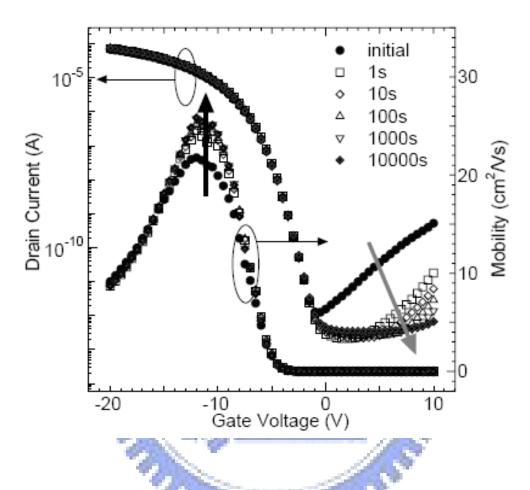

| Figure 5-4 Transfer characteristics and device mobility for the p-type device under the         |

| gate dynamic stress ranging between + 15 V and – 15 V144                                        |

| Figure 5-5 The model describing the mechanism for the degradation of p-type device              |

| under the gate dynamic stress ranging between + 15 V and – 15 V145                              |

| Figure 5-6 A conventional pixel-addressing method for the TFT-LCD panels146                     |

| Figure 5-7 The purpose for the stress conditions studied in this work147                        |

| Figure 5-8 Transfer characteristics and device mobility for the n-type device after the         |

| gate dynamic stress ranging between 0 V and - 20 V with the grounded source and                 |

| drain electrodes                                                                                |

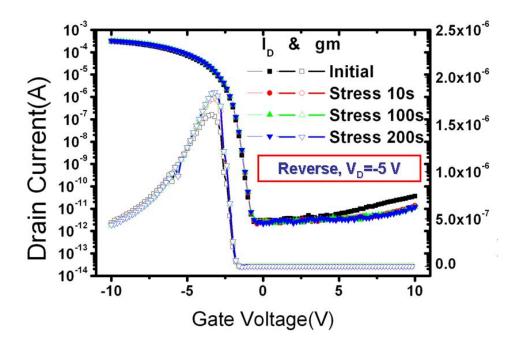

| Figure 5-9 Transfer characteristics and device mobility for the n-type device after the         |

| gate DC stress – 20 V with source and drain electrodes grounded149                              |

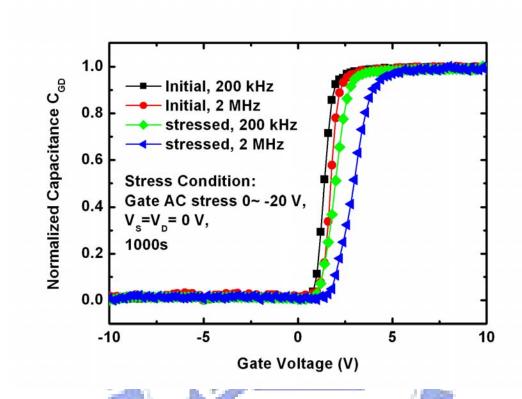

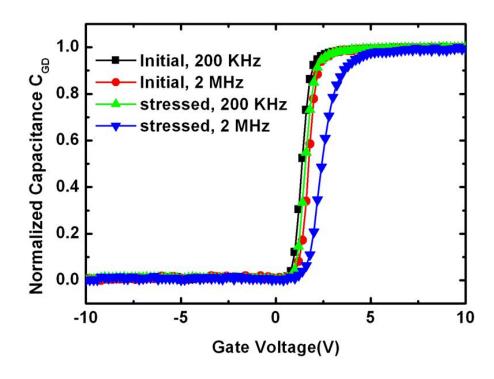

| Figure 5-10 Normalized capacitance C <sub>GD</sub> for the n-type device after the gate dynamic |

| stress ranging between 0 V and – 20 V150                                                        |

| Figure 5-11 Normalized capacitance $C_{GD}$ for the n-type device after $-20$ V gate DC         |

| stress 151                                                                                      |

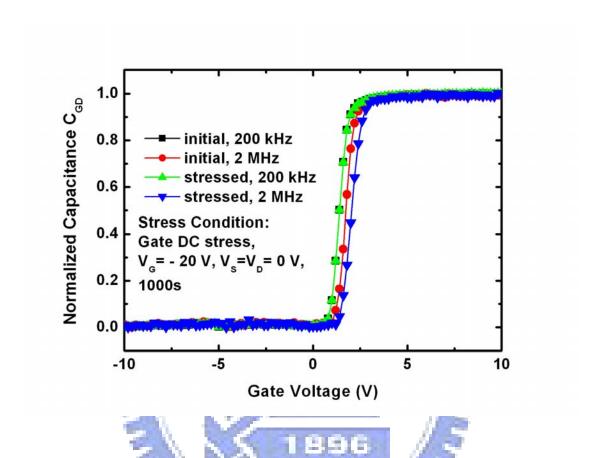

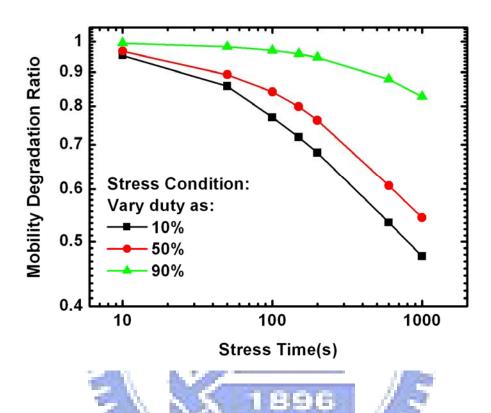

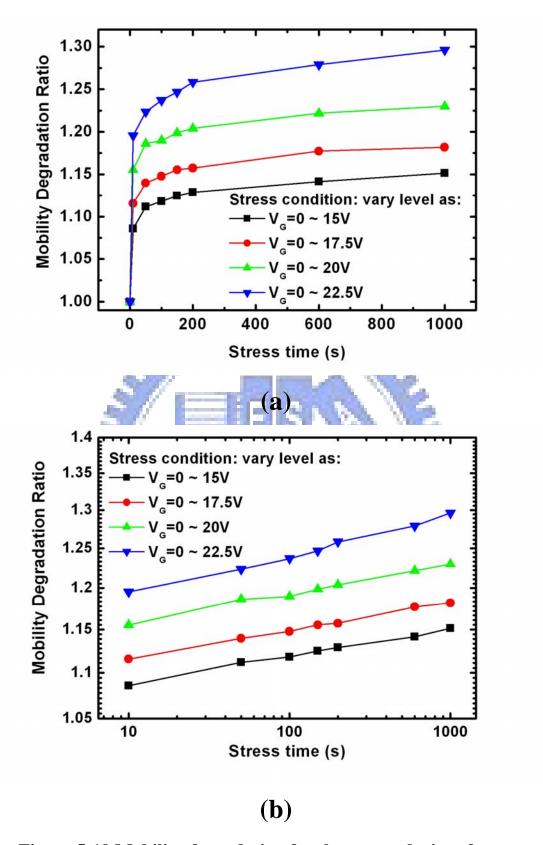

| Figure 5-12 Mobility degradation for the n-type device after gate dynamic stress with           |

| different voltage range in (a) linear scale and (b) logarithmic scale152                        |

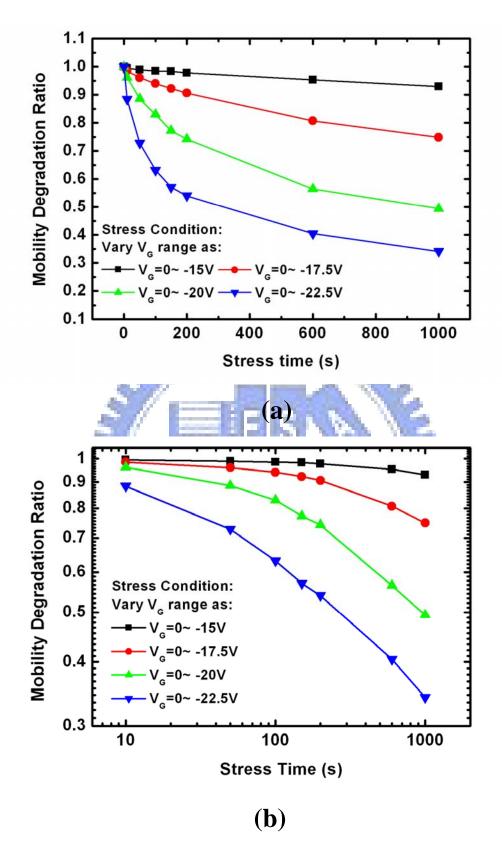

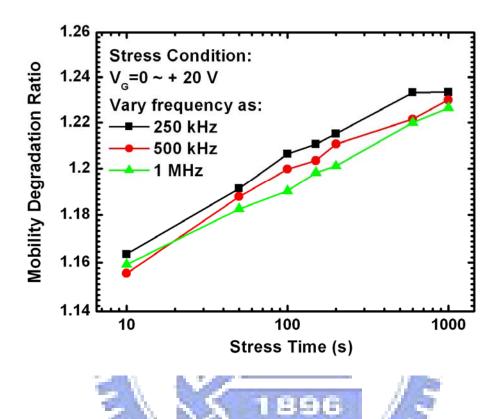

| Figure 5-13 Mobility degradation for the n-type device after gate dynamic stress with           |

| different pulse frequencies 153                                                                 |

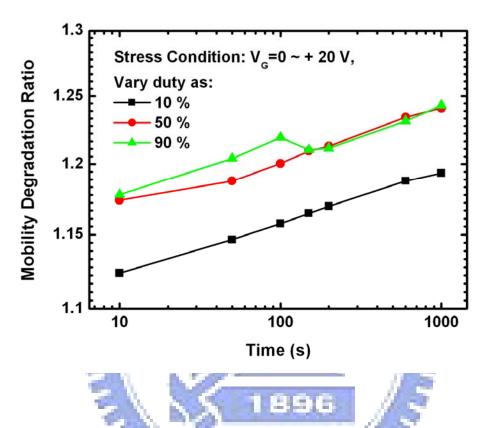

| Figure 5-14 Mobility degradation for the n-type device after gate dynamic stress with          |

|------------------------------------------------------------------------------------------------|

| different duty ratios154                                                                       |

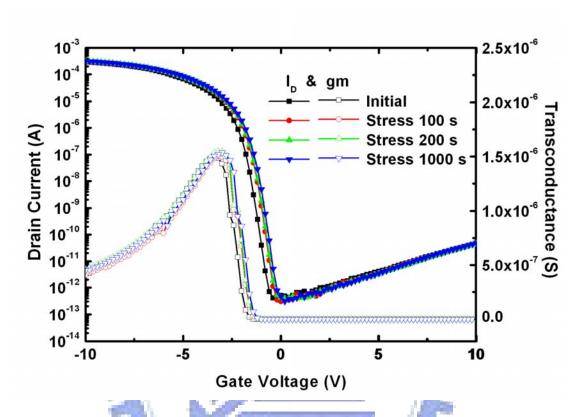

| Figure 5-15 Transfer characteristics and device mobility for the p-type device under           |

| the gate dynamic stress ranging between 0 V and + 20 V with the grounded source                |

| and drain electrodes155                                                                        |

| Figure 5-16 Transfer characteristics and device mobility for the p-type device under           |

| the gate DC stress + 20 V with source and drain electrodes are grounded156                     |

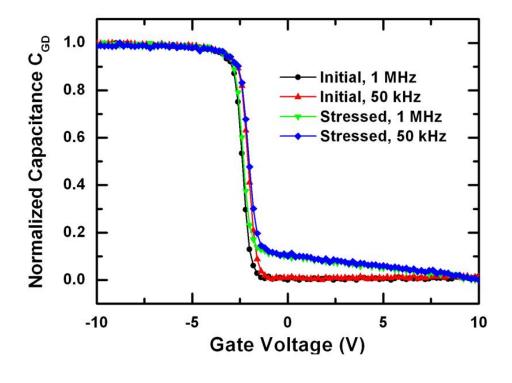

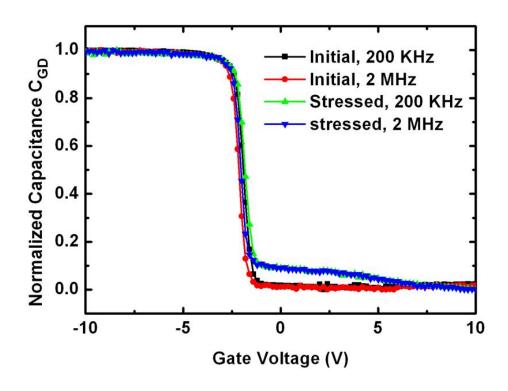

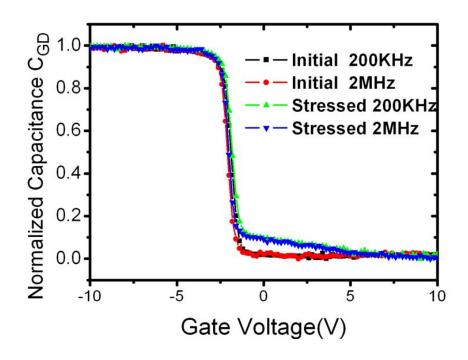

| Figure 5-17 Normalized capacitance $C_{GD}$ for the p-type device after gate dynamic           |

| stress ranging between 0 V and + 20 V157                                                       |

| Figure 5-18 Normalized capacitance $C_{GD}$ for the p-type device after the gate DC stress     |

| + 20 V158                                                                                      |

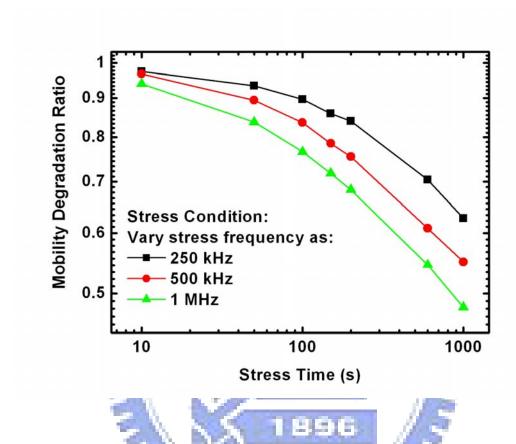

| Figure 5-19 Mobility degradation for the p-type device after gate dynamic stress with          |

| different voltage range shown in (a) linear scale and (b) logarithmic scale159                 |

| Figure 5-20 Mobility degradation for the p-type device after gate dynamic stress with          |

| different pulse frequencies160                                                                 |

| Figure 5-21 Mobility degradation for the p-type device after gate dynamic stress with          |

| different duty ratios161                                                                       |

| Figure 5-22 Device cross section view and an equivalent circuit model for an n-type            |

| poly-Si TFT162                                                                                 |

| Figure 5-23 Device cross section view and the band diagram for the gated p-i-n                 |

| device163                                                                                      |

| Figure 5-24 The figure showing how the voltage is picked to have only the N-side               |

| junction with large electric field164                                                          |

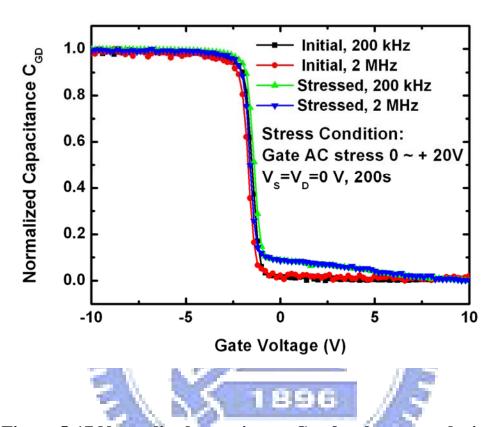

| Figure 5-25 Normalized capacitance C <sub>GD</sub> for the gated p-i-n device after 200 second |

| DC stress165                                                                                   |

| Figure 5-26 The figure showing how the voltage is picked to have only the P-side               |

| junction with large electric field166                                                    |

|------------------------------------------------------------------------------------------|

| Figure 5-27 Normalized capacitance $C_{GD}$ for the gated p-i-n device after 200 second  |

| DC stress167                                                                             |

| Figure 5-28 The figure discussing how the large electric field over the junctions could  |

| lead to the degradation168                                                               |

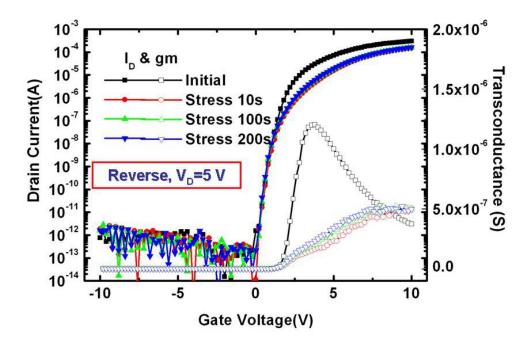

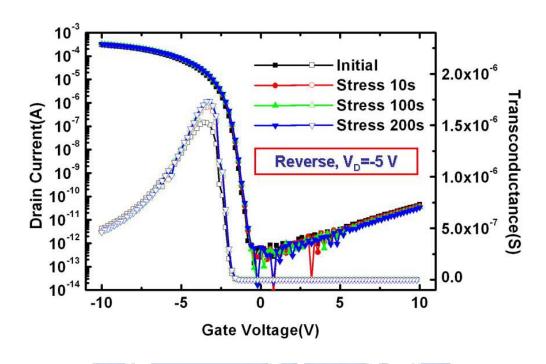

| Figure 5-29 Transfer characteristics and device mobility for the n-type device before    |

| and after the DC hot carrier stress with stress duration 200 seconds169                  |

| Figure 5-30 Normalized capacitance $C_{GD}$ for the n-type device before and after DC    |

| hot carrier stress170                                                                    |

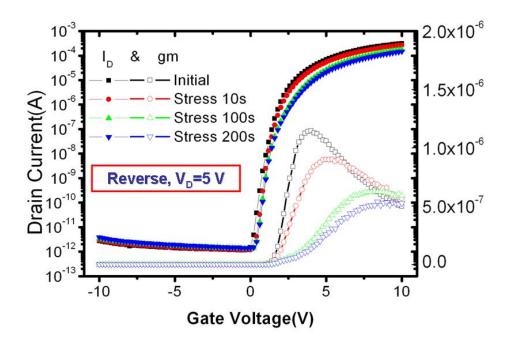

| Figure 5-31 Transfer characteristics and device mobility for the p-type device after the |

| DC hot carrier stress with stress duration 200 seconds171                                |

| Figure 5-32 Normalized capacitance $C_{GD}$ for the p-type device before and after DC    |

| hot carrier stress172                                                                    |

| Figure 5-33 Transfer characteristics and device mobility for the n-type device before    |

| and after the drain DC stress with stress duration 200 seconds173                        |

| Figure 5-34 Normalized capacitance $C_{GD}$ for the n-type device before and after drain |

| DC stress174                                                                             |

| Figure 5-35 Transfer characteristics and device mobility for the p-type device before    |

| and after the drain DC stress with stress duration 200 seconds175                        |

| Figure 5-36 Normalized capacitance $C_{GD}$ for the p-type device before and after drain |

| DC stress176                                                                             |

| Figure 5-37 Transfer characteristics and device mobility for the n-type device before    |

| and after the gate AC stress toggling between ON/OFF regions177                          |

| Figure 5-38 Normalized capacitance $C_{GD}$ for the n-type device before and after gate  |

| AC stress178                                                                             |

| Figure 5-39 Transfer characteristics and device mobility for the p-type device before    |

| and after the gate AC stress toggling between ON/OFF regions179                                |

|------------------------------------------------------------------------------------------------|

| Figure 5-40 Normalized capacitance $C_{\text{GD}}$ for the p-type device before and after gate |

| AC stress180                                                                                   |

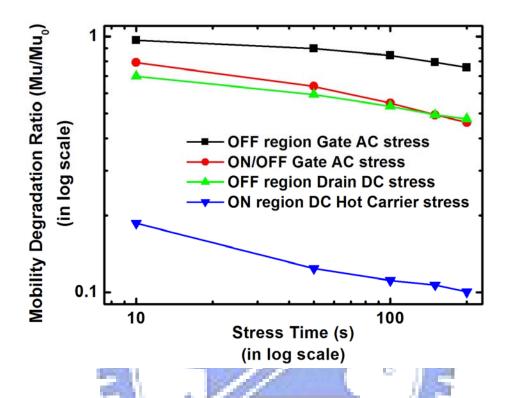

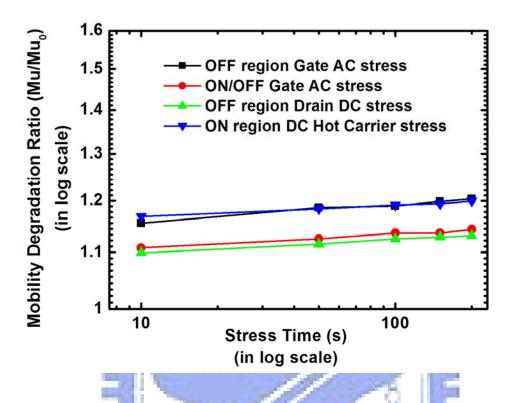

| Figure 5-41 Mobility degradation comparison for the n-type devices under various               |

| "generalized hot carrier stress" conditions181                                                 |

| Figure 5-42 Mobility degradation comparison for the p-type devices under various               |

| "generalized hot carrier stress" conditions182                                                 |

### **Tables**

## Chapter 3

| Table 3-1 The summarized average (AVG) and standard deviation (STD) value for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (a) V <sub>TH</sub> and (b) mobility61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 3-2 The table illustrating the possible factors for long-range and micro variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| as well as the corresponding design techniques62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |