# 第一章

# 序論

# (Introduction)

### 1-1、前言

記憶體(Memory)在現今生活中,已經成為不可或缺的一樣東西,記憶體被應用在各種的電子產品中,例如電腦中的 DRAM、SRAM 和 Flash Memory 等。尤其是快閃記憶體 flash memory 更是大家生活中所最常見到的記憶體之一,例如,隨身碟、記憶卡等產品,都是所謂的 flash memory。

隨著微影技術的進步,單位面積上的元件(Device)跟著增加,flash memory 的容量也越來越大,市面上一開始從 16 MB 的記憶卡,到現在 2 GB、4 SB 都可以用很便宜的價錢購買到。這也顯示 flash memory 技術的進步和大家對於 flash memory 的需求越來越高。目前也有出現 32 GB 的固態硬碟 SSD (Solid State Disk)產品,相信未來將可以利用flash 的方便和安全性取代硬碟。

快 閃 記 憶 體 (flash memory) 基 本 上 是 EEPROM's (Electrically erasable and programmable read only memories)的一種,對於每一個 bit 元件都可以利用電的方法來將電子清除(erase)和寫入(program)到記憶體中。他的方便性因此就高於需要利用紫外線(UV)來清除(erase)記憶的 EPROM's (electrically programmable read-only memories)。

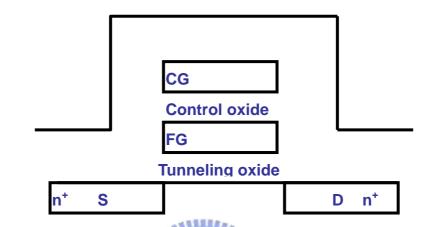

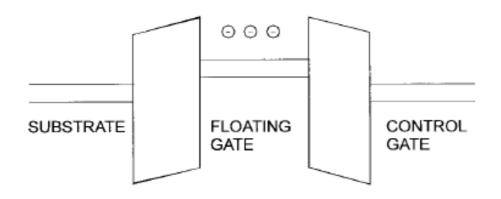

EEPROM是一種利用浮動閘極(Floating gate)來儲存電荷,達到記憶效果的一種記憶體。Floating gate簡稱FG,FG被介電質,例如絕緣體二氧化矽 $SiO_2$ 所包圍著,下面的介電層稱做穿隧氧化層(tunneling oxide layer),FG上方的介電層稱做控制氧化層(control

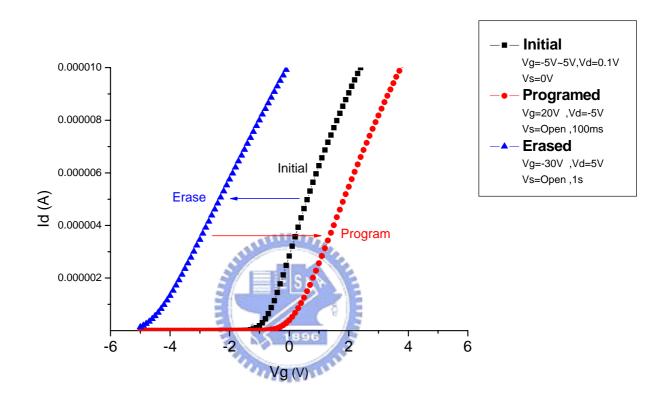

oxide layer)。整個結構如圖 1-1,上方有著控制閘極(Control gate)來控制他的電位,電位的改變是利用FG內的電荷量來決定,當電子被注入到浮動閘極(Floating gate)中,會使元件的臨界電壓(Threshold voltage)向右偏移,此時的狀態稱做"1",也可以稱做"被寫入(Programed)"。相反的,若浮動閘極(Floating gate)中的電子排出,則臨界電壓(Threshold voltage)向左偏移,此時的狀態稱做"0",也可以稱做"被清除(Erased)"如圖 1-2。

圖 1-1、浮動閘極元件剖面圖。 The crosss-ection of Floating gate device。

圖 1-2.、浮動閘極元件的電流-電壓曲線 I-V curves of an FG device。

#### 浮動閘極的材料

浮動閘極記憶體最早期是使用非晶矽(α-Si)做為浮動閘極的材料,近年來,許多的研究是改用Si<sub>3</sub>N<sub>4</sub>或是奈米粒子來取代非晶矽。

#### **SONOS**

所謂的SONOS是指利用Si<sub>3</sub>N<sub>4</sub>來做為浮動閘極(Floating gate)的元件,SONOS就是指

(silicon-oxide-nitride-oxide-silicon),從上而下,電極到基材的材料結構。SONOS利用 oxide-nitride接面(interface)所產生的電荷捕捉元素(charge-trapping element)來儲存電子。

#### 奈米粒子記憶體

除了使用 $Si_3N_4$ ,奈米粒子(Nanoparticle)也是被許多來研究當作記憶體的浮動閘級層 (Floating gate layer)。所謂的奈米粒子(Nanoparticle)就是指大小在數個奈米(nanometer =  $10^{-9}$ m)到數時個奈米等級的粒子,其材料包含半導體、絕緣體金屬。電荷儲存的原理也是利用奈米粒子和絕緣層例如二氧化矽( $SIO_2$ )接面所行成的電荷捕捉元素 (charge-trapping element)來儲存電子。

我們所使用的是金奈米粒子,其優點是 1.金的功函數(work function of gold)很大,對於電子來說是很好的捕捉因子(trap center)。2.奈米等級的大小所產生的能階分裂,有利於更多的電子的儲存。3.因為奈米粒子是互相被絕緣體所絕緣,所以當電子流失的時候,並不會有全部同時流失的情況,因此可以提高記憶的時間(Retention time)。另外,我們加入半導體性質的硒化鎘(CdSe),讓半導體和金屬混合成為浮動閘極的材料,希望對電性有所幫助。

#### 臨界電壓的變化

更深一步來討論,從臨界電壓(Threshold voltage)的公式(1-1)和公式(1-2)來看,當整個元件的結構固定,能夠影響的就只剩下最後一項,也就是浮動閘極 FG 中的電荷量,當 FG 儲存電子的時候,Q<0,因此 Vth 會比沒有儲存電子的時候大( $\Delta Vth > 0$ ),相反的,當 FG 中的電子被排開,使 FG 中的電荷 Q>0,則 Vth 就會變小( $\Delta Vth < 0$ )。 我們就是利用元件這兩種不同狀態來判斷記憶體是否有"記憶"。

$$Vth = \frac{|Q'_{SD}(\text{max})|}{Cox} + \phi_{ms} + 2\phi_{fp} - \frac{Q}{Cox}$$

(1-1)

$$\Delta Vth = -\frac{\Delta Q_{FG}}{C_{FG}} \tag{1-2}$$

Vth=臨界電壓(Threshold voltage)

Cox= 氧化層電容

$\phi_{ms}$ = 金屬和半導體之間的位障

$\phi_{\mathit{fp}}$  = 費米能階(Fermi level)到本質費米能階(Intrinsic Fermi level )的距離

Q= 氧化層中的電荷量

ΔVth = 臨界電壓的偏移(The shift of threshold voltage)

QFG= 浮動閘極中的電荷量

CFG = 浮動閘極電容,(如圖 1-3)

CONTROL GATE

CFC

FLOATING GATE

CS CB CD

SOURCE

SOURCE

SUBSTRATE

圖 1-3、浮動閘極元件的等效電容圖。

### 1-2、載子注射的機制 Carrier injection mechanisms

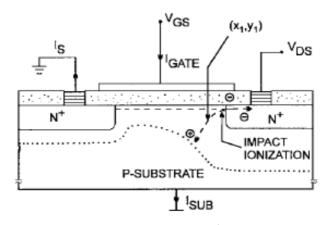

前面提到,我們改變控制浮動閘極(Floating gate)內的電荷量,來改變浮動閘極(Floating gate)的電位,進而判斷記憶體元件是在"1"記憶或是"0"失憶的狀態。而這節我們討論要如何將載子注入到浮動閘極的機制。我們實驗所使用的元件是 NMOSFET(電子通道金屬氧化半導體場效電晶體),因此我們所操作的載子就是電子(electron)。最常見的兩種方式就是熱電子注入(HEI-Hot electron injection)和 F-N 穿隧(F-N tunneling)。

#### 1-2-1 熱電子注入(Hot election injection)

熱電子注入(HEI)的機制是相當的簡單去了解,一個電子從接地的汲極(Source)獲得能量往源極(Drain)移動,當加速電場超過 100kV/cm,電子就有足夠的能量被控制閘極 (control gate)改變方向越過二氧化矽的能障(The barrier of the thermal oxide)然後到達浮動閘極。(如圖 1-4)。

熱電子注入(HEI)的特點就是快速,因為這時元件已經操作在飽和區,所以電子已經被加速到電子在半導體中速度的極限,大約為  $10^7 {\rm cm/s}$ ,這時,再被控制閘極吸引上去,相對的就比F-N 穿歲的速度快,時間通常在 1 到 10 微秒( $1\sim1~\mu {\rm s}$ ),因此通常用在將電子注入浮動閘極層(Floating gate layer),

圖 1-4、熱電子注入機制。

#### 1-2-2FN 穿隧(Fowler-Nordheim tunneling)

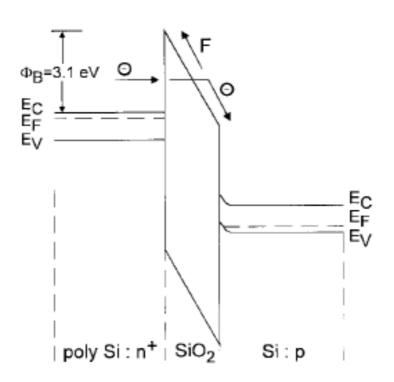

穿隧機制(Tunneling mechanism)是從量子力學中,將邊界條件帶入薛丁格方程式 (Schrödinger equation)中所解出的答案。有別於古典力學的概念,穿隧(Tunneling)的電子 不需要比位能障(Energy beerier)能量高,便有穿過位能障的機率存在,就如同一個人要 越過一道高牆,他不需要攀爬,只要往牆面衝過,他就會穿過那道牆。

穿隧機率和位能障(Energy beerier)的寬度有關,寬度越小,電子穿隧的機率就會上升,而 FN tunneling 不同於一般的穿遂,就是他會隨著 MOS 操作的電壓上升,而使測量到的電流上升。在操作在 MOS 結構的時候,電極所施加的電壓會使的氧化層的等效寬度變小,(如圖 1-5),因此電子從矽穿過氧化層的機率就因此上升。浮動閘極元件(Floating Device)就是利用 F-N 穿隧(F-N tunneling)使源極(Drain)的電子穿過穿隧氧化層(tunneling oxide)到達浮動閘極(Floating gate),接著關閉電壓,電子就會被侷限在由穿逐氧化層(tunneling oxide)和控制氧化層(control oxide)所侷限的位能井內(如圖 1-6)。

圖 1-5、F-N tunneling 在 MOS 中的示意圖。

圖 1-6.、電子侷限在氧化矽位能井之中。

相反的 F-N tunneling 的機制只要將控制閘極(control gate)施加反向的電壓就可以將 浮動閘極(Floating gate)中的電子穿隧到源極(Drain)。因此利用 F-N 穿隧(F-N tunneling) 機制,我們可以任意的將電子注入浮動閘極(Floating gate)或是從浮動閘極(Floating gate) 中排開。

不過 F-N 穿隧(F-N tunneling)的缺點就是慢,一般所需要的時間從 100 ms 到 1 s,因此 FN 穿隧(F-N tunneling)機制通常用來清除(F-F)記憶體的電子。

### 1-3 文獻回顧(Paper review)

在開始實驗之前,我們找了其他團隊發表在期刊或是會議上面有關浮動閘極記憶體 (Floating gate memory)的論文,從論文中也可以了解,實際上元件要如何的製作、實驗要如何的量測,以及哪些是我們在記憶體這領域要討論的項目。

表 1-1 是從最近幾年的期刊論文期刊中所挑選整理出來做成表格。[5][6][7]從年代遠而近,第一篇 2002IEEE,是利用 RTA(Rapair Thermal annealing)技術使很薄的金膜( $\sim$ 1-5 nm gold film),在高溫下( $\sim$ 500°C 左右)很短的時間( $\sim$ several second),因為薄膜表面能要達到最小狀態而形成幾個奈米大小的奈米金屬粒子。

不過這樣的方法所形成的奈米粒子大小分部會不均勻而有一個大小分佈出現。而 2003 JAP的文章利用SAM(self-assembled)技術將已經用化學方法調配好約 5 nm的金奈米粒子沉積在表面上,密度約  $5x10^{12}$  #/cm²。利用化學方法調配的奈米粒子其大小會RTA方法一致。第三篇 2007 APL也是使用RTA的方法形成金奈米粒子。不過他的特點是利用SiO $_1$ .3N來取代一般SiO $_2$ 當作穿遂氧化層(tunneling oxide layer)和控制氧化層(control oxide layer)。SiO $_1$ .3N的特點是介電常數k比SiO $_2$ 高,同樣的絕緣效果下,SiO $_1$ .3N厚度可以比SiO $_2$ 薄,這點在元件的縮小化中是相當的重要,如何在維持閘極控制能力(Gate control)、氧化層的電容( $C_{ox}$ )和通道的電流(Ids ,the current of Source to drain)之下還能使氧化層有足夠的絕緣能力,這也是目前大家努力的課題之一。

除了比較製成上的不同,最主要是比較其"記憶體"的優劣,除了一般MOSFET的比較,如導通電流(turn on current)、開關比例(on/off ratio)和次臨界斜率(Subthreshold slope),在記憶體的領域我們通常比較,1.臨界電壓的變化( $\Delta V$ th),變化越大越好,表示"0"和"1"更容易分辨出來。2.寫入和清除的電壓,產生同樣的臨界電壓變化下,操作電壓越小越好。3.寫入和清除的時間,時間越短表示元件可以操作在更快速的條件下。不過操作的時間和通道的長度有關,所以以同樣的通道長度做比較才會有意義。4.最後就是記

憶的時間(Retention time)和反覆操作次數(Endurance),這兩點是最主要判斷一個記憶體的好壞的重要因素,記憶的時間(Retention time)代表這記憶體元件可以將儲存電荷保存的能力,因為電荷儲存在浮動閘極層經過一段時間是一定會有電荷經由穿隧或是熱擾動等各種方法流失掉。因此一般市面的非揮發記憶體的記憶時間(Retention time)都要求在10~年以上,也就是 $3x10^8~$ seconds。[4][5]反覆操作次數(Endurance)則是表示一個記憶體元件的可靠度,寫入和清除反覆的次數越高,代表這個記憶體元件可靠度高。通常隨著操作次數的增加,會使氧化層捕捉子(oxide trap)和介面狀態(interface state)的產生,然後使臨界電壓的變化( $\Delta Vth$ )變小。

回頭看比較的這三篇論文,IEEE 2002 這篇沒有測量記憶時間(Retention time),另外兩篇記憶時間的表現也不錯,不過這三篇均沒有測量反覆操作次數(Endurance),所以無從得知這樣的結構的元件的可靠度是多少。

表、1-1 各篇論文參數的比較和整理。

|                 | IEEE 2002    | 2003 JAP              | 2007 APL                   |  |

|-----------------|--------------|-----------------------|----------------------------|--|

| Floating gate   | 9nm Au (RTA) | 5nm Au (SAM)          | 1-5nm Au (RTA)             |  |

| Density         | none         | $5x10^{12}$           | 1.5x10 <sup>12</sup>       |  |

| Tunneling layer | 8 nm         | SiO <sub>2</sub> 5 nm | SiO <sub>1.3</sub> N 5 nm  |  |

| control layer:  | 30 nm        | Cd-AA LB film         | SiO <sub>1.3</sub> N 45 nm |  |

| Channel length  | 6 μm         | 1.5 μm                | 2-20 μm                    |  |

| Channel width   | 9 μm         | 10 μm                 | none                       |  |

| Write:          | Vg=20 V      | Vg=6 V ,1 s           | Vg= 10 V ,100 μs           |  |

| Erase:          | Vg=-20 V     | Vg=-6 V ,1 s          | Vg=-10 V ,1 s              |  |

| ΔVth            | 0.7 V        | 6 V                   | 1.8 V (Vth=-2.0 V)         |  |

| Retention time  | none         | Lose 7%/order         | Lose 2.65%/order           |  |

# 第二章

# 實驗流程

上一章簡單了介紹記憶體的操作機制,以及回顧了前人的製作,這章將會介紹我們是如何做我們的實驗,從實驗動機開始,藉著介紹我們元件(記憶體)製作的流程,以及最後我們元件(記憶體)完成後我們如何測量,從測量的數據中,獲得我們之前所討論了一些參數,如臨界電壓偏移(ΔVth)、記憶時間(Retention time)等。

#### 2-1 實驗動機 Motivation

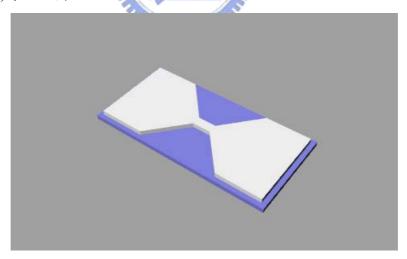

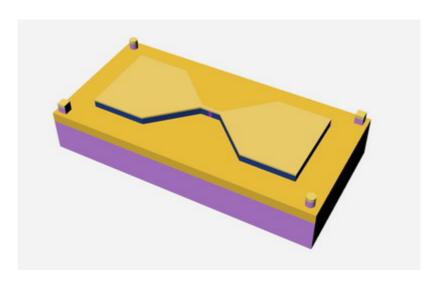

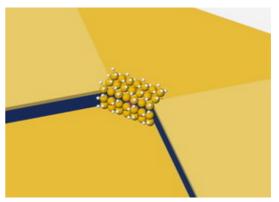

我們實驗室擁有在矽基版(Silicon substrate)上製造微米線(Microwire)和奈米線 (Nanowire)的技術。微米線是指寬度在數個微米(μm)、長度也在數個微米尺度的矽(Si)線,而奈米線(Nanowire)則是指寬度在數個奈米(nm)到數百奈米、長度在則是在數個微米左有的矽(Si)線,如圖 2-1。

圖 2-1、微米線或是奈米線

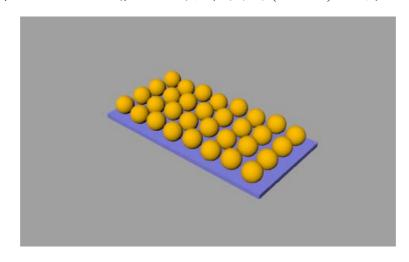

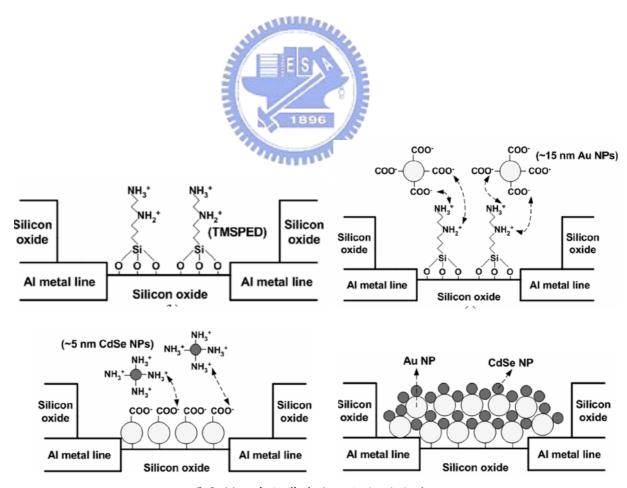

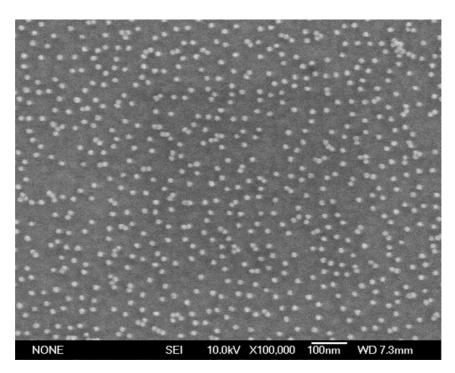

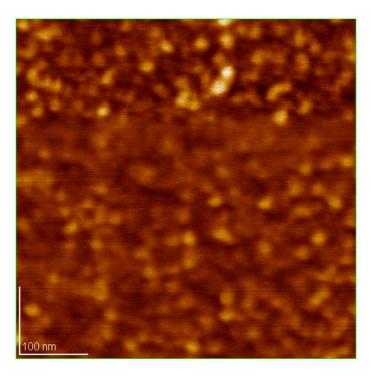

另外,本實驗室也有滿純熟SAM(self-assembling)的技術,就字面上的意思, SAM(self-assembling)就是讓分子可以自我組裝單層分子在我們所想要的材料上,加上利 用化學的方法調配出寬度約 15 nm的金奈米粒子(Au NPs = Au NanoParticles),因此我們 可以在SiO2的表面上SAM上一層 15 nm的金奈米粒子(Au NPs),如圖 2-2。

圖 2-2、在SiO<sub>2</sub> 表面SAM 上金奈米粒子AuNPs.。

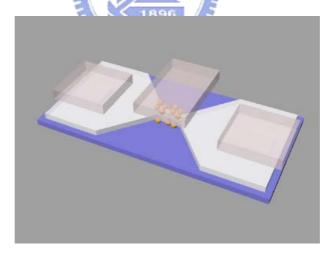

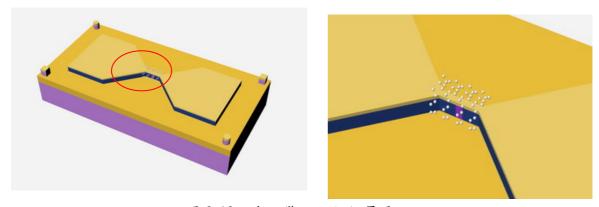

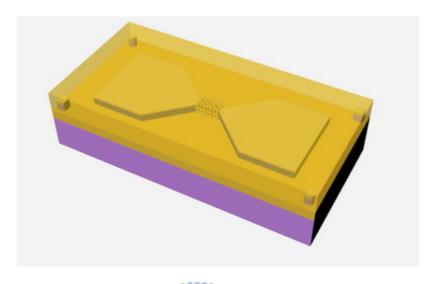

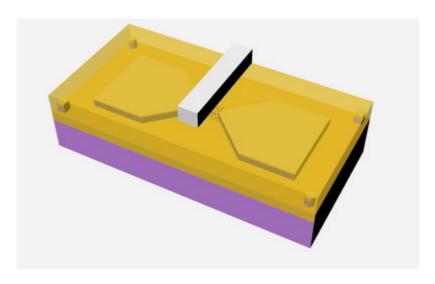

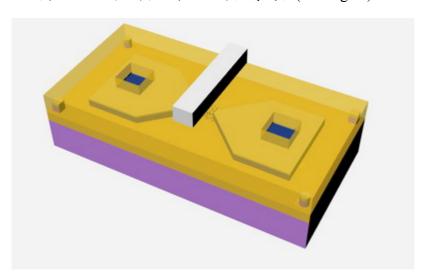

有了上述的兩樣方法。我們就嘗試將金奈米粒子(AuNPs)SAM在已經成長SiO $_2$  (Tunneling oxide)的矽微米線或是奈米線上,以金的奈米粒子當作浮動閘極(Floating gates),然後再疊上一層SiO $_2$ (Control oxide)覆蓋住金奈米粒子,最後疊上金屬(Control gate),便完成了我們的金奈米粒子記憶體(Au Nanoparticles memory) ,如圖 2-3。

圖如 2-3、結合 SAM AuNPs 和 奈米線索製作出來的記憶體。

### 2-2 元件製作流程

這一節將會詳細的介紹整個奈米粒子記憶體的製作流程,包含前段奈米線(nano wire)和微米線(micro wire)的製作、自我組裝的金和鎘奈米粒子(SAM Au nanoparticles and CdSe Nano particle)和最後 Control oxide 的沉積和金屬的配置。

#### 2-2-1 奈米線和微米線製作(Fabrication of Nanowire and Microwire)

#### 微米線

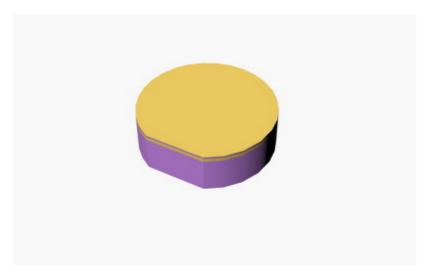

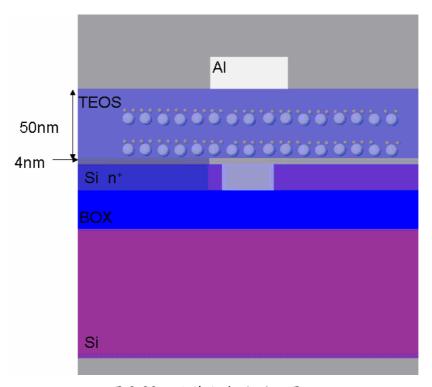

微米線的製作,我們使用的儀器中的爐管、bench和為影設備均是使用交大奈米中心 10k。而Ozone和RIE則是使用同步輻射中心,許博淵教授的。我們所使用的晶片是六吋(100) SOI wafer,最上層的Si 厚度是 150 Å,BOX oide是 1500 Å,如圖 2-4。首先我們會做RCA clean 並進入爐管 950°C 30 分鐘,長約 270 Å厚的SiO<sub>2</sub>,如圖 2-5 。

圖 2-4、 6"SOI wafer,最上層的 Si 厚度是 150 Å, BOX oxide 是 1500 Å

圖 2-5、爐管長 27 nm 厚的犧牲氧化層。

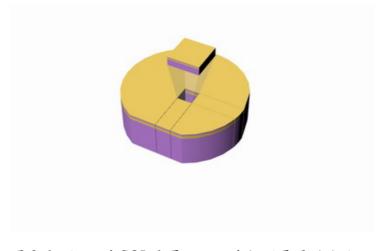

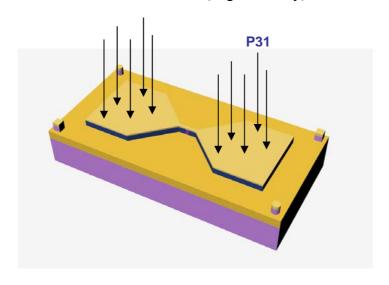

這一層SiO<sub>2</sub>將做為犧牲氧化層。然後會從整片的晶圓上切下 1cm x 1cm的大小,如圖 2-6、2-7。接著就做離子佈植(Boron 20 keV  $5E13/cm^2$ ),調整臨界電壓。然後進行微影,定義對準鑰匙(alignment key),如圖 2-8。用RIE蝕刻出對準鑰匙(alignment key)。接著做第二到光罩微影定義通道長度,我們的通道長度有  $5~\mu m$ 、 $10~\mu m$ 和  $20~\mu m$ 。接著就送離子佈值,將Source和Drain重參雜,(P31+ 20 keV  $5E15/cm^2$ ),使他之後和金屬能形成歐姆接面(ohmic contact),如圖 2-9。離子佈植後,使用Ozone在  $250^{\circ}$ C 做 10~%全,再用SPM(硫酸:雙氧水=3:1)去光阻。接著就是做第三道光罩定義狗骨頭,也就是微米線。然後再用光阻做為抵擋層,用BOE蝕刻SiO<sub>2</sub>、RIE蝕刻Si。然後SPM去掉光阻。這時候要利用AFM(原子力探針顯微鏡)去判斷我們所蝕刻的高渡是否正確。微米線就完成了,如圖 2-10。

圖 2-6、從六吋 SOI 晶圓上切下我們所需要的大小。

圖 2-7、接著利用這切下來的片子開始製作元件。

圖 2-8、曝對準鑰匙(alignment key)。

圖 2-9、將 Source 和 Drain 重參雜。

圖 2-10、蝕刻出 Active area, 載重新成長氧化層。

#### 奈米線

我們也有使用奈米線,奈米線的製程,和微米線不同,會先使用 LPCVD 疊上 20 nm 的 TEOS 做為犧牲氧化層。再利用電子東直寫,在六吋(100)SOI wafer 上,畫出寬度 100 nm,長度 5 μm 到 20 μm 的奈米線。光阻顯定影之後利用位在 NDL 的 tel 5000 和 TCP 分別蝕刻 TEOS 和最上層的 Si。然後再將我們所需要的奈米線從六吋晶圓下切下來。一樣做臨界電壓調整的離子佈植。再做一道微影定義通道長度,我們的通道長度均是 5 μm。然後 Source 和 Drain 做重參雜,所有的參數和微米線都一樣。最後使用 Ozone 和 SPM 將光阻去掉,奈米線就完成了。

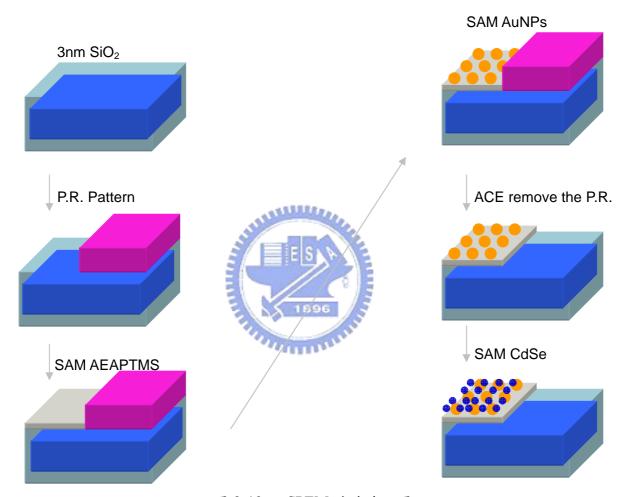

穿隧氧化層和奈米粒子的自組裝(Tunneling oxide & SAM Nanoparticles): 奈米線和 微米線完成後,之後的步驟均會一樣。首先利用 BOE 去掉犧牲氧化層。然後做 RCA clean。用手推入奈米中的爐管,在  $850^{\circ}$ C行成約 4 nm 的穿隧氧化層(Tunneling oxide),然後再升溫到  $950^{\circ}$ C,利用氮氣做 30 分鐘的退火,使穿隧氧化層可以更耐高電壓。爐管結束後就做第四道光罩,定義浮動閘極 Floating gate 的位置,也就是之後要 SAM 奈米粒子的位置。

#### 2-2-2 奈米粒子的自組裝

我們所使用的奈米粒子有粒徑 15 nm的金(Au)還有 5 nm的硒化鎘(CdSe)。所使用的基材是SiO2,也就是剛剛在爐管所長出來的穿隧氧化層(Tunneling oxide),而這兩種奈米粒子都不會直接和SiO2接上。所以我們使用AEAPTMS做為SiO2和奈米粒子連接的橋樑。AEAPTMS上面的OHT會和SiO2行成共價鍵。而另一端NH3<sup>+</sup>會使其帶正電。接下來再利用正負相吸的靜電力,將表面包圍著負電的金(Au)和硒化鎘(CdSe)量子點吸附上去。另外,我們也有帶正電的硒化鎘(CdSe)量子點,我們則是將其沉積在金奈米粒子上(AuNPs),因為金奈米粒子帶負電就會吸引帶正電的硒化鎘(CdSe)量子點。帶負電的CdSe外面的link為Mercaptosuccinic acid (MSA);帶電的CdSe外面的link為Mercaptosuccinic acid (MSA);帶電的CdSe外面的link為Mercaptosuccinic acid (MSA);帶電的CdSe外面的link為Mercaptosuccinic acid (MSA);帶電的CdSe外面的link為Mercaptosuccinic acid (MSA);

圖 2-11、自組裝金和硒化鎘的方法。

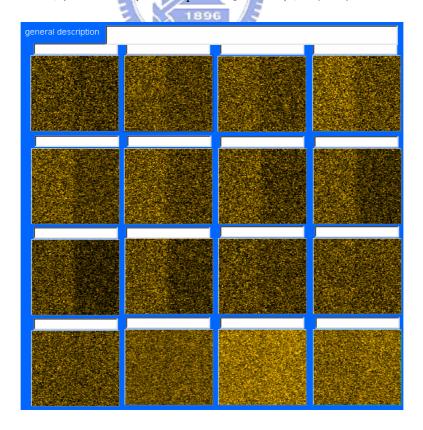

整個流程首先我們會用Ozone treatment在奈米線和微米線上做 10 分鐘,使SiO2的表面形成OH 這樣有利於SAM上AEAPTMS。再這之前會將試片放在  $120^{\circ}$ C 的烤盤上約半小時,避免Ozone treatment使光組參生龜裂。接著將奈米線和微米線放入AEAPTMS中(40 ml DI water  $+20\mu$ l AEAPTMS)十分鐘。接著放在  $120^{\circ}$ C 的烤盤上約半小時,使多餘的水分蒸發乾。然後再放入金奈米粒子或硒化鍋量子點(CdSe NPs)的溶液中約 2 小時。接著再用接著放入水中,使用超音波震盪器振一分鐘,將多餘的奈米粒子振開。若是要再沉積上硒化鍋量子點(CdSe Qdots),就再把已經沉積好金奈米粒子的試片放入帶正電的硒化鍋量子點(CdSe NPs)的溶液中約 2 小時。最後再放入水中,使用超音波震盪器振一分鐘,將多餘的奈米粒子振開。這樣我們就分別將金(AuNPs)、硒化鍋(CdSe Qdots)還有金加上硒化鍋的量子點成功的分別SAM在我們的奈米線和微米線上了,如圖 2-12、2-13、2-14、2-15-2、2-3

圖 2-12、自主裝, 金奈米粒子。

圖 2-13、自主裝, 硒化鎘量子點。

圖 2-14、自主裝金混合硒化鎘量子點。

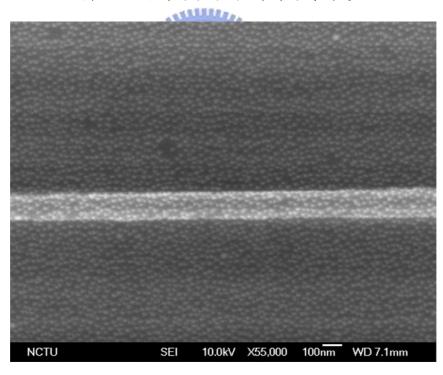

我們會使用 TEM 和 AFM 去判斷我們的奈米粒子是否沉積上去,如圖 2-15,因為 硒化鎘量子點(CdSe NPs)很小,所以用 SEM 看不出來,AFM 也只能從高度和粗操度 (Roughness)來判斷,如圖 2-16、表 2-1。

圖 2-15、金奈米粒子的 SEM 圖片。

圖 2-16、金奈米粒子侷限在奈米線附近。

圖 2-17、奈米線上的金奈米粒子 SEM 圖。

圖 2-18, 硒化鎘(CdSe)的 AFM 圖。

表 2-1、氧化矽、AEAPTMS 和硒化鎘三種不同比的的粗操度。

|         | Roughtness |  |  |

|---------|------------|--|--|

| SiO2    | Rq=0.188nm |  |  |

| AEAPTMS | Rq=0.193nm |  |  |

| CdSe    | Rq=1.42nm  |  |  |

#### 金奈米粒子(Au)和硒化鎘量子點(CdSe)的判定

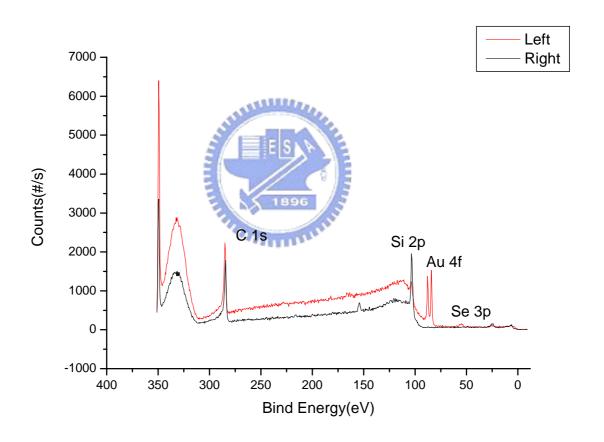

硒化鎘大小約 5nm左右,無法使用SEM來判定,因此我們利用SPEM(XPS)來做成份定性的分析。試片準備的方法如圖 2-19,先利用光組在 3nm厚的 $SiO_2$ 上做pattern,然後把金奈米粒子SAM在沒有光阻的地方,接著再將光組去除,然後再將試片浸到含有CdSe量子點的溶液中,讓CdSe和AuNPs做靜電力的吸附,最後將試片做<math>SPEM的掃描分析。

圖 2-19 、SPEM 試片流程圖。

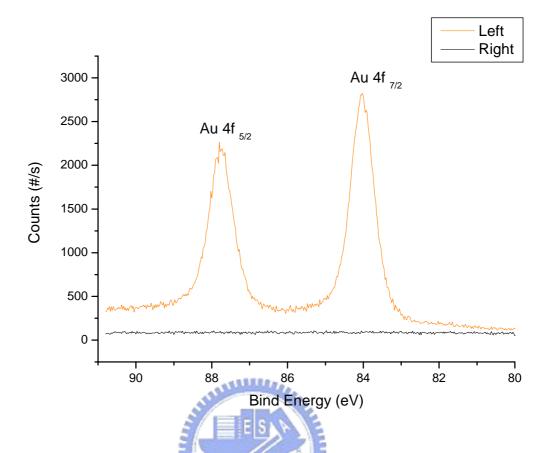

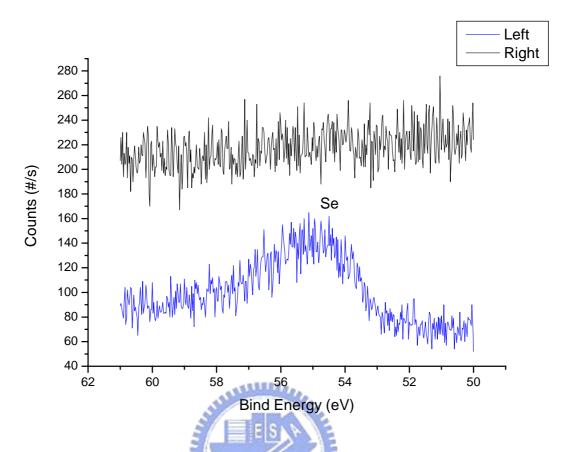

從掃描的結果如圖 2-20、黑色曲線代表試片右側。紅色曲線代表試片的左側,含有金奈 米粒子和硒化鎘量子點的區域,從曲線也可以看到有Au 4f和Se 3p 的訊號出現。而右側 沒有金(Au)和硒(Se)的訊號,從這邊可以知道金奈米粒子和硒化鎘量子點的吸附是靠靜 電力,所以硒化鎘量子點不會吸附在沒有帶電的SiO2 上面。對於Au 4f和Se 3p做進一步 的掃描,可以看到Au 4f  $_{5/2}$  和Au 4f  $_{7/2}$  ,鍵能(binding energy) 分別為 88eV和 84eV金的 訊號,如圖 2-21、2-22。另外,硒(Se)比較微弱,不過依舊可以分辨出,在左側有硒(Se) 2p,鍵能(binding energy)為 55eV,硒的訊號出現,如圖 2-23、2-24。

圖 2-20、XPS 掃描的結果。

圖 2-21 、對於金訊號 XPS 掃描的結果。

圖 2-22、對於金訊號 SPEM 掃描的結果。

圖 2-23 、對於硒 2p2 訊號 XPS 掃描的結果。

圖 2-24 、對於硒 2p2 訊號 SPEM 掃描的結果。

#### 2-2-3 控制氧化層和金屬(Control gate & Metal)

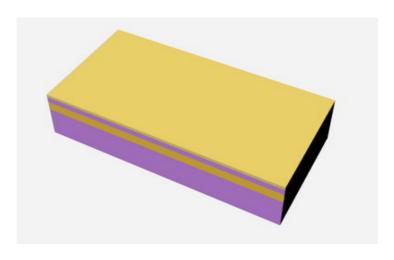

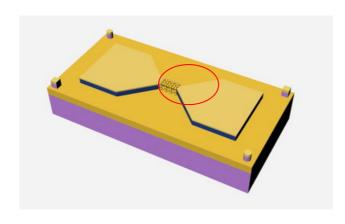

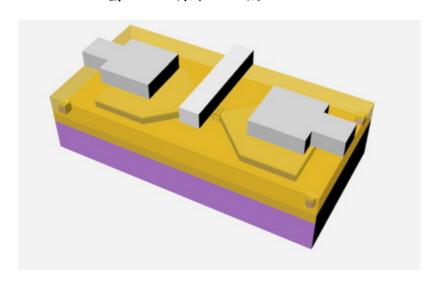

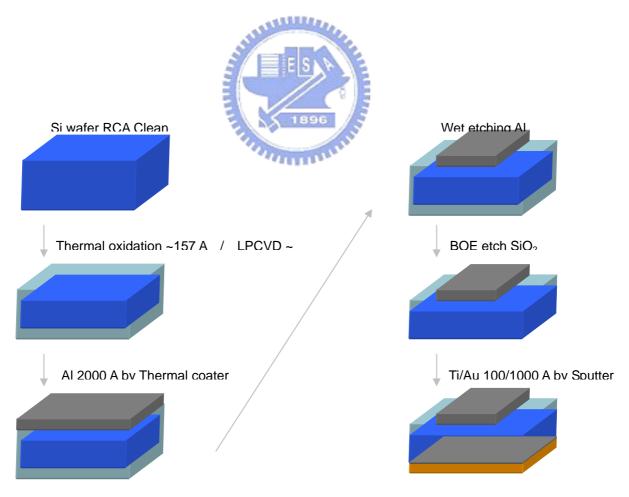

將奈米粒子放在奈米線和微米線上之後。我們先用丙酮(ACE)去除當初定義浮動閘極(Floating gate)區域的光組。使用 NDL 的 PECVD 疊上約 250 Å 的 TEOS,如圖 2-25。

圖 2-25、疊上 PECVD TEOS=25 nm。

# ES

若是做兩層浮動閘極,在疊完 TEOS 之後用光組定義浮動閘極(Floating gate)區域,並再 SAM 上奈米粒子,去掉光組,再疊上 250 Å 一樣超會漏電的 TEOS。

疊完 TEOS 之後,就使用熱蒸鍍(Thermal coater)方法,鍍上 2000 Å 厚的鋁(Al),做第五 道光罩微影,定義控制閘極(Control gate),然後利用濕蝕刻,吃出圖案來,如圖 2-26。接著做第六道光罩微影,定義 contact,然後使用 BOE 蝕刻,如圖 2-27。再接著做第七道光罩微影,定義連接 Source 和 Drain 的金屬。接著就再使用熱蒸鍍(Thermal coater)方法 鍍鈦和鋁(Ti/Al),厚度分別是 100 Å 和 2000 Å , 如圖 2-28。因為是使用抬離(Lift off)的方法定義金屬而不是蝕顆。所以鋁和矽(Si)之間要鍍上鈦(Ti)來增加附著力(Adhesion)。抬離(Lift off)的方法,先將試片泡在丙酮(ACE)約半小時,再用超音波震盪器振掉光阻,然後再用去離子水(DI Water)清洗。

圖 2-26、利用濕蝕刻做鋁的金屬閘極(metal gate)。

圖 2-27、利用 BOE 做 Contact。

圖 2-28、利用 lift off 做汲極和源極的金屬。

金屬完成後,就推進 400℃的爐管中,做半小時到一小時的金屬退火,這樣的溫度可以使鋁原子重新排列,使鋁(Al)和矽(Si)之間的接觸電阻(Contact resistance)下降。最後我們再使用 PECVD 疊上 3000 Å 的 SiNx,這一層可以隔絕外界水氣對記憶體元件的影響,最後再做第八道光罩微影,定義"通過"(Via)(奈米線沒有這道光罩),然後用 RIE 挖開,讓量測機台的探針的接觸到金屬鋁(Al),這樣就完成了,如圖 2-29。

圖 2-29、元件完成的剖面圖。

#### 2-2-4、離子佈值得檢測

本實驗在元件的製作過程中有兩次的離子佈值,第一次為調整臨界電壓的硼參雜 (Boron implant),第二次為汲極和源極的 n 型重參雜(phosphorous implant)。這兩次參雜 的濃度是否是我們當初所要求的,是我們檢測的目的。我們使用的量測儀器為 NDL 的 四點探針,作為試片的片電阻量測,公式 2-1。另外用 SUPREM 的軟體模擬計算我們,離子佈值的參數(parameter of implant),包含氧化層厚度,離子佈值的能量和濃度,還有 退火參數,包含溫度以及時間,這些可以推算出擴散的深度和濃度,然後以這些為參考,來計算出我們的試片的濃度,公式 2-8。

$$Rs = \frac{\rho}{t} \quad (2-1)$$

Rs=片電阻,單位為  $\Omega/\square$ 。  $\rho$ =電阻率,單位為  $\Omega.\text{cm}$ 。 t=厚度,單位為 cm。  $\rho = \frac{1}{q(\mu_{\scriptscriptstyle n} n + \mu_{\scriptscriptstyle p} p)} \tag{2-2}$

n=電子濃度,p=電洞濃度, $\mu_n$ =電子的遷移率(mobility), $\mu_p$ =電洞的遷移率(mobility)。

#### 硼參雜 (Boron Implant)

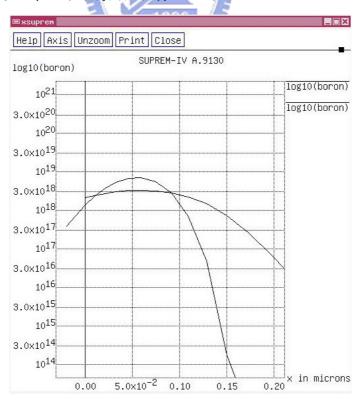

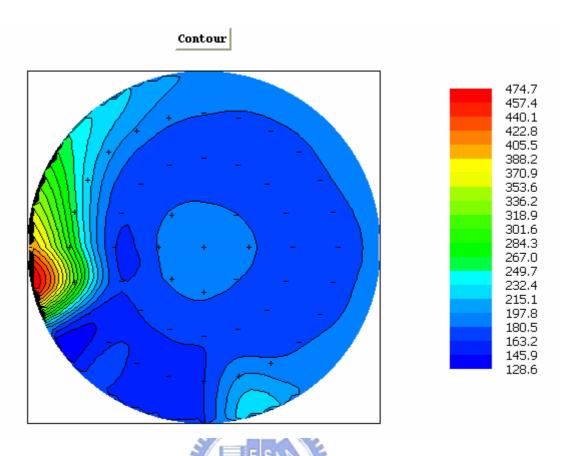

我們實驗中的硼參雜 (Boron implant)參數為 20 keV,濃度為  $5 \text{x} 10^{13} \text{/cm}^2$ ,氧化層厚度約為 200 Å。退火參數為  $950 ^{\circ}\text{C}$ ,30 分鐘。經過Suprem的分別計算出退火前後在Si的濃度曲線分布,如圖、2-30。從圖中看到兩條曲線,比較平緩的為退火之後的曲線。其在表面的濃度約為  $3 \text{x} 10^{18} \text{/cm}^3$ ,可查表出電阻率 $\rho = 3.26 \text{ x} 10^{-3} \Omega.\text{cm}$ 。深度約為 200 nm,計算後片電阻為  $1022\Omega/\square$ ,和四點探針測量平均值  $181 \Omega/\square$ ,(如表 2-2)。有 5.6 倍的差距,誤差推斷為擴散深度所造成。以  $181 \Omega/\square$ 的片電阻,計算出來擴散的深度約為 1000 nm,因此推測是退火時候所造成模擬和實驗上的誤差。

圖、2-30、硼在 Si 的擴散曲線。

#### 磷參雜(Phosphorous Implant)

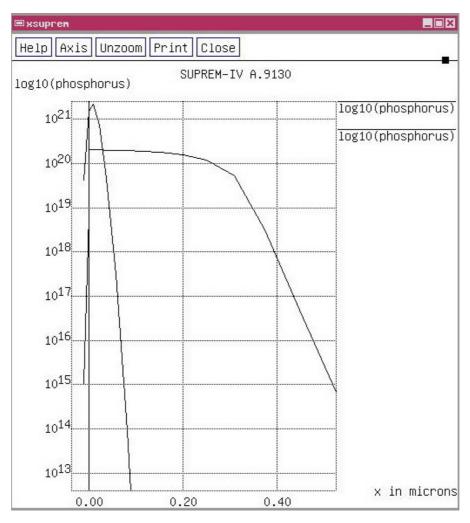

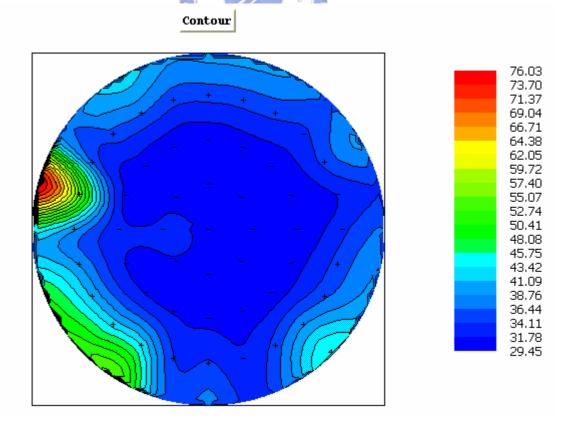

磷參雜 (Phosphorus implant)參數為 15 keV,濃度為  $5x10^{15}/cm^2$ ,氧化層厚度約為 100 Å。退火參數為  $950^{\circ}$ C,30 分鐘。經過Suprem的分別計算出退火前後在Si的濃度曲線分布,如圖、2-31。從圖中看到兩條曲線,比較平緩的為退火之後的曲線,其在表面的濃度約為  $2x10^{20}/cm^3$ ,查表出來的電阻率 $\rho$ =4.21 x  $10^{-4}$   $\Omega$ .cm。深度約為 300 nm,算出來的片電阻值為 14.03  $\Omega/\square$ ,和四點探針量測出來的 34.25  $\Omega/\square$ (如表 2-3),有 2.5 倍的差距,推斷也是退火時候所產生的誤差,Rs=34.25  $\Omega/\square$ ,所算出的擴散深度為 140 nm,在濃度為  $2x10^{20}/cm^3$ 的時候。

圖 2-31、磷在 Si 的擴散曲線。

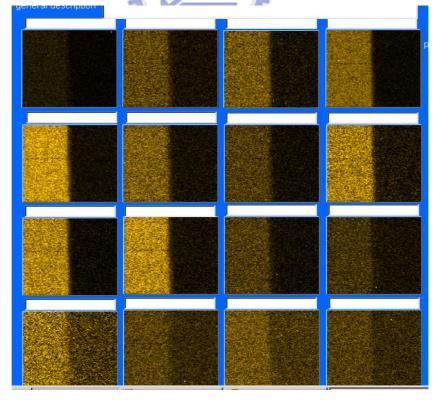

圖 2-32、硼參雜(5E13、20keV)、退火後的四點探針 49 點測量結果。

圖 2-33、磷參雜(5E15、15keV)、退火後的四點探針 49 點測量結果。

表 2-2、 硼參雜後的四點探針測量結果。

| Point No | 片電阻   |

|----------|-------|----------|-------|----------|-------|----------|-------|

| 1        | 183.9 | 15       | 164.6 | 29       | 175.6 | 43       | 313.9 |

| 2        | 180.7 | 16       | 163.8 | 30       | 175.7 | 44       | 289.3 |

| 3        | 181.3 | 17       | 165.4 | 31       | 173.9 | 45       | 255.8 |

| 4        | 183.1 | 18       | 165.6 | 32       | 173.4 | 46       | 222.7 |

| 5        | 181.6 | 19       | 165.3 | 33       | 173.6 | 47       | 203.3 |

| 6        | 183.1 | 20       | 164   | 34       | 173.9 | 48       | 194.1 |

| 7        | 182.6 | 21       | 164   | 35       | 177.5 | 49       | 185.1 |

| 8        | 182.2 | 22       | 164.5 | 36       | 185   | Average  | 181.6 |

| 9        | 182.9 | 23       | 166   | 37       | 197.8 |          |       |

| 10       | 168.2 | 24       | 165.3 | 38       | 162.7 |          |       |

| 11       | 167.5 | 25       | 166.1 | 39       | 161.4 |          |       |

| 12       | 165.5 | 26       | 181.3 | 40       | 160.6 |          |       |

| 13       | 164.3 | 27       | 177.9 | 41       | 160.7 |          |       |

| 14       | 166.1 | 28       | 176.4 | 42       | 161.2 |          |       |

ES

表 2-3、磷參雜後的四點探針測量結果。

| Point No | 片電阻   |

|----------|-------|----------|-------|----------|-------|----------|-------|

| 1        | 31.24 | 15       | 30.87 | 29       | 33.21 | 43       | 42.21 |

| 2        | 30.21 | 16       | 30.29 | 30       | 33.97 | 44       | 41.86 |

| 3        | 30.09 | 17       | 30.88 | 31       | 31.5  | 45       | 63.62 |

| 4        | 30.77 | 18       | 31.22 | 32       | 33.02 | 46       | 37.37 |

| 5        | 30.82 | 19       | 31.52 | 33       | 34.27 | 47       | 36.49 |

| 6        | 30.72 | 20       | 31.59 | 34       | 35.04 | 48       | 37.38 |

| 7        | 31.53 | 21       | 31.69 | 35       | 37.22 | 49       | 35.07 |

| 8        | 32.23 | 22       | 32.41 | 36       | 34.31 | Average  | 34.25 |

| 9        | 30.79 | 23       | 31.04 | 37       | 32.28 |          |       |

| 10       | 30.28 | 24       | 30.74 | 38       | 34.45 |          |       |

| 11       | 30.61 | 25       | 30.33 | 39       | 34.22 |          |       |

| 12       | 30.43 | 26       | 34.89 | 40       | 45.11 |          |       |

| 13       | 29.57 | 27       | 34.96 | 41       | 45.26 |          |       |

| 14       | 30.02 | 28       | 34.47 | 42       | 44.29 |          |       |

### 2-3 元件測量方法

這節我們將會介紹記憶體元件的一些量測參數的獲得方法,包括臨界電壓(threshold voltage,  $V_{th}$ ) 、次臨界斜率(subthreshold slope (S.S.)),開關電流比(On/Off current ratio) 、 F-N 穿 隧 電 流 (F-N tunneling current) 、 記 憶 時 間 (Retention time) 和 反 覆 操 作 次 數 (Endurance)。

#### 2-3-1 臨界電壓(threshold voltage, Vth)的決定

臨界電壓對於金氧半場效電晶體(MOSFET)來說是一個很重要的參數。而求臨界電壓的方法也有很多。在浮動閘極記憶體中,為了方便,定義一個固定的 Ids(源極到汲極的電流),取其所對應的 Vgs(閘極-源極壓降)數值來當做 Vth。通常取 Ids=10 nA,當 Vds=0.1 V。或是 Ids=100 nA,當 Vds=5 V。

#### 2-3-2 次臨界斜率(subthreshold slope (S.S.))

次臨界斜率(Subthreshold slope S.S). (V/dec)是一個重要的參數,其可以代表一個元件他的閘極的控制能力的程度。當S.S.越小,表示閘極的控制能力越好。而S.S.跟汲極和閘極的電壓是有相關的(independent of drain voltage and gate voltage)。另外,S.S.和元件的結構也很很大的關係,S.S.變小會因為短通道效應(Short-channel effects)的影響。而在本實驗中,S.S.是取Ids=10 nA到1 fA對應Vgs斜率的倒數。

#### 2-3-3 開關電流比(On/Off current ratio)

開關電流比(On/Off current ratio)對於金氧半場效電晶體(MOSFET)是另一個重要的參數。高的 On/Off 比值,就表示有比較高的開電流(On current)和比較小的關電流(Off current)。越高的開關電流比(On/Off current ratio),也有越容易區隔開和關的兩種狀態。計算開關電流比(On/Off current ratio)的方法很多種,在本實驗的計算方式是取 Vgs=5 V時候的 Ids 當作 Turn on current,除以最小的 Ids,再取 Log 值。

#### 2-3-4 F-N 穿隧電流(F-N tunneling current)的決定

F-N穿隧電流(F-N tunneling current)在前一章有介紹,這是浮動閘極記憶體用來清除浮動閘極(Floating gate)中的電子所使用的一個機制。公式(2-3)是一個F-N穿隧電流(F-N tunneling current) 對電場的表示式, $\alpha$ 和 $\beta$ 在固定的結構中是常數。因此公式中的變數只有 J(current density)和 E(electric field),經過一個簡單的轉換,可以從公式(2-7)  $\ln\left(\frac{J}{E^2}\right) \propto -\frac{\beta}{E}$ ,我們對 $\ln(J/E^2)$ 和 1/E做圖可以得到一個斜率為負的直線,另外,F-N穿隧電流(F-N tunneling current)和溫度是沒有關係的,所以當我們在不同溫度下做電流的測量,所得到的結果應該是要一樣的。

$$J = \alpha E^{2} \exp\left(-\frac{\beta}{E}\right) \qquad (2-3) \qquad \alpha = \frac{q^{3}}{16\pi^{2}\hbar\phi_{B}} \qquad \beta = \frac{4\sqrt{2m^{*}\phi_{B}^{3}}}{3\hbar q}$$

$$\ln\left(\frac{J}{\alpha E^{2}}\right) = -\frac{\beta}{E} \qquad (2-4)$$

$$\ln\left(\frac{J}{E^{2}}\right) - \ln(\alpha) = -\frac{\beta}{E} \qquad (2-5)$$

$$\ln\left(\frac{J}{E^{2}}\right) = \ln(\alpha) - \frac{\beta}{E} \qquad (2-6)$$

$$\ln\left(\frac{J}{E^{2}}\right) \propto -\frac{\beta}{E} \qquad (2-7)$$

J:電流密度, The current density

E:電場, The electric field

q:電荷常數。

m\*:電子在穿隧物體中的等效質量

$\hbar$ :plank constant  $/2\pi$

$\phi_R$ :電子穿隧時所面對的能障高度。

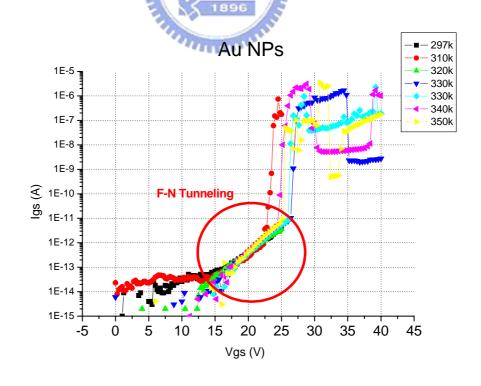

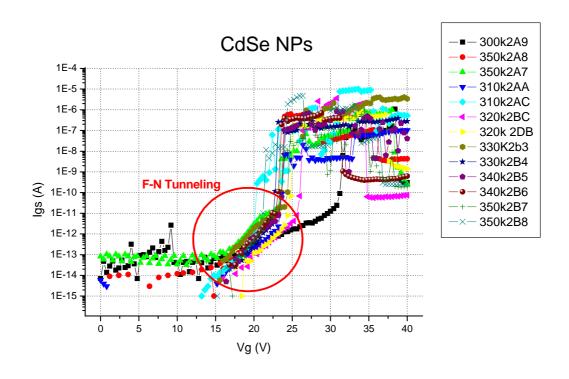

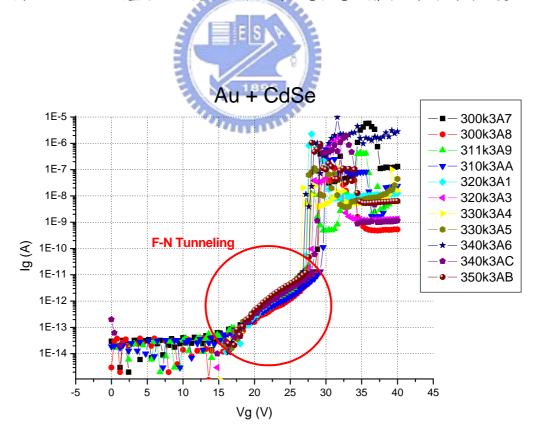

我們想證明記憶體操作是在F-N穿隧電流(F-N tunneling current)機制。首先在各種不同問度下量測Vgs-Igs,從Vgs=0V加到Vgs=40V,以二氧化矽所能承受的電場約 10 MV/cm來看,我們的元件大約在 25~30V會崩潰(Breakdown)。然而F-N穿隧(F-N tunneling current)

是發生在接近崩潰但是還沒崩潰的區域。因此取那個區域的電壓-電流值,再經過換算 為 $\ln(J/E^2)$ 和 1/E,從圖中看是否為一條線性的曲線判斷是否為穿隧電流(F-N tunneling current)。

#### 2-3-5 記憶時間(Retention time)的決定

記憶時間(Retention time)對於記憶體是一個很重要的參數,我們首先將電子寫入 (Prohram),並且每隔一段時間測量 Vgs-Ids,並且判斷 Vth 的數值,最後將 Vth 和時間 做圖,可以看出這個記憶體的記憶時間(Retention time)的長短。除了寫入還會做清除 (Erase)的記憶時間。

#### 2-3-6 反覆操作次數(Endurance)的決定

我們將電子寫入(Program)浮動閘極(Floating gate)中並且再將電子清除(Erase),不斷的翻覆這樣的動作,然後判斷  $\Delta V$ th 對 P/E 次數的變化。

1896

# 第三章.

# 記憶體元件量測結果和討論

# (Memory device measurement and discussion)

前面一章節介紹本實驗的計體的製作方式流程和要探討的項目。本章節將會對於實際完成的記憶體元件做量測,並且做討論。將有三小節探討發表我們記憶體元件的特性,分別為基本操作應用(Basic driving device application)、非揮發記憶體的寫入和清除應用(Program and erase of nonvolatile memory application)、以及可靠度之記憶時間應用(Reliability of retention time)。最後一小節會統整全部做一個討論。

# ES

#### 3-1 基本操作應用(Basic driving device application)

本節將對我們做出來的三種不同浮動閘極的記憶體, $1.金奈米粒子、2.硒化編量子點和3.金加硒化編量子點,還有沒有控制閘極的控制組(Control),做基本電性操作的應用,包含量測臨界電壓(<math>V_{th}$ )、次臨界斜率(subthreshold slope (S.S.))和開闢電流比(On/Off current ratio)。

#### 3-1-1 臨界電壓(Vth)

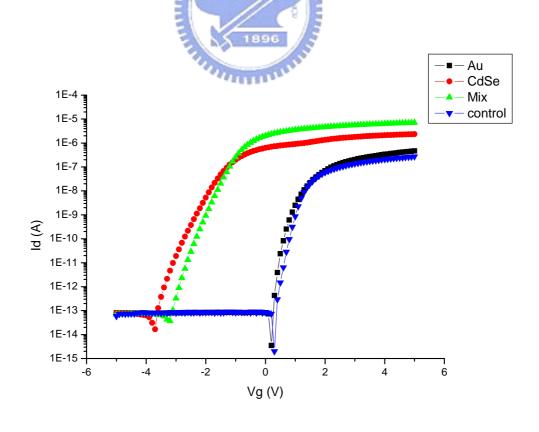

本實驗所使用的量測儀器為安捷倫肆壹伍伍和肆壹伍陸(4155&4156),測量的參數是閘極電壓由負五到正五(Vg=-5 to Vg=5 V),汲極電壓為 0.1 V(Vd=0.1 V),源極接地 (Vs=0 V)。量測閘極電壓對汲極電流的變化(Vg vs. Id)。量測的元件是的通道長度是 5  $\mu m$ ,寬度是 100 nm。並計算臨界電壓(Vth),當電流為 10 pA 的時候。

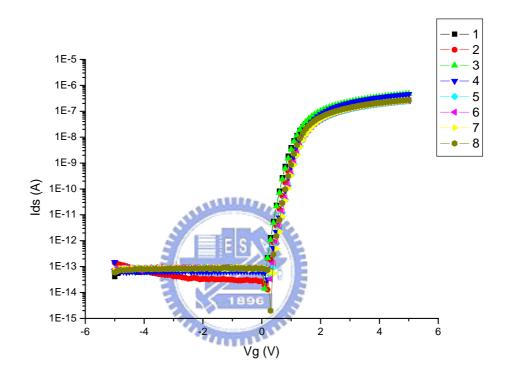

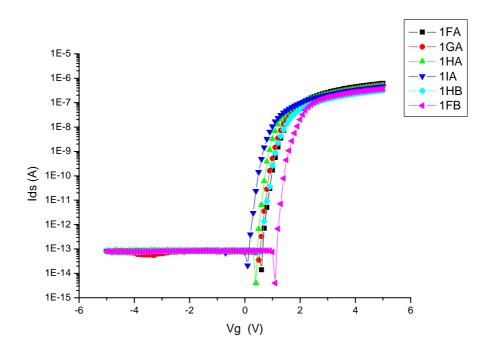

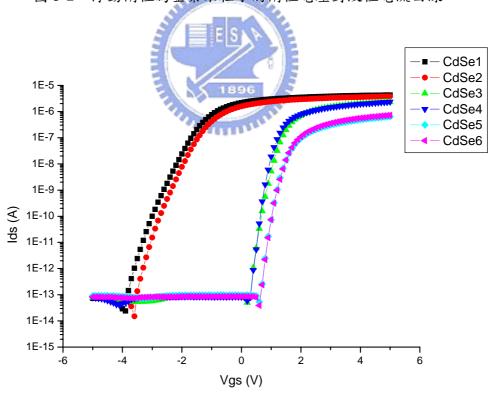

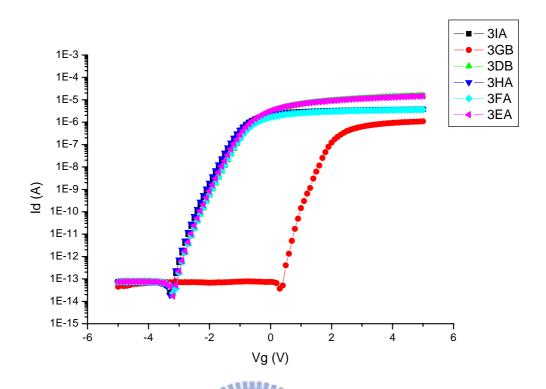

首先我們量測控制組總共 8 個不同的元件的閘極電壓對汲極電流的變化(Vg vs.

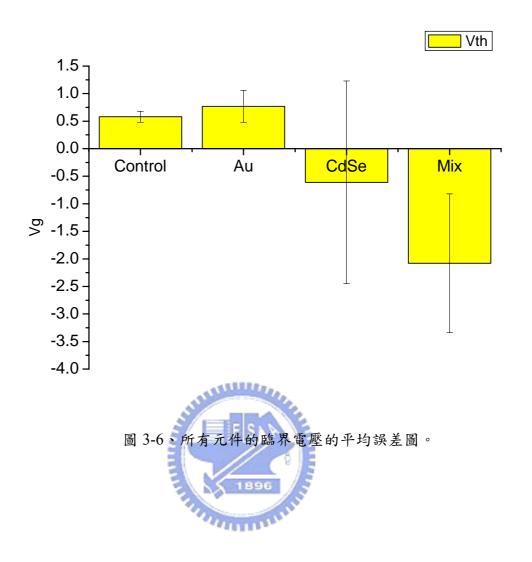

Id),如圖 3-1。6 個不同金奈米粒子元件閘極電壓對汲極電流的變化(Vg vs. Id),如圖 3-2。6 個不同硒化編量子點元件閘極電壓對汲極電流的變化(Vg vs. Id),如圖 3-3。6 個不同金加硒化編量子點元件閘極電壓對汲極電流的變化(Vg vs. Id),如圖 3-4。最後,將上面各表的值做平均,統整在一個圖上,如圖 3-5。並計算平均以及誤差(標準差)將其做成長條圖,如圖 3-6,也把所有數值統整在表 3-1 內。

圖 3-1、8 個不同控制組閘極電壓對汲極電流的曲線。

圖 3-2、浮動閘極為金奈米粒子的閘極電壓對汲極電流曲線。

圖 3-3、浮動閘極為硒化鎘量子點的閘極電壓對汲極電流曲線。

圖 3-4、浮動閘極為金加上硒化鎘量子點的閘極電壓對汲極電流曲線。

圖 3-5、控制組和奈米粒子記憶體(取平均)閘極電壓對汲極電流曲線。

表 3-1、所有元件的臨界電壓的平均和誤差表。

| Vth     | 1       | 2       | 3       | 4       | 5       | 6       | 7      | 8      | Ave     | Error  |

|---------|---------|---------|---------|---------|---------|---------|--------|--------|---------|--------|

| Control | 0.6167  | 0.6763  | 0.6593  | 0.7055  | 0.4251  | 0.5471  | 0.4310 | 0.6104 | 0.5839  | 0.1005 |

| Au      | 0.8198  | 0.7260  | 0.6068  | 0.3337  | 0.8037  | 1.3041  |        |        | 0.7657  | 0.2909 |

| CdSe    | -3.3294 | -3.0611 | 0.5147  | 0.5096  | 0.8526  | 0.8610  |        |        | -0.6088 | 1.8360 |

| Mix     | -2.6975 | 0.7408  | -2.5811 | -2.7339 | -2.5870 | -2.6066 |        |        | -2.0775 | 1.2617 |

控制組的臨界電壓平均是 0.58 V,誤差(標準差)是 0.1 V。金奈米粒子(AuNPs)浮動 閘極記憶體的臨界電壓平均是 0.77 V,誤差(標準差)是 0.29 V。硒化編量子點浮動閘極記憶體的臨界電壓平均是負 0.61 V,誤差(標準差)是 1.84 V。金加硒化編量子點浮動閘極記憶體的臨界電壓平均是負 2.08 V,誤差(標準差)是 1.26 V。

可以看到臨界電壓隨著我們沉積的奈米粒子越多,他的誤差變異(標準差)就越大。 從臨界電壓的公式來看,臨界電壓在整個結構固定下,可以影響的數值只剩下氧化層中 的電荷數目,因為我們沉積的奈米粒子都是有帶電荷的,若是沉積在不同元件中的數目 有差異的話,變化造成這樣的影響。

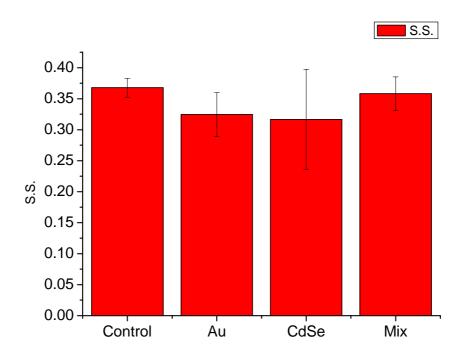

### 3-1-2 次臨界斜率(subthreshold slope)

次臨界斜率可以看出元件閘極對於通道的控制能力好壞。其值越小表示控制能力越好。我們也將剛才所測量的閘極電壓對汲極電流的變化(Vg vs. Id),取汲極電流 10 奈安(10-8 A)到 100 奈安(10-9 A)對閘極電壓斜率的倒數就是所謂的次臨界斜率(V/dec)。

圖 3-7 是將四種元件的次臨界斜率(subthreshold slope)做長條圖的整理,並且標上誤差(標準差)。從圖表中可以看出,S.S.在不同情況下有不同的數值,不過因為靠率誤差值之後,整體將沒有什麼差別,推斷元件的的 S.S.都是差不多的。

圖 3-7、所有元件次臨界斜率的的平均和誤差圖。

表 3-2、所有元件的次臨界斜率的平均和誤差的比較。

|         |        |        |        | The second Contract of the last | Charge of Assertan | A CONTRACTOR OF THE PARTY OF TH |        |        |        |        |

|---------|--------|--------|--------|---------------------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|

| S.S.    | 1      | 2      | 3      | 4                               | 5                  | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7      | 8      | Ave    | Error  |

| Control | 0.3735 | 0.3781 | 0.3740 | 0.3391                          | 0.3480             | 0.3855                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0.3647 | 0.3790 | 0.3677 | 0.0152 |

| Au      | 0.3035 | 0.3138 | 0.2886 | 0.3468                          | 0.3925             | 0.3025                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | 0.3246 | 0.0353 |

| CdSe    | 0.4401 | 0.4161 | 0.2279 | 0.2819                          | 0.2650             | 0.2687                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | 0.3166 | 0.0808 |

| Mix     | 0.3589 | 0.3000 | 0.3816 | 0.3700                          | 0.3763             | 0.3617                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |        | 0.3581 | 0.0271 |

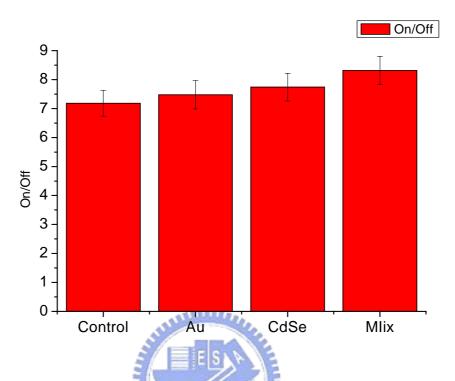

#### 3-1-3 開關電流比(On/Off current ratio)

開關電流比(On/Off current ratio)越高,將會越容易分辨開和關。圖 3-8 是將四種元件的次開關電流比(On/Off current ratio)做長條圖的整理,並且標上誤差(標準差)。從表 3-3 可看出隨著沉積的奈米粒子越多,開關電流比(On/Off current ratio)也就越高,控制組的開關電流比臨界電壓平均是 7.19,誤差(標準差)是 0.44。金奈米粒子浮動閘極記憶體的開關電流比臨界電壓平均是 7.48,誤差(標準差)是 0.49。硒化鎘量子點浮動閘極記

憶體的開關電流比臨界電壓平均是 7.74, 誤差(標準差)是 0.47。金加硒化編量子點浮動 閘極記憶體的開關電流比臨界電壓平均是 8.32, 誤差(標準差)是 0.49。

圖 3-8、所有元件開闢電流比的的平均和誤差圖。

表 3-3 所有元件的開關電流比的平均和誤差的比較。

| On/Off  | 1      | 2      | 3      | 4      | 5      | 6      | 7      | 8      | Ave    | Error  |

|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|

| Control | 8.1351 | 6.7386 | 6.8914 | 6.6651 | 7.0889 | 7.2840 | 7.5241 | 7.1548 | 7.1853 | 0.4463 |

| Au      | 7.6420 | 7.1883 | 8.0881 | 7.3415 | 6.6418 | 7.9590 |        |        | 7.4768 | 0.4886 |

| CdSe    | 8.2533 | 8.4048 | 7.6646 | 7.7690 | 7.0839 | 7.2663 |        |        | 7.7403 | 0.4773 |

| MIix    | 8.1714 | 7.4692 | 8.8423 | 8.3033 | 8.1845 | 8.9309 |        |        | 8.3169 | 0.4849 |

# 3-2 非揮發記憶體的寫入和清除應用(Program and erase of nonvolatile memory application)

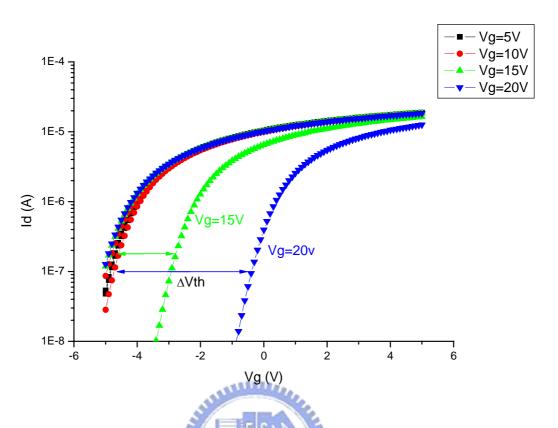

在本節我們討論沉積三種不同條件的奈米粒子(金、硒化鎘、金加上硒化鎘的混合) 非揮發浮動閘極記憶體,當我們施加不同的寫入電壓(Program voltage)時,會有多少的 記憶窗戶(Memory windows)也就是臨界電壓( $\Delta V$ th)的變化。最後我們會討論我們寫入和清除的機制,是否為我們先前所預測的 F-N 穿隧(F-N tunneling)。

# 3-2-1 寫入和清除電壓(Program and erase voltage)對記憶窗戶(memory window)的影響

我們使用的機台一樣是安捷倫肆壹伍伍和肆壹伍陸(4155&4156)。實驗的步驟如下:

- 1. 量測一次閘極電壓對汲極電流(Vg vs. Id),如圖 3-9 黑線。

- 2. 對元件做一次清除(Erase),條件為源極開路(Vs=Open), 閘極加-30V, 汲極為 5 V(Vd=5 V), 所施加電壓的時間為 1 s。

- 3. 接著量測一次閘極電壓對汲極電流(Vg vs. Id),並判斷臨界電壓的偏移,如圖 3-9 紅線。

- 4. 接著對記憶體元件寫入,條件為源極開路(Vs=Open), 閘極加 1 到 20 V,每個步驟增加 5 V,沒極為-5 V(Vd=-5 V),所施加電壓的時間為 100 ms。

- 5. 再一次量測閘極電壓對汲極電流(Vg vs. Id),並判斷臨界電壓的偏移,如圖 3-9 綠線。 。然後再重複 1 到 5 步驟,其中第 2 步驟,施加的閘極電壓依序為 1 V、5 V、10 V、15 V和 20 V,如圖 3-10。

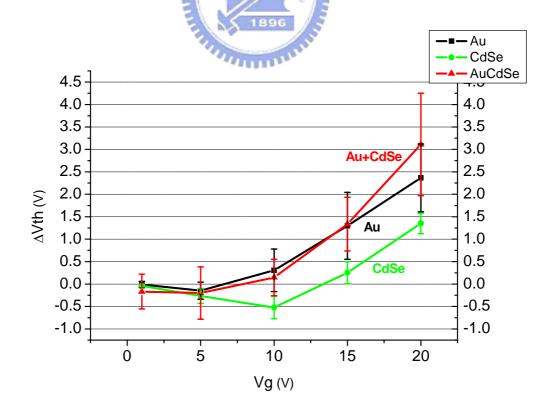

本實驗的記憶體分別沉積 1.金奈米粒子(Au NPs)。2.硒化鎘量子點(CdSe NPs)。3. 混合金和硒化鎘量子點(Au+CdSe NPs)。三種不同的條件所測量出來的臨界電壓偏移做統整在,表 3-4、表 3-5 和表 3-6 以及圖 3-11。

從統計的結果來看,金(Au)奈米粒子在Vg=20V的臨界電壓變化為 2.37V,硒化鎘 (CdSe)量子點在Vg=20V的臨界電壓變化為 0.87V。混合金和硒化鎘(Au+CdSe)奈米粒子的臨界電壓變化為 3.11V。雖然有蠻大的變異,不過可以輕易的看出混合金和硒化鎘 奈米粒子的臨界電壓變化,是最大的。

圖 3-9、記憶體元件的寫入和清除的操作,此數據為沉積金和硒化鎘(Au+CdSe NPs)。

圖 3-10、不同閘極電壓對應不同臨界電壓偏移。

圖 3-11、統計三種條件下的臨界電壓變化(ΔVth)和閘極電壓的關係。

表 3-4 金奈米粒子(Au)記憶體,寫入電壓對應之臨界電壓偏移。

| Vg   | Au1  | Au 2  | Au 3  | Au 4  | Au 5  | Ave   | Error |

|------|------|-------|-------|-------|-------|-------|-------|

| 1 V  | 0.00 | 0.00  | -0.06 | 0.11  | -0.10 | -0.01 | 0.07  |

| 5 V  | 0.14 | -0.36 | -0.27 | -0.26 | 0.01  | -0.15 | 0.19  |

| 10V  | 0.24 | -0.57 | 0.42  | 0.71  | 0.73  | 0.31  | 0.47  |

| 15 V | 0.41 | 0.45  | 1.46  | 2.15  | 2.02  | 1.30  | 0.75  |

| 20 V | 1.33 | 1.68  | 2.63  | 3.39  | 2.80  | 2.37  | 0.76  |

表 3-5 硒化鎘量子點(CdSe)記憶體,寫入電壓對應之臨界電壓偏移。

|      | CdSe1 | CdSe2 | CdSe3 | CdSe4  | CdSe5 | CdSe6 | Ave   | Error |

|------|-------|-------|-------|--------|-------|-------|-------|-------|

| 1 V  | -0.05 | 0.00  | 0.00  | -0.06  | -0.03 | -0.01 | -0.03 | 0.02  |

| 5 V  | -0.47 | -0.01 | 0.00  | -0.26  | -0.27 | -0.07 | -0.18 | 0.17  |

| 10 V | -0.68 | -0.02 | -0.04 | 1-0.62 | -0.64 | -0.15 | -0.36 | 0.29  |

| 15 V | 0.21  | -0.05 | -0.03 | 0.00   | 0.21  | 0.59  | 0.16  | 0.22  |

| 20 V | 1.49  | -0.08 | -0.08 | 1.04   | 1.55  | 1.32  | 0.87  | 0.69  |

表 3-6 金加硒化鎘量子點(Au+CdSe)記憶體,寫入電壓對應之臨界電壓偏移。

|      | Mix1  | Mix2  | Mix3 | Mix4  | Mix5  | Ave   | Error |

|------|-------|-------|------|-------|-------|-------|-------|

| 1 V  | 0.00  | 0.00  | 0.10 | -0.94 | 0.00  | -0.17 | 0.39  |

| 5 V  | -0.04 | -0.02 | 0.47 | -1.29 | -0.12 | -0.20 | 0.58  |

| 10 V | 0.19  | 0.18  | 0.86 | -0.25 | -0.25 | 0.15  | 0.41  |

| 15 V | 2.03  | 1.94  | 1.40 | 0.65  | 0.65  | 1.33  | 0.60  |

| 20 V | 4.56  | 4.43  | 2.46 | 2.05  | 2.05  | 3.11  | 1.14  |

#### 3-2-2 不同寫入機制的影響

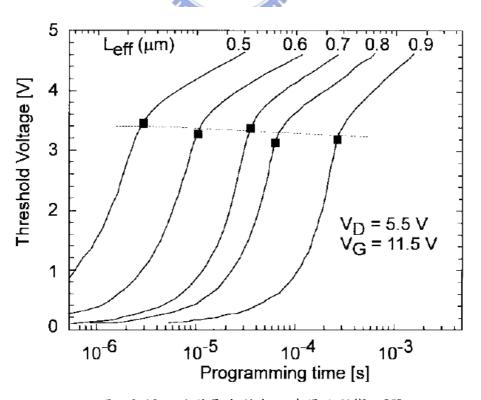

在第一章有提到寫入機制,分為兩種,一種是FN穿遂和熱電子注入(Hot Electron Injection)兩種,在一般的元件操作大部分是以熱電子注入(Hot Electron Injection)來寫入電子,因為操作的速度較快,大約在  $1 \mu s$ 到  $100 \mu s$ 。因為,熱電子注入操作在元件飽和區,所以電子在通道中(Channel)已經被加速到約  $10^7 \, cm/s$ ,這是電子在矽半導體中的極限速度,然後再被閘極的電場吸引穿過穿隧氧化層(tunneling oxide)。反觀F-N穿遂機制,電子是從汲極(drain)直接被閘極電場所吸引而穿隧過穿隧氧化層(tunneling oxide),通常要  $0.1 \, s$ 到  $1 \, s$ ,在沒有先被加速的情況下,因此,F-N穿遂的寫入速度會比熱電子注入(Hot Electron Injection)慢上許多。

另外,熱電子注入(Hot Electron Injection)機制的速度會受到通道長度的影響,當通道越長,所需要謝入的時間也就越長[5], (如圖、3-12)。從圖中看出越長的通道,其所需要的寫入時間越長。

圖、3-12、通道長度對寫入時間的影響。[5]

在本實驗中的元件通道是  $5 \mu m$ ,這樣的通道長度相當的長,使用熱電子注入(Hot Electron Injection)寫入或是 F-N 穿隧寫入,所需要的時間是差不多的,也就是熱電子注入(Hot Electron Injection)在比較長通道的元件中,並沒有太大的優勢。實際元件測量金奈米粒子和硒化鎘量子點的混合記憶體,使用的參數如表 3-7,測量結果為圖 3-15,從測量結果看來熱電子注入(Hot Electron Injection)寫入在本實驗的元件中並沒有比較快,因此本實驗的謝入機制均為 F-N 穿遂機制。

HEI FN 20 V 20 V Vg Vd 6 V -5 V Vs Open - HEI FΝ 2.6-2.4 2.2 2.0 1.8 1.6 1.4 1.2 1.0 8.0 0.6 0.4 0.2 -0.0 10<sup>-3</sup> 10<sup>-6</sup> 10<sup>-4</sup> 10<sup>-2</sup> 10<sup>-7</sup> 10<sup>-5</sup> Time (sec)

表 3-7、HEI 以及 FN 的操作參數。

圖 3-13、F-N 穿隧和 HEI 機制對謝入時間的影響。

#### 3-2-3 金奈米粒子儲存的電荷

當我們有了臨界電壓偏移( $\Delta V$ th)後,以及浮動閘極的電容( $C_{FC}$ ),從公式(3-1)中我們可以算出浮動閘極總共的電荷變化量( $\Delta Q_{FG}$ ),也就是電荷的儲存量。

$$\Delta Vth = -\frac{\Delta Q_{FG}}{C_{FG}} \qquad (3-1)$$

其中, C<sub>FC</sub>在本實驗是由兩個電容串聯C'和C"而成,因為結構為雙層的奈米粒子,對應的氧化層厚度t'<sub>0x</sub>和t''<sub>0x</sub> 都是 25 nm。

$$\frac{1}{C_{FC}} = \frac{1}{C'} + \frac{1}{C'} = \frac{t'_{ox}}{\varepsilon_{ox}} + \frac{t''_{ox}}{\varepsilon_{ox}}$$

(3-2)

$C_{FC}=6.9 \times 10^{-6} \, \text{F/cm}^2$  ,所以 $\Delta Q_{FG}=1.63 \times 10^{-5} \, \text{C/cm}^2$  (金的 $\Delta V$ th=2.37 V , 在Vg=20 V的 時候)。從SEM的圖片中可知道,金的密度為  $1.68 \times 10^{11} \,$  顆/cm² ,因為雙層結構所以密度為兩倍  $3.36 \times 10^{11} \,$  顆/cm² ,所以每一顆所儲存的電荷量為  $4.8 \times 10^{-17} \,$  C ,也就等於  $302.78 \,$  顆的電子。至於硒化鎘(CdSe)和混合金和硒化鎘(CdSe),都因為沒有辦法知道硒化鎘(CdSe)的密度而無法計算。

## 3-2-4 F-N 穿隧 (F-N tunneling)的驗證。

F-N 穿隧的機制在 2-3-4 有比較詳細的說明,從公式(3-3)推到(3-5),可以知道 F-N 穿隧的電流電壓的關係。

$$J = \alpha E^{2} \exp\left(-\frac{\beta}{E}\right)$$

$$\ln\left(\frac{J}{E^{2}}\right) = \ln(\alpha) - \frac{\beta}{E}$$

(3-3)

$$\alpha = \frac{q^{3}}{16\pi^{2}\hbar\phi_{B}}$$

$$\beta = \frac{4\sqrt{2m^{*}\phi_{B}^{3}}}{3\hbar q}$$

(3-4)

$$\ln\left(\frac{J}{E^2}\right) \propto -\frac{\beta}{E} \tag{3-5}$$

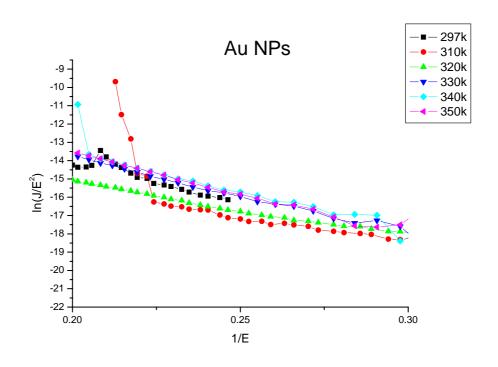

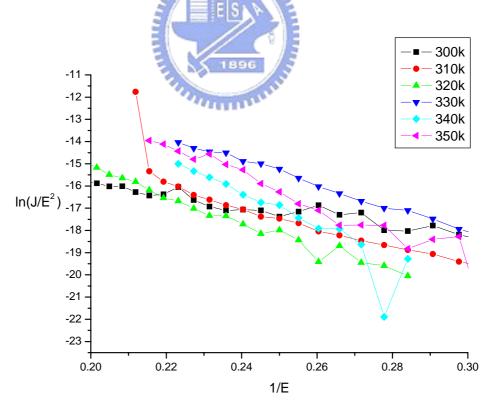

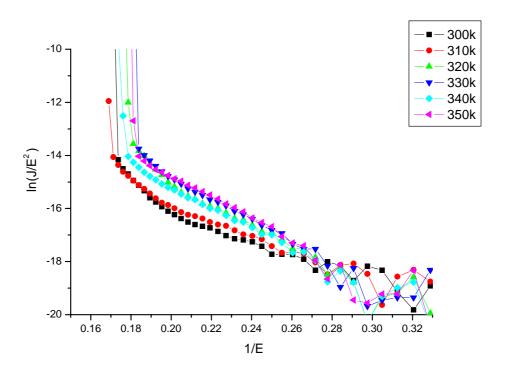

本實驗測量閘極電壓和閘極電流(Vg vs. Ig)的關係,閘極電壓從零加到四十(Vg=0 V to 40 V),如圖 3-14、3-15 和 3-16。並且使用可以變溫的量測系統,使用六種不同的溫度 300 K(297 K)、310 K、320 K、330 K、340 K 和 350 K,來看溫度對於電流是否有影響。本實驗測量後,該元件在 Vg=25~30 V 就會崩潰(Breakdown),因此,更換不同溫度時,也就會換另一個元件做測量。

圖 3-14、金奈米粒子記憶體元件, 閘極電壓電流關係, 在不同的溫度。

圖 3-15、硒化鎘量子點記憶體元件,閘極電壓電流關係,在不同的溫度。

圖 3-16、金奈米粒子加硒化鎘量子點記憶體元件, 閘極電壓電流關係, 在不同的溫度。

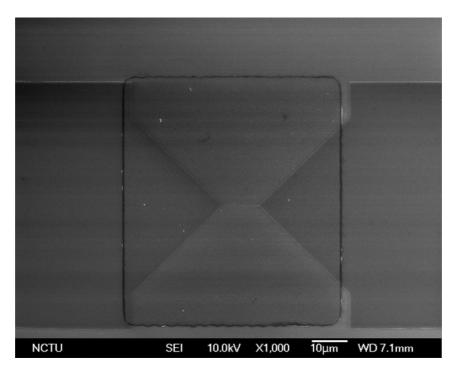

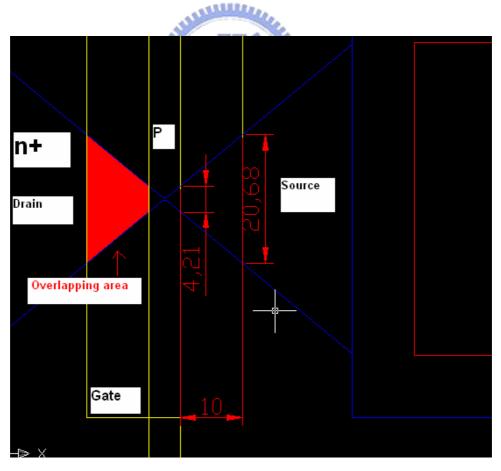

從圖 3-14、圖 3-15 和圖 3-16 中可以看到,當電壓加超過介電質所能承受時,就歲產生崩潰,此時電流會大幅的上升,大約  $1 \, \mathrm{dec/V}$ ,增加一伏特的電壓,電流上升  $10 \, \mathrm{dec}$  然後這個元件就壞了。不過,在接近崩潰之前,由紅色圈圈框起來的地方,就是要探討的區域。因此,我們將此區域的數據做  $\ln\left(\frac{J}{E^2}\right)$  和  $\frac{1}{E}$  的圖,其中J位電流密度,是電流I除以控制閘極(Control gate)和 汲極(Drain)的交疊面積(Overlapping area),如圖 3-17。E電場(V/cm)是閘極電壓除以通道(Channel)到控制閘極(Control gate)的厚度,大約為 50 奈米(50nm=5x $10^{-6}$  cm)。圖 3-18、圖 3-19 和圖 3-20,分別是金、硒化鎘和混合金和硒化鎘的  $\ln\left(\frac{J}{E^2}\right)$  對應  $\frac{1}{E}$  的圖形,可以看出曲線為一個斜率為負的曲線,符合F-N穿隧 (F-N tunneling)公式(2-7),另外,不同的溫度對於斜率也沒有影響,不過在y軸截距上有些影響,但是卻沒有和溫度有什麼相關性,所以判斷這是不同元件之間的變異。

圖 3-17、閘極和汲極交疊面積(Overlapping area),面積為 124.45  $\mu m^2$ 。

圖 3-19、硒化編量子點記憶體,  $\ln\left(\frac{J}{E^2}\right)$ 和  $\frac{1}{E}$  的關係,在不同溫度下。

圖 3-20、金加上硒化鎘量子點記憶體, $\ln\left(\frac{J}{E^2}\right)$ 和 $\frac{1}{E}$ 的關係,在不同溫度下。

# 3-3 可靠度之記憶時間 (Reliability of retention time)

#### 3-3-1 記憶時間(Retention time)

記憶時間(Retention time)的測量的步驟如下

- 對記憶體元件寫入電子,寫入參數為閘極電壓 20 V (Vg=20 V)、汲極電壓-5 V (Vd=-5 V)、源極開路 (Vs=Open),時間為 100 ms。

- 2. 每隔一段對時間對記憶體做讀取的動作,讀取參數為閘極電壓為-5 V到 5 V (Vg=-5~5),汲極電壓 0.1 V(Vd=0.1 V)、源極接地(Vs=0 V),並且判斷臨界電壓。量測時間通常為  $10^4$ 到  $10^5$ 秒。

- 3. 將第1步驟寫入改為清除,清除條件為閘極電壓-20 V(Vg=-20 V)、汲極電壓 5 V (Vd=5V)、源極開路 (Vs=Open),時間為1s。

- 4. 每隔一段對時間對記憶體做讀取的動作,讀取參數為閘極電壓為-5 V到 5 V (Vg=-5~5 V),汲極電壓 0.1 V (Vd=0.1 V)、源極接地(Vs=0 V),並且判斷臨界電壓。量測時間 通常為  $10^4$ 到  $10^5$ 秒。

- 5. 最後將臨界電壓和時間做圖

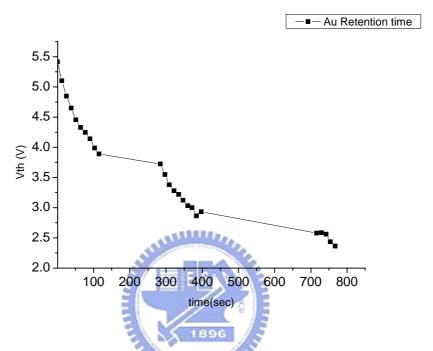

本實驗分別對三種不同浮動閘極條件的記憶體量測記憶時間(Retention time)。三種條件分別為金奈米粒子,如圖 3-21。硒化編量子點,如圖 3-22。金和硒化編量子點混合,如圖 3-23。

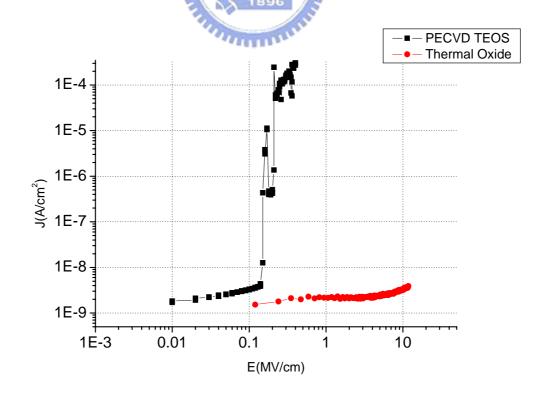

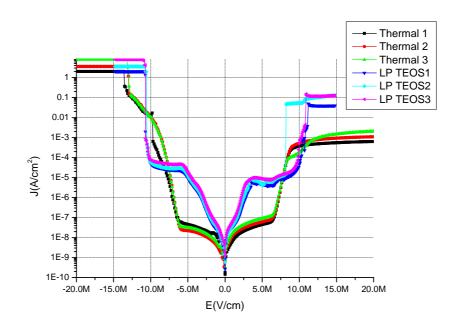

本次實驗所用的控制氧化層(Control oxide)的厚度為 25 nm,而我們做的是雙層的結構,所以就是乘於 2 為 50 nm。控制氧化層(Control oxide)是由NDL的PECVD所長出的TEOS,而這台機器所長出的TEOS和爐管長出的二氧化矽(SiO<sub>2</sub>)的漏電比起來,TEOS的品質是相當的不好,如圖 3-24。所以這對於記憶體元件的記憶時間(Retention time),的結果並不是很看好,會建議使用絕緣性更好的LPCEV來取代PECVD,從圖 3-25 可以看到LPCVD的漏電和Thermal oxide比較起來是比較差,但是差距沒有像PECVD TEOS那樣的差,圖 3-26 則是漏電測試片的製作流程。

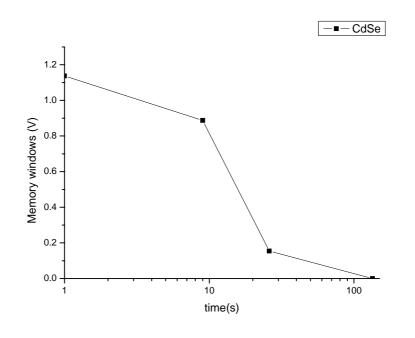

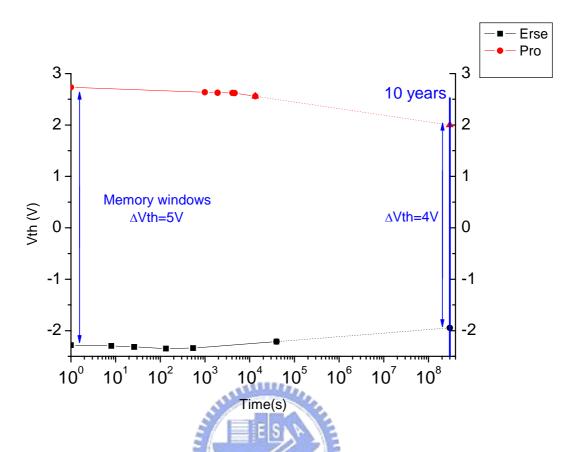

從這三張圖中可以明顯看到,單獨一種奈米粒子的記憶體,像是金奈米粒子(AuNPs)和

硒化鎘量子點(CdSe NPs)的記憶時間都相當的短,而當我們混合這兩種奈米粒子,他的記憶時間就被大大的拉長至少都  $10^4$ 秒,這結果是超出我們期望的好。而由所測得的數據推斷,記憶窗Memory windows)。由一開始的 5 V,過了十年應該可以保有 4 V就是 80%的記憶窗 (Memory windows)

圖 3-21、金奈米粒子的記憶時間(Retentions time of Au NPs)。

圖 3-22 硒化鎘量子點的記憶時間(Retentions time of CdSe Qdots)。

圖 3-23 混合金和硒化鎘量子點的記憶時間(Retentions time of Au+CdSe NPs)。

圖 3-24、PECVD TEOS 和爐管成長的氧化矽閘極電壓對電流曲線。

圖 3-25、LPCVD TEOS 和爐管成長的氧化矽閘極電壓對電流曲線。

圖 3-26、漏電測試試片的製作流程。

#### 3-4 討論(Discusssion)

本實驗的奈米粒子是利用自組裝的方式沉積在奈米線的上面,因為 SAM 的均勻度 對於奈米線的變異蠻大,導致初始狀態(Initial state)的臨界電壓(Vth)有些不同,不過對 於元件結構所影響的參數如次臨界斜率(subthreshold slope)、開關電流比(On/Off current ratio)就沒有什麼差異。

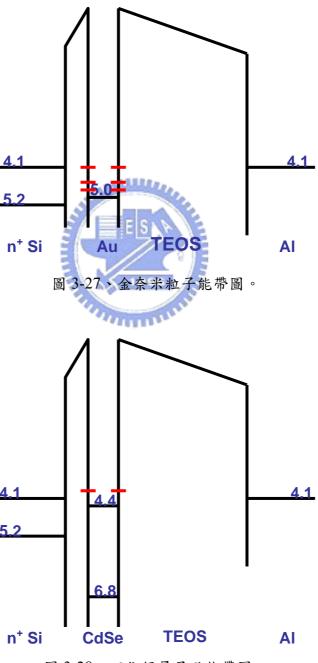

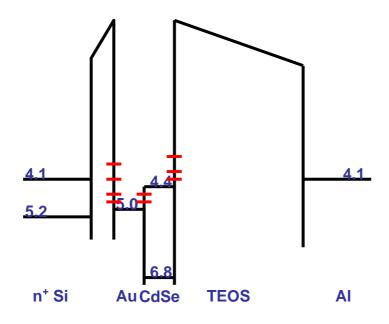

而操作不同的寫入電壓(Vg)對於臨界電壓變化( $\Delta Vth$ ),則是越大的寫入電壓,相對會有比較大的臨界電壓變化,因為電子,受到控制閘極(Control oxide)的吸引,穿隧過穿隧氧化層(Tunneling oxide)到達奈米粒子所形成的浮動閘極(Floating gate),然後被奈米粒子(Nanopaarticles)捕捉住(trap),然後電子會儲存在奈米粒子(Nanoparticles)和二氧化矽(SiO<sub>2</sub>)的接面狀態(Interface state)。另外,金在奈米的尺度下會有能階的產生,加上金有很深的功函數(work function),可以捕捉更多的電子,如圖 3-27。所以從能帶圖來看,可以看到金所形成的臨界電壓變化( $\Delta Vth$ ) 比半導體材料的硒化鍋(CdSe)來的大的許多,如圖 3-28。

而當我們混合這兩種奈米粒子,金和硒化鎘(Au and CdSe),會產生更大的臨界電壓變化( $\Delta$ Vth),主要的原因就是奈米粒子之間會有更多的接觸面,也就形成更多的接觸狀態(Interface state)。所以相對的臨界電壓變化( $\Delta$ Vth)就會更大,如圖 3-29。

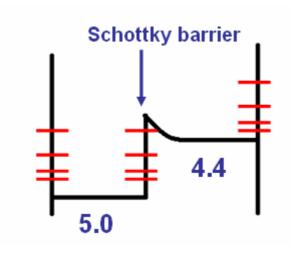

而在記憶時間(Retention time)方面,混合金和硒化鎘(Au and CdSe)的記憶體有很好的儲存能力,推測是電子被捕捉(trap)而儲存在金和硒化鎘(Au and CdSe)的接面,如圖

3-29。而金和硒化鎘(Au and CdSe)之間是半導體和金屬的接面,所謂的蕭特基接面 (Schottky contact),如圖 3-30。而兩種材料費米能階要一樣,會使得階面(interface)形成 蕭特基位障(Schottky barrier)。另外,被儲存的電子要自行離開浮動閘極,可能有很多的機制,不過跟所經過的厚度有關。因此金奈米粒子混合硒化鎘(Au and CdSe),對於被捕抓的電子來說,多了一個位能障和硒化鎘所產生的厚度,將會增加電子離開浮動閘極層的難度,進而增加記憶時間(Retnetion time)。

圖 3-28、硒化鎘量子點能帶圖。

圖 3-29、金加上硒化鎘混合奈米粒子能帶圖。

圖 3-30、局部放大金和硒化鎘的接面,將會形成蕭特基位障。

# 第四章

# 結論與建議

# (Summary and suggestion)

#### 4-1 結論

我們可以利用半導體製程技術和自我組裝(SAM)奈米粒子的方法,成功的做出奈米粒子當作浮動閘極的記憶體。當浮動閘極的材料是金和硒化鎘混合(Au+CdSe),相較於單獨只有金(Au)或是硒化鎘(CdSe)的記憶體,可以提升臨界電壓的變化(ΔVth)和增加記憶時間(Retention time)。比較本實驗的元件特性,和文獻參考的三篇論文[5][6][7],在各個方面,雖然不是最好,但是也都有不錯的表現,如表 3-9。

# ES

金屬奈米粒子和半導體量子點之間會形成蕭特基位障,而可以增加記憶時間 (Retention time),因此我們可以利用這個特性,查表 3-8[1]找出最好的金屬和半導體之間的搭配,其蕭特基位障是比較高,而有更好的記憶時間(Retention time)的表現。

Type (eV) 5.47 0.66 0.54 0.50 0.78 0.54 0.48 0.48 6.00 0.67 0.80 0.82 0.80 0.84 1.07 2.24 1.20 1.12 0.16 0.33 1.29 0.17' 0.47' 0.52 0.18 0.56 Ohmic 0.43 0.81 0.76 0.50 0.84 0.62 0.76 0.68 0.80 0.30 1.50 0.91 0.75 1.84 1.40 1.65 1.21 0.95 2.00

表 3-8、各種金屬半導體的蕭特基位障。[1]

表 3-9、本實驗元件和其他三篇論文之比較。

|                 | 1 Sam Ass (DTA) | Francisco (CAM)     | Orace Ass (DTA) | 15nm Au +5nm     |

|-----------------|-----------------|---------------------|-----------------|------------------|

| Floating gate   | 1-5nm Au (RTA)  | ənin Au (SAIVI)     | 9nm Au (RTA)    | CdSe             |

| Density         | 1.5x1012        | 5x1012              | none            | 2x1011           |

| Tunneling layer | SiO1.3N 5 nm    | SiO2 5 nm           | 8 nm            | 4 nm             |

| control layer:  | SiO1.3N 45 nm   | Cd-AA LB film       | 30 nm           | 25nm x 2         |

| Channel length  | 2-20 μm         | 1.5 μm              | 6 μm            | 5 μm             |

| Channel width   | none            | 10 μm               | 9 μm            | 100 nm           |

| Write:          | Vg= 10V ,100us  | Vg=6V ,1sec         | Vg=20V          | Vg=20V ;Vd=-5v   |

| Erase:          | Vg=-10V ,1s     | Vg=-6V ,1sec        | Vg=-20V         | Vg=-30V ;Vd=5v   |

| ΔVth            | 1.8V            | 6V                  | 0.7V            | 2 ~ 4.5V         |

| A V (II         | (Vth=-2.0V)     | ESTA                | 0.7 <b>v</b>    | 2 ~ 4.3 <b>v</b> |

| Retention Decay | 0.33V/dec       | 0.11V/dec           | 0.083V/dec      | 0.10 V/ dec      |

|                 | 2007 APL        | 2003 JAP            | IEEE 2002       |                  |

|                 | •               | THE PERSON NAMED IN |                 |                  |

# 4-2 建議

本次實驗的實驗的步驟很多,加上 NDL PECVD TEOS 所形成的控制氧化層(control oxide)成的品質不太理想,未來實驗室若是要繼續製作記憶體元件的話,建議能改用 NDL 的 LPCVD TEOS,這樣的優點是,人為的因素對於製成的的變異會減少很多,線寬也可以減少很多(奈米中心線寬極限為 1  $\mu$ m,對準誤差在 10  $\mu$ m),而且會有更好品質的 TEOS,相信會有更好的電性結果出現。

# 参考文獻 References

- [1] S. M. Sze, Physics of Semiconductor Device, 2<sup>nd</sup>, 1985.

- [2] Neamen, Semiconductor physics and devices basic principles, third edition, 1992.

- [3] Dieter K. Schroder, Semiconductor material and device characterization, 3<sup>rd</sup>, 1998.

- [4]William D. Brown, Joe E. Brewer, <u>Nonvolatile Semiconductor Memory Technology</u>, 1<sup>st</sup>, 1997.

- [5] P. PAVAN, R. BEZ, P. OLIVO, E. ZANONI, "Flash Memory Cells—An Overview", PROCEEDINGS OF THE IEEE, VOL. 85, NO. 8, AUGUST 1997

- [6] Z. Liu, C. hungho Lee, V. Narayanan, G. Pei, and E. C. Kan, "Metal Nanocrystal Memories—Part II: Electrical Characteristics", *IEEE TRANSACTIONS ON ELECTRON DEVICES*, VOL. 49, NO. 9, SEPTEMBER 2002

- [7] S. Kolliopoulou, P. Dimitrakis, P. Normand, Hao-Li Zhang, Nicola Cant, Stephen D. Evans, S. Paul, C. Pearson, A. Molloy, M. C. Petty, D. Tsoukalasa," Hybrid silicon–organic nanoparticle memory device", *JOURNAL OF APPLIED PHYSICS*, VOLUME 94, NUMBER 8 15 OCTOBER 2003

- [8] D. U. Lee, M. S. Lee, J. H. Kim, E. K. Kima, H. M. Koo, W. J. Cho, W. M. Kim, "Floating gated silicon-on-insulator nonvolatile memory devices with Au nanoparticles embedded in SiO1.3N insulators by digital sputtering method", APPLIED PHYSICS LETTERS, 90, 0935141-3 2007

- [9] Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan," Metal Nanocrystal Memories—Part

I: Device Design and Fabrication", *IEEE TRANSACTIONS ON ELECTRON DEVICES*,

VOL. 49, NO. 9, SEPTEMBER 2002

- [10] Chang-Ching Tu, Yaw-Kuen Li, Teng-Ming Chen, and Chung-Yu Wu, "Design and Fabrication of a Photosensing Nanodevice Structure With CdSe and Au Nanoparticles on a Silicon Chip", IEEE TRANSACTIONS ON NANOTECHNOLOGY, VOL. 5, NO. 3, MAY 2006

- [11] Chia-Chou Tsai, "Study on Nano-Scaled Poly-Si Thin-Film Transistor with Stacked Gate Dielectric", National Chiao Tung University, the Degree of Master, 2006

- [12] H. H. Liu,"Nanopatterning with Dip-Pen Nanolithography", National Chiao Tung University, the Degree of Master, 2006

# 附錄一

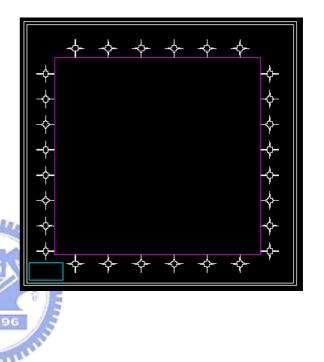

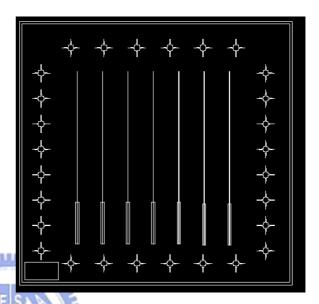

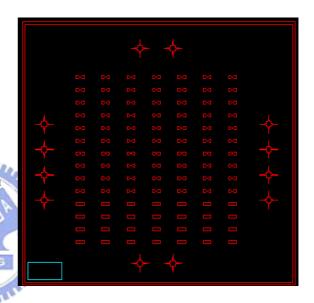

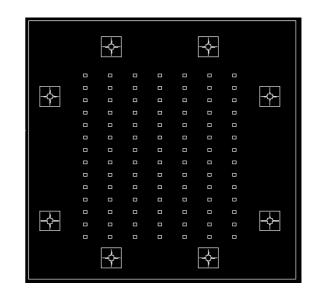

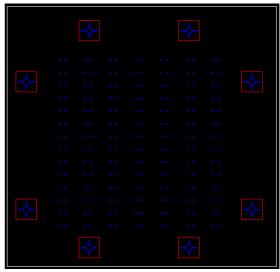

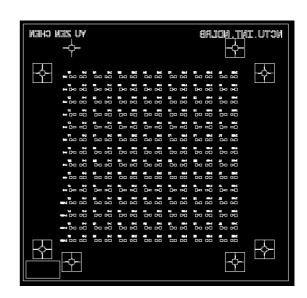

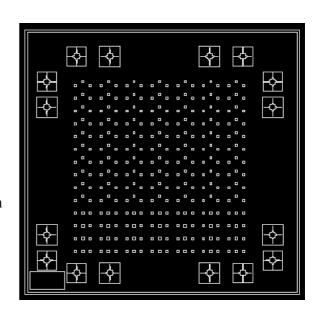

整個微米線製程詳細的流程,右邊的圖示包含光罩的圖形。

# AuNPs / CdSeNPs Micro-wire Flash Memory Process

# [RCA Clean]

DI water rinse 5 min

SPM 10 min

DI water rinse 5 min

DHF 10~15 s

SC1 10 min

DI water rinse 5min

SC2 10 min

DI water rinse 5 min

DHF several s

DI water rinse 5 min

# [Dry oxidation ]

950°C 10min O2/N2=2.51/51

N<sub>2</sub> annealing 950°C 30 min

# [n&k analysis]

Check the thickness of film

# [Implant]

Boron

5E13cm<sup>-2</sup>

20keV

# [Photolithography: Alignment key mask]

SPM 10 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

1st step 1500rpm 10s / 2nd step

4500rpm 40 s

Soft bake 90°C

Exposure 330 J/cm<sup>2</sup> (filter)

After exposure bake 120°C 1min

Development 45~60 s

DI water rinse 20 s

Hot bake 10~20 min

# [Implant]

Boron

5E13 cm<sup>-2</sup>

20 keV

#### [RIE etching] samco RIE-10NR

O2/CF4/Ar = 5/40/10 sscm; 50 w; 26.6 pa 15min

ACE 5 min

DI water rinse 5 min

### [Photolithography: Implant mask]

SPM 10 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

1st step 1500rpm 10s / 2nd step

4500 rpm 40s

Soft bake 90°C

Exposure 330 J/cm<sup>2</sup> (filter)

After exposure bake 120°C 1min

Development 45~60 s

DI water rinse 20 s

Hot bake 10~20 min

# [Implant]

P31<sup>+</sup>

5E15 cm<sup>-2</sup>

15 keV

# [Remove PR]

Ozone treatment 250°C 10min

SPM 10 min

DI water rinse 5 min

#### [Photolithography: Active Area mask]

SPM 10 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

1<sup>st</sup> step 1500rpm 10s / 2<sup>nd</sup> step 4500 rpm

40 s

Soft bake 90°C

Exposure 330 J/cm<sup>2</sup> (filter)

After exposure bake 120°C 1 min

Development 45~60 s

DI water rinse 20 s

Hot bake 10~20 min

BOE etching SiO2 30 s

DI water rinse 5 min

#### [RIE etching] samco RIE-10NR

$O2/CF4/Ar = 5/40/10 \text{ sscm}; 50\text{w}; 26.6\text{pa } 1\sim 2 \text{ min}$

ACE 5 min

DI water rinse 5 min

## [AFM check the etching rate]

# [Gate oxide growth]

#### [RCA Clean]

DI water rinse 5 min

SPM 10 min

DI water rinse 5 min

DHF 10~15 s

SC1 10 min

DI water rinse 5 min

SC2 10 min

DI water rinse 5 min

DHF several s

DI water rinse 5 min

#### [Dry oxidation & Annealing after implant]

950°C 10min O<sub>2</sub>/N<sub>2</sub>=2.5 L/5 L

N<sub>2</sub> annealing 950°C 10 min

# -n&k analysis -

Check the thickness of film

#### [Photolithography: AuNPs Localization mask]

ACE 5 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

$1^{st}$  step 1500 rpm 10s /  $2^{nd}$  step 4500 rpm 40s

Soft bake 90°C

Exposure 270 J/cm<sup>2</sup> (no filter)

Development 35~45 s

DI water rinse 20 s

#### [SAM AuNPs]

SAM AEAPTMS (AEAPTMS 20ul + DI water 40 ml)

DI water rinse 1 min

Hot bake 120°C 30 min

SAM AuNPs 12 min

DI water rinse 5 min

Hot bake 120°C 30 min

Ozone treatment to remove organic material at 220°C , 10 min

#### -SEM-

SEM to check the AuNPS

#### [SAM CdSe NPs]

SAM CdSe (negative charge) 2 h

DI water rinse 5 min

# [PECVD TEOS]

Recipe: SiO2 1K 35 s~ 500 Å

Or SiO2 3K 20 s~250 Å

-n&k analysis

Check the thickness of film

#### [Thermal coat the metal]

Al (2000 Å)

# [Photolithography: Metal Gate mask]

ACE 5 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

$1^{\text{st}}$  step 1500 rpm 10s /  $2^{\text{nd}}$  step 4500 rpm 40

$\mathbf{S}$

Soft bake 90°C

Exposure 270 J/cm<sup>2</sup> (no filter)

Development 35~45 s

DI water rinse 20 s

# [Etching Al]

H<sub>3</sub>PO<sub>4</sub>:CH<sub>3</sub>C00H:HNO<sub>3</sub>:H<sub>2</sub>O=8:4:1:1 at 45°C

Etahing rate = 3 nm/s

# [Photolithography: Contact hole mask]

ACE 5 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

1<sup>st</sup> step 1500 rpm 10s / 2<sup>nd</sup> step 4500

rpm 40 s

Soft bake 90°C

Exposure 270 J/cm<sup>2</sup> (no filter)

Development 35~45 s

DI water rinse 20 s

BOE etching SiO<sub>2</sub> 1 min

DI water rinse 5 min

# [Remove PR]

SPM 10 min

DI water rinse 10 min

#### [Photolithography: S\D metal mask]

ACE 5 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

1<sup>st</sup> step 1500 rpm 10s / 2<sup>nd</sup> step 4500 rpm 40s

Soft bake 90°C

Exposure 270J/cm<sup>2</sup> (no filter)

Development 35~45 s

DI water rinse 20 s

BOE dip 5 s

DI water rinse several seconds

# [Metallization]

Ti/Al (10/100nm)

# [Lift off]

ACE 30 min

DI water rinse 5 min

# [Metal annealing]

400°C 30 min

#### [Isolation layer]

PECVD SiN<sub>x</sub> 300 nm

# [Photolithography: S\D Via]

ACE 5 min

DI water rinse 10 min

HMDS 2 min

Spin coating Photo Resister FH6400

$1^{st}$  step 1500 rpm 10s /  $2^{nd}$  step 4500 rpm

40 s

Soft bake 90℃

Exposure 270 J/cm<sup>2</sup> (no filter)

Development 35~45 s

DI water rinse 20 s

# [RIE etching SiNx] samco RIE-10NR

$O2/CF4/Ar = 5/40/10 \text{ sscm}; 50\text{w}; 26.6\text{pa } 1\sim 2 \text{ min}$

ACE 5 min

DI water rinse 5 min

# [Finish]

[Measurement]