# 國立交通大學

# 資訊學院 資訊學程

# 碩士論文

指令快取記憶體的電源管理 -(對程式流程有感知能力的昏睡指令記憶體)

Power Management for Instruction Cache

-(Program Flow Sensitive Drowsy I-Cache)

研 究 生:周國維

指導教授:鍾崇斌 教授

中華民國九十六年八月

i

# 指令快取記憶體的電源管理 Power Management for Instruction Cache

研究生:周國維 Student: Kuo-Wei Chou

指導教授:鍾崇斌 Advisor: Chung-Ping Chung

國立交通大學 資訊學院 資訊學程

碩士論文

A Thesis

Submitted to College of Computer Science

National Chiao Tung University in partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Computer Science

August 2007

Hsinchu, Taiwan, Republic of China

中華民國九十六年八月

## 指令快取記憶體的電源管理

學生:周國維 指導教授:鍾崇斌 博士

#### 國立交通大學 資訊學院 資訊學程

## 摘 要

指令快取記憶體的電源管理,其只要的概論是將處於工作模式的快取列的數量最小化。於是乎,在啟動的方案上,便是利用固定的目標位址使非循序的快取列預先活躍化。在關閉的方案上,在某一快取列最後一次使用並且將其內容物傳遞之後,此時便將此快取列關閉成昏睡模式。此概論的目的便是將漏電所產生的能耗減少到最少。在開啟的階段,由於快取記憶體的取代方案採用"關連性取代法",如此導致會有好幾個的快取列同時活躍化。在一段覺醒時間之後,除了會參考到的快取列,將其餘不會參考的快取列切換成昏睡模式。這些額外增加的輔助硬體不只能提供下一個"基礎區塊"的預測能力,並且當"錯誤的預測"發生後能導正程式的流程。在實驗的結果顯示本論文建議的設計能減少的漏電能耗。當"覺醒潛在因素"是由一個clock 的"覺醒時間"以及一個 clock1 本設計"電路延遲"。在一般的個例中,執行時間會增加10.898%至 14.581% 已及減少77.5% 知82.4% 的漏電能耗。

## 指令快取記憶體的電源管理

#### Power Management for Instruction Cache

student: Kuo-Wei Chou Advisors: Dr. Chung-Ping Chung

# Degree Program of Computer Science National Chiao Tung University

## **ABSTRACT**

Main concept of Power management of Instruction Cache - (Program Flow Sensitive Drowsy I-Cache (pfsDIC for brief)) is that minimize the numbers of active cache lines. So, on Turn-On scheme, utilize fixed Target address to preactivate the discontinuous Instruction Cache Line. On Turn-Off scheme, turn-off the cache lines after the last content of this cache line is transmitted. The purpose of such concept is to reduce maximum leakage energy. On Turn-On stage, there is several cache lines are activating due to low-way associated. After an amount of wakeup time, switch these awaken cache lines to "Drowsy mode" except to the referred cache line. The additional auxiliary hardware don't only offer the predictive ability of next Basic Block, but also maintain the correct program flow when wrong prediction happens. The experiment results show the leakage reduction of proposed designs. When the wakeup latency is the sum of 1 clock of wakeup time and an extra 1 clock of circuit delay that caused by proposed design. In the average case, the Runtime increment is 10.898%~14.581% and the leakage reduction is 77.5% ~ 82.4%

#### 誌謝

首先感謝指導教授 鍾崇斌老師在學生就學期間给於學生耐心地教導與彈性又充足的研討時間。再者感謝口試委員 單智君教授、王益文教授與陳德生教授願意擔任學生的口試委員,並且在口試時的提供學生在研究上可以再改善的寶貴意見,使論文得以修改得更完整以及完善。除此之外,感謝博士班的楊惠親學姊和喬偉豪學長在研究過程中所給與的協助及幫助。

就一個在職生來說,我必須感謝公司主管潘正峰經理就學生在學期間在工作上的安排,以及徐日明、閻學斌學長在學生修課時給予業界資料取得的協助,使得學生得以順利地完成學業。

再次感謝 王益文老師以及第一次修習學分班〈多媒體影像處理〉 傅心家老師以及主管 潘正峰經理,在兩年前要考專班時惠賜推薦書,並感謝交大的在職專班讓我有再一次回 到校園學習的機會。

過去因為考試、作業、研究時常到深夜以致影響到家人的睡眠品質,在這裏衷心感謝家人的體諒與支持。

周國維 2007.8.30

## **Table of Contents**

| Mas  | ter o  | f Scier | nce                                                          | ii   |

|------|--------|---------|--------------------------------------------------------------|------|

| 摘    |        | 要       |                                                              | iii  |

| ABS  | STR A  | ACT     |                                                              | iv   |

| 誌    |        | 謝       |                                                              | v    |

| Tabl | e of   | Conte   | nts                                                          | vi   |

| List | of Fi  | gures.  |                                                              | viii |

| List | of T   | ables   |                                                              | X    |

| Cha  | pter   | l Intro | duction                                                      | 1    |

|      | 1.1    | Back    | ground                                                       | 1    |

|      |        | 1.1.1   | DVS (Dynamic Voltage Scaling)                                | 1    |

|      |        | 1.1.2   | Characteristics of Program Execution                         | 2    |

|      |        | 1.1.3   | J I                                                          |      |

|      |        | 1.1.4   | Basic Block                                                  | 7    |

|      |        | 1.1.5   | Drowsy Caches: Simple Techniques for Reducing Leakage Power. | 8    |

|      |        | 1.1.6   | [-]                                                          |      |

|      | 1.2    | Resea   | arch Motivation                                              | 10   |

|      | 1.3    |         | arch Objective                                               |      |

|      | 1.4    | Organ   | nization of this Thesis                                      | 12   |

| Cha  | pter 2 | 2 Desig | gn of Proposed Architecture                                  | 13   |

|      | 2.1    | Chall   | lenges in Design                                             | 13   |

|      | 2.2    | Desig   | gn of BTB Side                                               | 13   |

|      |        | 2.2.1   | Extra component of BTB side                                  | 14   |

|      |        | 2.2.2   | Update & Use of "BBSize"                                     | 16   |

|      |        | 2.2.3   | Summary of BTB side                                          | 18   |

|      | 2.3    | Desig   | gn of Processor                                              | 21   |

|      |        | 2.3.1   | Extra component on processor                                 | 21   |

|      |        | 2.3.2   | Example for explain predictive instruction address           | 23   |

|      | 2.4    | Design  | n of Cache                                                   | 27   |

|      |        | 2.4.1   | Extra component (Preactivating Cache-Line FIFO)              | 28   |

|      |        | 2.4.2   | Extra component (Lines sensor)                               | 29   |

|      |        | 2.4.3   | Extra component (Lines sensor)                               | 29   |

|      |        | 2.4.4   | Extra component (Content Transmitter)                        | 30   |

|      |        | 2.4.5   | Extra component (Stage Master)                               | 31   |

| Cha  | pter 3 | 3 Eval  | uation and Discussion                                        | 33   |

| 3.1 Evaluation Methodology                                 | 33 |

|------------------------------------------------------------|----|

| 3.2 Evaluation Metrics                                     | 34 |

| 3.3 Experimental Environment                               | 35 |

| 3.4 Experimental Benchmark                                 | 36 |

| 3.5 Experimental Results                                   | 38 |

| 3.6 Discussion                                             | 46 |

| 3.6.1 Discussion with five evaluation metrics              | 46 |

| 3.6.2 Important Considerations and/or Further Improvements | 47 |

| Chapter 4 Conclusion and Future work                       | 51 |

| 4.1 Conclusion                                             | 51 |

| 4.2 Future work                                            | 51 |

| References                                                 | 53 |

| Vita                                                       | 54 |

## **List of Figures**

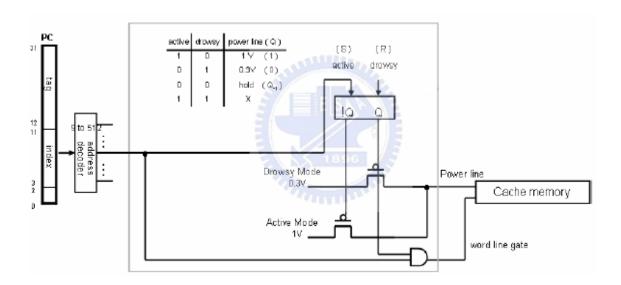

| FIGURE 1.1 LOGIC DIAGRAM OF DROWSY CACHE-LINE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

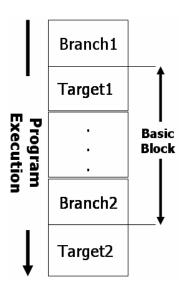

| FIGURE 1.2 DIAGRAM OF BASIC BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

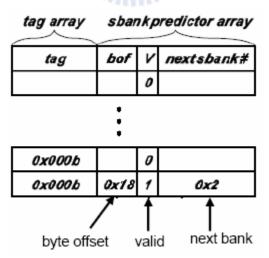

| FIGURE 1.3 DIAGRAM OF SUB-BANK PREDICTION BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

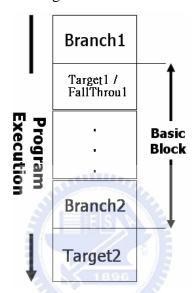

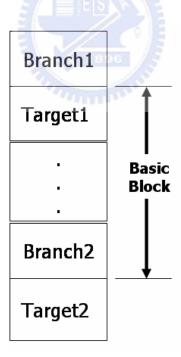

| FIGURE 1.4 DIAGRAM OF BASIC BLOCK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

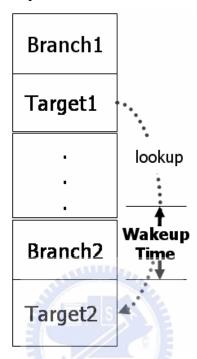

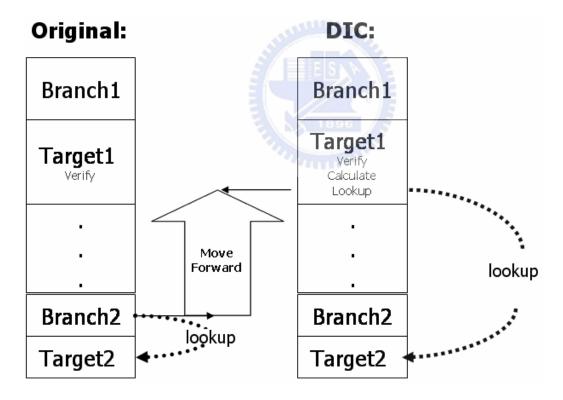

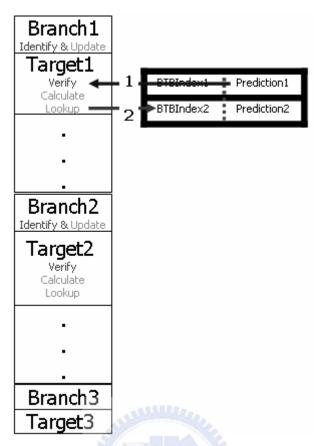

| FIGURE 1.5 DIAGRAM FOR DESCRIBING LOOKUP TIMING OF THIS THESIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

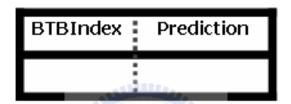

| FIGURE 2.1 DIAGRAM FOR DESCRIPTION OF "BBSIZE" FIELD EACH BTB ENTRY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| FIGURE 2.2 DIAGRAM FOR DESCRIPTION OF 2-DEPTH FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

| FIGURE 2.3 TRUTH TABLE OF "PREDICTION" FIELD AFTER VERIFY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

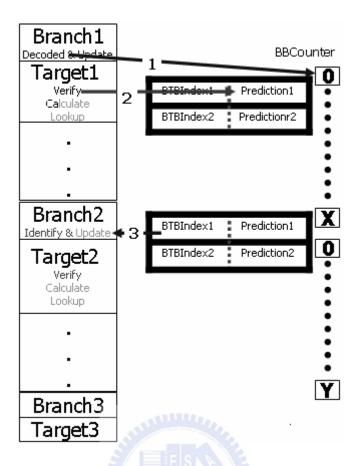

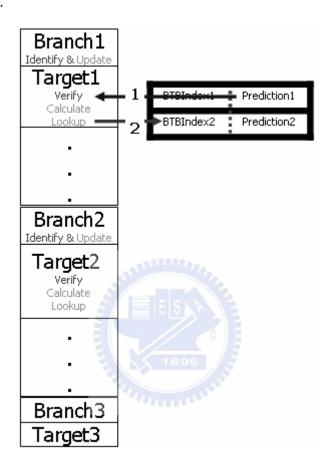

| Figure 2.4 Diagram for gathering "BBsize"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

| FIGURE 2.5 DIAGRAM FOR USING "BBSIZE"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

| FIGURE 2.6 A PIECE OF PROGRAM EXECUTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| FIGURE 2.7 BLOCK DIAGRAM OF ORIGINAL ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

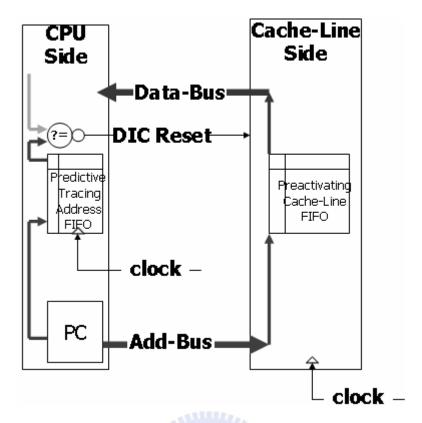

| FIGURE 2.8 BLOCK DIAGRAM OF CPU CORE SIDE AND I-CACHE SIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

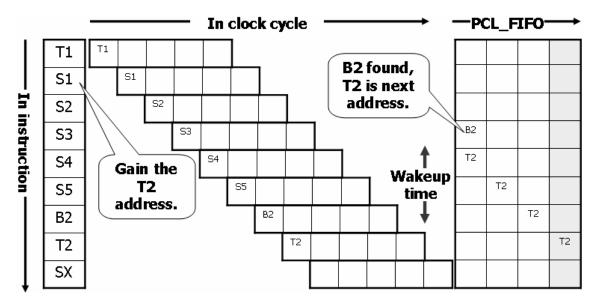

| FIGURE 2.9 THE DIAGRAM OF PIPELINE: THERE HAS 1 CIRCUIT DELAY, 2 WAKEUP TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

| FIGURE 2.10 TIMING DIAGRAM OF PREDICTIVE TARGET:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

| THERE HAS 1 CIRCUIT DELAY, 2 WAKEUP TIME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

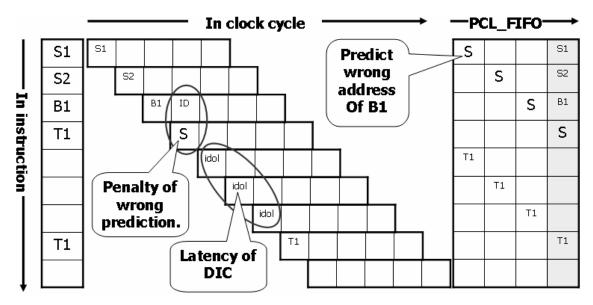

| FIGURE 2.11 TIMING DIAGRAM OF WRONG PREDICTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

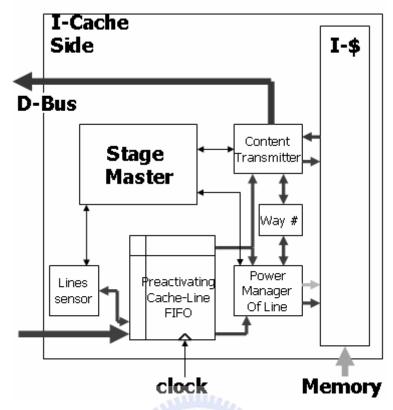

| FIGURE 2.12 GLOBAL VIEW OF CACHE SIDE28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

| FIGURE 2.12 BLOCK DIAGRAM OF "PREACTIVATING CACHE-LINE FIFO"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

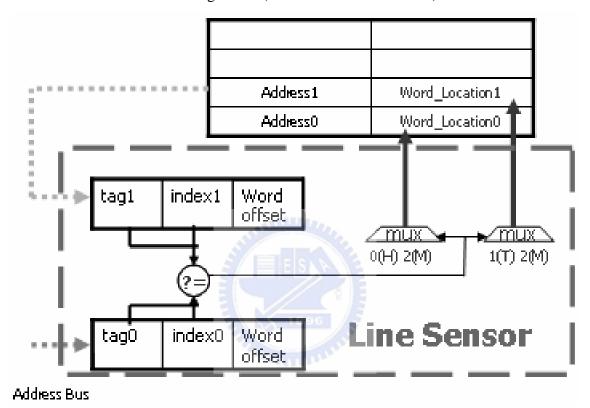

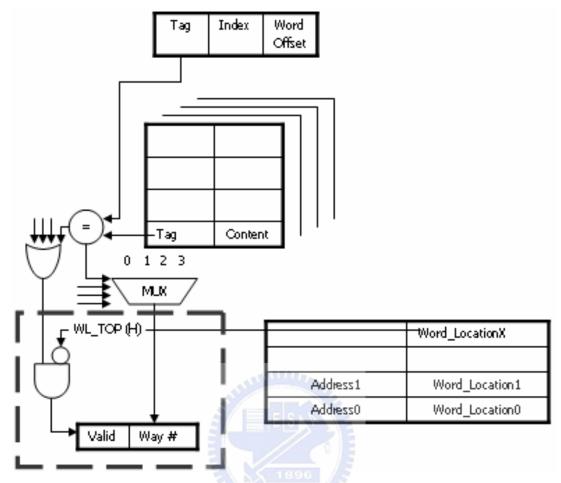

| FIGURE 2.13 BLOCK DIAGRAM OF "LINE SENSOR" AND "PREACTIVATING CACHE-LINE FIFO"29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

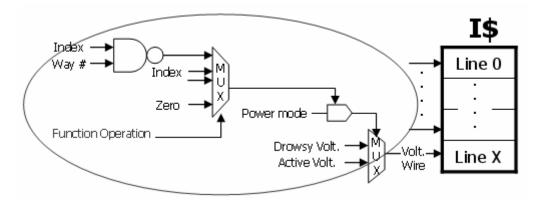

| FIGURE 2.14 LOGIC CIRCUIT DIAGRAM OF "CACHE-LINE"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| FIGURE 2.15 TRUTH TABLE OF "FUNCTION OPERATION"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

| FIGURE 2.16 LOGIC CIRCUIT OF "CONTENT TRANSMITTER", WHEN TRANSMITTED FIRST CONTENT OF LINE.31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

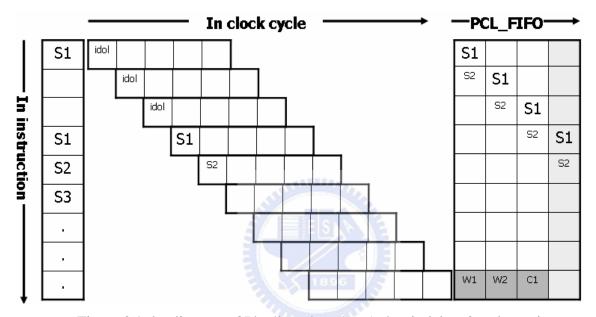

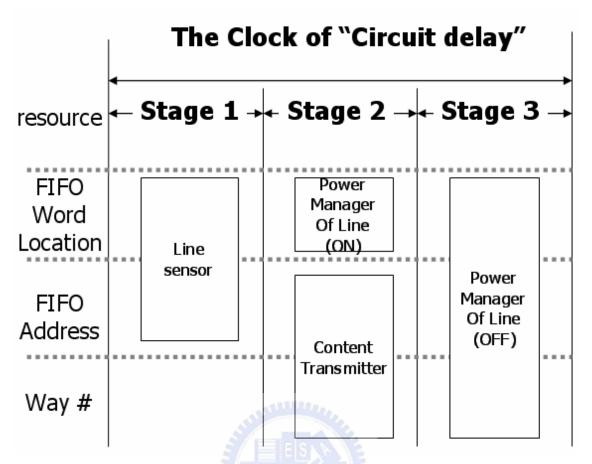

| FIGURE 2.17 DIAGRAMS OF TIMING AND RESOURCE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

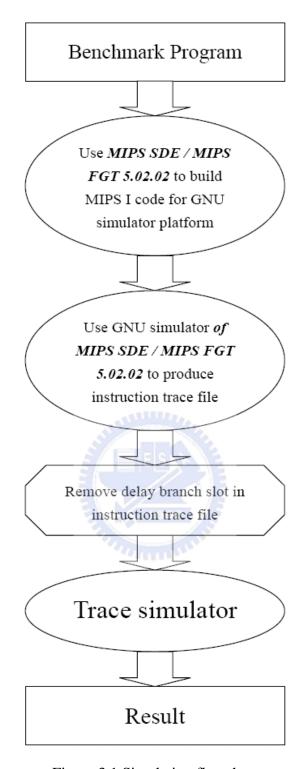

| FIGURE 3.1 SIMULATION FLOWCHART                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     |

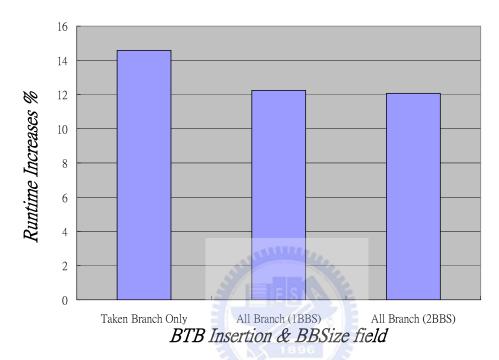

| ${\it Fig~3.2~Block~Diagram~of~"Runtime~increment"}~{\it that~affected~by~"BTB~Insertion"}~{\it and~"BBSize~Field~by~"BTB~Insertion"}~{\it and~"BBSize~Field~by~"BTB~In$ | )". |

| 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |

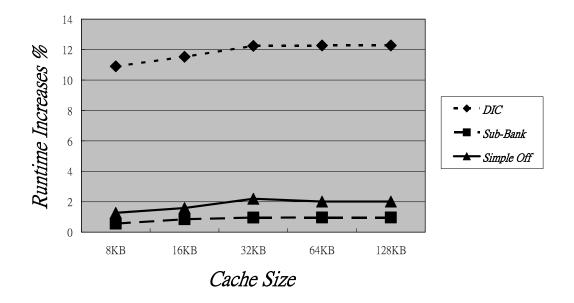

| FIG 3.3 BLOCK DIAGRAM OF "RUNTIME INCREMENT" THAT AFFECTED BY "CACHE SIZE"41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

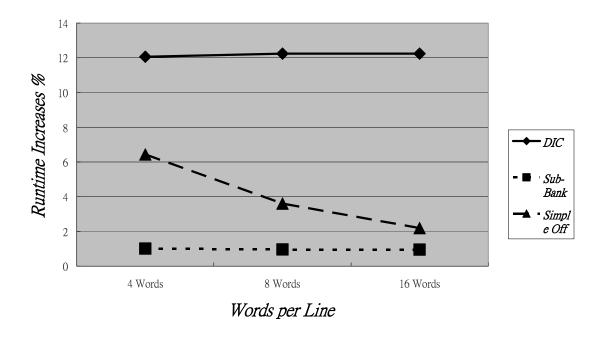

| FIG 3.4 BLOCK DIAGRAM OF "RUNTIME INCREMENT" THAT AFFECTED BY "WORDS PER LINE"42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     |

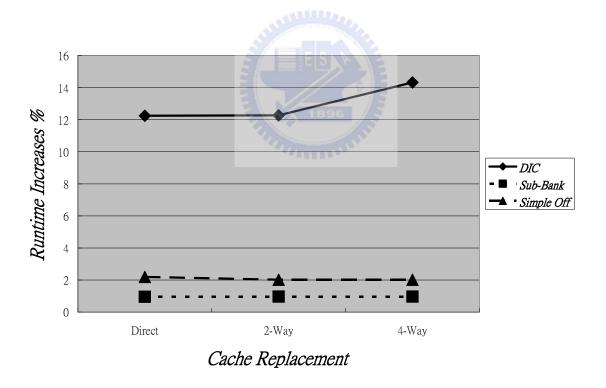

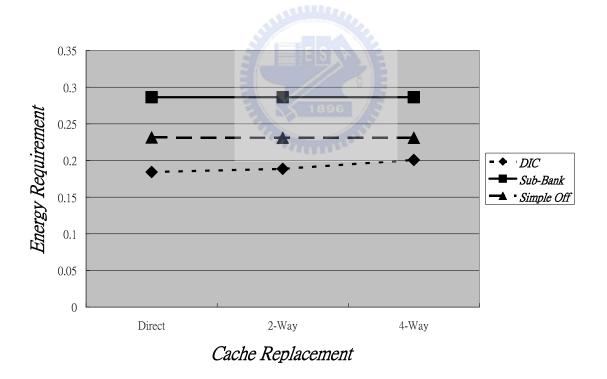

| FIG 3.5 BLOCK DIAGRAM OF "RUNTIME INCREMENT" THAT AFFECTED BY "CACHE REPLACEMENT"42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

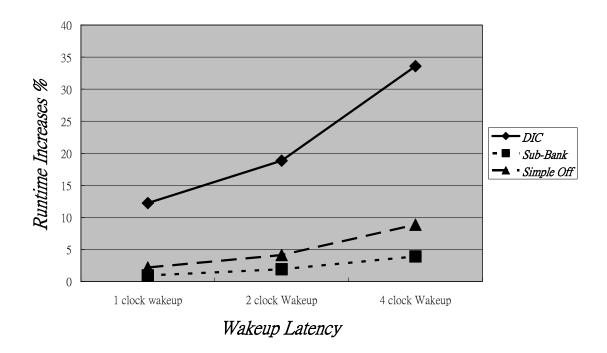

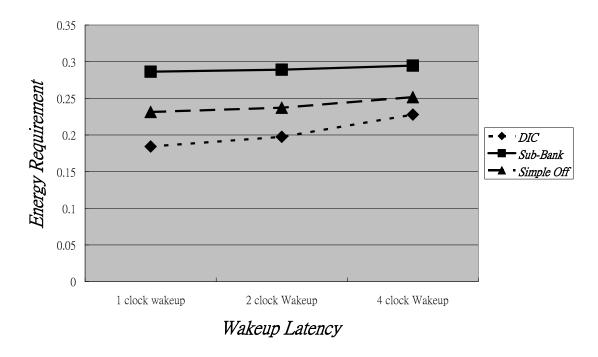

| FIG 3.6 BLOCK DIAGRAM OF "RUNTIME INCREMENT" THAT AFFECTED BY "WAKEUP LATENCY"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

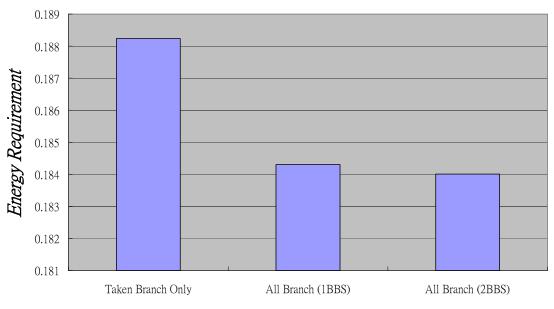

| Fig 3.7 Block Diagram of "Leakage energy reduction" that affected by "BTB insertion" and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

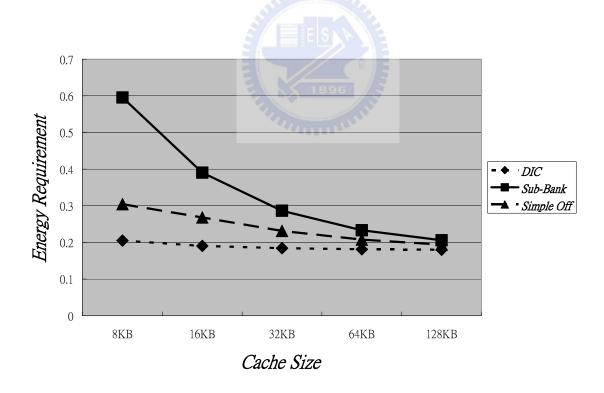

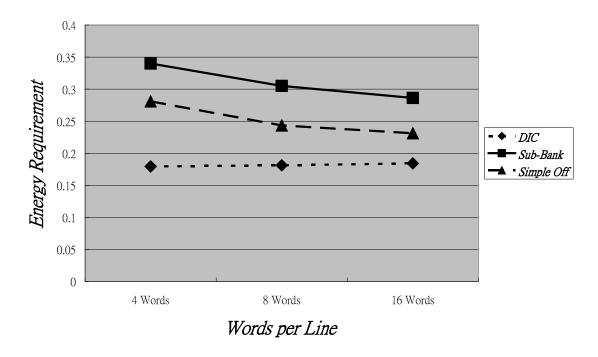

| "BBSize field"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |