# 國立交通大學

工學院專班半導體材料與製程設備學程

碩 士 論 文

淺溝槽隔離製程的缺陷研究

A Study on Defect of Sallow Trench Isolation Process

研究生: 林美慧

指導教授: 陳家富教授

中華民國九十六年七月

# A Study on Defect of Sallow Trench Isolation Process

研 究 生: 林美慧 Student: Mei-Hui Lin

指 導 教 授:陳家富 博士 Advisor: Dr. Chia-Fu Chen

## 國立交通大學

工學院專班半導體材料與製程設備組

碩士論文

#### A Thesis

Master Degree Program of Semiconductor Material and Process Equipment

College of Engineering

National Chiao Tung University

in Partial Fulfillment of the Requirements

for the Degree of

Master of Science

in

Program of Semiconductor Material and Process Equipment

July 2007

Hsinchu, Taiwan, Republic of China

中華民國 九十六 年 七 月

#### 淺溝槽隔離製程的缺陷研究

學生:林美慧 指導教授:陳家富 博士

國立交通大學工學院專班半導體材料與製程設備組碩士班

#### 摘 要

積體電路技術的縮小化,是為了加強電路之元件積成密度與功能性, 改善速度切換與元件消耗功率,其中以其通道長度與閘極氧化層的縮小 化最為顯著。而通道的隔離技術以淺溝槽隔離製程取代傳統 LOCOS (local oxidation of silicon)方式,以滿足高積成密度的要求。本論文主 要是研究因淺溝槽隔離製程所衍生出來的氣泡(bubble)缺陷,及運用兩 種方法改善此氣泡缺陷,進而改善晶圓廠內電性品質及良率。

第一種方法是改良淺溝槽隔離高密度電漿氧化層沉積程式,減緩預熱時間與主沉積時間的溫度差,降低其預熱到主沉積前之間的熱膨脹係數的差異,第二種方法是在淺溝槽隔離內墊熱氧化層步驟多加一 $N_2$ 現場退火的步驟,利用高溫先將內壁熱氧化矽層表層壓應力的殘留氣體或水氣先釋放出來,再用 $N_2$ 讓表面氮化,增加與後層淺溝槽隔離高密度電漿氧化層的附著力,但對需用到磊晶製程晶片的產品,若用第二種方法則需考量熱預算對電性的影響程度有多大,避免自動掺入的問題產生。

The Defect Study for Shallow Trench Isolation Process

Student: Mei-Hui Lin Advisor: Dr. Chia-Fu Chen

Program of Semiconductor Material and Process Equipment

National Chiao Tung University

**Abstract**

The shrinkage of IC (integrated circuit) enhance the circuit density,

device function, switch speed and power consumption. The channel length and

gate oxide thickness are the most critical parameters. To achieve the

high-density purpose, STI (shallow trench isolation) was designed to replace

LOCOS (local oxidation of silicon) for channel isolation. The subject of this

thesis studied the bubble defect induced in STI process. We make use of two

methods to solve the bubble defect and then improve such kind of electrical

quality and circuit probe yield.

The first one is improve the deposition recipe of shallow trench isolation

high density plasma oxide layer, to ease the temperature variation between

pre-heat time and main deposition time that can reduce the coefficient of thermal

expansion difference between pre-heat time and main deposition time.

The second one is extra N<sub>2</sub> in-situ annealing step in shallow trench

isolation liner thermal oxide layer, the high temperature can release the surface

compressive stress of liner oxide layer which surface nitrogen treatment can

enhance the adhesion between high density plasma oxide and liner oxide. But

for those products used Epi wafer, we should study the electrical shift level due

to thermal budget to avoid auto-doping problem.

ii

回顧這兩年豐富的碩士班生涯中,最感謝的莫過於我尊敬的指導教授 陳家富博士,他秉持著孜孜不倦的教導方式,不斷給予我們指導及鼓勵,百忙之中還不辭辛苦的抽空指導我們,著實令我十分敬佩那種堅持的精神與毅力。還要謝謝我們美麗高雅的師母,在這段時間對學生們的照料。同時也要感謝 郭正次博士、潘扶民博士及 陳密博士的審閱,並給予許多寶貴的意見與指正,使得本論文能更加完善。

另外要謝謝諸多學長們(吳明昆、邱晴暉、廖柏東、曾建儒、彭徵富、蔡毓通、高耀寰、林孟君、張允武、蔡明光、黄仲堯及余文光)的照顧及同學們(林俊杰、楊學修、張顗民、黃閔顯、鍾隆泓)的相互激勵與成長,因為有你們的存在,讓我在交大這段期間增添許多難忘的回憶。

最後我要謝謝我的家人,在這段期間對我的包容與支持,給予我 最大的原動力,讓我能順利完成我的學業與論文。在此祝福我的家人 及所有關心我的親友們都能健健康康、快快樂樂。

# 目錄

| 中文摘要  |                         | i   |

|-------|-------------------------|-----|

| 英文摘要  |                         | ii  |

| 誌謝    |                         | iii |

| 目錄    |                         | iv  |

| 表目錄   |                         | vi  |

| 圖目錄   |                         | vii |

| 第一章、  | 緒論                      | 1   |

| 1.1   | 研究背景                    | 1   |

| 1.2   | 研究動機與目的                 | 1   |

| 1.3   | 論文架構                    | 2   |

| 1.4   | 問題概述                    | 3   |

| 1.5   | 影響程度                    | 5   |

| 第二章、  | 文獻回顧                    | 6   |

| 2.1   | 淺溝槽隔離製程流程介紹             | 6   |

| 2.1.1 | 常見的淺溝槽隔離流程              | 6   |

| 2.2   | 掀起缺陷形成機制                | 9   |

| 2.2.1 | bubble 缺陷來源分析           | 9   |

| 2.2.2 | 不同淺溝槽隔離薄膜之應力與接觸角度分析     | 12  |

| 2.2.3 | bubble 缺陷 EDX 分析        | 14  |

| 2.2.4 | 消除 bubble 缺陷方法          | 16  |

| 第三章、  | 實驗方法                    | 18  |

| 3.1   | 缺陷檢驗步驟規劃                | 18  |

| 3.2   | 缺陷檢驗機台原理與簡介             | 19  |

| 3.3   | 檢閱缺陷機台簡介                | 22  |

| 3.4   | 形成原因分析→缺陷來源分析           | 23  |

| 3.4.1 | Fab-A & Fab-B bubble 缺陷 | 23  |

| 3.4.2 | Fab-A 形成原因分析→缺陷來源       | 26  |

| 3.4.3 | Fab-A 缺陷來源實驗一結果         | 26  |

| 3.5   | Fab-A 形成原因分析→缺陷發生點      | 27  |

| 3.5.1 | 缺陷發生點實驗條件二              | 27  |

| 3.5.2 | Fab-A 缺陷發生點實驗二結果        | 29  |

| 3.6   | 薄膜應力                    | 31  |

| 第四章、  | 實驗結果與討論                 | 34  |

| 4.1   | Fab-A 改善掀起缺陷→實驗三條件      | 34  |

| 4.2   | Fab-A 改善掀起缺陷→缺陷檢驗實驗三結果  | 35  |

| 4.3   | Fab-A 改善掀起缺陷→良率結果       | 36  |

| 4.4    | Fab-B 改善掀起缺陷→實驗四條件          | 37 |

|--------|-----------------------------|----|

| 4.5    | Fab-B 改善掀起缺陷實驗四結果→缺陷檢驗      | 38 |

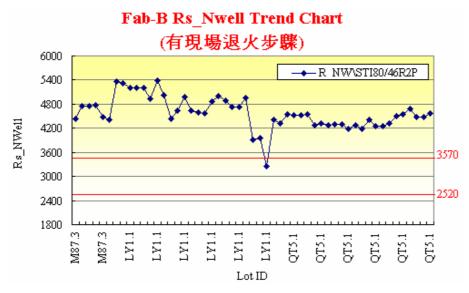

| 4.6    | Fab-B 改善掀起缺陷實驗四結果→電性結果      | 41 |

| 4.7    | Fab-B 電性異常分析→機台釐清           | 43 |

| 4.8    | 文獻回顧→磊晶矽膜製程簡介               | 44 |

| 4.8.1  | 矽磊晶製程                       | 44 |

| 4.8.2  | 矽磊晶成長                       | 45 |

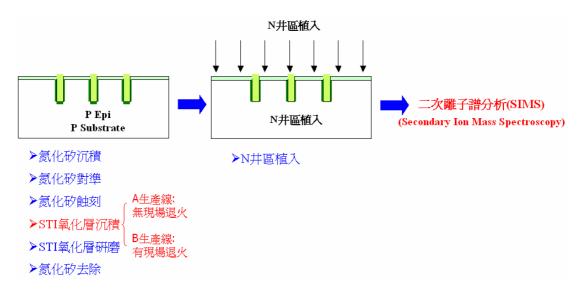

| 4.9    | Fab-B的N井區阻值異常分析~SIMS分析實驗設計  | 46 |

| 4.10   | Fab-B的N井區阻值異常分析~阻值飄高形成原因    | 47 |

| 4.11   | Fab-B 的 N 井區阻值異常分析~阻值飄高形成原因 | 49 |

| 4.11.1 | 實驗五步驟說明                     | 49 |

| 4.11.2 | 實驗五結果說明                     | 49 |

| 4.12   | Fab-B 的 N 井區阻值異常分析~阻值飄高解決方法 | 51 |

| 4.12.1 | 實驗六步驟說明                     | 51 |

| 4.12.2 | 實驗六結果說明                     | 52 |

| 第五章、   | 結論                          | 54 |

| 參考文獻   | CALLED CO.                  | 56 |

# 表目錄

| 表 2-1 不同薄膜之應力與接觸角度               | 13  |

|----------------------------------|-----|

| 表 2-2 不同淺溝槽隔離氧化層的崩潰電壓強度          | 17  |

| 表 2-3 氧化內墊層及氧氮化物薄膜之應力與接觸角度       | 麦17 |

| 表 3-1 缺陷來源實驗結果                   | 27  |

| 表 3-2 Fab-A 缺陷發生點實驗二             | 29  |

| 表 3-3 預熱時間比較表                    | 31  |

| 表 4-1 O2預熱步驟新舊程式差異               | 34  |

| 表 4-2 實驗四條件                      | 38  |

| 表 4-3 實驗四 STIDEP 缺陷檢驗結果          | 39  |

| 表 4-4 Fab-A 與 Fab-B 之 N 井區 阻 值 表 | 42  |

| 表 4-5 N 井區植入劑量條件與阻值              | 43  |

| 表 4-6 實驗五條件                      | 49  |

| 表 4-7 實驗五 N 井區阻值及缺陷檢驗結果          | 50  |

| <b>麦 4-8 實驗 六 條 件</b>            | 52  |

# 圖目錄

| 圖 | 1-1 | CMOS 製程結構                 | 2  |

|---|-----|---------------------------|----|

| 圖 | 1-2 | STIDEP 檢驗站點缺陷圖            | 4  |

| 圖 | 1-3 | 淺溝槽隔離掀起缺陷之 SEM 圖示         | 4  |

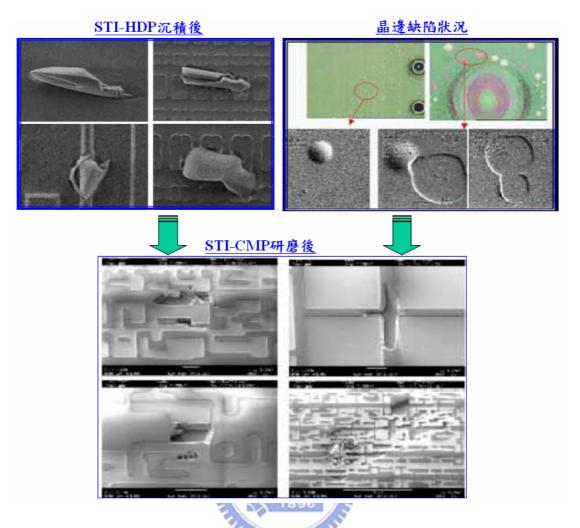

| 圖 | 1-4 | STI-HDP 沉積後到 CMP 研磨後的缺陷圖示 | 5  |

| 圖 | 2-1 | 淺溝槽隔離製程流程簡介               | 8  |

| 圖 | 2-2 | 生產晶片 bubble 缺陷 TEM 圖示1    | 0  |

| 圖 | 2-3 | 異常控片 bubble 缺陷 SEM 圖示1    | 0  |

|   |     | 生產晶片凹洞缺陷 SEM 圖示1          |    |

| 圖 | 2-5 | 異常控片凹洞缺陷圖示1               | 1  |

| 圖 | 2-6 | bubble 缺陷形成機制1896         | 4  |

| 圖 | 2-7 | bubble 缺陷的 EDX 分析1        | 5  |

| 圖 | 2-8 | 不同內墊層之晶邊狀態圖示1             | 7  |

| 圖 | 3-1 | 缺陷檢驗步驟圖示1                 | 8  |

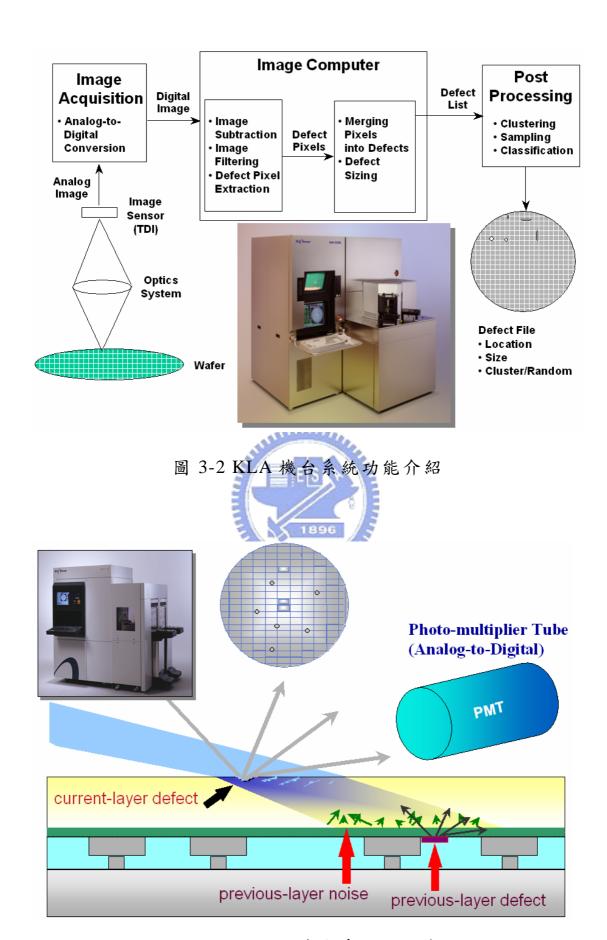

| 圖 | 3-2 | KLA 機台系統功能介紹2             | :0 |

| 圖 | 3-3 | TENCOR 機台系統功能介紹2          | :0 |

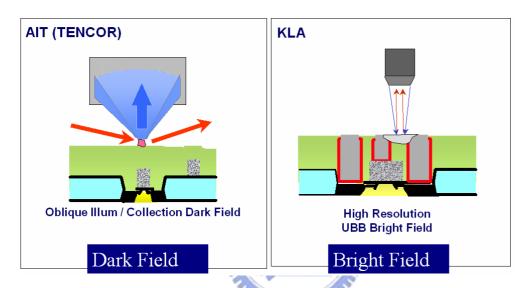

| 圖 | 3-4 | 暗區(TENCOR)與亮區(KLA)技術2     | :1 |

| 圖 | 3-5 | 缺陷機台 KLA & TENCOR 比對2     | :1 |

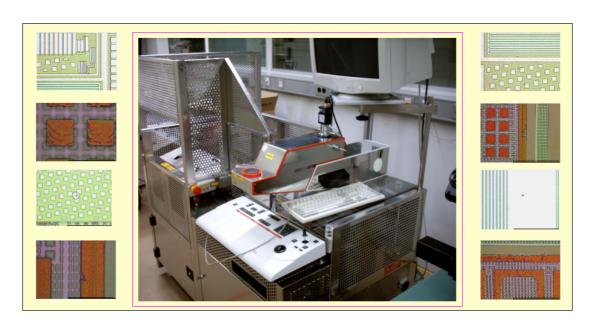

| 圖 | 3-6 | 光學顯微鏡機台(LEICA INS3000)2   | 22 |

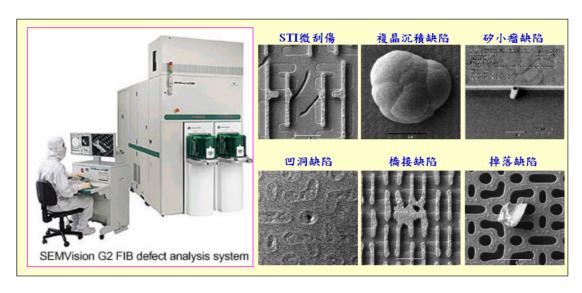

| 圖 3-7 掃描式電子顯微鏡機台(Applied SEMVision) | 23 |

|-------------------------------------|----|

| 圖 3-8 Fab-A bubble 缺陷               | 24 |

| 圖 3-9 Fab-B bubble 缺陷               | 25 |

| 圖 3-10 Fab-A & Fab-B STI 機台比較       | 25 |

| 圖 3-11 缺陷來源分析實驗流程                   | 26 |

| 圖 3-12 生產 晶片 vs 控片的 bubble 缺陷圖      | 27 |

| 圖 3-13 應材機台晶片溫度監控(WTM)圖             | 28 |

| 圖 3-14 沉積時間對應掀起缺陷圖                  | 30 |

| 圖 3-15 預熱時間對應掀起缺陷圖                  |    |

| 圖 3-16 薄膜應變狀況                       |    |

| 圖 4-1 不同預熱程式 WTM Profile 圖          | 35 |

| 圖 4-2 新舊 STI-HDP 程式的掀起缺陷圖           | 36 |

| 圖 4-3 新舊 STI-HDP 程式的良率差異            | 37 |

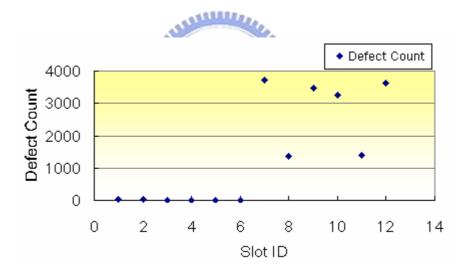

| 圖 4-4 實驗四STIDEP檢驗之缺陷趨勢線             | 39 |

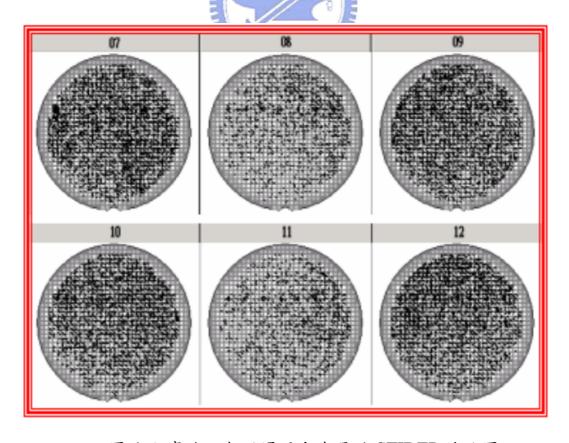

| 圖 4-5 實驗四有加現場退火步驟的STIDEP缺陷圖         | 40 |

| 圖 4-6 實驗四無現場退火步驟的STIDEP缺陷圖          | 40 |

| 圖 4-7 實驗四無現場退火步驟的SEM缺陷圖             | 41 |

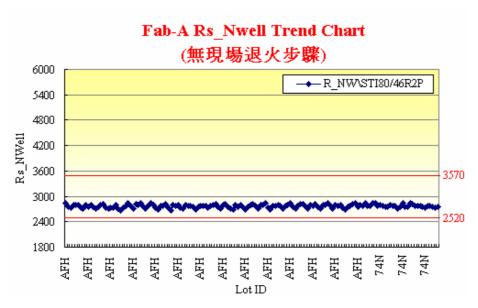

| 圖 4-8 Fab-A與Fab-B之N井區植入阻值趨勢線        | 42 |

| 圖 4-9 N井區 植入阳值                      | 43 |

| 圖  | 4-10 | 矽磊晶之COP缺陷對電性影響              | 44  |

|----|------|-----------------------------|-----|

| 圖  | 4-11 | 磊晶SIMS深度剖面圖                 | 46  |

| 圖  | 4-12 | SIMS實驗流程圖                   | .47 |

| 圖。 | 4-13 | FAB-A & FAB-B 的 SIMS 實驗分析結果 | 48  |

| 圖  | 4-14 | 磊晶自動掺入                      | .48 |

| 昌  | 4-15 | 實驗五條件三bubble缺陷分類            | .51 |

| 圖  | 4-16 | 實驗六 SIMS 結果                 | 53  |

# 第一章、緒論

#### 1.1 研究背景

隨著積體電路技術的演進造就電腦,通訊與網路業的蓬勃發展,而其進步的原動力,在於金氧半導體尺寸不斷地縮小,因為縮小的元件能改善速度切換與元件消耗功率,電路之元件積成密度與功能性(如資訊儲存、邏輯運算、訊號處理等)也都加強了。1998年的 NMOS技術[1],以其通道長度與閘極氧化層的縮小化最為顯著,接面深度次之。在元件的隔離技術上,以往傳統都是採用局部矽氧化(local oxidation of silicon isolation; LOCOS)的隔離技術,但是因為半導體走入 0.25µm 製程以下,LOCOS 便衍生出了一些缺失如:鳥嘴效應(bird beak)、離子佈值導致高溫擴散、沉積薄膜凸出形狀不利平坦化趨勢、小尺寸開口氧化厚度比大尺寸小,為避免這些問題,便開發出淺溝槽隔離(Shallow Trench Isolation或STI)製程取代傳統 LOCOS 方式,以滿足高積成密度的要求。

### 1.2 研究動機與目的

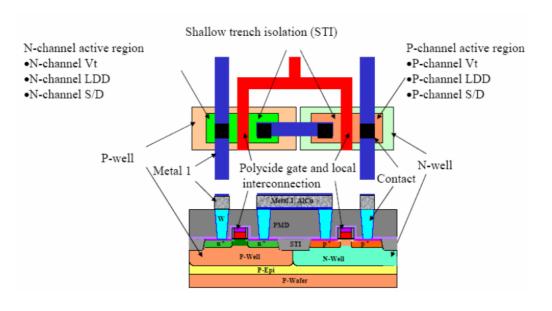

圖 1-1 為CMOS製程結構,製程線寬愈做愈小其元件的隔離區也會相對變小,淺溝槽隔離雖然能提高元件的集積度,但在淺溝槽隔離製程中所衍生的許多問題都須加以解決,傳統的淺溝槽隔離氧化層多以常壓化學氣相沉積(APCVD)或次常壓化學氣相沉積(SACVD)

的O<sub>3</sub>/TEOS反應沉積的氧化層來進行,近來,高密度電漿 (High Density Plasma或HDP) 化學氣相沉積,因具有良好的填洞能力、低的熱預算、低的HF蝕刻率和高產出率,而被廣泛使用在溝槽填洞材料上[2-5]。不過,淺溝槽隔離製程仍有許多問題,例如平坦化的改善[6-7]、隔離邊緣的尖角的影響[8]、消除製程相關的缺陷[9-10],以及降低應力問題[11-13]等等,都是需要防範的重點。

圖 1-1 CMOS 製程結構

#### 1.3 論文架構

本論文架構共分成五章:

第一章、緒論:包含研究背景、研究動機與目的、問題概述及影響程 度。

第二章、文獻回顧:淺溝槽隔離製程流程介紹、掀起缺陷形成機制,

包含來源分析、應力和接觸角度分析、EDX 成分分析及消除的方法等相關文獻。

第三章、實驗方法:利用 KLA & TENCOR 缺陷檢驗機台來分析缺陷形成原因及來源,並運用 HDP 機台的溫度監控找出缺陷發生步驟點,以改善此缺陷問題及提升良率。

第四章、實驗資料分析及結果:其中包含實驗數據分析、最適條件的 決定及確認實驗及產品驗證

第五章、結論:為本研究結果的說明。

#### 1.4 問題概述

八吋半導體廠材料下線的準則,通常一批包含 25 片晶片,而製程流程會依客戶需求而有所不同,材料在製作過程中,會在重要的製程步驟後加缺陷檢驗帳點,以抽樣檢驗方式抽取三片檢驗該批缺陷狀況,以確保該批生產材料的品質狀況,避免不良品續流程,導致不良率產生。本論文研究方向,主要是探討因淺溝槽隔離製程所衍生出來的缺陷來做研究,此缺陷發現的站點是在淺溝槽隔離高密度電漿氧化層沉積步驟後的

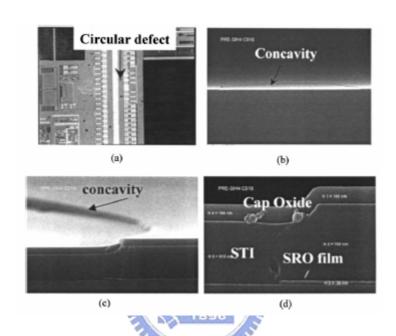

TENCOR "STIDEP"缺陷檢驗站點如圖 1-2 所示,檢驗的晶片缺陷數量超出該層缺陷檢驗規格,從圖 1-3 的 SEM 圖示,發現缺陷的形狀大都是圓形或呈捲曲狀的嵌入在淺溝槽隔離薄膜

裡的缺陷,其缺陷分佈以晶片的晶邊最為嚴重,然後再慢慢延伸到晶片中間區域。

圖 1-2 STIDEP 檢驗站點缺陷圖

圖 1-3 淺溝槽隔離掀起缺陷之 SEM 圖示

# 1.5 影響程度

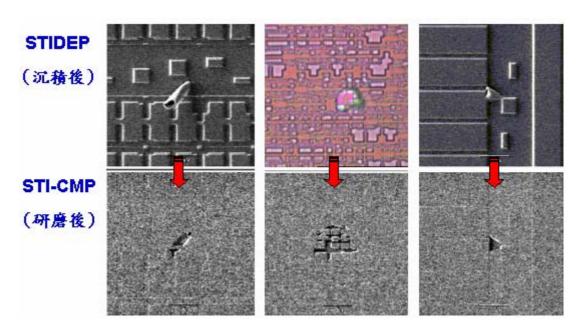

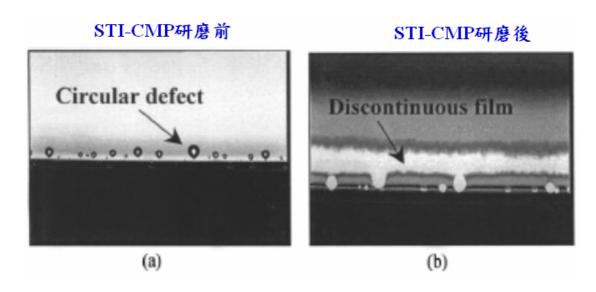

淺溝槽隔離掀起缺陷是 bubble 缺陷的脫落再崁入在淺溝槽隔離薄膜層中(如圖 1-4 STIDEP),在後續的化學機械研磨拋光 (chemical-mechanical polishing 或 CMP)步驟,會將此掀起缺陷一併掏空帶走,被掏空的地方會形成一空洞,導致淺溝槽隔離高密度電漿氧化層之間的薄膜不連續,變成一凹洞缺陷(如圖 1-4 STI-CMP),此會造成電性上漏電流的問題。

圖 1-4 STI-HDP 沉積後到 CMP 研磨後的缺陷圖示

# 第二章、文獻回顧

## 2.1 淺溝槽隔離製程流程介紹(圖 2-1)

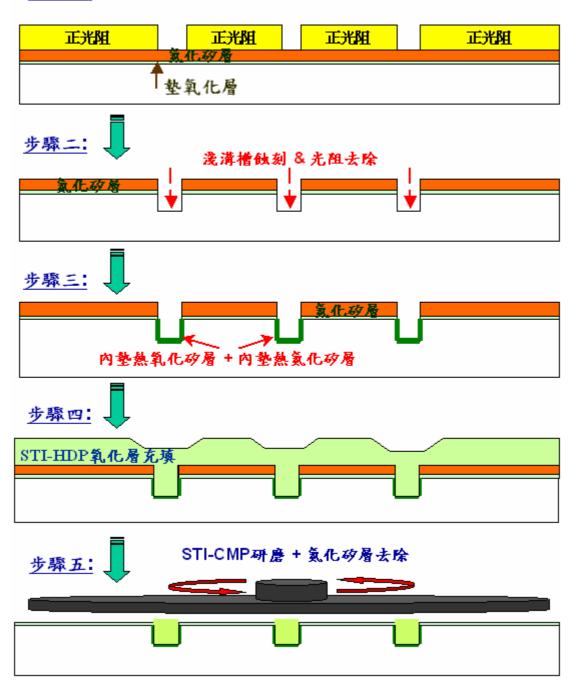

## 2.1.1 常見的淺溝槽隔離流程[15]

首先,步驟一:在8吋矽基板上成長一墊氧化層(pad oxide layer)與一氮化矽層(nitride layer),以正光阻微影程序定義隔離 區後,步驟二:依序進行墊氧化層和氮化矽層的淺溝槽蝕刻步 驟,蝕刻完再將光阻去除。步驟三:之後在淺溝槽的內墊上以 熱氧法成長一氧化矽內墊層(oxide liner layer),其作用是圓滑 主動區上下角區域。上角圓滑非常重要,它可以避免形成寄生 角電晶體,使閘限電壓的漂移最小,並能防止過早出現閘介質 擊穿[19-21]。下角圓滑可以盡量減少壓力引起的缺陷,這些缺 陷在後續加工製程中被繼續散佈下去就會導致漏電。接著以 LPCVD方式沉積一氮化矽內墊層(nitride liner layer),其作用 為避免後續淺溝槽隔離氧化層的RFbias對主動區溝槽側墊的 傷害,尤其可避免影響到窄通道的寬度。步驟四:再以高密度 電漿化學氣相沉積方式沉積氧化層於溝槽內,氧化層充填也是 另一項重點。當隔離尺寸變小後,溝槽內的高寬比(aspect ratio) 明顯增加,對氧化層充填是一項考驗。製程上要求達到無細縫 (seamless)與無孔洞(void free)的形成。早期多以常壓(AP)CVD

或次常壓(SA)CVD 的O<sub>3</sub>/TEOS反應沉積的氧化層來進行,近 來高密度電漿化學氣相沉積由於具有更好的充填能力與薄膜 品質,加上機台的改良,減少沉積時金屬物的污染率,所以才 後來居上[16]。高密度電漿化學氣相沉積係利用一高效率電漿 產生器(如電感藕合(ICP)、電子迴旋共振(ECR)、螺旋波(helicon wave)等),產生一高電漿密度反應源,另外在晶圓上施加另一 個獨立的射頻偏壓(RF bias)電源,沉積時電漿中的正離子撞擊 沉積膜表面,具有消除空洞或細縫的效果[17],並能使氧化層 緻密化。但RF bias潛在地對溝槽側墊的矽基板有傷害的疑慮, 須特別小心防範。氧化層充填沉積後,一般會加上一高溫退火 的密化(densify)步驟使氧化層較緻密,避免後續的化學機械研 磨拋光(chemical-mechanical polishing或CMP)平坦化時研磨速 率的變異,而且改善充填氧化層的品質,步驟五:接著以CMP 技術去除表面多出之材料,並以nitride作為研磨終止層(polish stop),留下一平坦的表面。最後再將氮化矽層薄膜去除,以進 行後續元件之製作。

# 步驟一:

圖 2-1 淺溝槽隔離製程流程簡介

#### 2.2 掀起缺陷形成機制

#### 2.2.1 bubble 缺陷來源分析[10]

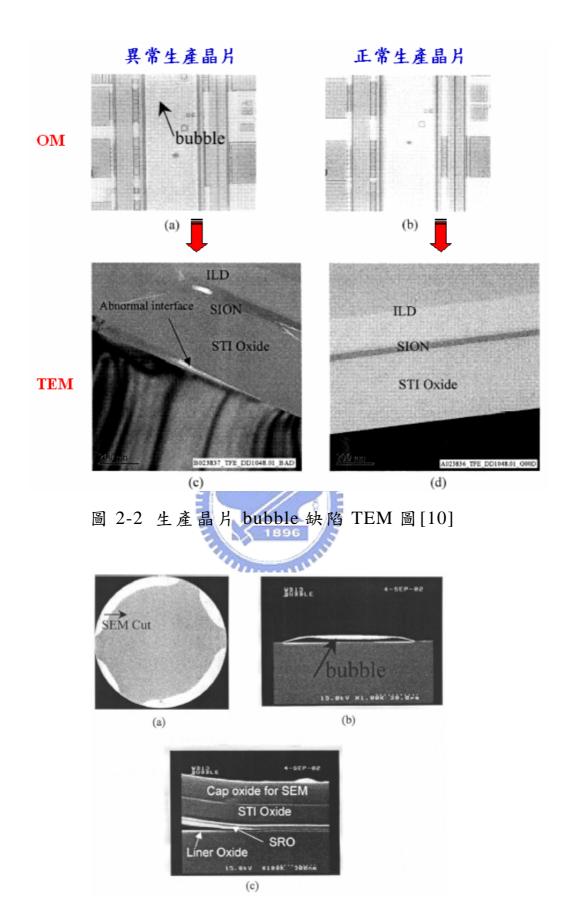

掀起缺陷是來自於bubble缺陷從淺溝槽隔離氧化內墊層薄 膜中掀起脫落,掉落到晶片其他地方,原先 bubble 脫落的地方 變成一凹洞,bubble 掀起掉落到其他地方則形成外來增加的缺 陷, Jin-Kun Lan 等人於 2002 年底, 在新竹科學學區的某半導 體廠,在 0.18 µm 製程使用淺溝槽隔離製程的產品中,也發現 相同的缺陷問題,此半導體廠的淺溝槽隔離結構是爐管氧化矽 內墊層搭配淺溝槽隔離高密度電漿氧化層,他們分析正常無 bubble 跟異常有 bubble 缺陷之生產晶片的 TEM 差異,發現 bubble 缺陷是發現在淺溝槽隔離-HDP 氧化層充填跟爐管氧化 William ! 內墊層間介面有多一層異常的薄膜(圖 2-2 c),而正常晶片在淺 溝槽隔離-HDP氧化層充填跟爐管氧化矽內墊層間的介面並沒 有多一層異常的薄膜產生(圖 2-2 d)。相對也針對異常控片上有 無脫落的 bubble 缺陷做 SEM 分析(圖 2-3),結果跟 TEM 一樣 也是在淺溝槽隔離高密度電漿氧化層充填跟爐管氧化矽內墊 層間介面,發現多一層異常的薄膜,而這異常薄膜 EDX 分析 出來的結果,為偏向 SRO(silicon rich oxidation)的薄膜材質。

圖 2-3 異常控片 bubble 缺陷 SEM 圖[10]

由於 bubble 缺陷與爐管氧化矽內墊層的附著力很差,受到薄膜應力影響會導致 bubble 缺陷掀起,脫離氧化矽內墊層薄膜表面形成一凹洞缺陷(圖 2-4),而這凹洞缺陷在經過後續的後續的化學機械研磨拋光步驟,會形成一不連續的薄膜(圖 2-5)。

圖 2-4 生產晶片凹洞缺陷 SEM 圖示[10]

圖 2-5 異常控片凹洞缺陷圖示[10]

# 2.2.2 不同淺溝槽隔離薄膜之應力與接觸角度分析[10]

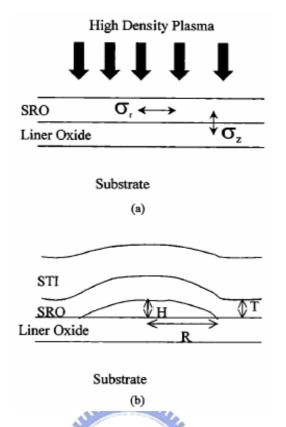

表 2-1 是針對三種不同薄膜材質(爐管氧化矽內墊層薄膜、SRO 薄膜及淺溝槽隔離高密度電漿氧化層薄膜)分析其應力及接觸角度的差異。接觸角度量測的原理乃基於三相(three-phase boundary)平衡,亦即當液體滴入固體表面時,其將會受到來自不同表面/界面間的張力而修飾其形狀,直到達成平衡態為止,進而量測其接觸角母,以判定材料之親、疏水性,而其量測的範圍為 0°~180°,親水性的材料表面其接觸角越小,相反地,若接觸角越大,則代表材料越疏水。從表 2-1 接觸角量測結果,以 SRO 薄膜材質最低 24°,其次是淺溝槽隔離高密度電漿氧化層薄膜 28°,再來是爐管氧化矽內墊層薄膜 33°,表示SRO 薄膜跟淺溝槽隔離高密度電漿氧化層薄膜和爐管氧化矽內墊層薄膜相比是比較偏向於親水性的材質。

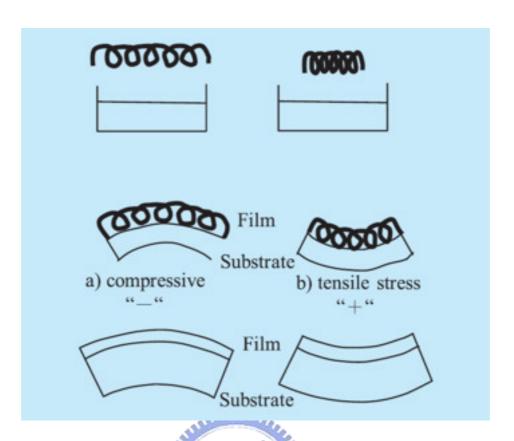

當薄膜沉積附著在基板上時,若受到某種力,因而改變薄膜的長度,薄膜應力通常可分為張應力(tensile stress)和壓應力(compressive stress)兩種,當力量使薄膜長度變長時,薄膜所承受的應力即為張應力,在力平衡情況下,此時基板就相對地承受壓應力,於是造成基板和薄膜會向內側彎曲及形成凹面;反之當力量使薄膜長度縮短時,薄膜所受的應力即為壓應力,

這將使基板和薄膜向下彎曲及形成凸面。兩者應力過大的情況下,容易造成薄膜破壞,或膜層從基板脫落。而應力量測是量測晶圓曲率在薄膜沉積前後的改變量,雷射光掃描晶圓表面,反射光標釋出晶圓的曲率。表 2-1 的應力量測結果顯示只有SRO薄膜的應力是屬於正的張應力,其他淺溝槽隔離高密度電漿氧化層薄膜和爐管氧化矽內墊層薄膜都是負的壓應力,若多此SRO薄膜,在淺溝槽隔離高密度電漿氧化層薄膜沉積時,其HDP機台的氫氣與反應的氣體會轟擊SRO的表面,導致SRO表面的溫度會比SRO跟氧化層內墊層介面之間的溫度來的高,外層薄膜溫度較高會導致膨脹此內層薄膜更多(圖 2-6),因而容易形成 bubble 缺陷。

表 2-1 不同薄膜之應力與接觸角度[10]

| Film                    | Thickness<br>(nm) | stress<br>(10 <sup>9</sup> , dyne/cm <sup>2</sup> ) <sup>a</sup> | Contact<br>angle (degree) |

|-------------------------|-------------------|------------------------------------------------------------------|---------------------------|

| Furnace liner oxide     | 20                | -3.93                                                            | 33                        |

| Silane burst (SRO) film | 26 <sup>b</sup>   | +1.22                                                            | 24                        |

| STI oxide               | 580               | -2.12                                                            | 28                        |

<sup>&</sup>lt;sup>a</sup>Negative and positive values presented compressive and tensile stress, respectively.

<sup>&</sup>lt;sup>b</sup>The thickness of silane burst film was measured using SEM.

圖 2-6 bubble 缺陷形成機制[10]

# 2.2.3 bubble 缺陷 EDX 分析[18]

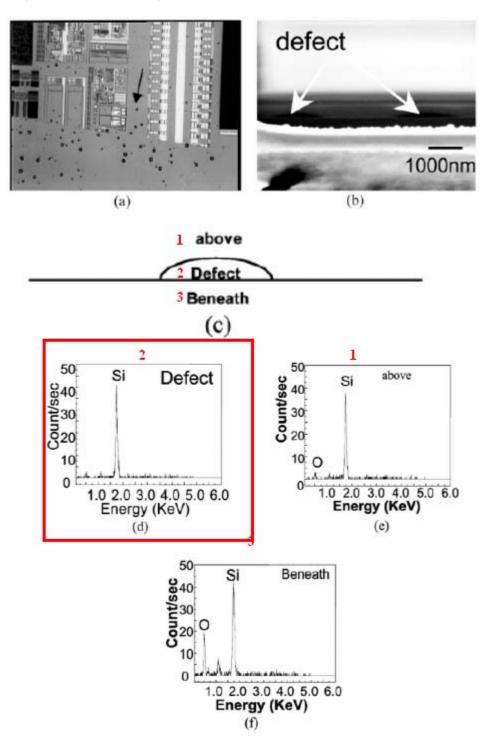

圖 2-7 是針對 bubble 缺陷的 EDX 分析,圖 2-7a 是生產晶片在 OM 下的 bubble 缺陷圖,圖 2-7b 是 bubble 缺陷的 FIB 圖,圖 2-7c 是分析 bubble 缺陷的 EDX 相對位置,EDX 共分析 3個點,bubble 缺陷本身及其上下點,圖 2-7d 是 bubble 缺陷本身 EDX 分析,圖 2-7ebubble 缺陷上方的 EDX 分析,圖 2-7f 是 bubble 缺陷下方的 EDX 分析。

從圖 2-7d 的 EDX Si 和 O 的含量發現, Si 的含量比上下層高,而 O 的含量比上下層低,表示 bubble 缺陷的薄膜性質較

偏向 silicon rich 的薄膜(SRO),此與先前佐證的結果相同,證實 bubble 缺陷是產生在氧化內墊層與淺溝槽隔離高密度電漿氧化層之間的 SRO層。

圖 2-7 bubble 缺陷的 EDX 分析[18]

# 2.2.4 消除 bubble 缺陷方法[18]

Jin-Kun Lan發現用氧氮化物(oxynitride)搭配氧化層(oxide) 的內墊層結構可以消除bubble缺陷,圖 2-8 是不同內墊層結構 的缺陷檢驗狀況,圖 2-8a是淺溝槽隔離高密度電漿氧化層搭配 爐管氧化內墊層,圖 2-8b是淺溝槽隔離高密度電漿氧化層搭配 爐管氧化內墊層及有加N<sub>2</sub>O電漿處理步驟的氧氮化物,圖 2-8c 是淺溝槽隔離高密度電漿氧化層搭配爐管氧化內墊層及有沒 加N2O電漿處理步驟的氧氮化物,檢驗缺陷結果顯示以氧氮化 物有加N2O電漿處理步驟的bubble缺陷最為嚴重(圖 2-8b),其次 是沒加氧氮化物的爐管氧化內墊層(圖 2-8a),而加了 $N_2O$ 電漿 處理步驟的氧氮化物(圖 2-8c),其接觸角度比沒加N2O電漿處 理步驟氧氮化物及爐管氧化內墊層的接觸角度低很多(表 2-3),表示加N<sub>2</sub>O電漿處理步驟的氧氮化物較偏向於親水性材 質,所以容易有bubble缺陷問題的產生。除此之外氧氮化物與 爐管氧化層的內墊層結構搭配,也能改善淺溝槽隔離高密度電 浆氧化層的電性,其崩潰電壓強度有加氧氮化物的內墊層比單 純只有爐管氧化層的內墊層高(表 2-2),

oxynitride without N<sub>2</sub>O treatment (SION-NT)/oxide composite liner.

(b) oxynitride with  $N_2O$  treatment (SION-T)/oxide composite liner

# 圖 2-8 不同內墊層之晶邊狀態圖示[18]

# 表 2-2 不同淺溝槽隔離氧化層的崩潰電壓強度[18]

| $E_{\rm B,C}~({ m MV/cm})^{\rm b}$ | $E_{\rm B,E}~({\rm MV/cm})^{\rm c}$ |

|------------------------------------|-------------------------------------|

| -1.79<br>-9.15                     | -5.88<br>-9.04<br>-7.66             |

|                                    | -1.79                               |

<sup>&</sup>lt;sup>a</sup> The thickness of STI oxide was 200 nm and liner thickness was kept at 40 nm.

# 表 2-3 氧化內墊層及氧氮化物薄膜之應力與接觸角度[18]

Stress data and contact angle for various films

| Film                | Thickness (nm) | Stress (10E9, dyne/cm²) <sup>a</sup> | Contact angle (°) |

|---------------------|----------------|--------------------------------------|-------------------|

| Furnace oxide liner | 20             | -3.93                                | 33                |

| SION-T              | 20             | -1.35                                | 17                |

| SION-NT             | 20             | -1.66                                | 72                |

a Negative values presented compressive stress.

$<sup>^{\</sup>hat{b}}E_{B,C}$ : breakdown electric field strength in wafer center.

$<sup>^{\</sup>rm c}E_{\rm B,E}$ : breakdown electric field strength in wafer edge.

# 第三章、實驗方法

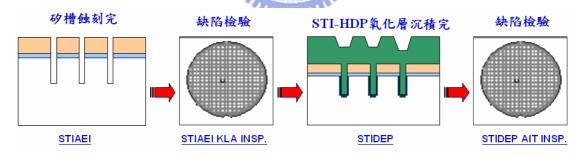

#### 3.1 缺陷檢驗步驟規劃

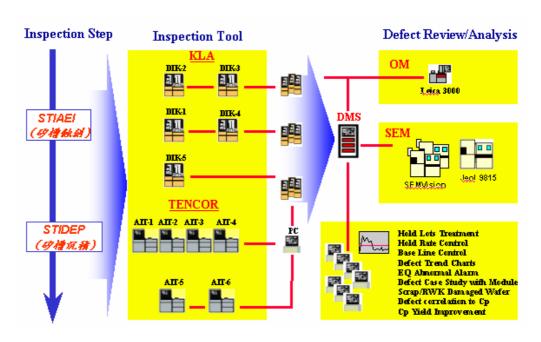

本論文的缺陷研究是發生在淺溝槽隔離高密度電漿沉積完的TENCOR機台檢驗步驟,所以此實驗的檢驗步驟會針對淺溝槽隔離高密度電漿沉積前的 KLA 檢驗機台的矽槽蝕刻檢驗站點(STIAEI)及淺溝槽隔離高密度電漿沉積後的TENCOR檢驗機台的淺溝槽隔離高密度電漿沉積檢驗站點(STIDEP)來做缺陷分析的檢驗帳點,其缺陷檢驗步驟如圖 3-1 所示,在 KLA 機台(STIAEI)或 TENCOR 機台(STIDEP)檢驗完的缺陷資料會儲存到各別的伺服器,伺服器再將資料丟到缺陷管理系統資料庫(DMS)中,如需分析缺陷狀況,再將缺陷資料丟到分析缺陷設備(OM/SEM)。

圖 3-1 缺陷檢驗步驟圖示

#### 3.2 缺陷檢驗機台原理與簡介

KLA-TENCOR 股份有限公司為一專業提昇良率及製程控制的半導體設備商。KLA-TENCOR 擁有相當廣泛產品系列包含軟體、硬體、分析、服務及協助 IC 廠整體晶圓製程上專業化設計良率管理,更提供市場整體良率及晶圓廠數據分析,又包含線上晶圓瑕疵品的監控、光罩瑕疵檢驗、電子束、註記誤差量測、薄膜及表面量測等一系列產品服務。

KLA檢驗機台(圖 3-2 & 圖 3-4)為亮區模式(bright field)下檢驗,使用 die 與 die 之間的灰階差的晶片影像比對,取其影像灰階差值來決定缺陷影像與位置,中間 die 會與左右兩個 die 的影像灰階差值比對,比對有差異機台就會判定為缺陷,呈現在晶片缺陷圖的相對位置中,KLA機台對蝕刻有圖案的檢出率會比沉積鍍膜後的檢出率好。

而 TENCOR 檢驗機台(圖 3-3 & 圖 3-4)為暗區模式(dark field)下的表面缺陷檢驗,以傾斜角度的雷射光打到晶片薄膜表面,PMT 將光轉換為電子訊號,與偵測缺陷所需之訊號差值比其差異,超出設定的則視為缺陷,再呈現在晶片缺陷圖的相對位置中,而 TENCOR 機台對沉積鍍膜後的檢出率會比蝕刻有圖案的檢出率好。

圖 3-3 TENCOR 機台系統功能介紹

KLA與TENCOR機台的主要的差異(圖 3-5)在於燈源、光源角度、訊號處理方式的不同,而對檢驗層的檢出率,KLA機台對蝕刻有圖案的檢出率較好,而TENCOR機台則對沉積平坦薄膜的檢出率比較好,至於機台的產出率(throughput),TENCOR機台比KLA機台快。

圖 3-4 暗區(TENCOR)與亮區(KLA)技術

|                                       | KLA2139                        | AIT                  |

|---------------------------------------|--------------------------------|----------------------|

| • Lamp                                | Xe lamp                        | Ar laser             |

| PM period                             | 6 weeks                        | 1 month              |

| <ul> <li>Light angle</li> </ul>       | 90 degree                      | 20 degree            |

| <ul> <li>Signal processing</li> </ul> | gray level                     | light scattering     |

| <ul> <li>Scan mode</li> </ul>         | random/array mode              | random mode          |

| <ul> <li>Compare mode</li> </ul>      | die to die / cell to cell      | die to die           |

| <ul> <li>Sensitivity</li> </ul>       | front-/back-end 0.2/0.4~.6     | similar              |

| • Excellent detection                 | flat/etch pattern defect       | small jut defect     |

| <ul> <li>Poor detection</li> </ul>    | color variation layer          | roughly/etch layer   |

| <ul> <li>Throughput</li> </ul>        | loW(15~25min.3wfs.50%scan/lot) | high(10min.3wfs/lot) |

| Inspection layer                      | pattern layer                  | flat layer           |

| -                                     |                                |                      |

圖 3-5 缺陷機台 KLA & TENCOR 比對

# 3.3 檢閱缺陷機台簡介

此研究會用到兩種機型的檢閱缺陷機台,一個是光學顯微鏡(OM)另外一個是掃描式電子顯微鏡(SEM)。

光學顯微鏡(圖 3-6)是用光線為光源,經過光學(玻璃)透鏡 聚焦後,使物體放大成像,光學顯微鏡就是利用此原理將缺陷 放大到人眼足以觀察的尺寸。

圖 3-6 光學顯微鏡機台(LEICA INS3000)

掃描式電子顯微鏡(圖 3-7)是奈米材料顯微形貌觀察方面最主要、使用最廣泛普遍的分析儀器。其影像解析度極高,達 0.6nm;且具有景深長特點,可以清晰的觀察起伏程度較大的樣品,如破斷面等;儀器操作使用容易方便,試片製備簡易;多功能(如分析磁性對比);加附件,並可作微小區域的化學組成分析、陰極發光分析等。

SEM是以一極細的電子束在試樣表面上作平面掃描,再偵測電子束與試樣交互作用所產生的二次電子訊號,這是一種低能電子,其產生數量對試樣表面形貌(Morphology)有極大敏感性。要提高SEM的解析度,就要採用一極細且亮度極高的電子束來掃描,高亮度的微小電子束與試片交互作用時,才能在微小作用區域產生足夠數量的二次電子以供偵測。

圖 3-7 掃描式電子顯微鏡機台(Applied SEMVision)

# 3.4 形成原因分析→缺陷來源分析

#### 3.4.1 Fab-A & Fab-B bubble 缺陷

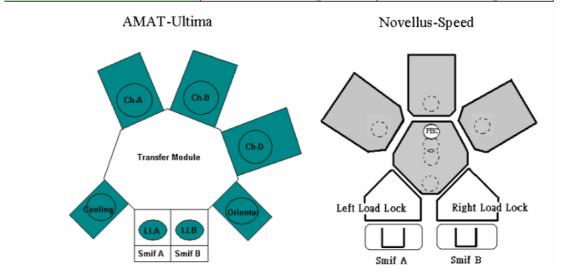

Fab-A和 Fab-B 是隸屬不同廠區,但所生產的產品都是同一客戶所設計的相同產品,此兩個廠區在 STI 製程端機台上的差異,只在於淺溝槽隔離氧化層,Fab-A 是用 AMAT-Ultima 機型而 Fab-B 則是用 Novellus-Speed 機型(圖 3-10),但這兩個生產線都有 bubble 缺陷的問

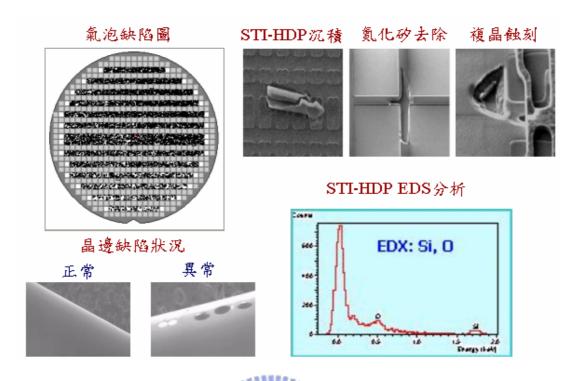

題。圖 3-8 為 Fab-A 的 bubble 缺陷圖,其 bubble 缺陷會在 STI 研磨被帶走,在氮化矽去除後形成一空洞,影響複晶蝕刻的圖案,因 bubble 缺陷導致的空洞,會導致複晶黃光曝的線寬歪曲不正常,影響 複晶蝕刻後的結果與規格不符,對 bubble 缺陷做 FIB 分析,從 FA 圖 示可看出,在後續的鎢通道填洞(tungsten via)步驟,鎢會填滿空洞的 地方,把原本元件要隔絕地方變成導通的地方,形成漏電流。圖 3-9 為 Fab-B 的 bubble 缺陷圖,其 bubble 缺陷也跟 Fab-A 的 bubble 狀況相同,在氮化矽步驟也會造成空洞,也會影響複晶蝕刻後的圖案,正常的晶邊是乾淨無 bubble 缺陷,但異常的晶邊就可看到 bubble 缺陷的痕跡,有些 bubble 沒被掀起,有些 bubble 則已被掀起形成空洞,其 bubble 缺陷的 EDX 元素為 Si和 O。

# 氣泡缺陷圖

STI-HDP沉積

氮化矽去除

複晶蝕刻

FA Image

圖 3-8 Fab-A bubble 缺陷

圖 3-9 Fab-B bubble 缺陷

| STI步驟                     | Fab-A生產線                     | Fab-B生產線                     |

|---------------------------|------------------------------|------------------------------|

| <b>放</b> 縣 為 化 <b>办</b> 展 | TEL Alpha 8SE Vertical       | TEL Alpha 8SE Vertical       |

| 內壁熱氧化矽層                   | Furnaces                     | Furnaces                     |

| <b>分段总条化力度</b>            | TEL Alpha 8SE Vertical       | TEL Alpha 8SE Vertical       |

| 內壁熱氮化矽層                   | Furnaces                     | Furnaces                     |

| 淡溝槽隔離高密度電漿氧化層             | AMAT-Ultima                  | Novellus-Speed               |

| 次海信而解同省及电浆氧化信             | Multi Chamber ; Single Wafer | Multi Chamber ; Single Wafer |

圖 3-10 Fab-A & Fab-B STI 機台比較

### 3.4.2 Fab-A 形成原因分析→缺陷來源

要解決掀起缺陷,首先要找出其缺陷的來源處,實驗一總共用6片實驗晶片,三片為依正常流程生產有圖形的生產晶片、另外三片則為驗機的空白控片,實驗晶片擺放位置,以一片生產晶片搭配一片驗機控片方式穿插擺放,此實驗流程圖如圖 3-11 所示,首先需先檢驗此六片實驗晶片前的缺陷狀況,以區別其前後的缺陷差異,所以在氮化矽蝕刻完的步驟,先用 KLA 檢驗機台檢驗這六片實驗晶片在淺溝槽隔離高密度電漿氧化層沉積前的缺陷狀況,之後再依實驗條件去做淺溝槽隔離高密度電漿氧化層薄膜沉積步驟,沉積完再送到TENCOR 檢驗機台,檢驗淺溝槽隔離高密度電漿氧化層沉積完後的晶片缺陷狀況,比較 STIDEP 沉積後跟 STIAEI 之前後缺陷的差異。

圖 3-11 缺陷來源分析實驗流程

## 3.4.3 Fab-A 缺陷來源實驗一結果

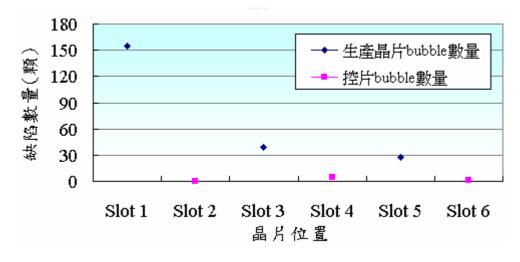

實驗一的缺陷檢驗結果如表 3-1 及圖 3-12 所列,從表 3-1 缺陷檢驗的 bubble 缺陷增加量可發現,如果是機台異常,其生晶片 與控片的缺陷增加量應該也會同步增加,但結果只有生產晶片的缺 陷增加量有增加,而驗機控片的缺陷增加量卻很少,由此可初步推 論其掀起缺陷主要是來自產品製程本身產生,而並非來自 STI-HDP 機台端異常所導致。

| 位置     | 晶片類別 | STIAEI 缺陷數量 | STIDEP缺驗數量 | Bubble 缺陷增加量 |

|--------|------|-------------|------------|--------------|

| Slot 1 | 生產晶片 | 3           | 158        | 155          |

| Slot 2 | 驗機控片 | 0           | 0          | 0            |

| Slot 3 | 生產晶片 | 2           | 41         | 39           |

| Slot 4 | 驗機控片 | 0           | 5          | 5            |

32

28

表 3-1 缺陷來源實驗結果

生產晶片

驗機控片

Slot 5

Slot 6

4

0

圖 3-12 生產晶片 vs 控片的 bubble 缺陷圖

## 3.5 Fab-A 形成原因分析→缺陷發生點

### 3.5.1 缺陷發生點實驗條件二

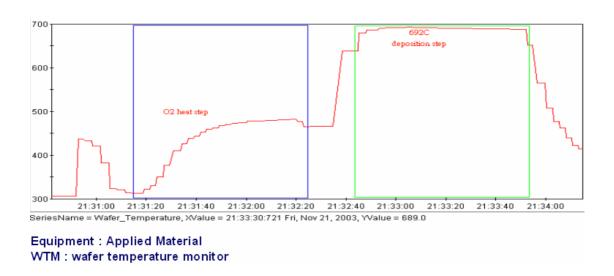

由於發現掀起缺陷開端是在淺溝槽隔離高密度電漿氧化層 沉積完的檢驗帳點發現的,Fab-A所用的淺溝槽隔離高密度電漿 氧化層的機型是美商應材公司,該機型有偵測晶片於沉積時的溫 度監控分佈功能,因此開啟該溫度模擬功能,觀察晶片實際沉積時的溫度狀況,圖 3-13 是淺溝槽隔離高密度電漿機台沉積時的晶片溫度監控(WTM)量測數據圖,從這溫度監控圖發現,晶片在送至沉積室一開始會有 80 秒的O<sub>2</sub>氣體預熱步驟,之後會有 10 秒等待主要沉積步驟反應氣體穩定的時間,而其等待時間到主沉積之間約有 200 多度的溫度差。

圖 3-13 應材機台晶片溫度監控(WTM)圖

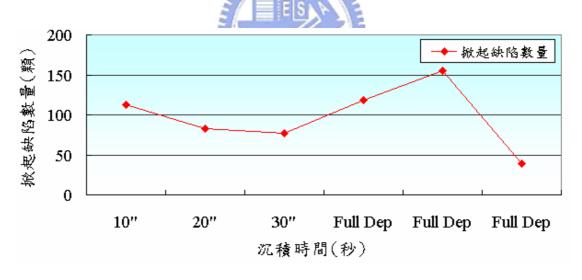

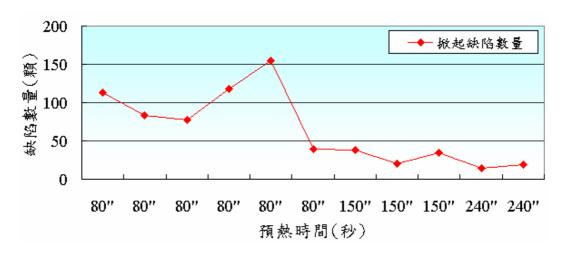

另外從 STI-CMP 研磨後缺陷照片的凹陷地方及其深度看來,缺陷位置大都在內墊層的底部,再加上先前文獻回顧[10]也已分析出其掀起缺陷是介於內墊層間跟淺溝槽隔離高密度電漿氧化層充填之間,為了佐證掀起缺陷是否介於內墊層間跟淺溝槽隔離高密度電漿氧化層充填之間,所以實驗二如表 3-2 所示,在淺溝槽隔離高密度電漿氧化層沉積步驟個別分沉積 10 秒、20 秒、

30 秒與標準完整沉積時間等四種條件,而預熱時間分預熱 80 秒 (標準預熱時間)、150 秒跟 240 秒等三種條件,將這兩個步驟七種條件組成 11 種搭配實驗組,分別也是在氮化矽蝕刻完的步驟,先用 KLA檢驗機台檢驗這 11 片實驗晶片在氧化層沉積前的缺陷狀況,再分別依不同的實驗條件去沉積淺溝槽隔離高密度電漿氧化層薄膜,最後再統一送到 TENCOR 檢驗機台,檢驗沉積完後的晶片缺陷狀況,比較其缺陷的狀況。

表 3-2 Fab-A 缺陷發生點實驗二

| •         |         |          |         |            |      |

|-----------|---------|----------|---------|------------|------|

| A U U VIÈ | STI-HDP | STI-HDP  | 氮化矽蝕刻後  | STI-HDP沉積後 | 掀起缺陷 |

| 晶片片號      | 預熱時間(秒) | 沉積時間(秒)  | 缺陷數量(顆) | 缺陷數量(顆)    | 數量   |

| 1         | 80"     | 10"      | 1       | 114        | 113  |

| 2         | 80"     | 20"      | 2       | 85         | 83   |

| 3         | 80"     | 30"      | 1       | 78         | 77   |

| 4         | 80"     | Full Dep | 1       | 119        | 118  |

| 5         | 80"     | Full Dep | 3       | 158        | 155  |

| 6         | 80"     | Full Dep | 2       | 41         | 39   |

| 7         | 150"    | Full Dep | 1       | 39         | 38   |

| 8         | 150"    | Full Dep | 2       | 22         | 20   |

| 9         | 150"    | Full Dep | 1       | 35         | 34   |

| 10        | 240"    | Full Dep | 0       | 14         | 14   |

| 11        | 240"    | Full Dep | 0       | 19         | 19   |

#### 3.5.2 Fab-A 缺陷發生點實驗二結果

從表 3-2 第一片條件(淺溝槽隔離高密度電漿沉積 10 秒)的缺陷數量可看出,掀起缺陷在一開始的淺溝槽隔離高密度電漿沉積就已經開始產生,表示掀起缺陷最初發生點在淺溝槽隔離高密度電漿氧化層主沉積階段,在電漿一開始反應就形成,圖 3-14 的沉積時間對應掀起缺陷圖可得知隨著沉積時間拉長,其缺陷數量也會因而增加,但

有些缺陷可能會包覆在淺溝槽隔離高密度電漿沉積薄膜中而尚未能在 STIDEP 沉積檢驗帳點檢驗出來,必須流程到 STI-CMP 研磨的步驟,其掀起缺陷會被 STI-CMP 研磨一併研磨帶走掉,待 STI 裸露出來時,才能知道實際 bubble 缺陷數量多寡。從實驗二可得知其 bubble 缺陷發生點是介於內墊層間跟淺溝槽隔離高密度電漿氧化層充填之間。另外,我們從圖 3-15 的預熱時間對應掀起缺陷圖比較,也發現如果延長預熱的時間,可有效降低掀起缺陷數量,表示延長預熱時間,使晶片有足夠的時間將薄膜表面的水氣先揮發出來,增加其薄膜附著能力,避免 bubble 缺陷掀起。

圖 3-14 沉積時間對應掀起缺陷圖

圖 3-15 預熱時間對應掀起缺陷圖

## 3.6 薄膜應力

從先前缺陷發生點的實驗結果發現,雖然延長淺溝槽隔離 高密度電漿沉積前的預熱時間,可降低 bubble 缺陷產生,但從 表 3-3 預熱時間的比較表可看出,如果使用延長預熱時間的方法,一 批需多增加約 66 分鐘的額外時間,此對機台產出會有很大的影響, 較不適用於實際生產線使用。

表 3-3 預熱時間比較表

| 預熱時間(秒) | 標準時間 | 延長時間 | 差異   |

|---------|------|------|------|

| 單片      | 80   | 240  | 160  |

| 一批      | 2000 | 6000 | 4000 |

從 Jin-Kun Lan[10]的分析結果發現掀起缺陷與薄膜的應力有強相關,而應力是不同材料間的不匹配所造成,針對薄膜而言,當薄膜沉積在基板後,薄膜處於應變狀態,若以薄膜應力造成基板彎曲形變的方向來區分,如圖 3-16 所示可將應力[22]分為張應力(tensile

stress)與壓應力(compressive stress)。張應力是當膜施力向外伸張,基 板向內壓縮、膜表面下凹,薄膜因為有張應力的作用,薄膜本身產生 收縮的趨勢,如果膜層的張應力超過薄膜的彈性限度,則薄膜就會破 裂甚至剝離基板而翹起。壓應力則呈相反的狀況, 膜表面產生外凸的 現象,在壓應力的作用下,薄膜有向表面擴張的趨勢。相同的如果壓 應力到極限時,則會使薄膜向基板內側捲曲,導致膜層起水泡。數學 上表示方法為張應力--正號、壓應力--負號。造成薄膜應力的主要來 源有外應力 (external stress)、熱應力 (thermal stress) 及內應力 (intrinsic stress),其中,外應力是由外力作用施加於薄膜所引起的; 熱應力是因為基板與膜的熱膨脹係數相差太大而引起,此情形發生於 製鍍薄膜時基板的溫度,冷卻至室溫取出而產生。內應力則是薄膜本 身與基板材料的特性,主要取決於薄膜的微觀結構和分子沉積缺陷等 因素,所以薄膜彼此的界面及薄膜與基板邊界之相互作用就相當重 要,這完全控制於製鍍的參數與技術上,此為壓力的主要成因。

圖 3-16 薄膜應變狀況[22]

## 第四章、實驗結果與討論

## 4.1 Fab-A 改善掀起缺陷→實驗三條件

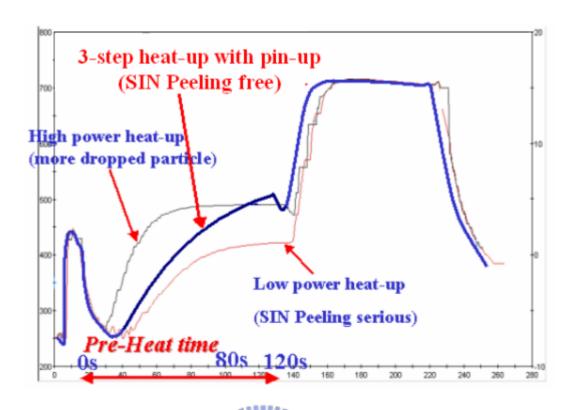

實驗三主要新舊參數差異如表 4-1 所示,主要針對O2預熱(O2 heat up)步驟做改變,實驗條件有三種,條件一是原本的舊程式 (baseline; low power heat-up) 一 段 式 步 驟 的 RF 能 量 (1300W/3100W) ,預熱時間 80 秒,晶片在夾盤預熱狀態是 pin-down。條件二是用high power heat-up也是一段式步驟的RF 能量(2500W/3100W),預熱時間也是 80 秒,晶片在夾盤預熱狀態也是pin-down。條件三new recipe則分三段RF能量,三段不同預熱時間(共 110 秒),晶片在夾盤預熱狀態是pin-up,晶片用pin-up預熱,其晶片受熱面積會較均勻,其傳熱速度會比 pin-down方式來的快些。

表 4-1 O2預熱步驟新舊程式差異

| Baseline   | ○2 Heat up  |

|------------|-------------|

| Top RF(W)  | 1300        |

| Side RF(W) | 3100        |

| Pin 位置     | down        |

| 時間(秒)      | 80          |

| 備註         | SIN Peeling |

| New recipe | O₂ Heat up    | O <sub>2</sub> Heat up-2 | O <sub>2</sub> Heat up-3 |

|------------|---------------|--------------------------|--------------------------|

| Top RF(W)  | 1300          | 2500                     | 3000                     |

| Side RF(W) | 3100          | 3500                     | 4000                     |

| Pin 位置     | up            | up                       | up                       |

| 時間(秒)      | 80            | 25                       | 5                        |

| 備註         | SIN Peeling t | ree                      |                          |

圖 4-1 不同預熱程式 WTM Profile 圖

## 4.2 FAB-A 改善掀起缺陷→缺陷檢驗實驗三結果

實驗結果其條件一舊程式低能量預熱,會有 bubble 掀起缺陷的問題,條件二高能量預熱,雖然可改善 bubble 掀起缺陷的問題,但因能量太高會導致機台內壁會有掉落缺陷問題,以條件三分三階段能量預熱,並搭配 pin-up 功能,改善 bubble 掀起缺陷效能最佳,可改善製程 bubble 掀起缺陷也能控制機台掉落缺陷的問題,原因可從圖 4-1 WTM 圖看出端倪,條件一低能量預熱,其預熱到沉積的溫度差最大近 300℃,所以會有產品薄膜預熱到沉積前的膨漲係數差異過大,所造成的製程上所引起的掀起缺陷,條件二高能量預熱,雖然可降低預熱到沉積

的溫度差,但高能量的能量太強會導致機台有掉落缺陷問題, 因此也不適用,而條件三是分三階段能量預熱搭配 pin-up 功能,其預熱到沉積的溫度差,可從原先差 300℃降到 200℃,讓 薄膜預熱到主沉積前的膨脹係數差異不要太大,減緩熱應力作 用。

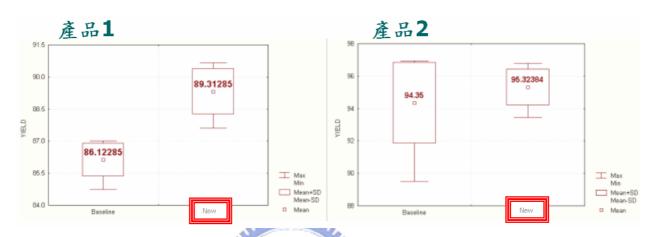

圖 4-2 為針對新舊程式各選 20 片晶片去沉積淺溝槽隔離高密度電漿氧化層薄膜,沉積完檢驗其缺陷狀況,從缺陷趨勢圖可看出新程式(三階段能量預熱搭配 pin-up 功能)改善掀起缺陷能力比現行舊程式好,因為新程式減緩預熱步驟到主沉積步驟之間的溫度差,降低薄膜預熱到沉積前的熱膨脹係數的差異。

圖 4-2 新舊 STI-HDP 程式的掀起缺陷圖

## 4.3 FAB-A 改善掀起缺陷→良率結果

為了驗證新程式對產品良率的改善程度,故以兩批產品(產品1&產品2)在淺溝槽隔離高密度電漿氧化層步驟,新程式與

舊程式分別各沉積一半的淺溝槽隔離高密度電漿氧化層薄膜,後續步驟則按照正常流程到整個產品製程結束,最後再比較其良率上的差異,圖 4-3 為兩個產品在良率的差異,結果顯示新的 STI-HDP 程式其良率改善會比舊程式高約 1~3%。

圖 4-3 新舊 STI-HDP 程式的良率差異

# 4.4 FAB-B 改善掀起缺陷→實驗四條件

Fab-B 所用的淺溝槽隔離高密度電漿氧化層的機型跟 Fab-A不同,Novellus-Speed機型並沒有偵測晶片溫度功能,所以無法提供溫度曲線的分佈來調整參數,降低預熱和主沉積之間的溫差,所以Fab-B實驗步驟點鎖定在淺溝槽隔離內墊熱氧化層步驟,在淺溝槽隔離內墊熱氧化層高100℃並通氮氣的現場退火步驟,目的是利用高溫去除內墊熱氧化層薄膜的水氣,釋放晶片表面的熱應力,減緩與後層薄膜的熱膨脹係數差異,而通氮氣目的是用來氮化內墊熱氧化層表面以增加晶片表面與後層薄膜的

附著能力,降低 bubble 掀起的數量。

實驗四條件如表 4-2 所列,共有 12 片實驗晶片,第1到6片是在淺溝槽隔離內墊熱氧化層沉積完後多加一現場退火步驟,而第7到 12 片,則依目前標準生產條件(baseline)不加現場退火步驟,後續的淺溝槽隔離內墊熱氮化層跟淺溝槽隔離高密度電漿氧化層則依標準條件不做變更。

表 4-2 實驗四條件

| Step               | Condition                    | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

|--------------------|------------------------------|---|---|---|---|---|---|---|---|---|----|----|----|

| STI Oxide Liner    | Baseline                     |   |   |   |   |   |   | Χ | Χ | Χ | χ  | χ  | Х  |

|                    | Baseline + in-situ annealing | 0 | 0 | 0 | 0 | 0 | 0 |   |   |   |    |    |    |

| STI Nitride Liner  | Baseline                     | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  |

| STI-HDP Deposition | Baseline(Novellus)           | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  |

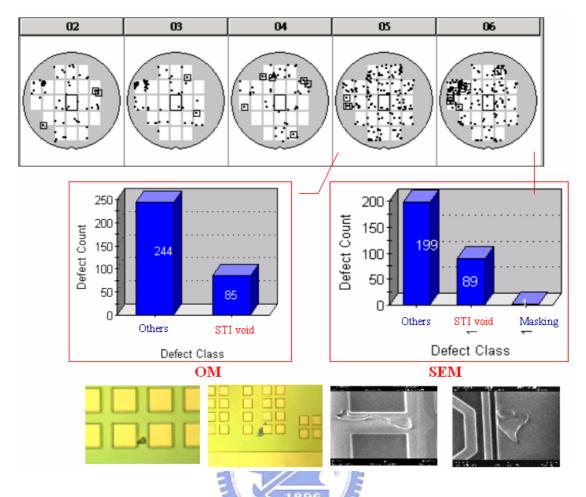

# 4.5 FAB-B 改善掀起缺陷實驗四結果→缺陷檢驗

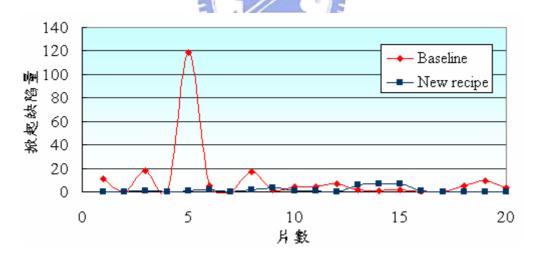

表 4-3 為實驗四實驗條件及STIDEP的缺陷檢驗資料,圖 4-4 為 STIDEP的缺陷趨勢圖,從這檢驗結果顯示有加現場退火步驟的晶片(圖 4-5;第1到第6片缺陷圖),因高溫先將內壁熱氧化矽層表層壓應力的殘留氣體或水氣先釋放出來,再用N2讓表面氮化,增加與後層的附著力,所以可有效降低bubble缺陷產生,而沒加現場退火步驟的晶片(圖 4-6;第7到第12片缺陷圖),因在淺溝槽隔離內墊熱氧化層沉積前後薄膜的熱膨脹係數差異太大,所以會有嚴重的bubble缺陷問題,圖 4-7 為沒加現場退火步驟在STI-DEP沉積後&晶邊缺陷狀況及STI-CMP研磨後有bubble缺陷的SEM圖,從STI-DEP沉

積後的SEM圖可看出薄膜因張應力施力破裂剝離,形成掀起缺陷, 在晶邊的缺陷狀況SEM圖可看出有些在晶邊的bubble缺陷已經 被剝離,也些則尚未被剝離,缺陷成鼓起狀態,此缺陷若續流 程到STI-CMP研磨則會變成一凹洞缺陷,導致淺溝槽隔離之間的 薄膜不連續。

表 4-3 實驗四 STIDEP 缺陷檢驗結果

| Condition                 | 1  | 2  | 3  | 4  | 5 | 6 | 7    | 8    | 9    | 10   | 11   | 12   |

|---------------------------|----|----|----|----|---|---|------|------|------|------|------|------|

| without in-situ annealing |    |    |    |    |   |   | Х    | Х    | X    | Х    | Х    | Х    |

| with in-situ annealing    | 0  | 0  | 0  | 0  | 0 | 0 |      |      |      |      |      |      |

| STIDEP Defect Count(ea)   | 16 | 18 | 15 | 12 | 8 | 4 | 3724 | 1364 | 3482 | 3269 | 1408 | 3614 |

圖 4-4 實驗四 STIDEP 檢驗之缺陷趨勢線

圖 4-5 實驗四有加現場退火步驟的 STIDEP 缺陷圖

圖 4-6 實驗四無現場退火步驟的 STIDEP 缺陷圖

圖 4-7 實驗四無現場退火步驟的 SEM 缺陷圖

#### 4.6 FAB-B 改善掀起缺陷實驗四結果→電性結果

實驗證明 Fab-B 在淺溝槽隔離內墊熱氧化層沉積後多加一現場退火步驟,可有效降低 bubble 掀起缺陷產生,但比較 FAB-A 與FAB-B 的電性結果如表 4-4,發現 Fab-B 的 N 井區阻值高達 4584 Ohm-cm,超出客戶要求的阻值規格 3045 Ohm-cm,跟 Fab-A 的 N 井區阻值 2768 Ohm-cm 比較,Fab-B 的 N 井區阻值比FAB-A 的 N 井區阻值高出 50%以上,比較幾批 N 井區阻值的電性結果,Fab-B的 N 井區阻值都比 FAB-A 的 N 井區阻值高(圖

4-8) •

表 4-4 FAB-A 與 FAB-B 之 N 井區阻值表

| N井區阻值(Ohm-cm) | Fab-A | Fab-B |

|---------------|-------|-------|

| 平均值           | 2768  | 4584  |

| 平均最大值         | 2850  | 5392  |

| 平均最小值         | 2660  | 3260  |

| 規格下限          | 2520  | 2520  |

| 規格            | 3045  | 3045  |

| 規格上限          | 3570  | 3570  |

圖 4-8 FAB-A 與 FAB-B 之 N 井區阻值趨勢線

### 4.7 FAB-B 電性異常分析~機台釐清

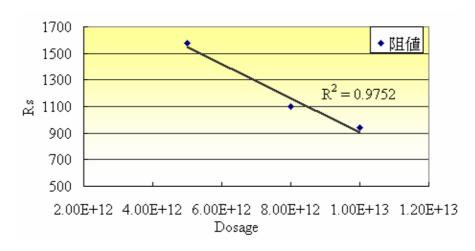

首先先澄清是否為中電流植入機台偏移導致N井區阻值飄高,故針對N井區植入步驟分三種不同劑量,正常N井區植入的劑量是與阻值呈反比,實驗條件如表 4-5 所示,第一種條件為現行生產程式的劑量(8E+12),第二種條件為增加劑量(1E+13),第三種為減少劑量(5E+12),此三片分別依不同實驗條件植入不同劑量,待三片植入完,再一起量其N井區的阻值,實驗結果如圖 4-9 所示,其阻值趨勢圖是呈逆線性分佈(R²=0.9752),植入劑量愈多阻值愈低,澄清N井區阻值飄高並非植入機台異常所致。

表 4-5 N 井區植入劑量條件與阻值

|          |      | A STATE OF THE STA |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N井區植入劑量  | 阻值   | 備註                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.00E+13 | 938  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 8.00E+12 | 1102 | 現行程式                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5.00E+12 | 1575 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

圖 4-9 N 井區植入阻值

## 4.8 文獻回顧~磊晶矽膜製程簡介

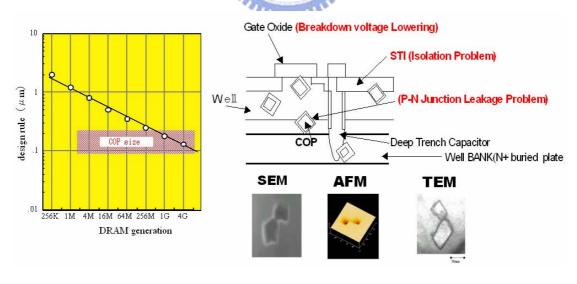

由於該研究的產品為繪圖晶片的產品,對電性要求會比較嚴謹,因此晶片材料需用到矽磊晶製程的晶片,高階產品之所以要求用磊晶晶片主要是傳統拉晶的晶片會在長晶過程造成空缺孔洞缺陷,這種缺陷型態稱為 COP(crystal originated particles)缺陷,圖 4-10 為 COP對電性的影響程度,COP在 SEM 的形狀是菱形狀,而 COP 缺陷的尺寸會隨著 DRAM 製程演進要求愈嚴苛,COP 缺陷對高階產品電性影響很大,COP 若落在井區的匯合點,會導致 P-N 匯合點漏電流,若落在 STI 區,則會影響 STI 在元件隔離的問題,若落在閘極區,則會導致崩潰電壓較低的問題產生。

圖 4-10 矽磊晶之 COP 缺陷對電性影響

#### 4.8.1 矽磊晶製程

磊晶矽膜是指在一基座上(大半是矽晶圓),長出的矽單晶薄膜,

矽磊晶的應用,主要是在一含高濃度掺入雜質的矽基座 (Heavily Doped Substrate)上,如 n+層,長一層低濃度掺入雜質的矽磊晶層,如 n-型或 p-型磊晶,其掺入雜質 (Dopant) 濃度,視元件的應用而有所不同,此種結構可降低軟錯 (Soft Errors),防止鎖上(Latch-up),及提供局部雜質吸著(Gettering) 的作用,一般而言,數位 (Digital) 元件,尤其是數位二極元件,對厚度及均勻度的要求較嚴格。

#### 4.8.2 矽磊晶成長

用來成長矽磊晶的反應器,最常見的有水平式(Horizontal),垂直式 (Verticle),及柱形(Cylinder),是依反應氣體流通方向相對於晶面方向 所定,且每次可放多片矽晶圓,進行矽磊晶成長。而較新式之矽磊晶 反應器,與傳統之磊晶反應器相比,新式的反應器設計,主要是儘可能的增加每次磊晶成長所能放的矽晶圓片數,以提高產能,降低成本。

矽磊晶成長的主要目的,是長出一層缺陷少,且可控制厚度及掺入雜質的矽單晶薄膜,其先決條件,是矽基座必須乾淨無缺陷,且基座表面溫度需夠高,或提供非熱能能量,使經化學反應後吸附原子有足夠的動能,移動到適當的位置,而達到磊晶成長的目的。

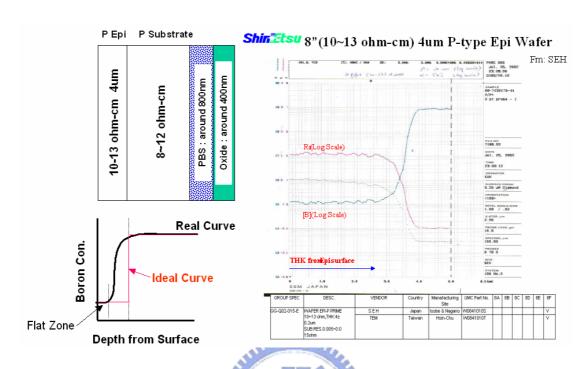

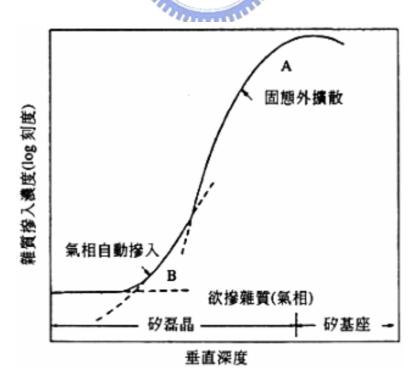

圖 4-11 為此產品所用的磊晶 SIMS 剖面圖,此磊晶流程是在P-type 矽基座上在長 4um 厚度的單晶薄膜,因矽基座含高濃度掺入雜質,因此雜質會由晶背蒸發出而造成自動掺入,所以晶背會以 CVD

方式長兩層薄膜(PBS & oxide)來避免自動掺入產生。

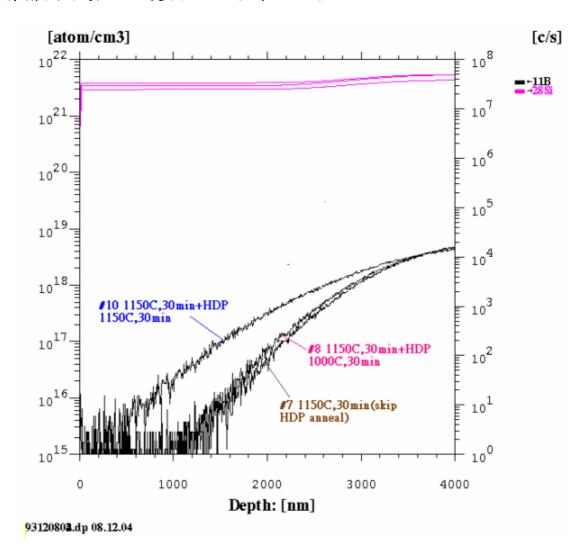

圖 4-11 磊晶 SIMS 深度剖面圖

## 4.9 FAB-B的N井區阻值異常分析~SIMS分析實驗設計

圖 4-12 為分析 FAB-A 與 FAB-B 在 N 井區阻值差異的 SIMS 實驗流程圖,也是跟產品相同一樣是用 P-type 的 4um 的磊晶晶片,FABA 與 FAB-B 各一片,從氮化矽沉積步驟,模擬兩個生產線實際生產流程狀況,一直到 N 井區植入步驟結束,其中唯一的差異是在淺溝槽隔離氧化層沉積步驟,FAB-A 是沒有額外的現場退火步驟,而 FAB-B 是有加額外的現場退火步驟,待 N 井區植入完再一起做 SIMS 分析。

圖 4-12 SIMS 實驗流程圖

## 4.10 FAB-B 的 N 井區阻值異常分析~阻值飄高形成分析

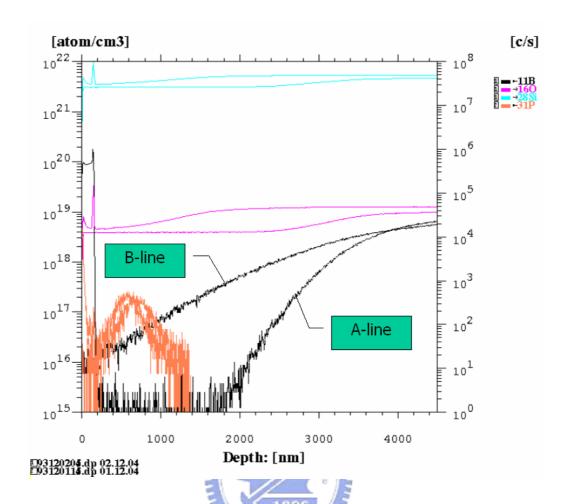

圖 4-13 為 FAB-A & FAB-B 的 SIMS 實驗分析結果,比較兩個生產線的 SIMS 結果,發現 FAB-B 是因為 P 矽基座的高掺入雜質 濃度 埋層 (Heavily Doped Buried Layer) 有氣相自動掺入 (Auto-doping)到低掺入雜質的磊晶層中,導致原本在 N 井區植入深度的 phosphorous 濃度範圍,正常是不應該有磊晶 boron 濃度,因氣相自動掺入(圖 4-14),磊晶 boron 濃度(提供額外電洞)跑到 N 井區植入 phosphorous 濃度(提供額外電子)範圍內,導致 N 井區植入 phosphorous 劑量不足,造成 N 井區阻值飄高。

圖 4-13 FAB-A & FAB-B 的 SIMS 實驗分析結果

圖 4-14 磊晶自動掺入[23]

### 4.11 FAB-B 的 N 井區阻值異常分析~阻值飄高形成分析

### 4.11.1 實驗五步驟說明

因 SIMS 分析出是 P 矽基座的高掺入雜質濃度埋層有氣相自動掺入到低掺入雜質的磊晶層,所以初步懷疑是否為過長熱預算時間導致,故實驗五條件(表 4-6)是針對淺溝槽隔離內墊熱氧化層的現場退火時間,去比較不同熱預算時間對 N 井區阻值的影響程度有多大。實驗條件有三種,條件一(片號 2)為目前 STI 內壁熱氧化層現行程式 1150℃現場退火90 分搭配 1150℃ 30 分的淺溝槽隔離密化(總熱預算時間 120 分),條件二(片號 3-4)則將 1150℃現場退火時間從 90 分降到 30 分,淺溝槽隔離密化也是搭配 1150℃ 30 分(總熱預算時間 60 分),而條件三(片號 5-6)則為依照 FAB-A 的方式其 STI 內壁熱氧化層並沒有多作額外的現場退火步驟,而後續的淺溝槽隔離密化時間也是 1150℃ 30 分(總熱預算時間 30 分)。

表 4-6 實驗五條件

| 製程  | 步驟     | 現場退火時間     | STI密化時間   | 總共熱預算時間 | 2 | 3 | 4 | 5 | 6 |

|-----|--------|------------|-----------|---------|---|---|---|---|---|

|     |        | 1150℃ 90分  | 1150℃ 30分 | 120分    | ٧ |   |   |   |   |

| STI | 內壁熱氧化層 | 1150℃ 30分▼ | 1150℃ 30分 | 60分     |   | ٧ | V |   |   |

|     |        | 無          | 1150℃ 30分 | 30分     |   |   |   | ٧ | ٧ |

## 4.11.2 實驗五結果說明

表 4-7 為實驗五 N 井區阻值及缺陷檢驗結果,從 N 井區阻

值可發現降低 STI 內壁熱氧化層的現場退火時間,確實可降低 N 井區阻值,現場退火時間若從 90 分降到 30 分,就可降約 30% N 井區阻值(從 4416 ohm-cm 降到 3080 ohm-cm),但仍超出規格無法達到客戶要求,其中以條件三(片號 5-6) FAB-A 的 N 井區阻值,最能符合規格(2658 ohm-cm),但此條件雖然能改善 N 井區阻值的問題,卻有掀起缺陷的問題,圖 4-15 為實驗五的 STIDEP 的缺陷檢驗圖,直條圖分析歸類的 others 缺陷為細小的 nodule 缺陷,此缺陷是 non-killer 缺陷,但條件三除了 nodule 缺陷,還有掀起缺陷,故不適用於解決 N 井區阻值飄高問題。由此實驗證明過長的熱預算時間對磊晶產品確實會造成 P 矽基座的高掺入雜質濃度埋層自動掺入到低掺入雜質的磊晶層中,而導致 N 井區阻值飄高。

表 4-7 實驗五 N 井區阻值及缺陷檢驗結果

| 製程  | 步驟     | 現場退火時間    | STI密化時間   | 總共熱預算時間 | 2    | 3    | 4    | 5    | 6    | STI掀起缺陷 |

|-----|--------|-----------|-----------|---------|------|------|------|------|------|---------|

|     |        | 1150℃90分  | 1150℃ 30分 | 120分    | 4416 |      |      |      |      | 無       |

| STI | 內壁熱氧化層 | 1150℃ 30分 | 1150℃30分  | 60分     |      | 3080 | 3004 |      |      | 無       |

|     |        | 無         | 1150℃ 30分 | 30分     |      |      |      | 2658 | 2522 | 有       |

N井區阻值(規格 3045 +/- 525 ohm-cm)

圖 4-15 實驗五條件三 bubble 缺陷分類

#### 4.12 FAB-B 的 N 井區阻值異常分析~阻值飄高解決方法

### 4.12.1 實驗六步驟說明

實驗五將淺溝槽隔離內墊熱氧化層的現場退火時間從 90 分降為 30 分,雖然可降低 N 井區阻值,但還是超出客戶所要求的規格,因此實驗六如表 4-8 所示,淺溝槽隔離內墊熱氧化層的現場退火時間固定為 30 分,主要是針對淺溝槽隔離氧化層沉積後的密化步驟的溫度做改變,實驗六條件有三種,條件一(片號 7)不做淺溝槽隔離密化步驟、條件二(片號 10-11)現行程式 1150°C 30 分鐘的淺溝槽

隔離密化及條件三(片號 8-9) 1000℃ 30 分鐘的淺溝槽隔離密化,目的是分析降低密化溫度對 N 井區阻值的影響程度,最後選三片做SIMS 分析(片號 7、8、10)。

表 4-8 實驗六條件

| 製程步驟          |            | 實驗條件          | 7 | 8 | 9 | 10 | 11 |

|---------------|------------|---------------|---|---|---|----|----|

|               | 內壁熱氧化層     | 1150℃ 現場退火30分 | ٧ | ٧ | ٧ | ٧  | v  |

| STI STI密化温度及時 |            | 無             | ٧ |   |   |    |    |

|               | STI密化溫度及時間 | 1150℃ 30分     |   |   |   | ٧  | V  |

|               |            | 1000℃ 30分 🔻   |   | ٧ | ٧ |    |    |

#### 4.12.2 實驗六結果說明

實驗六的 SIMS 結果如圖 4-16 所示,條件二(月號 10)現行程式 1150°C 30分,其 P 矽基座的高掺入雜質濃度埋層自動掺入到低掺入雜質的磊晶層中,導致磊晶 boron 的濃度自動掺入到 N 井區植入 phosphorous 濃度範圍,導致 N 井區阻值飄高,而條件三(月號 8)降低淺溝槽隔離密化溫度從 1150°C到 1000°C,則可避免 P 矽基座的高掺入雜質濃度埋層自動掺入到低掺入雜質的磊晶層中,因此其磊晶 boron 的濃度曲線降到正常曲線,條件一(月號 7)不做淺溝槽隔離密化步驟,雖然 SIMS 結果與條件三相同,其磊晶 boron 的濃度曲線也是降到正常曲線,但淺溝槽隔離密化目的是將淺溝槽隔離氧化層薄膜緻密化,便於後層 STI-CMP 研磨,如果將此步驟刪除,可能會影響到 STI-CMP

研磨的均匀性,故不採用條件一作法,採用條件三的作法,將 淺溝槽隔離密化溫度從 1150℃到 1000℃。

圖 4-16 實驗六 SIMS 結果

## 第五章、結論

每個時代的製程能力會隨著技術的演進而所不同,在新製程開發 階段,必須針對電性、製程能力、廠的機台極限及客戶需求,對每個 環節做驗證,建立不同製程的平台,以便提供給相同製程不同客戶的 需求,一旦電性的規格及製程平台建立好,後續任一的製程變更,都 會影響電性的效能,尤其對淺溝槽隔離部分,對電性的影響佔很大的 比重,更不容忽視。在淺溝槽隔離高密度電漿氧化層沉積前的薄膜為 壓應力,在淺溝槽隔離高密度電漿氧化層步驟,其機台的預熱時間與 主沉積間的溫度差異,會導致薄膜預熱到沉積前的熱膨脹係數相差 太大,使壓應力轉成張應力使bubble缺陷剝離,而變成掀起缺陷,其 淺溝槽隔離的結構會依各半導體製程開發而有所不同,針對FAB-A的 Marine No. 淺溝槽隔離掀起缺陷問題,是改良淺溝槽隔離高密度電漿氧化層沉積 參數,減緩預熱時間與沉積時間的溫度差,降低其預熱到沉積前之 間的熱膨脹係數的差異,而FAB-B則是在淺溝槽隔離內墊熱氧化層步 驟增加No現場退火的步驟,利用高溫先將內壁熱氧化矽層表層壓應力 的殘留氣體或水氣先釋放出來,再用No讓表面氮化,增加與後層淺溝 槽隔離高密度電漿氧化層的附著力。但對需用到磊晶製程晶片的產 品,若用FAB-B方法則需考量過長的熱預算會造成P矽基座的高摻入 雜質濃度埋層會自動摻入到低摻入雜質的磊晶層中,因而導致N井區 阻值飄高的問題發生,上述此兩個方法都已成功驗證在現行生產線的 產品上,進而解決該半導體廠淺溝槽隔離製程所衍生的缺陷問題。

# 参考文獻

- 1. Data presented by H. Iwai in the Short Course Program of the Sixth Symposium on Nano DeviceTechnology (SNDT) (1999) •

- 2. D. Nag, IEDM Tech. Dig. (1996) 841 °

- 3. M. Nandakumar, IEDM Tech. Dig. (1997) 657 •

- 4. S. Lee, SSDM Dig. (1997) 524 °

- 5. K. Saino, K. Okonogi, S. Horiba, M. Sakao, M. Komuro, Y. Takaishi, T. Sakoh, K. Yoshida, K. Koyama, IEDM(1998)149 °

- 5. G. Badenes, R. Rooyackers, E. Augendre, E. Vandamme, C. Perello, N. Heylen, J. Grillaert, L. Deferm, J. Electrochem. Soc. 147 (10) (2000) 3827 °

- 7. Y.B. Park, J.Y. Kim, D.W. Seo, W.G. Lee, J. Electrochem. Soc. 148 (10) (2001) 572 °

- 8. N. Balasubramanian, E. Johnson, J. Vac. Sci. Technol. B 18 (2) (2002) 700 °

- 9. H. Park, K.B. Kim, C.K. Hong, U.I. Chung, M.Y. Lee, Jap. J. Appl. Phys. 37 (1998) 5849 °

- 10. J.K. Lan, C.G. Chao, Y.L. Cheng, Y.L. Wang, C.W. Liu, K.-Y. Lo, J. Vac. Sci. Technol. B21 (5) (2003) 2098 °

- 11. C. Stuer, J.V. Landuyt, H. Bender, I.D. Wolf, R. Rooyackers, G. Badenes, J. Electrochem. Soc. 148 (11) (2001) 597 °

- 12. T.K. Kim, D.H. Kim, J.K. Park, T.S. Park, Y.K. Park, H.J. Lee, K.Y. Lee, J.T. Kong, J.W. Park, IEDM (1998) 145 °

- 13. K.F. Dombrowski, A. Fischer, B. Dietrich, I.D. Wolf, H. Bender, S. Pochet, V. Simons, R. Rooyackers, G. Badenes, C. Stuer, J.V. Landuyt, IEDM (1999) 357 °

- 14. J.K. Lan, Y.L. Wang, C. P. Liu, W. H. Lee, Chyung Ay, Y. L. Cheng, S.C. Chang. Thin Solid Films 447-448(2004) 645-650 °

- 15. 林鴻志, NDL 奈米通訊, 奈米金氧半電晶體元件技術發展趨勢 (I)。

- 16. L. Peter, Semiconductor International, Vol-22, pp.69-75 (April, 1999) •

- 17. E. Korczynski, Solid-State Technol., 38, pp.63-73 (1996) •

- 18. J.-K. Lan et al. / Thin Solid Films 447 –448 (2004) 645–650 °

- 19. P. Ferreira, R-A. Bianchi, F. Guyader, R. Pantel and E. Granger, "Elimination of Stress Induced Silicon Defects in Very High-Density SRAM Structures," presented at the 31st European Solid-State Device Research Conference, September 2001 °

- 20. M. Nandakumar, A. Chatterjee, S. Sridhar, K. Joyner, M. Rodder, and I.-C. Chen, "Shallow Trench Isolation for Advanced ULSI CMOS Technologies," 1998 IEDM Tech. Digest, pp. 133 °

- 21. T. Speranza, Y. Wu, J. Wong, E. Fisch, J. Slinkman, and K. Beyer, "Manufacturing Optimization of Shallow Trench Isolation for Advanced CMOS Logic Technology," presented at 12th Annual IEEE/SEMI Advanced Semiconductor Manufacturing Conference (ASMC) 2001 °

- 21. C. S. Olsen, F. Nouri, M. Rubin, O. Laparra and G. Scott, "Stress Minimization of Corner Rounding Process during STI," presented at SPIE Conference on Microelectronic Device Technology III,

September 1999, Volume 3881, p. 215 °

- 22. 儀科中心簡訊 77 期

- 23. http://140.114.18.41/micro/chap4/4-3.htm