Home Search Collections Journals About Contact us My IOPscience

InAs High Electron Mobility Transistors with Buried Gate for Ultralow-Power-Consumption Low-Noise Amplifier Application

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2008 Jpn. J. Appl. Phys. 47 7119

(http://iopscience.iop.org/1347-4065/47/9R/7119)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 140.113.38.11

This content was downloaded on 25/04/2014 at 15:09

Please note that terms and conditions apply.

©2008 The Japan Society of Applied Physics

## InAs High Electron Mobility Transistors with Buried Gate for Ultralow-Power-Consumption Low-Noise Amplifier Application

Chien-I Kuo, Heng-Tung Hsu<sup>1</sup>, Edward Yi Chang, Yasuyuki Miyamoto<sup>2</sup>, and Wen-Chung Tsern

Department of Materials Science and Engineering, National Chiao-Tung University, Hsinchu, Taiwan 30010, R.O.C.

(Received March 19, 2008; accepted May 13, 2008; published online September 12, 2008)

An InAs/In<sub>0.7</sub>Ga<sub>0.3</sub>As composite channel high-electron-mobility transistor (HEMT) fabricated using the gate sinking technique was realized for ultralow-power-consumption low-noise application. The device has a very high transconductance of 1900 mS/mm at a drain voltage of 0.5 V. The saturated drain–source current of the device is 1066 mA/mm. A current gain cutoff frequency ( $f_{\rm T}$ ) of 113 GHz and a maximum oscillation frequency ( $f_{\rm max}$ ) of 110 GHz were achieved at only drain bias voltage  $V_{\rm ds} = 0.1$  V. The 0.08 × 40 µm<sup>2</sup> device demonstrated a minimum noise figure of 0.82 dB and a 14 dB associated gain at 17 GHz with 1.14 mW DC power consumption. [DOI: 10.1143/JJAP.47.7119]

KEYWORDS: InAs/InGaAs, gate sinking, current gain cutoff frequency ( $f_T$ ), ultralow power

Low-noise amplifiers (LNAs) with extremely low DC power consumption have always been considered as critical components for various emerging wireless communication applications including mobile radio systems and handheld imagers. Among all the possible technologies that meet the stringent system requirements, high-indium-content InP-based InAlAs/In<sub>1-x</sub>Ga<sub>x</sub>As high electron mobility transistors (HEMTs) are particularly promising because they provide higher electron mobility, higher saturation velocity, and higher sheet electron densities which lead to incomparable speed-power device performance with competing technologies such as GaAs HEMTs.  $^{1-3}$ )

In general, high electron mobility and conductivity are essential for devices to have high drive currents at both low drain ( $I_{\rm DLIN}$ ) and high drain ( $I_{\rm DSAT}$ ) biases, which are very critical to maintain excellent RF performance with extremely low DC power consumption.<sup>4,5)</sup> In the effort of minimizing noise figure of devices, several approaches have been adopted, as described in the references. Since noise figure is directly related to the gate length ( $L_{\rm g}$ ) and gate resistance ( $R_{\rm g}$ ), reduction of these two parameters has been the principle in achieving extremely low noise figure of devices. While reduction of gate length seems to be a good approach, the limitation of such an approach lies mainly in the degradation of performance caused by the short channel effect. Thus, care must be taken in obtaining the optimum physical parameters of devices for such applications.<sup>2)</sup>

Pt-based gate sinking technology has been widely applied in the fabrication of HEMTs since it provides a promising solution that enables vertical scaling of gate-to-channel distance without increasing access resistance. On the other hand, the short-channel effect can also be minimized. <sup>6,7)</sup> Another advantage of using a Pt-based structure is the relatively larger Schottky barrier height, which in turn suppresses gate leakage current. <sup>8)</sup> In this study, we developed 80 nm gate InAs/In<sub>0.7</sub>Ga<sub>0.3</sub>As composite channel HEMTs using the Pt-buried gate technique with excellent DC and RF performances for ultralow-power low-noise applications.

In the HEMT structure,  $In_xAl_{1-x}As$  was used as the buffer layer, which was grown by the molecular beam epitaxy (MBE) method on a 2-in. InP substrate. The epitaxial structure of the device is shown in Fig. 1. The following

process flow describes the sequence of device fabrication. The active area of the device was isolated by wet chemical mesa etching. After that, the 3 µm source-drain (S-D) spacing ohmic contacts were formed by evaporating Au/Ge/ Ni/Au on a heavily doped n-InGaAs cap layer and then alloyed at 250 °C using rapid thermal annealing (RTA) system. The contact resistance and sheet resistance measured using the transmission line model (TLM) were 0.021 Ω·mm and  $37.4 \Omega/\Box$ , respectively. To process the T-shaped gate, the 50 kV JEOL electron beam lithography system (JBX 6000 FS) of 100 pA beam current was used with a conventional trilayer e-beam resist consisting of ZEP-520/PMGI/ ZEP-520. After gate recess, the Pt (12 nm)/Ti (60 nm)/ Pt (80 nm)/Au (180 nm) were deposited as Schottky gate metal and lifted off using a ZDMAC remover (ZEON) to form a 80 nm T-shaped gate. Devices were passivated with 1000 Å silicon nitride film by plasma-enhanced chemical vapor deposition (PECVD). Finally, thermal annealing at 250 °C for 3 min in forming gas ambient was performed for gate sinking to further recess the channel. The access resistance increased from  $0.021 \Omega \cdot mm$  to  $0.032 \Omega \cdot mm$ during gate sinking, the change was negligible and the characteristics of the device did not degrade.

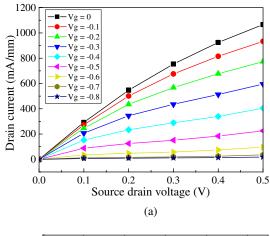

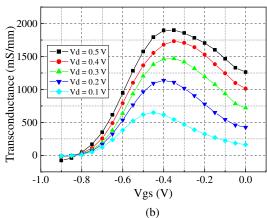

The drain–source current  $I_{\rm ds}$  versus drain–source voltage  $V_{\rm ds}$  curves and the dc transconductance  $(g_{\rm m})$  versus gate voltage at different  $V_{\rm ds}$  values of the 80 nm gate,  $2\times20\,\mu{\rm m}^2$  width InAs/In<sub>0.7</sub>Ga<sub>0.3</sub>As composite channel HEMT with gate sinking are shown in Figs. 2(a) and 2(b), respectively. The device exhibits a very high drain current density (1066 mA/mm), which is mainly attributed to a very low contact resistance and the superior electron mobility in the InAs channel.

Additionally, very high  $g_{\rm m}$  values at low drain voltages were achieved due to the reduction of distance between the gate and the channel resulting from the gate sinking process. A peak of  $g_{\rm m}$  1900 mS/mm at  $V_{\rm ds}=0.5$  V was observed. Care must be taken in the biasing of such devices with a very small energy bandgap since the impact ionization phenomenon would occur at a high drain bias level, which in turn causes serious performance degradation. S-parameter measurement was performed from 5 to 80 GHz using a Cascade Microtech on-wafer probing system with a vector network analyzer, and a standard load-reflection-reflection-match

<sup>&</sup>lt;sup>1</sup>Department of Communications Engineering, Yuan Ze University, Chungli, Taiwan 32003, R.O.C.

<sup>&</sup>lt;sup>2</sup>Department of Physical Electrons, Tokyo Institute of Technology, O-okayama, Meguro-ku, Tokyo 152-8552, Japan

| n+ Cap     | InGaAs, $x = 0.53$ | 35 nm, 2x10 <sup>18</sup> |

|------------|--------------------|---------------------------|

| Etch stop  | InP                | 4 nm                      |

| Barrier    | InAlAs, $x = 0.52$ | 10 nm                     |

| δ-doping   | Si                 | 5x10 <sup>12</sup>        |

| Spacer     | InAlAs, $x = 0.52$ | 4 nm                      |

| subchannel | InGaAs, $x = 0.7$  | 2 nm                      |

| Channel    | InAs               | 5 nm                      |

| subchannel | InGaAs, $x = 0.7$  | 3 nm                      |

| Buffer     | InAlAs, $x = 0.52$ | 500 nm                    |

## 2-in. S.I. InP Substrate

Fig. 1. (Color online) Epitaxial structure of the InAs HEMT device.

Fig. 2. (Color online) (a) The drain–source current  $I_{\rm ds}$  vs drain–source voltage  $V_{\rm ds}$  curves and (b) the dc transconductance  $(g_{\rm m})$  versus gate voltage curves at different  $V_{\rm ds}$ , the device size is  $80\,{\rm nm}\times40\,{\rm \mu m}$  with gate sinking.

(LRRM) calibration method was used to calibrate the measurement system. The reference plane of calibration was set at the tips of the probes. To accurately evaluate the performance of the intrinsic device, the parasitic effects due to the probing pads were carefully de-embedded from the measured S-parameters using the same method as that described in ref. 9 and the equivalent circuit model describ-

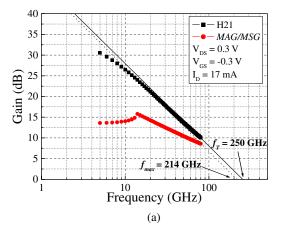

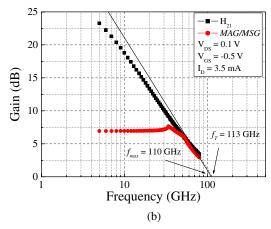

Fig. 3. (Color online) Maximum frequency of oscillation  $(f_{\rm max})$  and corresponding cutoff frequency  $f_{\rm T}$  of  $80\,{\rm nm}\times40\,{\rm \mu m}$  device at different drain biases.

ed in ref. 10. The maximum frequency of oscillation  $f_{\rm max}$  of a  $2 \times 20 \, \mu {\rm m}^2$  device peaked at 214 GHz, at gate and drain bias of -0.3 and  $0.3 \, {\rm V}$ , respectively [see Fig. 3(a)]. The corresponding cutoff frequency  $f_{\rm T}$  at this bias point was 250 GHz.

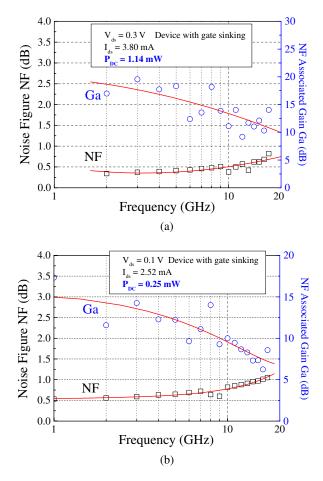

In evaluating the devices for ultralow-DC-power-consumption applications, the devices were biased at 0.1 V and the RF performance of the devices was characterized. As shown in Fig. 3(b), a reasonable  $f_T/f_{max}$  of 113/110 GHz was achieved at low bias levels. The total DC power consumptions were 5.10 and 0.35 mW when biased at peak  $f_{\rm T}$  and  $f_{\rm max}$ , respectively. These excellent RF performances resulted from reduced gate-to-channel distance by the gate sinking process. This reduction of gate-to-channel distance through gate sinking tends to suppress the short-channel effect and enhances the overshooting in electron velocity. The noise performances at different drain voltage biases are shown in Figs. 4(a) and 4(b) with the frequency range from 1 to 17 GHz under optimum bias conditions. The measured minimum noise figures (NF<sub>min</sub>) at 17 GHz were 0.82 and 1.05 dB for  $V_{\rm ds} = 0.3$  and 0.1 V, respectively; in addition, the corresponding associated gains ( $G_a$ ) were 14 and 8.6 dB, respectively.

In summary, the 80 nm T-gate InAs/In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs fabricated by Pt gate sinking were characterized for ultra-low-power low-noise applications. With the epitaxial structure of the device optimized, the reduction of gate-to-

Fig. 4. (Color online) Measured noise performance of device under various bias conditions (a) with  $V_{\rm ds}=0.3\,\rm V,~I_{\rm ds}=3.80\,\rm mA/mm$  and (b) with  $V_{\rm ds}=0.1\,\rm V,~I_{\rm ds}=2.52\,\rm mA/mm$ .

channel distance was achieved by the gate sinking process. The device exhibited a very high drain current density of  $1066 \,\mathrm{mA/mm}$  at  $V_{\rm ds} = 0.5 \,\mathrm{V}$ , with a maximum  $g_{\rm m}$  of  $1900 \,\mathrm{mS/mm}$ . It also exhibited an  $f_{\rm T}$  of  $113 \,\mathrm{GHz}$  and an

$f_{\rm max}$  up to 110 GHz at  $V_{\rm ds}=0.1$  V. Measured noise performance revealed that the devices had a very low noise figure of 1.05 dB with an 8.6 dB associated gain at 17 GHz with only 0.25 mW DC power consumption. These state-of-the-art results demonstrate the potential of InAs HEMT for ultra-low-power and low-noise applications.

## Acknowledgments

The authors would like to acknowledge the assistance and support of the National Science Council, and the Ministry of Economic Affairs, Taiwan, R.O.C., under the contracts NSC 96-2752-E-009-001-PAE and 95-EC-17-A-05-S1-020. Part of this work was supported by the "Nanotechnology Network Project" of the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan.

- J. B. Boos, W. Kruppa, B. R. Bennett, D. Park, S. W. Kirchoefer, R. Bass, and H. B. Dietrich: IEEE Trans. Electron Devices 45 (1998) 1869

- K. Shinohara, P. S. Chen, J. Bergman, H. Hazemi, B. Brar, I. Watanabe, T. Matsui, Y. Yamashita, A. Endoh, K. Hikosaka, T. Mimura, and S. Hiyamizu: Proc. IEEE Microwave Symp., Dig., 2006, p. 337.

- 3) K.-S. Seo and D.-H. Kim: Proc. 18th Int. Conf. InP and Related Materials, 2006, p. 30.

- R. Chau, S. Datta, and A. Majumdar: IEEE Compound Semiconductor Integrated Circuit Symp., 2005, p. 17.

- Y. Yamashita, A. Endoh, K. Shinohara, K. Hikosaka, T. Matsui, T. Mimura, and S. Hiyamizu: IEEE Electron Device Lett. 23 (2002) 573.

- K. J. Chen, T. Enoki, K. Arai, and M. Yamamoto: IEEE Trans. Electron Devices 43 (1996) 252.

- 7) K. Shinohara, W. Ha, M. J. W. Rodwell, and B. Brar: Proc. 19th Int. Conf. InP and Related Materials, 2007, p. 18.

- L. H. Chu, E. Y. Chang, L. Chang, Y. H. Wu, S. H. Chen, H. T. Hsu, T. L. Lee, Y. C. Lien, and C. Y. Chang: IEEE Electron Device Lett. 28 (2007) 82.

- Y. Yamashita, A. Endoh, K. Shinohara, M. Higashiwaki, K. Hikosaka, T. Mimura, S. Hiyamizu, and T. Matsui: IEEE Electron Device Lett. 22 (2001) 367.

- G. Dambrine, A. Cappy, F. Heliodore, and E. Playez: IEEE Trans. Microwave Theory Tech. 36 (1988) 1151.