# Method for Extracting Gate-Voltage-Dependent Source Injection Resistance of Modified Schottky Barrier (MSB) MOSFETs

Bing-Yue Tsui, Senior Member, IEEE, Chi-Pei Lu, Student Member, IEEE, and Hsiao-Han Liu

Abstract—The modified Schottky barrier (MSB) MOSFET with low-resistance metal source/drain and good short-channel effect immunity is one of the promising nanoscale device structures. In this letter, a modified external load resistance method was proposed to extract the bias-dependent source injection resistance of the MSB MOSFET for the first time. The effect of the thermal budget of the MSB process on the source injection resistance is reported. The injection resistance is exponentially proportional to  $(V_{\rm GS}-V_{\rm th}-0.5V_{\rm DS})$  and would be close to the source/drain resistance of conventional MOSFETs at high gate bias. This work provides a good method to directly evaluate the efficiency of the MSB junction.

Index Terms—Carrier injection, implantation-to-silicide (ITS), modified Schottky barrier (MSB), multigate FET (MuGFET).

#### I. Introduction

THE SCHOTTKY barrier (SB) MOSFET is one of the candidates for future nanoscale devices because of its easy processing, ultrashallow junction, and low source/drain (S/D) external resistance compared to the conventional p-n junction MOSFETs [1]-[5]. Recently, modified SB (MSB) MOSFETs have been proposed to improve the driving current and reserve the advantages of SB MOSFETs. The MSB junction is a Schottky junction with a very thin but high doping concentration layer located at silicide/Si-channel interface, which not only drastically improves driving capability by reducing and thinning the SB at source junction but also can significantly suppress the OFF-state leakage due to the thick SB at the drain junction. The MSB junction can be accomplished by either the implantation-to-silicide (ITS) method or the dopant segregation method [6], [7]. Several researches have been devoted to evaluate the efficiency of the MSB junction. Zhang et al. reported that the effective Schottky barrier height can be reduced to about 0.1 eV at high gate bias [8]. Kinoshita et al. reported the carrier injection velocity enhance-

Manuscript received March 7, 2008; revised June 8, 2008. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC-95-2221-E-009-302-MY3. The review of this letter was arranged by Editor X. Zhou.

The authors are with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: bytsui@cc.nctu.edu.tw).

Digital Object Identifier 10.1109/LED.2008.2001478

ment associated with the velocity overshoot [9]. It has been also reported that the current transport mechanism of SB and MSB MOSFETs may change from thermionic emission and tunneling to drift diffusion as the gate bias increases [10]. The gate bias for transport mechanism change decreases with the increase of the thermal budget for MSB junction formation. However, the source injection resistance and its gate bias dependence have not been reported. In this work, a modified external loading method is proposed to extract the bias-dependent S/D resistance. The bias-dependent source injection resistance of MSB MOSFETs provides a good indicator to evaluate the efficiency of the MSB junction and would be useful for device and circuit simulation.

### II. DEVICE FABRICATION

Fully depleted n-channel SOI MSB MOSFETs fabricated by the ITS technique are used in this work. The process flow of an MSB MOSFET has been previously described in detail [11]. Therefore, we list some important process and structure parameters here. The thicknesses of the Si active layer and buried oxide layer were 40 and 150 nm, respectively. A thick SiO<sub>2</sub> hard mask layer was deposited on the Si layer so that only sidewall channels could be conducted. A 3-nm-thick SiO<sub>2</sub> was thermally grown as the gate dielectric followed by a 150-nmthick poly-Si film deposition. The poly-Si gate was doped by  $P_{31}^+$  ion implantation at 40 keV to a dose of  $5 \times 10^{15}$  cm<sup>-2</sup> followed by a rapid thermal activation at 1025 °C for 10 s. Then, a  $SiO_2$  (10 nm)/ $Si_3N_4$  (20 nm) composite spacer was formed. The S/D region was completely converted into NiSi by a two-step annealing silicidation process. To form the MSB S/D junction,  $P_{31}^+$  ions were implanted into the nickel silicide (ITS) at 20 keV to a dose of  $5\times10^{15}~cm^{-2}$  followed by a post-ITS annealing step at 600 °C for 30 min or 30 s. During this annealing step, phosphorus ions diffused out of the silicide and piled up at the Si/silicide interface to form the MSB junction [11]. For the reference devices, phosphorus ions were implanted into the S/D region at 10 keV to a dose of  $5 \times$  $10^{15}$  cm<sup>-2</sup> followed by a rapid thermal activation at 1025 °C for 20 s before the Ni-salicide process. The silicide thickness is about 25 nm.

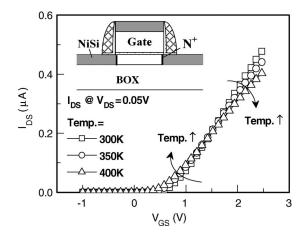

Fig. 1 shows the typical transfer characteristics of an MSB MOSFET with  $W/L=80~{\rm nm}/5~\mu{\rm m}$  biasing at  $V_{\rm DS}=0.05~{\rm V}$  and operating at different temperatures. The inset shows the

Fig. 1. Typical transfer characteristics of an MSB MOSFET with  $W/L=80~\rm nm/5~\mu m$  biasing at  $V_{\rm DS}=0.05~\rm V$  and operating at a different device temperature. The inset shows the device structure. The reversal of temperature dependence at  $V_{\rm GS}=1.35~\rm V$  indicates the change of current transport mechanism.

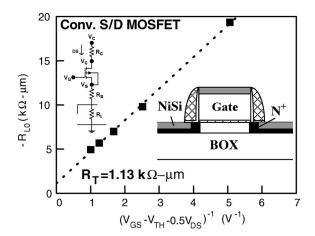

Fig. 2.  $-R_{\rm L0}$  versus  $1/(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  plot of the conventional MOSFET. The insets show the circuit diagram of the external loading method and the device structure. The  $V_{\rm DS}$  is 0.05 V.

schematic device structure. The on-state current increases with temperature, increasing at low  $V_{\rm GS}$ . While at high  $V_{\rm GS}$ , the temperature dependence is reversed, and the intersecting point occurs at about  $V_{\rm GS}=1.35$  V. This intersection indicates that the on current of the MSB MOSFET is dominated by a thermionic emission mechanism or a tunneling mechanism at low gate bias [10].

#### III. MODIFIED EXTERNAL LOADING METHOD

The external loading method was proposed to extract the S/D resistance of the MOSFET by Hsu [12]. The benefit of this method is that only one device is measured, and the extracted result is exactly the S/D resistance of the measured device. The inset in Fig. 2 shows the circuit diagram of this method. An external load resistor with a suitable range of impedance is connected to the source terminal. The total resistance of the circuit is composed of external load resistance ( $R_{\rm L}$ ), source resistance ( $R_{\rm S}$ ), drain resistance ( $R_{\rm D}$ ), and channel resistance,

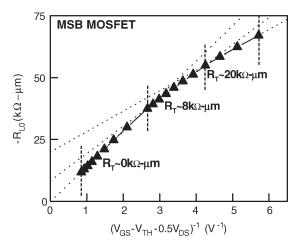

Fig. 3.  $-R_{\rm L0}$  versus  $1/(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  plot of the MSB MOSFET with W/L=80 nm/5  $\mu$ m obtained by the modified external loading method. The  $V_{\rm DS}$  is 0.05 V, and the post-ITS annealing time is 30 min.

where  $R_{\rm S}$  and  $R_{\rm D}$  depend on the properties of the MSB junction. The channel current  $(I_{\rm DS})$  of the MOSFET operating at a linear region is given by

$$\begin{split} I_{\rm DS} &= \frac{W}{L} \mu C_{\rm ox} \left( V_{\rm GS}' - V_{\rm TH} - \frac{1}{2} V_{\rm DS}' \right) V_{\rm DS}' \\ &= K \bigg\{ \left[ V_{\rm GS} - I_{\rm DS} (R_{\rm S} + R_{\rm L}) - V_{\rm TH} \right] \\ &- \frac{1}{2} \left[ V_{\rm DS} - I_{\rm DS} (R_{\rm S} + R_{\rm D} + R_{\rm L}) \right] \bigg\} \\ &\times \left[ V_{\rm DS} - I_{\rm DS} (R_{\rm S} + R_{\rm D} + R_{\rm L}) \right] \end{split}$$

where  $K=(W/L)\mu C_{\rm ox},~W$  is the channel width, L is the channel length,  $\mu$  is carrier mobility, and  $C_{\rm ox}$  is gate capacitance. This equation models the intrinsic channel property and is independent of the S/D junction. After some manipulations, this equation becomes

$$\frac{1}{I_{\rm DS}} = \frac{R_{\rm T} + R_{\rm L}}{V_{\rm DS}} + \frac{1}{K \left(V_{\rm GS} - V_{\rm TH} - \frac{1}{2}V_{\rm DS}\right)V_{\rm DS}}$$

(1)

where  $R_{\rm T}=R_{\rm S}+R_{\rm D}$ , and  $R_{\rm T}$  represents the total external resistance of this MOSFET. Then, by plotting  $1/I_{\rm DS}$  versus  $R_{\rm L}$  with  $V_{\rm GS}$  as a parameter, the x-axis intersection  $R_{\rm L0}$  could be expressed as

$$-R_{\rm L0}(V_{\rm GS}) = R_{\rm T} + K^{-1} \left( V_{\rm GS} - V_{\rm TH} - \frac{1}{2} V_{\rm DS} \right)^{-1}$$

. (2)

By plotting  $-R_{\rm L0}$  versus  $1/(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$ , the y-axis intersection gives  $R_{\rm T}$ .

The  $-R_{\rm L0}$  versus  $1/(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  plot of the MOSFET with a conventional S/D junction is shown in Fig. 2, where the  $V_{\rm DS}$  is 0.05 V. The good linearity as predicted by (2) confirms that the external loading method can be applied to SOI devices well. However, Fig. 3 shows that when using

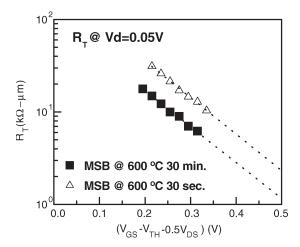

Fig. 4. Extracted  $R_{\rm T}$  as a function of the  $(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  of the MSB MOSFET with W/L=80 nm/5  $\mu$ m. The  $V_{\rm DS}$  is 0.05 V.

this method to the MSB MOSFET, the nonlinear  $-R_{\rm L0}$  versus  $1/(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  plot deviates from (1). This difference arises from that the  $R_{\rm T}$  of the MSB MOSFET is dependent on the bias condition, which conflicts with the basic assumption of the external loading method.

To solve this problem, we assume that  $R_{\rm T}$  can be treated as a constant in a small  $\Delta V_G$  range  $(V_{\rm GX} \pm \Delta V_G/2)$ . The x-axis intersection of the  $-R_{L0}$  versus  $1/(V_{GS} - V_{TH} - 0.5V_{DS})$  plot extracted at  $V_{\rm GS} = V_{\rm GX} - \Delta V_G/2$ ,  $V_{\rm GX}$ , and  $V_{\rm GX} + \Delta V_G/2$ could be explained as the  $R_{\rm T}$  at  $V_{\rm GX}$ . Consequently, the bias dependence of  $R_{\rm T}$  can be obtained by repeating this procedure. Fig. 4 shows the extracted  $R_{\rm T}$  of the MSB MOSFET with 30-min and 30-s post-ITS annealing as a function of  $(V_{\rm GS}$  –  $V_{\rm TH} - 0.5 V_{\rm DS}$ ), where the  $V_{\rm DS}$  is 0.05 V. It is observed that the  $R_{\rm T}$  is exponentially proportional to the bias condition of  $(V_{\rm GS} - V_{\rm TH} - 0.5V_{\rm DS})$ . This is reasonable because the S/D resistance is dominated by the effective SB height at the source side, and the effective SB height is linearly proportional to  $V_{\rm GS}$ in the measured  $V_{\rm GS}$  range [8]. The  $R_{\rm T}$  of the device with 30-min post-ITS annealing is much lower than that with 30-sec post-ITS annealing. This result indicates that a sufficient thermal budget is required to form an efficient MSB junction. Extrapolating  $R_{\rm T}$  to  $(V_{\rm GS} - V_{\rm TH} - 0.5 V_{\rm DS}) = 0.5 \text{ V}, R_T$  is 1.17  $K\Omega - \mu m$  and is very close to that of the conventional MOSFET. It should be noted that as the device is biased at the ON state, the effect of MSB at the drain side is much smaller than the MSB at the source side. Therefore, the decrease of  $R_{\rm T}$  is mainly attributed to the decrease of the source injection resistance.

#### IV. CONCLUSION

In this letter, a modified external load resistance method has been proposed to extract the bias-dependent source injection resistance of the MSB MOSFET. It is observed that the source injection resistance is exponentially proportional to  $(V_{\rm GS}-V_{\rm TH}-0.5V_{\rm DS})$  and the S/D resistance of the MSB MOSFET would be close to that of the conventional MOSFET at moderate high gate bias. Without a sufficient post-ITS thermal budget, the source injection resistance cannot be effectively suppressed at reasonable  $V_{\rm GS}$ . This work provides a good method to directly evaluate the efficiency of the MSB junction.

## ACKNOWLEDGMENT

The devices were fabricated at the Nano Facility Center of National Chiao Tung University and the National Nano Device Laboratory.

#### REFERENCES

- [1] J. P. Synder, C. R. Helms, and Y. Nishi, "Experimental investigation of a PtSi source and drain field emission transistor," *Appl. Phys. Lett.*, vol. 67, no. 10, pp. 1420–1422, Sep. 1995.

- [2] J. R. Tucker, "Schottky barrier MOSFETs for silicon nanoelectronics," in *Proc. IEEE Front. Electron.*, 1997, pp. 97–100.

- [3] M. Nishisaka and T. Asano, "Reduction of the floating body effect in SOI MOSFETs by using Schottky source/drain contacts," *Jpn. J. Appl. Phys. 1, Regul. Rap. Short Notes*, vol. 37, no. 3B, pp. 1295–1299, 1998.

- [4] C. Wang, J. P. Synder, and J. R. Tucker, "Sub-40 nm PtSi Schottky source/drain metal-oxide-semiconductor field-effect transistors," *Appl. Phys. Lett.*, vol. 74, no. 8, pp. 1174–1176, Feb. 1999.

- [5] W. Saitoh, S. Yamagami, A. Itoh, and M. Asada, "35 nm metal gate p-type metal oxide semiconductor field-effect transistor with PtSi Schottky source/drain on separation by implanted oxygen substrate," *Jpn. J. Appl. Phys.*, vol. 38, no. 6A/B, pp. L629–L631, 1999.

- [6] B.-Y. Tsui and C.-P. Lin, "A novel 25-nm modified Schottky-barrier FinFET with high performance," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 430–432, Jun. 2004.

- [7] A. Kinoshita, Y. Tsuchiya, A. Yagishita, K. Uchida, and J. Koga, "Solution for high-performance Schottky-source/drain MOSFETs: Schottky barrier height engineering with dopant segregation technique," in *VLSI Symp. Tech. Dig.*, 2004, pp. 168–169.

- [8] M. Zhang, J. Knoch, Q. T. Zhao, A. Fox, S. St. Lenk, and S. Mantl, "Low temperature measurements of Schottky-barrier SOI-MOSFETs with dopant segregation," *Electron. Lett.*, vol. 41, no. 19, pp. 1085–1086, Sep. 2005.

- [9] A. Kinoshita, T. Kinoshita, Y. Nishi, K. Uchida, S. Toriyama, R. Hasumi, and J. Koga, "Comprehensive study on injection velocity enhancement in dopant-segregated Schottky MOSFETs," in *IEDM Tech. Dig.*, 2006, pp. 79–82.

- [10] B. Y. Tsui and C. P. Lu, "Current transport mechanisms of Schottky barrier and modified Schottky barrier MOSFETs," in *Proc. 37th ESSDERC*, 2007, pp. 307–310.

- [11] B.-Y. Tsui and C. P. Lin, "Process and characteristics of modified Schottky barrier (MSB) p-channel FinFETs," *IEEE Trans. Electron Devices*, vol. 52, no. 11, pp. 2455–2462, Nov. 2005.

- [12] S. T. Hsu, "A simple method to determine series resistance and k factor of an MOS field effect transistor," RCA Rev., vol. 44, pp. 424–429, Sep. 1983.