This article was downloaded by: [National Chiao Tung University 國立交通大學]

On: 26 April 2014, At: 00:46 Publisher: Taylor & Francis

Informa Ltd Registered in England and Wales Registered Number: 1072954 Registered

office: Mortimer House, 37-41 Mortimer Street, London W1T 3JH, UK

### **Ferroelectrics**

Publication details, including instructions for authors and subscription information:

http://www.tandfonline.com/loi/gfer20

## Preparation and Properties of Perovskite Thin Films for Resistive Nonvolatile Memory Applications

Chun-Hung Lai <sup>a</sup> & Tseung-Yuen Tseng <sup>b c</sup>

$^{\rm a}$  Department of Electronic Engineering , National United University , Miaoli, 360, Taiwan

<sup>b</sup> Department of Electronics Engineering , National Chiao Tung University , Hsinchu, 300, Taiwan

<sup>c</sup> National Taipei University of Technology, Taipei, 106, Taiwan Published online: 07 Nov 2007.

To cite this article: Chun-Hung Lai & Tseung-Yuen Tseng (2007) Preparation and Properties of Perovskite Thin Films for Resistive Nonvolatile Memory Applications, Ferroelectrics, 357:1, 17-27, DOI: 10.1080/00150190701527381

To link to this article: <a href="http://dx.doi.org/10.1080/00150190701527381">http://dx.doi.org/10.1080/00150190701527381</a>

#### PLEASE SCROLL DOWN FOR ARTICLE

Taylor & Francis makes every effort to ensure the accuracy of all the information (the "Content") contained in the publications on our platform. However, Taylor & Francis, our agents, and our licensors make no representations or warranties whatsoever as to the accuracy, completeness, or suitability for any purpose of the Content. Any opinions and views expressed in this publication are the opinions and views of the authors, and are not the views of or endorsed by Taylor & Francis. The accuracy of the Content should not be relied upon and should be independently verified with primary sources of information. Taylor and Francis shall not be liable for any losses, actions, claims, proceedings, demands, costs, expenses, damages, and other liabilities whatsoever or howsoever caused arising directly or indirectly in connection with, in relation to or arising out of the use of the Content.

This article may be used for research, teaching, and private study purposes. Any substantial or systematic reproduction, redistribution, reselling, loan, sub-licensing, systematic supply, or distribution in any form to anyone is expressly forbidden. Terms & Conditions of access and use can be found at <a href="http://www.tandfonline.com/page/terms-and-conditions">http://www.tandfonline.com/page/terms-and-conditions</a>

Ferroelectrics, 357:17–27, 2007 Copyright © Taylor & Francis Group, LLC ISSN: 0015-0193 print / 1563-5112 online DOI: 10.1080/00150190701527381

# Preparation and Properties of Perovskite Thin Films for Resistive Nonvolatile Memory Applications

#### CHUN-HUNG LAI1 AND TSEUNG-YUEN TSENG2,\*

<sup>1</sup>Department of Electronic Engineering, National United University, Miaoli 360, Taiwan

<sup>2</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan; National Taipei University of Technology, Taipei 106, Taiwan

Various perovskite structure electroceramic thin films have been studied for semiconductor memory applications. The high permittivity and ferroelectric remanent polarization properties of these materials give the promise of a new generation of advanced dynamic and/or nonvolatile memory devices. The recent study indicates that perovskite oxide showing bistable resistance switching behavior is a highly promising candidate for nonvolatile semiconductor device, the so-called resistance random access memory (RRAM). RRAMs exhibit sufficiently fast switching capability and low operation voltages as compared with flash memory, and bring about the current upsurge in research. This paper summarizes the fabrication and characterization of these potential materials, and provides a broad view of the current status and future trends for perovskite oxides-based RRAMs. The associated conduction mechanisms are also discussed with specific examples from recent literature.

**Keywords** PRAM; perovskite thin film; electrical property; resistance switching

#### 1. Introduction

The inherent property of drastically reduced power consumption makes nonvolatile memory (NVM) a highly promising candidate for energy-saving semiconductor device. The key feature of the two-terminal NVM is the ability to switch the resistance of the system simply by applying a voltage or current pulse. The resistance of the device is then measured by a small bias voltage, which does not significantly perturb the state, and if the system is disconnected from the electronic circuit, the resistance can remain stable. The requirements for ideal memories include the followings: 1) Speed: shorter program, erase, and switching time, 2) Power: smaller switching voltage and appropriate high/low operating current, 3) Reliability: longer data retention and cycling endurance (under voltage and/or thermal stress), 4) Integration: lower processing temperature and compatibility with semiconductor fabrication process, and 5) Cost: simple structure and fewer mask steps. Recently, new nonvolatile memory devices such as polymer random access memory (RAM) [1], magnetic RAM [2], flash memory [3], ferroelectric RAM [4], and resistance RAM (RRAM) [5]

Table 1

Nonvolatile memory at a glance (after Ref. [6])

| Parameter                                        | Flash<br>(production)                                        | Ferroel-<br>ectric<br>RAM   | Magnetore-<br>sistive<br>RAM | Ovonic<br>Unified<br>Memory                    |

|--------------------------------------------------|--------------------------------------------------------------|-----------------------------|------------------------------|------------------------------------------------|

| Largest array built, Mb <sup>a</sup>             | 256                                                          | 64                          | 1                            | 4                                              |

| Cell size factor <sup>b</sup>                    | 8–10                                                         | 18                          | 10-20                        | 5–8                                            |

| Endurance, cycles                                | $10^{6}$                                                     | $10^{16}$                   | $10^{14}$                    | $10^{12}$                                      |

| Read/write voltages, V                           | 2/12                                                         | 1.5/1.5                     | 3.3/3.3                      | 0.4/1                                          |

| Read/write speeds, ns                            | 20/1000                                                      | 40/40                       | 50/50                        | 50/50                                          |

| Extra mask steps<br>needed to<br>embed<br>memory | 6–8                                                          | 2                           | 4                            | 3–4                                            |

| In production                                    | Yes                                                          | Yes                         | 2004                         | $2005^{c}$                                     |

| Some major players                               | • AMD • Intel                                                | <ul> <li>Fujitsu</li> </ul> | • IBM                        | • BAE                                          |

|                                                  | <ul> <li>Semiconductor</li> </ul>                            | <ul> <li>Ramtron</li> </ul> | <ul> <li>Infineon</li> </ul> | <ul><li>Intel</li></ul>                        |

|                                                  | Storage Technology                                           | <ul> <li>Samsung</li> </ul> | <ul> <li>Motorola</li> </ul> | <ul><li>Ovonyx</li></ul>                       |

|                                                  | <ul><li>Sharp • Toshiba</li><li>STMicroelectronics</li></ul> | • Texas<br>Instruments      |                              | • STMicroelectronics<br>• Samsung <sup>c</sup> |

$<sup>^{</sup>a}1Mb = 1024 \text{ by } 1024 \text{ bits.}$

have been extensively investigated for future memory device applications Table 1. lists parameters for several NVM technologies [6].

The RRAM is composed of a simple sandwich of a functional oxide layer with two conductive electrodes. Baek et al. has demonstrated the RRAM test vehicle to be fully integrated based on 0.18  $\mu$ m CMOS technology [7]. For scalability reasons, resistive information storage concepts have the higher potential compared to charge based storage concepts. Since the first observation of bistable resistance states in the 1960's, a great amount of effort has been exerted to elucidate the switching mechanism. Recently, dielectric perovskite type oxides have attracted increasing attention as candidates for new era NVM storage media [5, 8, 9]. This paper reviews the process and electrical characteristics of two promising perovskite oxides materials for RRAM applications,  $Pr_{1-x}Ca_xMnO_3$  manganites (PCMO) and doped strontium titanates  $SrTiO_3$  (STO)/ strontium zirconates  $SrZrO_3$  (SZO).

#### 2. PCMO

Perovskite manganites  $ReAMnO_3$  (Re = rare earth ions, A = alkaline ions), have been the subject for intense studies due to their unusual electronic and magnetic properties, such as colossal magnetoresistance (CMR) and colossal electroresistance (CER) effects. Among the

<sup>&</sup>lt;sup>b</sup>In multiples of the square of interconnect width on the chips lowest metal level.

<sup>&</sup>lt;sup>c</sup> modified by author.

various CMR manganites,  $Pr_{1-x}Ca_xMnO_3$  (PCMO) attracts considerable attention because PCMO films show an electric-pulse-induced resistance (EPIR) change effect under electric field pulsing without an applied magnetic field at room temperature [9]. The observed EPIR effect is reversible and pulse polarity dependent, which is very promising for its easy fabrication, fast switching speed (<100 ns), high density, and low power consuming [10]. In addition to describing the fabrication and properties of PCMO films for RRAM use, we introduce several models for CER effect in the following section and discuss the main disputes about the switching mechanism proposed, i.e., which one is the dominant factor responsible for the resistance switching phenomenon-bulk vs. the interface between the electrode and the film.

#### 2.1. Preparation and EPIR Properties

Pr<sub>1-x</sub>Ca<sub>x</sub>MnO<sub>3</sub> is unique in that it exhibits insulating behavior over the whole composition (x) range, and in the insulating paramagnetic state with x = 0.3-0.5 at room temperature [11, 12]. No changes in resistivity are observed even under magnetic fields of up to 8 T or applied voltage of up to 1000 V on bulk samples [13, 14]. Several research groups have studied the resistance switching behaviors of PCMO films. With YBa<sub>2</sub>Cu<sub>3</sub>O<sub>7</sub> or Pt as bottom electrode and Ag as top electrode, Liu et al. prepared Pr<sub>0.7</sub>Ca<sub>0.3</sub>MnO<sub>3</sub> film by pulsed laser deposition (PLD) on LaAlO3 substrates and found a new EPIR change effect in the CMR oxide at room temperature and under zero magnetic field [9]. It was observed that the resistance of the PCMO film (thickness  $\sim$ 600 nm) could either be decreased or increased (more than 1700%) according to the pulse polarity (above a threshold 5 V approximately). The resistance change also depended on the pulse magnitude, the pulse number, and the sample resistance change history. Aoyama et al. likewise adopted PLD technique to grow similar thin films on (001) SrTiO<sub>3</sub> substrates (with x = 0.5 and a typical thickness  $\sim 200$ nm) using Au and Al as electrodes [15]. A similar nonvolatile, reversible change in the reflectance of the light seemed to give the evidence that the EPIR effect was caused by the bulk properties, although the role of electrodes was not examined and the current-voltage (I-V) characteristics were not shown. Odagawa et al. [16] deposited the polycrystalline PCMO film on Pt/MgO substrate (x = 0.3 and  $\sim 150$  nm) by rf-magnetron sputtering technique with an evaporated Ag top electrode. The I-V measurements using dc and pulsed biases were conducted. They exhibited pronounced hysteretic and asymmetric behaviors. The dc bias range was about from 1.0 V to -2.0 V, and the amplitude of applying pulses was  $\pm 15$ V. The switching direction of high- to low-resistance state in the positive-voltage region was the same with the polarity required for the EPIR effect. The hysteresis induced a CER of more than 5000% at maximum and the effect tended to be suppressed with increasing biased voltage. The CER ratio was kept constant from dc to voltage pulses as short as 150 ns. The conduction current extending five orders of magnitude was well described via the trap-controlled space-charge-limited (SCL) mechanism.

#### 2.2. Metal-Oxide Interfaces

Baikalov et al. pointed out that the above interpretation of resistance switch to be attributed to bulk properties of PCMO has an apparent conflict with the reported bulk resistivity [17]. They developed multi-leads configuration to measure both the interfacial and bulk resistances of the samples, i.e., both the PCMO sandwiches and single layer PCMO strips. The experimental data confirmed the speculation that contribution from PCMO should be less than a few percent of the observed resistance changes. Additionally, they performed

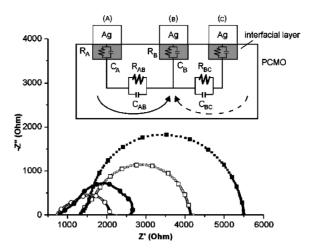

**Figure 1.** Impedance spectra for a PCMO thin-film strip across either A/B or B/C. Open and closed symbols represent the on and off states, respectively (after Ref. [17]).

impedance spectroscopy to separate individual component resistance, based on the assumption of different RC time constants. Measurements spanned a frequency range of  $0.1~\rm Hz$  to  $20~\rm MHz$ , one would expect the spectrum reach the Z' axis at a left end point with a resistance corresponding to the bulk portion of the sample, As shown in Fig. 1, the Z' segments between the origin and the high frequency intercept are unaffected by the switching, which is a further indication of the nearly unchanged bulk contribution in both conduction states. With the help of properly measuring the capacitance of the interface, they also estimated the interface layer is no thicker than  $10~\rm nm$ . As for the carrier transport, a field-created crystalline defect (a field-induced electrochemical migration) mechanism is proposed to explain the thermionic emission limited conduction (TELC) in the lower voltage regime and SCLC behavior in the higher regime.

Sawa et al. investigated the effects of several top electrodes such as Pt, Au, Ag, and Ti by characterizing the vertical transport properties of epitaxial layered structures [18]. In order to extract the voltage drop, the I-V characteristics were measured by a threepoint contact method with the use of separate current and voltage contacts for the bottom electrode. They ascribed the rectifying interface to the presence of a Schottky contact, in which PCMO was considered as a p-type semiconductor. According to a p-type Schottky contact model, the resultant barrier height due to different work function of metal electrodes explained the observed contact resistance variations consistently. To account for the almost same work function of  $\sim$ 4.3 eV for Ag and Ti but apparently distinct resistance switch for Ti, they considered Ti as a getter for oxygen. The high density of interface states induced by the oxygen vacancies could cause a large degree of band bending, as compared with the Ag/PCMO interface. The resistance switching was then interpreted as a consequence of a modification of a Schottky-like barrier width and/or height. Kim also explained the electrode dependence of EPIR switching effects by metal work function [19] and Shang el al. claimed that the hysteresis and asymmetry in the I-V curves are due to trapping/ detrapping process of hole carriers exponentially distributed in energy [20].

The hysteretic I–V properties at an epitaxial oxide junction SrRuO<sub>3</sub> / Sr(Ti,Nb)O<sub>3</sub> [21] and at a few nanometer thick active layers of chemically compatible materials combination SmCaMnO<sub>3</sub> / LaSrMnO<sub>3</sub> [22] further support the elucidation of the interface effect to be the origin of resistance switch. The concept of utilizing an insulator as a buffer layer between

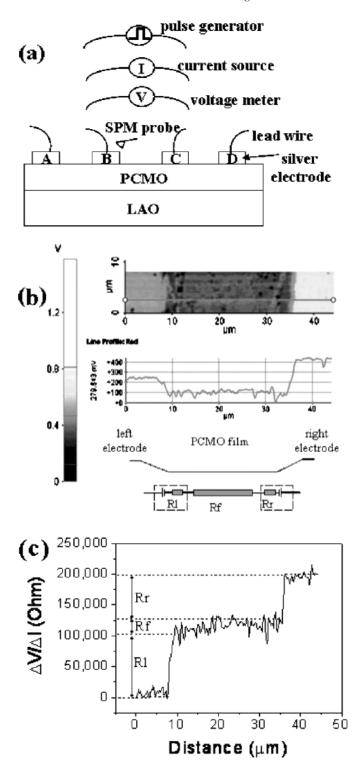

PCMO and top electrode was adopted by Chen et al. to significantly reduce the pulse voltage needed to switch the device and enhance the resistance switch ratio [23]. This observation also provides insight into optimization for possible application and enhancement of the device performance as memories in terms of atomic scale interface engineering. Tokunaga et al. had their experiments based on a strain-free and clean surface to avoid the lattice mismatch between films and substrates [24]. Chen et al. showed direct resistance profile through measurements of the sample surface potential by scanning Kelvin probe microscopy (SKPM) [25]. Figure 2 shows the SKPM experiment schematic, device surface potential with current from right to left, and the resultant resistance ( $\Delta V/\Delta I$ ) as a function of distance. They have found that about 98% of the resistance switching occurred in the interface regions within a width of about 1–3  $\mu$ m of the electrical contact surface.

#### 3. Doped SrTiO<sub>3</sub>/ SrZrO<sub>3</sub>

The ABO<sub>3</sub> perovskites are a valuable set of oxides. For instance, (Ba,Sr)TiO<sub>3</sub> (BST) is an important oxide for use as a dielectric in the storage capacitors of dynamic random access memories because of its high dielectric constant and low loss. The ferroelectric perovskite Pb(Zr,Ti)O<sub>3</sub> (PZT) is of interest as nonvolatile memory such as the ferroelectric random access memory (FeRAM) and optoelectronic memory. One of the focused materials in this section, SrTiO<sub>3</sub> (STO), has been developed as a substrate candidate for the high temperature superconductors. The possibility of epitaxial growth on Si(100) makes STO act as a gate dielectric. This opens up the possibility of field effect transistors (FETs) with functional gate oxides with ferroelectric, superconducting, or magneto-resistive properties.

Stoichiometric STO is a typical insulator with a wide energy gap of 3.2 eV. Treatment by Nb or La addition or in oxygen deficiency, i.e., in reducing atmosphere, will make STO a n-type semiconductor. Ever since the discovery of electric field induced resistance change and reproducible switching effect in doped STO film, there starts an upsurge in research on nonvolatile two-terminal RRAMs for next generation electronic applications.

#### 3.1. Electrical Properties

Beck et al. research group reported experimental results of the resistive switching behavior of Cr-doped SrZrO<sub>3</sub> (SZO:Cr) films epitaxially grown on STO single crystal substrates by PLD [5]. Doped with 0.2% Cr and sandwiched between a SrRuO<sub>3</sub> (SRO) bottom electrode and an Au top electrode, the metal-insulator-metal (MIM) capacitor-like structure was investigated by voltage pulse and dc-sweep scan. The important parameters for the I–V characteristics in their findings are described below and compared with those for PCMO, including 1) the switching direction and voltage (V<sub>SW</sub>) and 2) the resistance switch ratio and data retention. We list these comparisons in Table 2.

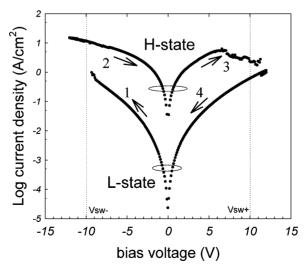

The switching behavior leads to a pronounced hysteretic I–V characteristic with two different resistance states. Electrical properties are characterized by the following operation conditions: stable intrinsic memory effect of I–V within  $\pm 0.5$  V, write and erase voltages of  $\pm 1.1$  V, and EPIR switching with pulses of  $\pm 5$  V, all of which fall into the range comparable to the threshold voltage for PCMO. In view of the high price of STO single crystal substrate, small deposition scale of PLD and incompatibility with Si processing, Liu et al. [8] and Park et al. [26] revealed the feasibility of SZO:Cr film for a commercial memory device. Liu et al. prepared their SZO:Cr films by rf-magnetron sputter on LaNiO<sub>3</sub> (LNO) bottom electrode and SiO<sub>2</sub>-Si substrate, which is applicable to commercial high-density RRAM devices. Even the SZO:V RRAM by sol-gel method was reported [27]. Figure 3 shows the

**Figure 2.** The direct scanning Kelvin probe microscopy (SKPM) observation of resistance switching on the Ag-PCMO-Ag device (after Ref. [25]). (See Color Plate I)

| companied of reasonable attentions controlled and all of the |                    |                    |  |  |

|--------------------------------------------------------------|--------------------|--------------------|--|--|

| Parameter                                                    | PCMO [19, 20]      | SZO/STO [26,33]    |  |  |

| Switching voltage V <sub>sw</sub>                            | 2–4 V              | 2.5 V              |  |  |

| Resistance switch ratio                                      | <1000              | >1000              |  |  |

| Endurance, cycles                                            | 1000               | 1000               |  |  |

| Data retention at 85°C                                       | 1600 min           | 1800 sec           |  |  |

| Switching direction <sup>a</sup>                             | L-state to H-state | H-state to L-state |  |  |

| Multi-bit storage <sup>b</sup>                               | YES                | YES                |  |  |

| Symmetric I–V                                                | YES                | NO                 |  |  |

| Stability <sup>c</sup>                                       | L-state better     | H-state better     |  |  |

Table 2

Comparison of resistance switching behaviors between PCMO and SZO/STO

current density versus bias voltage for SZO:V device, from which one can see the switching voltage higher than  $\pm 10$  V. Recently, Park et al. successfully lowered  $V_{SW}$  to  $\pm 2.5$  V for sputter-deposited SZO film on Si substrate by using the off-axis rf sputtering technique, in which a perpendicular arrangement between the substrate and the target was set to reduce the re-sputtering effects and create a clean surface between SZO:Cr thin film and electrode layer.

Obviously an almost symmetric I–V curve was obtained for SZO RRAM, unlike that of PCMO. Here "symmetric" means the observed  $V_{\rm SW+} \approx V_{\rm SW-}$  as well as the similar trend in the current variation and therefore the resistance ratio in both sweep directions, although different techniques and materials are adopted for the bottom and top electrodes preparation of the MIM structure. The arrows in Fig. 3 denote the switching direction at  $V_{\rm SW-}$  Depicted in semi-log scale for I–V data and at voltage sweep  $0 \rightarrow V_{\rm SW-} \rightarrow 0 \rightarrow V_{\rm SW+} \rightarrow 0$ , the resistance switch for SZO:V is obtained in a clockwise way, i.e., the current increases suddenly at the switching voltage  $V_{\rm SW-}$  and the film enters into its high current state

Figure 3. Typical curve of current density J versus bias voltage V for SZO:Cr film.

<sup>&</sup>lt;sup>a</sup>Polarity-dependent state switching at Vsw+, or positive EPIR switch.

<sup>&</sup>lt;sup>b</sup>Or multi-level switching ability.

<sup>&</sup>lt;sup>c</sup>In terms of shorter pulse width needed for EPIR switch, or longer data retention under thermal stress.

(H-state). The switching direction is therefore contrary to that of PCMO. As for the resistance switch ratio, the apparently larger value of 10<sup>5</sup> near the I–V origin for SZO was reported [8].

By tuning appropriately the write pulses voltage levels, four distinct and equidistant resistance or current levels were demonstrated to show the possibility of two bits of information stored in such a simple device [5]. Somewhat similar visually but different indeed the phenomenon of current variations under sequential switching pulses, called "soft errors", was often observed under EPIR endurance cycling with equal pulse amplitude [28]. This unintentionally caused state with middle resistance value compared to H- and L-state may lead to the uncertain data identification, or storage of bit information in error.

Reversible bistable behavior is obtained after an electroforming process, i.e., a high voltage, typically a value larger than the switching voltage, should be applied first to the as-deposited and/or post-annealed SZO films. Our tests show that no successful forming process is ever found for positive sweep direction, that is to say, the resistive switching nature is only achieved for negative forming voltage at which the sample is in H-state. The speculation of the more stable H-state than L-state may explain the experimental results of 1) retention after thermal stress and 2) the pulse width required for EPIR effect. For 1), we apply a prior treatment of 150°C for 1.5 h, in N<sub>2</sub> ambient under 1-atm pressure to prevent Al top-electrode oxidation, and then observe the I-V data variations. Compared with the slightly changed H-state, the L-state current drops closely to that of unformed condition (the initial state). It would need longer heating duration or higher temperature for H-state to restore to initial state [29]. The observation that conduction in H-state is more immune to thermal disturbance is consistent with the retention behavior found in conducting spots by atomic force microscopy (AFM) [30]. Up to now, we can say that the hysteretic current-voltage characteristics are formed and/or switched electrically, and can be restored thermally. For 2), by considering the various film preparing conditions and tuning the applied pulse amplitude, a negative pulse width of a few tens ns to hundreds ns is needed for the  $L\rightarrow H$  transition typically. The pulse height is specifically larger than the switching voltage, say, a fixed value at +15 V and -15V in our case. However, a much longer duration of a few tens  $\mu$ s to hundreds  $\mu$ s is required for the H $\rightarrow$ L transition. The different transition times for the switching between the two conduction states were also indicated by Liu [8]. Note that despite of different electrode materials, the resultant difference in the pulse duration required is up to three orders of magnitude. Rohde et al. found that the required power was the most dominant parameter for successful switching [31]. Estimated from the current levels for L- and H- states near  $V_{SW}$  in Fig. 3 and with the same pulse amplitude  $V_p$ , we have obviously the much lower power  $P = i \times V_p$  and therefore the significantly less energy  $E = P \times \Delta t$  required for the L $\rightarrow$ H transition compared with that for H $\rightarrow$ L transition. This relatively stable conduction nature for H-state may serve to explain the frequently observed I-V jiggle at V<sub>SW+</sub>. The relative stability between two states was also found in other RRAM branch. Sawa commented that the L-state is much more stable than the H-state for PCMO [18], and Kim observed intermediate R states and anomalous R fluctuations between R states during the resistive switching from L- to H-state for NiO films [32].

#### 3.2. Possible Mechanisms

Similar to that of PCMO, the origin of resistance switch and carrier conduction mechanism can be classified into two categories, the bulk effect vs. the interface effect. Beck ruled out the existence of metallic filaments, ferroelectricity, and the crystalline-amorphous phase transformation in the SZO:Cr single crystal film. He suggested the charge-transfer processes

via donor and acceptor levels (Cr<sup>3+</sup> and Cr<sup>4+</sup>) to be a plausible mechanism for carrier creation and transport within the insulator [5]. Rossel utilized the electron-beam-induced current (EBIC) imaging technique to examine the distribution of electrical current [5]. The distribution and intensity of the current, appearing as bright spots in EBIC images, change with the resistance switch. This result seems to be consistent with the AFM studies for TiO<sub>2</sub> [30], in which the resistance switch is closely related to the formation and elimination of conducting spots. The difference in point defect density generated by the applied bias field leads to the resistance switch. Lin et al. also found a more complicated and power consuming process during the H- to L-state switching in their sputtered SZO:V film and proposed this "off" process was due to ruptured current paths when the bulk defects randomly trapped electrons [33].

Sim et al. investigated single crystal STO:Nb with excellent switching characteristics and ascribed resistance switch to the modulation of Schottky barrier height by charge trapping at the interface [34]. Likewise, Choi et al. analyzed non-stoichiometric polycrystalline STO and verified that the sharp resistance switching takes place at the metal-oxide interface [35].

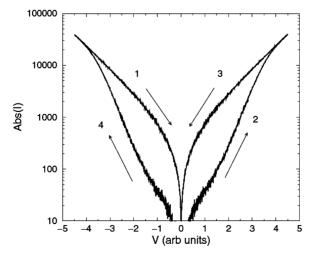

Up to now, the inferences or conclusions mentioned above appear to provide good explanation to each of their own observed phenomena, although there exists some disputes between them. Some reported brilliant research works are highlighted below. Rozenberg introduced a basic theoretical model to simulate three essential RRAM behaviors, namely, hysteresis, resistance switch, and retention [10]. The resulting I–V hysteresis is shown in Fig. 4, in spite of the switching direction inconsistent with that in Fig. 3. Gu performed a numerical simulation to investigate the electric-field-induced metal-insulator transition in doped manganites and found an important impact of the intrinsic inhomogeneities on this transition [36]. Hsu pointed out that the nonvolatile resistance change is neither an interface effect nor due to field induced electro-chemical migration [37]. By examining PCMO with different crystalline structure via MOD/PVD/PLD process, Hsu proposed a current driven process to be responsible for the EPIR increase and a field driven process for the EPIR decrease. Hamaguchi believed perovskite manganite is not a special compound for EPIR effect, or rather an universally observed phenomenon in transition-metal-oxide thin films

Figure 4. Simulated I–V characteristic showing an hysteresis cycle (after Ref. [10]).

[38]. He suggested the resistance switch is not dominated by a detailed electronic structure of each sample, but by a more general origin, e.g., crystalline defect. Fisher emphasized the influence of non-negligible temperature increment caused by Joule heating while performing the dc I–V measurements [39]. Compared with pulsed measurements, the widely used dc I–V ones are usually misleading. This argument may account for those *ad hoc* interpretations based on the misleading dc measured I–V hysteresis information.

#### 4. Summary

This brief review makes a description of the main advances for perovskite PCMO and STO/SZO RRAMs, and lists the debate on the mechanism about current conduction and switching in-between the bistable states. Both materials are appropriate for advanced NVM devices. Further experiments are needed to better understand the underlying physics if any direct correlation of dielectric behavior and conduction transport exists inside bulks. Attributed to the advancement of thin film synthesis technology and the need for energy-saving device, perovskite oxides will remain as a fertile field of research and development, full of application potential and rich in science.

#### References

- 1. Li. Ma, S. Pyo, J. Ouyang, Q. Xu, and Y. Yang, Appl. Phys. Lett. 82, 1419 (2003).

- 2. D. C. Worledge and D. W. Abraham, Appl. Phys. Lett. 82, 4522 (2003).

- 3. S. Choi, M. Cho, H. Hwang, and J. Kim, J. Appl. Phys. 94, 5408 (2003).

- 4. H. T. Lue, C. J. Wu, and T. Y. Tseng, IEEE Tran. on Electron Devices 49, 1790 (2002).

- A. Beck, J. G. Bednorz, Ch. Gerber, C. Rossel, and D. Widmer, *Appl. Phys. Lett.* 77, 139 (2000).

Y. Watanabe, J. G. Bednorz, A. Bietsch, Ch. Gerber, D. Widmer, and A. Beck, *Appl. Phys. Lett.* 78, 3738 (2001).

C. Rossel, G. I. Meijer, D. Brémaud, and D. Widmer, *J. Appl. Phys.* 90, 2892 (2001).

- 6. L. Geppert, IEEE Spectrum March, 48 (2003)

- I. G. Baek, M. S. Lee, S. Seo, M. J. Lee, D. H. Seo, D.-S. Suh, J. C. Park, S. O. Park, H. S. Kim, I. K. Yoo, U-In Chung, and J. T. Moon, *IEDM Tech. Dig.* 587 (2004)

- 8. C. Y. Liu, P. H. Wu, A. Wang, W. Y. Jang, J. C. Young, K. Y. Chiu, and T. Y. Tseng, *IEEE Electron Device Lett.* **26**, 351 (2005).

- 9. S. Q. Liu, N. J. Wu, and A. Ignatiev, Appl. Phys. Lett. 76, 2479 (2000).

- 10. M. J. Rozenberg, I. H. Inoue, and M. J. Sánchez, Phys. Rev. Lett. 92, 178302 (2004).

- Y. Tomioka, A. Asamitsu, H. Kuwahara, Y. Moritomo, and Y. Tokura, *Phys. Rev.* B 53, R1689 (1995).

- 12. H. Yoshizawa, H. Kawano, Y. Tomioka, and Y. Tokura, *Phys. Rev.* B **52**, R13145 (1995).

- 13. S. K. Singh, S. B. Palmer, D. M. Paul, and M. R. Lees, Appl. Phys. Lett. 69, 263 (1996).

- 14. A. Asamitsu, Y. Tomioka, H. Kuwahara, and Y. Tokura, *Nature (London)* 388, 50 (1997).

- 15. K. Aoyama, K. Waku, A. Asanuma, Y. Uesu, and T. Katsufuji, Appl. Phys. Lett. 85, 1208 (2004).

- A. Odagawa, H. Sato, I. H. Inoue, H. Akoh, M. Kawasaki, Y. Tokura, T. Kanno, and H. Adachi, *Phys. Rev.* B 70, 224403 (2004).

- A. Baikalov, Y. Q. Wang, B. Shen, B. Lorenz, S. Tsui, Y. Y. Sun, and Y. Y. Xue, *Appl. Phys. Lett.* 83, 957 (2003);

S. Tsui, A. Baikalov, J. Cmaidalka, Y. Y. Sun, Y. Q. Wang, Y. Y. Xue, C. W. Chu, L. Chen, and A. J. Jacobson, *ibid.* 85, 317 (2004).

- 18. A. Sawa, T. Fujii, M. Kawasaki, and Y. Tokura, Appl. Phys. Lett. 85, 4073 (2004).

- 19. C. J. Kim, B. I. Kim, and I. Chen, Jap. J. Appl. Phys. 44, 1260 (2005).

- D. S. Shang, Q. Wang, L. D. Chen, R. Dong, X. M. Li, and W. Q. Zhang, *Phys. Rev. B* 73, 245427 (2006).

- T. Fujii, M. Kawasaki, A. Sawa, H. Akoh, Y. Kawazoe, and Y. Tokura, *Appl. Phys. Lett.* 86, 12107 (2005).

- 22. A. Sawa, T. Fujii, M. Kawasaki, and Y. Tokura, Appl. Phys. Lett. 88, 232112 (2006).

- 23. X. Chen, N. Wu, and A. Ignatiev, IEDM Tech. Dig. 125 (2005).

- Y. Tokunaga, Y. Kaneko, J. P. He, T. Arima, A. Sawa, T. Fujii, M. Kawasaki, and Y. Tokura, *Appl. Phys. Lett.* 88, 223507 (2006).

- 25. X. Chen, N. J. Wu, J. Strozier, and A. Ignatiev, Appl. Phys. Lett. 87, 233506 (2005).

- 26. J. Park, J.-W. Park, M. K. Yang, K. Jung, D. Kim, and J. Lee, J. Val. Sci. Tech. A 24, 4, 907 (2006).

- C. Y. Liu, C. C. Chuang, J. S. Chen, A. Wang, W. Y. Jang, J. C. Young, K. Y. Chiu, and T. Y. Tseng, *Thin Solid Films* 494, 287 (2006).

- 28. C. Y. Lin, C. Y. Liu, C. C. Lin, and T. Y. Tseng, J. Electroceramics (in the press).

- 29. C. Y. Liu, A. Wang, W. Y. Jang, and T. Y. Tseng, J. Phys. D: Appl. Phys. 39, 1156 (2006).

- 30. B. J. Choi, D. S. Jeong, and S. K. Kim, J. Appl. Phy. 98, 33715 (2005).

- C. Rohde, B. J. Choi, D. S. Jeong, S. Choi, J. S. Zhao, and C. S. Hwang, *Appl. Phys. Lett.* 86, 262907 (2005).

- D. C. Kim, S. Seo, S. E. Ahn, D.-S. Suh, M. J. Lee, B.-H. Park, I. K. Yoo, I. G. Baek, H.-J. Kim, E. K. Yim, J. E. Lee, S. O. Park, H. S. Kim, U-In Chung, J. T. Moon, and B. I. Ryu, *Appl. Phys. Lett.* 88, 202102 (2006).

- C. C. Lin, B. C. Tu, C. C. Lin, C. H. Lin, and T. Y. Tseng, *IEEE Electron Device Lett*. (in the press).

- 34. H. Sim, H. Choi, D. Lee, M. Chang, D. Choi, Y. Son, E. H. Lee, W. Kim, Y. Park, I. K. Yoo, and Hyunsang Hwang, *IEDM Tech. Dig.* 758 (2005).

- 35. D. Choi, D. Lee, H. Sim, M. Chang, and H. Hwang, Appl. Phys. Lett. 88, 82904 (2006).

- 36. R. Y. Gu, Z. D. Wang, and C. S. Ting, Phys. Rev. B 67, 153101 (2003).

- 37. S. T. Hsu, W. W. Zhuang, T. K. Li, and W. Pan, IEDM Tech. Dig. 121 (2005).

- 38. M. Hamaguchi, K. Aoyama, S. Asanuma, and Y. Uesu, Appl. Phys. Lett. 88, 142508 (2006).

- B. Fisher, J. Genossar, K. B. Chashka, L. Patlagan, and G. M. Reisner, *Appl. Phys. Lett.* 88, 152103 (2006).