# High-Performance Metal-Induced Laterally Crystallized Polycrystalline Silicon P-Channel Thin-Film Transistor With TaN/HfO<sub>2</sub> Gate Stack Structure

Ming-Wen Ma, *Student Member, IEEE*, Tien-Sheng Chao, *Senior Member, IEEE*, Chun-Jung Su, *Student Member, IEEE*, Woei-Cherng Wu, *Student Member, IEEE*, Kuo-Hsing Kao, and Tan-Fu Lei, *Member, IEEE*

Abstract—In this letter, high-performance low-temperature poly-Si p-channel thin-film transistor with metal-induced lateral-crystallization (MILC) channel layer and TaN/HfO $_2$  gate stack is demonstrated for the first time. The devices of low threshold voltage  $V_{\rm TH}\sim 0.095~\rm V$ , excellent subthreshold swing S.S.  $\sim 83~\rm mV/dec.$ , and high field-effect mobility  $\mu_{\rm FE}\sim 240~\rm cm^2/V\cdot s$  are achieved without any defect passivation methods. These significant improvements are due to the MILC channel film and the very high gate-capacitance density provided by HfO $_2$  gate dielectric with the effective oxide thickness of 5.12 nm.

Index Terms—High- $\kappa$ , low-temperature poly-Si thin-film transistor (LTPS-TFT), metal gate, metal-induced lateral crystallization (MILC).

#### I. INTRODUCTION

**▼** IGH-PERFORMANCE low-temperature poly-Si thinfilm transistors (LTPS-TFTs) have been intensively investigated for the application of the active matrix liquid-phase crystal displays [1] and the three-dimensional (3-D) circuitintegration elements such as SRAMs and DRAMs [2], [3]. However, the poly-Si channel film would still have many grain boundaries which degrade the subthreshold swing S.S., threshold voltage  $V_{\rm TH}$ , and field-effect mobility  $\mu_{\rm FE}$  and the results in a large operation voltage [4]-[6]. Hydrogen-related plasma is generally used to passivate these grain boundaries in the poly-Si channel film to have a lower operation voltage of LTPS-TFTs [7]–[9]. Nevertheless, the introduction of hydrogen would also result in the degradation of the reliability of LTPS-TFTs [10], [11]. Recently, high- $\kappa$  materials such as HfSiO<sub>x</sub>, HfO<sub>2</sub>, LaAlO<sub>3</sub>, and Al<sub>2</sub>O<sub>3</sub> have been used as the gate dielectrics of LTPS-TFTs to enhance the gate-capacitance density, resulting in the improvement of the S.S. and  $V_{\rm TH}$  without any hydrogenrelated plasma treatments [12]–[15].

Manuscript received January 19, 2008; revised March 5, 2008. This work was supported by the National Science Council, Taiwan, R.O.C., under Contract NSC-96-2221-E-009-189. The review of this letter was arranged by Editor J. Sin.

M.-W. Ma, C.-J. Su, and T.-F. Lei are with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C.

T.-S. Chao, W.-C. Wu, and K.-H. Kao are with the Institute and Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C (e-mail: tschao@mail.nctu.edu.tw).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2008.921208

The improvement of S.S.,  $V_{\rm TH}$ , and  $\mu_{\rm FE}$  of the devices with high- $\kappa$  gate dielectrics is still not high enough for the application of system-on-panel (SOP) or 3-D circuit integration. Compared with solid-phase-crystallization (SPC) method, excimer laser crystallization (ELC) method is capable of producing poly-Si film with low defect densities and higher  $\mu_{\rm FE}$  [16]. However, ELC suffers from high initial cost and high process complexity. Metal-induced lateral-crystallization (MILC) method is another batch process with low cost to achieve high  $\mu_{\rm FE}$  of LTPS-TFTs due to its large grain size and longitudinal grain boundaries [17]–[21].

In this letter, we demonstrate the p-channel LTPS-TFT with TaN gate, HfO $_2$  gate dielectric, and MILC poly-Si channel film. High-performance LTPS-TFTs of very low  $V_{\rm TH}$ , excellent S.S., and very high  $\mu_{\rm FE}$  can be obtained, which are very promising for the realization of SOP and 3-D circuit integration.

# II. EXPERIMENTAL PROCEDURE

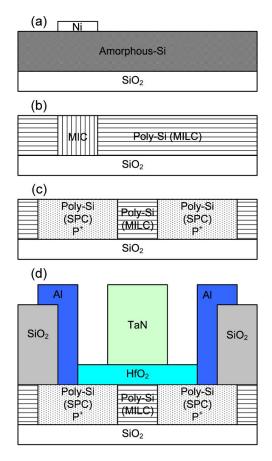

The fabrication of devices started by depositing a 50-nm undoped amorphous Si ( $\alpha$ -Si) layer at 550 °C in a low-pressure chemical-vapor-deposition system on Si wafers capped with a 500-nm thermal oxide layer. A 5-nm Ni was deposited by an electron-beam evaporation system at room temperature and patterned by a lift-off process as a seed layer to crystallize the  $\alpha$ -Si, as shown in Fig. 1(a). Lee et al. and Wong et al. have shown that a very thin thickness of Ni within 5 nm is enough for MILC process [17]–[21]. Then, the 50-nm  $\alpha$ -Si layer was recrystallized by the MILC process at 550 °C for 24 h in a N<sub>2</sub> ambient, as shown in Fig. 1(b). After the residual Ni was removed by  $H_2SO_4 + H_2O_2$ , a 500-nm plasmaenhanced chemical-vapor-deposition oxide was deposited at 300 °C for device isolation. The device active region was formed by patterning and etching the isolation oxide. The source and drain (S/D) regions in the active device region were implanted with boron (10 keV at  $5 \times 10^{15}$  cm<sup>-2</sup>) and activated at 600 °C for 24-h annealing in a N2 ambient, as shown in Fig. 1(c). A 25-nm HfO<sub>2</sub> was deposited by an electron-beam evaporation system at room temperature. Then, 200-nm TaN gate electrode was deposited by sputter at room temperature and patterned by reactive ion etching. After the patterning of S/D contact holes, Al was deposited by thermal evaporation system

Fig. 1. Cross-sectional view and process flow of the  $TaN/HfO_2$  gate stack structure LTPS-TFT with MILC channel film.

as the gate and S/D contact pad. Finally, the TFT devices were completed by the contact pad definition. The cross-sectional view of the TaN/HfO<sub>2</sub> gate stack structure LTPS-TFT with MILC channel film was shown in Fig. 1(d).

The device with gate length (L) and width (W) of 2  $\mu$ m and 1  $\mu$ m, respectively, was measured. The  $V_{\rm TH}$  was defined as the  $V_G$  at which the drain-current reaches 100 nA  $\times$  W/L and  $V_{\rm DS}=0.1$  V. The  $\mu_{\rm FE}$  was extracted from the maximum transconductance  $(G_m)$ .

### III. RESULTS AND DISCUSSION

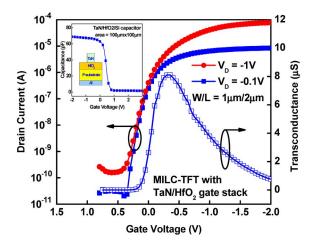

Fig. 2 shows the transfer characteristics  $(I_D-V_G \text{ and } G_m)$ of LTPS-TFT with TaN/HfO2 gate stack structure and MILC poly-Si channel film. A very low  $V_{\rm TH} (\sim 0.095 \text{ V})$  and ultrasharp subthreshold current curve is observed, which indicates an excellent S.S. (~83 mV/dec) that can be comparable with single crystalline silicon channel. A very high gate-capacitance density, which corresponds to a very low effective oxide thickness EOT  $\sim$ 5.12 nm, is obtained from the capacitance–voltage curve of TaN/HfO2 on a P-type single crystalline silicon substrate to extract the gate-capacitance density of TaN/HfO<sub>2</sub> LTPS-TFT, as shown in the inset in Fig. 2. Therefore, the high  $\mu_{\rm FE}~(\sim 240~{\rm cm^2/V\cdot s})$  can be calculated from the maximum  $G_m$ . The high-performance electrical characteristics of LTPS-TFT are attributed to both the low defect density of poly-Si channel film crystallized by MILC and high gate-capacitance density provided by high- $\kappa$  gate dielectric HfO<sub>2</sub>. Some impor-

Fig. 2. Transfer characteristics  $(I_D - V_G)$  and transconductance  $G_m$  of LTPS-TFT with TaN/HfO2 gate stack structure and MILC polycrystalline silicon channel film. The inserted figure is the C-V curve of TaN/HfO2 capacitor.

TABLE I IMPORTANT PARAMETERS OF THE TaN/HfO $_2$  Gate Stack Structure LTPS-TFT With MILC Channel Film. Other Works Are Also Listed for Comparison

|                                           | MILC<br>P-TFT<br>with<br>HfO <sub>2</sub> | MILC<br>P-TFT<br>with<br>SiO <sub>2</sub><br>[19] | SPC<br>P-TFT<br>with<br>HfSiO <sub>x</sub><br>[12] | SPC<br>P-TFT<br>with<br>SiO <sub>2</sub><br>[12] |

|-------------------------------------------|-------------------------------------------|---------------------------------------------------|----------------------------------------------------|--------------------------------------------------|

| W/L<br>(µm/µm)                            | 1/2                                       | 10/5                                              | 5/10                                               | 5/10                                             |

| V <sub>TH</sub> (V)                       | 0.095                                     | -4.2                                              | -0.91                                              | -6.85                                            |

| S.S. (V/decade)                           | 0.083                                     | 1.0                                               | 0.37                                               | 1.06                                             |

| EOT (nm)                                  | 5.12                                      | 100                                               | 25.5                                               | 46.5                                             |

| μ <sub>FE</sub><br>(cm <sup>2</sup> /V-s) | 240                                       | 98                                                | 27.45                                              | 15.82                                            |

| $I_{on}/I_{min}$                          | 4.09x10 <sup>5</sup>                      | 3.4x10 <sup>7</sup>                               | 4.12x10 <sup>6</sup>                               | 3.56x10 <sup>6</sup>                             |

tant electrical parameters of LTPS-TFT are listed in Table I and compared with other works. Compared with the conventional SPC TFT with thick SiO<sub>2</sub> gate dielectric, we can observe that the conventional MILC-TFT with thick SiO2 gate dielectric shows a significant improvement on  $\mu_{\rm FE}$ , as shown in Table I. It is due to the fact that the MILC channel film has low defect density in poly-Si [21]. However, the S.S. of conventional MILC-TFT is still too high to reduce the operation voltage of LTPS-TFT [17]–[21]. The replacement of thick SiO<sub>2</sub> gate dielectrics by high- $\kappa$  gate dielectrics can provide a large gatecapacitance density to attract more carriers with a smaller gate voltage to fill up the traps and lower the potential barrier height in the poly-Si channel film [22]. This makes the LTPS-TFTs turn on within several voltages, resulting in the reduction of the S.S. and the operation voltage. As shown in Table I, the  $V_{\mathrm{TH}}$  and S.S. can be obviously reduced without any hydrogenrelated plasma treatments, as high- $\kappa$  gate dielectrics are used. In addition, the mobility of TaN/HfO2 MILC-TFT is much larger than the conventional MILC-TFT. It can be attributed to the

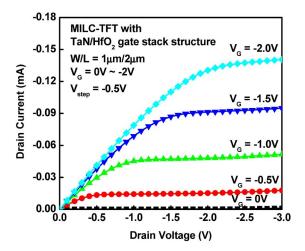

Fig. 3. Output characteristic  $I_D - V_D$  of MILC LTPS-TFT with TaN/HfO $_2$  gate stack structure.

small device's length and width that less grain boundaries exist in the channel film.

However, the drain leakage current of LTPS-TFT with TaN/HfO<sub>2</sub> gate stack structure and MILC poly-Si channel film is higher than conventional MILC and SPC LTPS-TFT, resulting in a degradation of the  $I_{\rm on}/I_{\rm min}$  current ratio. The high drain leakage current is attributed to the poor grain boundaries of SPC/MILC interface in S/D junction region, because the longitudinal grain boundaries of MILC channel film would not be continuous in the S/D junction region, which is activated by SPC. The SPC poly-Si has a columnar grain structure with grain boundaries that are randomly oriented with respect to the longitudinal grain boundaries of MILC channel film, resulting in poor grain boundaries of the S/D and channel interface. The process flow of S/D ion implantation before the MILC process may improve this drawback. However, the S/D ion implantation will affect the MILC length. The modified process of metalgate/high- $\kappa$  MILC TFT is under study.

Fig. 3 shows the output characteristic  $I_D$ – $V_D$  of MILC LTPS-TFT with TaN/HfO<sub>2</sub> gate stack structure and indicates a very high driving current within -2 V of gate and drain voltages. The high driving current would be very suitable for the application of SOP and 3-D circuit integration.

#### IV. CONCLUSION

The combination of high- $\kappa$  gate dielectric and MILC poly-Si channel film has been proposed for the first time. The p-channel LTPS-TFT with TaN/HfO<sub>2</sub> gate stack structure and MILC polycrystalline channel film can achieve high  $\mu_{\rm FE}$  (~240 cm²/V·s), low  $V_{\rm TH}$ (~0.095 V), and excellent S.S. (~83 mV/dec) simultaneously. The combination of TaN/HfO<sub>2</sub> gate stack structure and MILC poly-Si channel would be very promising for the application of SOP.

# ACKNOWLEDGMENT

The authors would like to thank the Nano Facility Center (NFC) of National Chiao Tung University and the National Nano Device Laboratory (NDL) for providing the process equipment.

#### REFERENCES

- [1] Y. Oana, "Current and future technology of low-temperature poly-Si TFT-LCDs," *J. Soc. Inf. Disp.*, vol. 9, no. 3, pp. 169–172, 2001.

- [2] F. Hayashi, H. Ohkubo, T. Takahashi, S. Horiba, K. Noda, T. Uchida, T. Shimizu, N. Sugawara, and S. Kumashiro, "A highly stable SRAM memory cell with top-gated P-N drain poly-Si TFTs for 1.5 V operation," in *IEDM Tech. Dig.*, 1996, pp. 283–286.

- [3] H. J. Cho, F. Nemati, P. B. Griffin, and J. D. Plummer, "A novel pillar DRAM cell for 4 Gbit and beyond," in VLSI Symp. Tech. Dig., 1998, pp. 38–39.

- [4] S.-D. Wang, W.-H. Lo, and T.-F. Lei, "CF<sub>4</sub> plasma treatment for fabricating high-performance and reliable solid-phase-crystallized poly-Si TFTs," *J. Electrochem. Soc.*, vol. 152, no. 9, pp. G703–G706, 2005.

- [5] C.-H. Tu, T.-C. Chang, P.-T. Liu, C.-H. Chen, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, L.-T. Chang, C.-C. Tsai, S. M. Sze, and C.-Y. Chang, "Electrical enhancement of solid phase crystallized poly-Si thin-film transistors with fluorine ion implantation," *J. Electrochem. Soc.*, vol. 153, no. 9, pp. G815–G818, 2006.

- [6] C.-H. Tu, T.-C. Chang, P.-T. Liu, H.-W. Zan, Y.-H. Tai, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, W.-R. Chen, and C.-Y. Chang, "Enhanced performance of poly-Si thin film transistors using fluorine ions implantation," *Electrochem. Solid State Lett.*, vol. 8, no. 9, pp. G246–G248, 2005.

- [7] T. Kamins and P. J. Marcoux, "Hydrogenation of transistors fabricated in polycrystalline-silicon films," *IEEE Electron Device Lett.*, vol. EDL-1, no. 8, pp. 159–161, Aug. 1980.

- [8] A. Mimura, N. Konishi, K. Ono, J.-I. Ohwada, Y. Hosokawa, Y. A. Ono, Y. Suzuki, K. Miyata, and H. Kawakami, "High performance low-temperature poly-Si n-channel TFTs for LCD," *IEEE Trans. Electron Devices*, vol. 36, no. 2, pp. 351–359, Feb. 1989.

- [9] I.-W. Wu, T.-Y. Huang, W. B. Jackson, A. G. Lewis, and A. C. Chiang, "Passivation kinetics of two types of defects in polysilicon TFT by plasma hydrogenation," *IEEE Electron Device Lett.*, vol. 12, no. 4, pp. 181–183, Apr. 1991.

- [10] S. Banerjee, R. Sundaresan, H. Shichijo, and S. Malhi, "Hot-electron degradation of n-channel polysilicon MOSFETs," *IEEE Trans. Electron Devices*, vol. 35, no. 2, pp. 152–157, Feb. 1988.

- [11] M. Hack, A. G. Lewis, and I.-W. Wu, "Physical models for degradation effects in polysilicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 40, no. 5, pp. 890–897, May 1993.

- [12] M.-J. Yang, C.-H. Chien, Y.-H. Lu, G.-L. Luo, S.-C. Chiu, C.-C. Lou, and T.-Y. Huang, "High-performance and low-temperature-compatible p-channel polycrystalline-silicon TFTs using hafnium-silicate gate dielectric," *IEEE Electron Device Lett.*, vol. 28, no. 10, pp. 902–904, Oct. 2007.

- [13] C.-P. Lin, B.-Y. Tsui, M.-J. Yang, R.-H. Huang, and C. H. Chien, "High-performance poly-silicon TFTs using HfO<sub>2</sub> gate dielectric," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 360–363, May 2006.

- [14] B. F. Hung, K. C. Chiang, C. C. Huang, A. Chin, and S. P. McAlister, "High-performance poly-silicon TFTs incorporating LaAlO<sub>3</sub> as the gate dielectric," *IEEE Electron Device Lett.*, vol. 26, no. 6, pp. 384–386, Jun. 2005.

- [15] Z. Jin, H. S. Kwok, and M. Wong, "High-performance polycrystalline SiGe thin-film transistors using Al<sub>2</sub>O<sub>3</sub> gate insulators," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 502–504, Dec. 1998.

- [16] C.-C. Tsai, H.-H. Chen, B.-T. Chen, and H.-C. Cheng, "High-performance self-aligned bottom-gate low-temperature poly-silicon thin-film transistors with excimer laser crystallization," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 599–602, Jul. 2007.

- [17] S.-W. Lee and S.-K. Joo, "Low temperature poly-Si thin-film transistor fabrication by metal-induced lateral crystallization," *IEEE Electron Device Lett.*, vol. 17, no. 4, pp. 160–162, Apr. 1996.

- [18] G. A. Bhat, Z. Jin, H. S. Kwok, and M. Wong, "Effects of longitudinal grain boundaries on the performance of MILC-TFTs," *IEEE Electron Device Lett.*, vol. 20, no. 2, pp. 97–99, Feb. 1999.

- [19] Z. Meng, M. Wang, and M. Wong, "High performance low temperature metal-induced unilaterally crystallized polycrystalline silicon thin film transistors for system-on-panel applications," *IEEE Trans. Electron Devices*, vol. 47, no. 2, pp. 404–409, Feb. 2000.

- [20] G. Bhat, H. Kwok, and M. Wong, "Plasma hydrogenation of metalinduced laterally crystallized thin film transistors," *IEEE Electron Device Lett.*, vol. 21, no. 2, pp. 73–75, Feb. 2000.

- [21] M. Wong, "Metal-induced laterally crystallized polycrystalline silicon: Technology, material and devices," *Proc. SPIE*, vol. 4079, pp. 28–42, 2000.

- [22] J. Y. W. Seto, "The electrical properties of polycrystalline silicon films," J. Appl. Phys., vol. 46, no. 12, pp. 5247–5254, Dec. 1975.