## 行政院國家科學委員會補助專題研究計畫成果報告

## 以智財元件為單元的系統晶片合成

計畫類別:個別型計畫

計畫編號: NSC 89 - 2215 - E - 009 - 073 -

執行期間:88年10月01日至 89年7月31日

計畫主持人:董蘭榮

執行單位:國立交通大學電機與控制工程研究所

中 華 民 國 89 年 9 月 19 日

# 行政院國家科學委員會專題研究計畫成果報告

### 國科會專題研究計畫成果報告撰寫格式說明

## **Preparation of NSC Project Reports**

計畫編號: NSC 89-2215-E-009-073

執行期限:88年10月1日至89年7月31日

主持人:董蘭榮 國立交通大學電機與控制工程研究所

計畫參與人員:

魏廷勳 國立交通大學電機與控制工程研究所

林國鼎 國立交通大學電機與控制工程研究所

吳俊銘 國立交通大學電機與控制工程研究所

彭仁俊 國立交通大學電機與控制工程研究所

李彥霖 國立交通大學電機與控制工程研究所

蔡仁傑 國立交通大學電機與控制工程研究所

#### 一、 中英文摘要

智財元件再利用(Intellectual Property Reuse) 技術已經是系統晶片(System-on-Chip)設 計的重要課題。這項技術有助於系統設計者處理日 益複雜的應用需求、整合大型的數位系統及達成較 短的設計週期要求。然而,高效率的智財元件再利 用技術有不少問題需要克服,特別是如何早期找出 最適當的智財元件及架構、如何整合及驗證由不同 類智財元件所組成的系統。目前的設計方法並未在 此問題上著墨太多,通常是由智財元件供應者直接 向設計者提供整合協助。但是,這些整合協助往往 是因智財元件及應用而異,設計者往往花費不少心 力與智財元件供應者協調以解決系統晶片設計問 題。根據近年來工業界的實際經驗,以智財元件為 單元的系統晶片合成技術要面臨下列幾項挑戰:軟 硬體物件的資訊交換、精確的效能評估、智財元件 的適當選擇、異質(Heterogeneous)智財元件的系 統模擬。為了發展一個整合智財元件的系統晶片合 成技術,本計劃將從兩個方向著手。首先從系統階 層的設計方法切入,整體考量演算法則、智財元件 屬性及系統結構。其次是建立異質模擬環境以模擬 及驗證由不同類智財元件組成的系統晶片。此計畫 要達成下列目標:選定符合不同即時要求的系統晶 片組織、正確地在選定的架構上實現應用並驗證 之、經濟快速地完成系統晶片合成與模擬。

關鍵詞:智財元件再利用,系統晶片,軟硬體共設計,硬體描述語言,系統整合,特定應用積體電路,軟硬體共模擬

#### Abstract

Intellectual Property (IP) reuse is becoming essential in System-On-Chip (SOC) design. It helps designers meet the challenges of increasingly complex

applications, highly integrated systems and shorter design cycles. However, effective IP reuse poses several problems, notably in the architecture exploration and the integration of the foreign IP cores within the target system. State-of-the-art design methodologies do not address these issues, but rather rely on the IP vendors to assist designers with the custom integration of their IP cores. According to the industrial practice, the IP-based SOC synthesis presents several challenges to designers. challenges are (1) communication between hardware and software instances, (2) accurate performance estimation of architectural candidates, (3) efficient selection of IP cores, and (4) IP-based heterogeneous system simulation. To achieve an effective IP-based SOC synthesis technology, there are two design phases in this proposal. First, we use three axes, {algorithm, attribution, structure}, to describe a target system. Each of these axes can be tuned to compose an architecture. Based on this three-dimensional representation, our technology allows the designer to describe their target systems entirely and estimate performance measures at a very early stage in the overall design process. Second, we build a heterogeneous co-simulation environment that allows a heterogeneous collection of IP cores to be verified, integrated, and reused seamlessly in a unified design environment. Given an application and a set of real-time constraints, the research has three goals: to synthesize and verify an architecture that can meet flexible real-time constraints, to port the application correctly onto the selected architecture, and to complete the design, simulation and verification quickly and economically.

Keywords: IP, System-On-Chip, hardware-software co-design, system integration, HW/SW co-simulation

#### 二、 緣由與目的

最近,系統晶片與智財元件設計在微電子設計領域備受重視。美國國防部高等計劃研究部門 (DARPA)對這些技術存有高度興趣,在特定應用信號處理之快速原型(RASSP)的計劃中開始發展相關技術。本計劃主持人於 1993 年加入這項計劃,開始從事系統晶片實現的工作。根據在研究工作上累積的經驗,提出此計畫以改善現有的高等晶片合成技術。

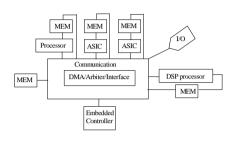

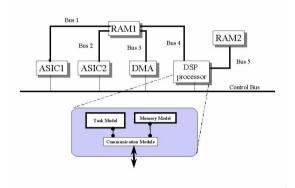

圖一: 典型的系統晶片組織

如圖一所示,典型系統晶片的架構是由通訊、嵌入式控制器、微處理器、數位信號處理器、ASIC、記憶體等單元組成。這些單元可利用智財元件來實現。我們可以歸納出三種基本組織元素:運算元素、通訊元素與儲存元素。其中,運算元素與儲存元素通常主宰處理速度與設計成本。而通訊元素決定了元件資源的使用效率。於是,一個系統晶片可以由不同的元素組合產生很多的選擇。關鍵的組織屬性根據三種元素可歸類如下:

- 運算元素:處理器種類、大部或細部工作指定、異質或同質處理環境、使用的軟體及演算法、單指令多資料或多指令多資料、控制方式、中斷型或監測型機制

- } 通訊元素:匯流排或連接種類、匯流排介面、 環境介面、路由或通信協定、連接拓撲、輸出 入設定、頻寬

- 儲存元素:記憶體種類、記憶體大小、記憶體 與處理器搭配度、記憶體配置與定址、資料暫存

設計者通常需要探索不同的可能屬性組合以找出適當的系統組織。

為了找出最適當的系統組織,系統晶片的設計分為三個階段,分別是演算法則開發、元件選擇、及組織合成。設計之初,根據應用定義好系統規格後,設計者使用高階驗證工具發展演算法則,在演算法則開發階段提出可能的方案。這些方案是以函數工作、資料交換量、工作相依圖等表示。以這些方案為基礎,設計者再利用軟硬體分割及工作配置的成本驅動程序選擇元件。最後,設計者以通訊與記憶體元件將元件整合起來合成系統組織。元件之間的聯結是取決於通訊量、運算速度、工作配置與資料交換量等等。值得注意的是這三個階段互

相關聯影響。然而,設計者很難找到系統層次的整 合設計工具能輔助設計以智財元件為單位的系 統。設計者往往依序在不同的設計環境下發展演算 法、選擇智財元件、建構組織。由於缺乏一個整體 的設計環境,設計工作存在不少的困難。例如:演 算法發展時缺乏考慮晶片實現時的細節、選擇智財 元件時不能選到對特定組織而言最適當的元件、合 成系統晶片時不易嘗試對不同的演算法做評估。像 這樣存在於演算法發展與系統實現之間的藩籬造 成設計發展無法快速準確的達成。為了能有效的合 成系統晶片,設計者必須克服 CAD 工具的整合問 題。因此,我們這個計劃的主要目標就是要發展出 一套整合的系統晶片合成方法與技術讓設計者能 通盤性的描述他們的目標系統並合成符合要求的 系統晶片。此計畫在目前高階微電子設計領域將扮 演很重要的角色,包括本計劃主持人曾服務的美國 洛克威爾公司在內的數家高科技公司正投入不少 研發人力開發相關技術。此計劃將使系統設計者能 從大量的智財元件中探索適當的組織以及無接縫 地合成系統晶片。

#### 三、 結果與討論

本計劃提出一個以智財元件為單元的設計方法。這個設計方法將消除演算法開發與硬體實現兩者間的落差並允許兩個設計階層能無接縫的整合在一起。,這個設計技術有兩個設計階段:

#### 組織探索階段:

這個階段是一個統合的設計階段。在考量組織抉擇 設計彈性 觀念驗證 實現細節等因素下,定出早期的系統組織。這個階段將決定百分之七十以上的製造與維護成本。透過我們在這個階段發展的技術,設計者僅需要最起碼的功能定義便可以得到可執行的規格與快速的組織探索。

我們很難找到在統合組織層次上可用於以智財元件為基本的系統設計工具。一般而言,設計者要在個別的環境下依序開發演算法、選擇智財元件、建構組織。由於缺乏一個整體的設計環境,設計工作存在不少的困難。例如:演算法發展時缺乏考慮晶片實現時的細節、選擇智財元件時不能選到對特定組織而言最適當的元件、合成系統晶片時不易嘗試對不同的演算法做評估。這個存在於演算法開發與硬體實現兩者間的落差使得系統晶片設計很難快速而正確的發展。為了早期對組織架構做出正確的抉擇,設計者必須克服電腦輔助設計工具的整合問題。

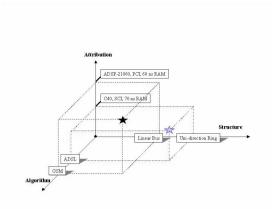

因此,我們將以三維{演算法,屬性,架構}空間來表示系統組織使得設計者能通盤的在組織探索階段描述他們的組織。如圖二所示,系統晶片的組織可以再這個三維空間中被定義。演算法用來表示一個已知應用的工作與流程,屬性定義出組織元素的參數如處理器種類、記憶體大小、通訊協定等,架構則是用來表示拓撲、元件安排、連結等。使用者可以利用這樣的三維表示法對系統晶片設計整體的考量演算法選擇、元件規格、組織配置以作出不同的組織抉擇。

#### 圖二:三維表示法

在系統合成的相關研究上,很多工作是以運算單元的選擇與設計為主。但是,很少的研究把重心擺在軟硬體共設計裏通訊與連接拓撲的考量上。事實上,平行運算的品質是由通訊協定與拓撲決定,通訊元素與運算元素視同等重要而不應該單純的將其忽略。因此,這個計劃對複雜的通訊與輸出入協定建立精確的系統層次模型。這樣的模型將是產生有效可靠的效能分析的關鍵。在這個階段,本計劃完成之成果如下:

#### (一) 軟硬體物件的成本驅動模型

本計劃於組織探索階段的第一步建立成本驅動模型(Cost-driven modeling),導出下列軟硬體成本方程式的箝制條件公式。根據箝制條件公式決定初始組織參數以驅動系統晶片架構探索。

$$\begin{split} Cost_1 &= C^S s_E + \sum_k C_k^{HW\_DEV} h_k + \sum_l C_l^{CUST\_DEV} z_l + r_L + \\ & V \left( \sum_i \sum_j C_{ij}^P x_{ij} + C^M y + \sum_k C_k^{HW} h_k + \sum_l C_l^{CUST\_BD} z_l \right) \\ Cost_2 &= C^S s_E + \sum_k C_k^{HW\_DEV} h_k + \sum_l C_l^{CUST\_DEV} z_l + p_L + \\ & V \left( \sum_i \sum_j C_{ij}^P x_{ij} + C^M y + \sum_k C_k^{HW} h_k + \sum_l C_l^{CUST\_BD} z_l \right) + \\ & T^{MAINT} \left[ C^{MAINT} m_E + V \left( \sum_i \sum_j M_{ij}^{Proc} x_{ij} + M^{mem} y \right) \right] + \\ & T^{MAINT} V \left( \sum_k M_k^{HW} h_k + \sum_l M_l^{CUST\_BD} z_l \right) \end{split}$$

#### (二) 軟硬體分割的最佳化

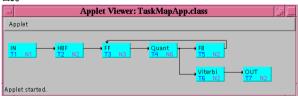

完成初始組織參數的定義後,考量即時限制 (real-time constraints)與上市時間(time-to-market)以 找出最佳區塊劃分、工作排程與串列化。如圖三所示,對已知應用的演算法則產生適當的軟硬體分割。

圖三:軟硬體分割最佳化(上圖為演算法,下 圖為系統組織)

#### (三) 處理器間通訊的高階時序模型

在組織探索階段,效能的分析(performance analysis)強調的是時序與資料交換的精確度,所以我們建立了可隨插即用(plug-and-play)的模擬模型如下圖所示。

#### 實現與驗證階段:

目前的系統晶片設計強調將硬體與軟體的設計分離,軟體必須要在硬體完成之後才開始編譯與測試。這樣遲來的整合導致很多的問題,如:較長的上市時間延遲與成本過度耗損、軟體對硬體做出不正確的假設、軟體在整合期硬體校正時缺乏維護能力。

在實現與驗證階段,我們提出一個能讓設計者發展目標系統的虛擬原型與共模擬模型的方法。這樣的模型會捕捉必要的應用細節使得目標系統的設計與整合可以像一個可模擬軟體模型一樣在製造之前做驗證。這個模型在功能與通訊上都是精確的,而且這個設計抽象階層將硬體製造從設計過程中排除。因此,它將在軟硬體間保持一個彈性的空間讓軟硬體可以同步發展與整合。當硬體模型調整時,軟體應用碼也可以獨立的發展。這樣的特性對於系統晶片組織是很重要的,如此一來,軟體的改變將不會導致硬體的修改。

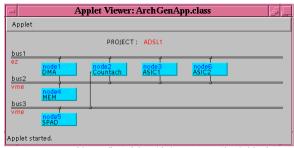

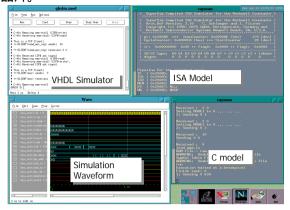

每一個智財元件通常有個別的驗證模式,例如,指令集模擬、硬體描述語言模型、高階語言模型、模擬板等等。而這些模式在速度、精確度、抽象度上有所不同。我們讓設計者視異質的智財元件為只觀察到輸出入介面的黑盒子。舉例言之,設若這個統合的設計環境是以 VHDL 為主,這些智財元件就看起來像 VHDL 物件。本計劃建立一個系統模擬的整合環境將成本驅動模型、軟硬體分割最佳化、高階時序模型整合於一個統合的設計環境。如下圖所示,整合環境依已知的演算法則找出候選的

系統組織後,整合不同之智財單元執行共模擬。最 後產生效能分析結果以利設計者除錯與實現系統 晶片。

- 26-27 October, 1998

- [7] Mohamed Ben-Romdhane, Marius Vassiliou and Lan-Rong Dung, "Rapid Prototyping of Multimedia Chip Sets", ICASSP-99, March,1999

- [8] Lan-Rong Dung, Vijay K. Madisetti, John W. Hines, "Model-Based Architectural Design and Verification of Scalable Embedded DSP Systems A RASSP Approach," Chapter in VLSI Signal Processing IX, IEEE Press, 1996, ISBN 0-7803-3134-6, pp. 147-158

- [9] J. DeBardelaben, V. Madisetti, and A. Gadient, "Incorporating Cost Modeling in Embedded-System Design," IEEE Design & Test of Computers, pp.24-35, July-September, 1997

#### 四、 成果自評

本計劃從應用系統的角度提出實現系統晶片的解決方案,成功實現軟硬體共設計、高階系統模擬、智財再利用等技術,研究之結果已達到預期目標。本計劃的應用價值有三:縮短產品上市時間、避免重設計週期(redesign cycle)、提高智財元件的再利用能力(IP reusability)。目前已將本計劃之研究成果整理出三篇學術性論文,正投稿於 IEEE Transactions on VLSI,與 ISCAS 2001 等期刊及國際會議。這些論文將對系統晶片之研究領域有所貢獻。

### 五、 參考文獻

- [1] Lan-Rong Dung, Vijay K. Madisetti, and John W. Hines, "Model-Based Architectural Design and Verification of Embedded DSP Systems," 1996 VLSI Signal Processing Workshop, October 1996

- [2] Daniel D. Gajski and Frank Vahid,

"Specification and Design of Embedded

Hardware-Software Systems," IEEE Design and

Test of Computers, Spring 1995

- [3] Mohamed Ben Romdhane, Vijay Madisetti, John Hines, "Quick-Turnaround ASIC Design in VHDL, a Core-Based Behavioral Synthesis," Kluwer Academic Publishers (KAP), 1996

- [4] Lan-Rong Dung, Mohamed Ben-Romdhane and Marius Vassiliou, "IP-Based Architecture Exploration," DesignCon99, February, 1999

- [5] Lan-Rong Dung and Vijay K. Madisetti, "Conceptual Prototyping of Scalable Embedded DSP Systems," IEEE Design and Test of Computers, Fall, 1996

- [6] Mohamed Ben-Romdhane, Lan-Rong Dung and Marius Vassiliou, "Lego-Like Integration of IP Cores," The second Intellectual Property in Electronics Conference - Europe, IP98 – Europe,