## Self-aligned contact metallization technology for III-V metal-oxide-semiconductor field effect transistors

Xingui Zhang, Huaxin Guo, Hau-Yu Lin, Chao-Ching Cheng, Chih-Hsin Ko, Clement H. Wann, Guang-Li Luo, Chun-Yen Chang, Chao-Hsin Chien, Zong-You Han, Shih-Chiang Huang, Hock-Chun Chin, Xiao Gong, Shao-Ming Koh, Phyllis Shi Ya Lim, and Yee-Chia Yeo

Citation: Journal of Vacuum Science & Technology B 29, 032209 (2011); doi: 10.1116/1.3592211 View online: http://dx.doi.org/10.1116/1.3592211 View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/29/3?ver=pdfcov Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

### Articles you may be interested in

Self-aligned Ni-GaSb source/drain junctions for GaSb p-channel metal-oxide-semiconductor field-effect transistors

Appl. Phys. Lett. 104, 093509 (2014); 10.1063/1.4867262

Magnetic evidence for solid-state solubility-limited dissolution of Ni into AuGe in alloyed AuGe/Ni/Au Ohmic contacts to GaAs J. Appl. Phys. 112, 043903 (2012); 10.1063/1.4743992

Self-aligned via and trench for metal contact in III-V semiconductor devices

J. Vac. Sci. Technol. B 24, 1117 (2006); 10.1116/1.2188000

Application of nonalloyed PdGe ohmic contact to self-aligned gate AIGaAs/InGaAs pseudomorphic high-electronmobility transistor

Appl. Phys. Lett. 74, 2866 (1999); 10.1063/1.124040

Thermal stability of Pd/Zn and Pt based contacts to p- In 0.53 Ga 0.47 As/InP with various barrier layers J. Vac. Sci. Technol. B 16, 227 (1998); 10.1116/1.589784

# **Re-register for Table of Content Alerts**

# Self-aligned contact metallization technology for III-V metal-oxide-semiconductor field effect transistors

Xingui Zhang and Huaxin Guo

National University of Singapore (NUS), Singapore 117576, Singapore

Hau-Yu Lin, Chao-Ching Cheng, Chih-Hsin Ko, and Clement H. Wann Taiwan Semiconductor Manufacturing Company, Hsinchu, Taiwan 300, Republic of China

#### Guang-Li Luo

National Nano Device Laboratory, Hsinchu, Taiwan 300, Republic of China

#### Chun-Yen Chang

Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, Republic of China

#### Chao-Hsin Chien

National Nano Device Laboratory, Hsinchu, Taiwan 300, Republic of China and Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, Republic of China

#### Zong-You Han

Institute of Electronics, National Chiao-Tung University, Hsinchu, Taiwan 300, Republic of China

#### Shih-Chiang Huang

National Nano Device Laboratory, Hsinchu, Taiwan 300, Republic of China

Hock-Chun Chin, Xiao Gong, Shao-Ming Koh, Phyllis Shi Ya Lim, and Yee-Chia Yeo<sup>a)</sup> National University of Singapore (NUS), Singapore 117576, Singapore

(Received 14 January 2011; accepted 28 April 2011; published 26 May 2011)

The demonstration of a salicidelike self-aligned contact technology for III-V metaloxide-semiconductor field-effect transistors (MOSFETs) is reported. A thin and continuous crystalline germanium-silicon (GeSi) layer was selectively formed on n<sup>+</sup> doped gallium arsenide (GaAs) regions by epitaxy. A new self-aligned nickel germanosilicide (NiGeSi) Ohmic contact with good morphology was achieved using a two-step annealing process with precise conversion of the GeSi layer into NiGeSi. NiGeSi contact with the contact resistivity ( $\rho_c$ ) of 1.57  $\Omega$  mm and sheet resistance ( $R_{sh}$ ) of 2.8  $\Omega/\Box$  was achieved. The NiGeSi-based self-aligned contact technology is promising for future integration in high performance III-V MOSFETs. © 2011 American Vacuum Society. [DOI: 10.1116/1.3592211]

#### I. INTRODUCTION

III-V materials such as gallium arsenide (GaAs) and indium gallium arsenide (InGaAs) have significantly higher electron mobility than silicon (Si) and are attractive channel material candidates for metal-oxide-semiconductor fieldeffect transistors (MOSFETs) in future high-speed and lowpower logic applications.<sup>1-12</sup> To realize high-performance III-V MOSFETs, low channel resistance as well as low parasitic series resistance in the source/drain (S/D) regions are required. Series resistance in the S/D regions includes the resistance in the doped S/D and the contact resistance between the doped S/D and the contact material. Selective growth of in situ doped S/D materials has recently been used for reducing the series resistance in the doped S/D.<sup>13-15</sup> In addition, contacts with low contact resistance to the S/D regions are required. Contacts for III-V MOSFETs can be formed by direct deposition and patterning (e.g., lift-off) of metals on the doped S/D, with or without a subsequent alloying anneal.<sup>16–22</sup> Contact metallization in III-V MOSFETs

is usually non-self-aligned with respect to the gate stack, unlike the self-aligned salicidation process in Si MOSFETs. A spacing between the contact metal and the gate leads to increased series resistance that compromises drive current  $I_{\text{Dsat}}$  performance. III-V MOSFETs with self-aligned contacts are thus needed for reduction of series resistance and for better device density scaling.<sup>23,24</sup> While a height selective etching process has been developed to achieve self-aligned contact for III-V MOSFETs,<sup>15,24</sup> a self-aligned metallization process analogous to the salicidation process in Si complementary metal-oxide-semiconductor technology is still needed for III-V MOSFETs.<sup>25,26</sup>

In this article, we report the demonstration of a salicidelike self-aligned nickel germanide (NiGe) based contact technology for GaAs MOSFETs. NiGe-based contact is attractive due to the low resistivity of NiGe (22  $\mu\Omega$  cm) as compared with PdGe (30  $\mu\Omega$  cm), the low cost of Ni, and the low germanide formation temperature<sup>27–29</sup> that is compatible with III-V materials. Transmission line method (TLM) test structures were fabricated using a process flow shown in Fig. 1 in the development of the self-aligned metallization technology. A thin continuous high-quality germa-

<sup>&</sup>lt;sup>a)</sup>Present address: National University of Singapore, 117576, Singapore; electronic addresses: yeo@ieee.org and eleyeoyc@nus.edu.sg

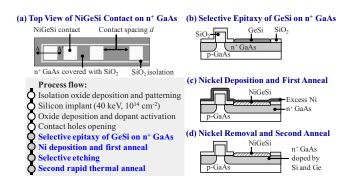

FIG. 1. (Color online) (a) Plan-view optical microscopy image of the TLM structure. The self-aligned ohmic contact formation process comprises (b) selective epitaxy of GeSi on  $n^+$  GaAs in a contact hole, (c) Ni deposition and a first thermal anneal for NiGeSi formation, (d) removal of excess Ni, and a second thermal anneal to form the Ohmic contact.

nium silicon (GeSi) layer was first selectively grown on n<sup>+</sup> doped GaAs regions [Fig. 1(b)]. Second, a two-step germanosilicide process was developed to form nickel germanosilicide (NiGeSi) Ohmic contacts on GaAs, where hydrochloric acid (HCl) was employed for selective removal of unreacted Ni [Figs. 1(c) and 1(d)].

### II. DEVELOPMENT OF SELF-ALIGNED CONTACT TECHNOLOGY

p-type  $(N_A \sim 5 \times 10^{16} \text{ cm}^{-3})$  GaAs (001) substrates were used to fabricate test structures which enable the extraction of contact resistance using the TLM.<sup>30,31</sup> A SiO<sub>2</sub> isolation pattern was formed and Si was implanted at an energy of 40 keV and a dose of  $1 \times 10^{14} \text{ cm}^{-2}$ . The projected Si implant depth and straggle are 43 and 22 nm, respectively. A thin capping layer of SiO<sub>2</sub> (~30 nm) was then deposited before dopant activation at 800 °C for 10 s. The SiO<sub>2</sub> cap was patterned and etched to define contact holes that exposed the n<sup>+</sup> GaAs surface for contact formation.

# A. Selective epitaxy of germanium silicon (GeSi) on GaAs

An epitaxy process was employed to selectively form a continuous GeSi film ( $\sim 40$  nm) on the n<sup>+</sup> GaAs surface in the contact holes. The wafers were annealed in vacuum at 650 °C for native oxide desorption before being loaded into a GeSi growth chamber. Epitaxial growth was performed at 565 °C using SiH<sub>4</sub> and GeH<sub>4</sub> as precursors with the flow rates of 3 and 5 SCCM (SCCM denotes cubic centimeter per minute at STP), respectively. The process pressure was maintained at 30 mTorr. SiH<sub>4</sub> flow was introduced during growth in an attempt to overcome the islanding issue which occurs when only GeH<sub>4</sub> precursor was used. Growth of GeSi seemed to have a flatter surface morphology as compared to the growth of Ge.<sup>32</sup> Ge islanding on n<sup>+</sup> GaAs gives a discontinuous Ge film and would cause Ni penetration into GaAs during a subsequent contact metallization step. This is expected to result in a nonuniform contact. It has been reported that NiGe formed on single crystalline Ge exhibits better uniformity and thermal stability than that formed on poly-

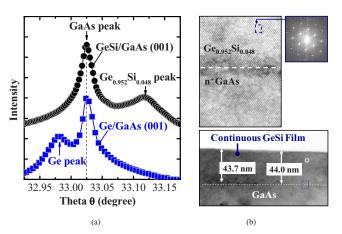

FIG. 2. (Color online) (a) High resolution x-ray diffraction (HRXRD) shows that 4.8 at. % of Si was incorporated in GeSi. The spectra intensity is plotted using a logarithmic scale. GeSi formed on GaAs is under tensile strain. (b) Transmission electron microscopy (TEM) shows the GeSi/GaAs hetero-structure formed and a diffractogram of a selected region enclosed by a dashed box indicates the good crystalline quality of GeSi.

crystalline Ge.<sup>33</sup> A continuous GeSi film with good single crystalline quality is crucial for NiGeSi contact formation.

The grown Ge and GeSi (004) diffraction peaks were clearly observed from the high resolution x-ray diffraction (XRD) [Fig. 2(a)]. The values of full width at half maximum were 0.02° and 0.037° for the Ge and Ge<sub>0.952</sub>Si<sub>0.048</sub> films, respectively, suggesting that the crystal quality is better for a lower lattice mismatch between the epilayer and GaAs. XRD spectra indicates that Ge (lattice constant=5.6577 Å) film on GaAs (lattice constant=5.6537 Å) is under a slight compressive strain with  $2\theta$ =32.981° while fully relaxed Ge has a  $2\theta$  of 33.0°. However, GeSi film on GaAs is fully tensile strained with  $2\theta$ =33.118° and the composition was extracted to be Ge<sub>0.952</sub>Si<sub>0.048</sub> by fitting XRD spectra using X'Pert epitaxy. Peak shift of Raman spectroscopy (not shown here) is 301 cm<sup>-1</sup> for Ge/GaAs and 298.9 cm<sup>-1</sup> for GeSi/GaAs, consistent with the strain and composition of the epilayers.

Transmission electron microscopy (TEM) images [Fig. 2(b)] indicate that the single-crystalline GeSi was uniformly formed and is free from dislocations. The TEM images in Fig. 2(b) also show the abrupt interface between GeSi and GaAs. Fast Fourier transform diffractogram [Fig. 2(b)] reveals the good crystalline quality of the GeSi epitaxial layer.

# B. Two-step metallization process for contact formation

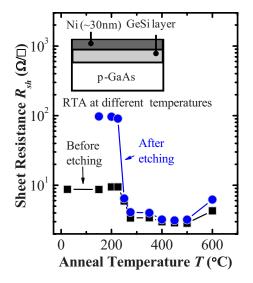

Single crystalline GeSi film  $(40 \sim 50 \text{ nm})$  was grown on blanket GaAs substrate followed by Ni (~30 nm) deposition. The structure of the sample is illustrated in Fig. 3. The Ni/GeSi/GaAs wafer was then cut into pieces and each piece went through rapid thermal anneal (RTA) at a different temperature for 60 s for the formation of NiGeSi. The RTA temperature ranges from 150 to 600 °C. The sheet resistance ( $R_{sh}$ ) of NiGeSi formed at various anneal temperatures was

edistribution subject to AVS license or copyright; see http://scitation.aip.org/termsconditions. Download to IP: 140.113.38.11 On: Wed, 30 Apr 2014 09:09:25

FIG. 3. (Color online) Sheet resistance vs anneal temperature for  $\sim 30$  nm Ni on blanket GeSi/GaAs sample annealed at different temperatures for 60 s. The sheet resistance values of annealed sample with and without selective etching in hot HCl are indicated by square and circle symbols, respectively. Nickel germanosilicide formed at above 250 °C has a low sheet resistance even after the selective etching process.

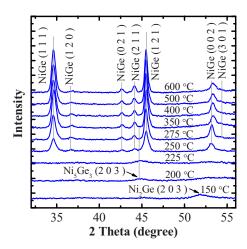

investigated. A four-point probe was used to measure  $R_{\rm sh}$ . XRD was performed to analyze the nickel germanide phase transformation.

Figure 3 shows the  $R_{\rm sh}$  of NiGeSi/GaAs samples right after RTA (square symbols) at different temperatures. The  $R_{\rm sh}$ of the as-deposited sample was 8.7  $\Omega/\Box$ . After annealing at 200–225 °C,  $R_{\rm sh}$  was slightly increased to 9.5  $\Omega/\Box$  due to Ni consumption and Ni<sub>5</sub>Ge<sub>3</sub> formation (Fig. 4). Ni<sub>5</sub>Ge<sub>3</sub> has a higher resistivity than the deposited Ni film. Nickel monogermanide (NiGe), a low resistivity phase, started to form at 250 °C and  $R_{\rm sh}$  decreased to 5.9  $\Omega/\Box$ . Both Ni<sub>5</sub>Ge<sub>3</sub> and NiGe phases exist when the samples were annealed at 250 °C. When the annealing temperature was increased

FIG. 4. (Color online) XRD spectra shows nickel germanide phases formed from 150 and 600 °C. The spectra intensity is plotted using a linear scale. The spectra indicates that NiGe started to form when annealing at 250 °C and confirms that only NiGe phase was formed with annealing temperature over 275 °C.

above 275 °C, only the NiGe phase existed, and the lowest  $R_{\rm sh}$  of 2.8  $\Omega/\Box$  was achieved at annealing temperatures of 450 and 500 °C. NiGe (111), (121), (120), (021), (211), (002), and (301) peaks can be observed (Fig. 4). When the anneal temperature was increased further to 600 °C,  $R_{\rm sh}$  increased to 4.3  $\Omega/\Box$  due to the effects of agglomeration.<sup>33</sup>

A selective etching process for removing excess Ni was developed to enable integration of self-aligned NiGeSi/GaAs contacts for GaAs MOSFETs. Dilute HCl (1:10) could achieve good etching selectivity of Ni over nickel germanide and thus was employed to remove the unreacted Ni. The  $R_{\rm sh}$  values of NiGeSi/GaAs samples after the HCl etching are also shown in Fig. 3 (circle symbols). The  $R_{\rm sh}$  increased significantly to ~95  $\Omega/\Box$  after the selective etching when the anneal temperature was below 225 °C. This is because some of the Ni was still unreacted and was removed by the subsequent HCl dip. However, Ni was completely consumed and nickel germanide (Ni<sub>5</sub>Ge<sub>3</sub> and NiGe) was formed when the annealing temperature was over 250 °C, giving low  $R_{\rm sh}$  even after the selective etching step.

A two-step contact metallization process for Ohmic contact formation on n<sup>+</sup> GaAs was conceived. A brief dilute hydroflouric acid dip was performed to remove the native oxide of GeSi prior to e-beam deposition of Ni (~30 nm). A first anneal at the temperature of 250 °C was then performed to consume all of the Ni on GeSi by forming nickel germanide. Unreacted Ni on SiO<sub>2</sub> was subsequently selectively removed by hot HCl. After the first anneal, we found that the nickel germanide does not form an Ohmic contact to the underlying GaAs yet. A second high temperature RTA at 500 °C was then performed to convert the nickel germanide phases into the nickel monogermanide phase, which achieves an Ohmic contact with GaAs and a low  $R_{sh}$ .

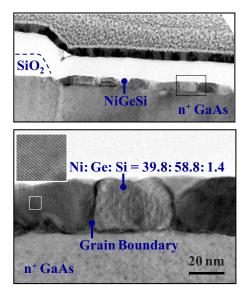

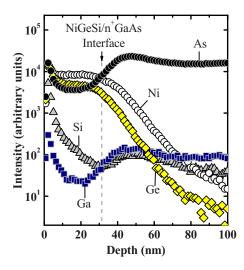

Figure 1(a) shows the top-view of a TLM structure with NiGeSi contacts on n<sup>+</sup> GaAs. TEM analysis of a portion (A-A') of the TLM structure (Fig. 5) clearly shows the polycrystalline structure of NiGeSi, which has a thickness of  $\sim 30$  nm. No nickel germanide was observed on the SiO<sub>2</sub> region, indicating good selectivity of GeSi epitaxy. High resolution TEM image shows good uniformity of the NiGeSi and several grains of NiGeSi could be observed clearly, showing a distinct interface between NiGeSi and GaAs. Energy dispersive x-ray spectrometry (EDX) indicates the approximate NiGeSi composition ratio of Ni:Ge:Si = 39.8:58.8:1.4. Secondary ion mass spectrometry (SIMS) analysis performed on the NiGeSi/n<sup>+</sup>GaAs contact shows the elemental distribution of Ga, As, Ni, Ge, and Si, as plotted in Fig. 6. The gray dashed line represents the estimated NiGeSi/GaAs interface. The thickness of NiGeSi obtained using SIMS is quite consistent with that obtained from TEM (Fig. 5).

# III. ELECTRICAL CHARACTERISTICS AND DISCUSSION

After the first anneal at 250 °C and selective removal of unreacted Ni, the current-voltage (*I-V*) curve measured between two adjacent germanosilicide (Ni<sub>5</sub>Ge<sub>3</sub>, NiGe) contacts

FIG. 5. (Color online) Cross-sectional TEM image (top) of TLM structure shows the formation of polycrystalline NiGeSi on  $n^+$  GaAs that is not covered by SiO<sub>2</sub>. No Ge or NiGeSi was also observed on the SiO<sub>2</sub> region, which confirmed the selectivity of GeSi epitaxy. A zoomed-in view (bottom) showing several grains of NiGeSi. A high-resolution TEM image of a portion of a NiGeSi grain is shown on the inset.

in a TLM structure did not show Ohmic behavior. A second high temperature anneal at 500 °C converted the nickel germanide phases into a low resistivity nickel monogermanide phase, and probably helped to drive Ge and/or Si diffusion into GaAs. Ge has been also reported to dope GaAs heavily through interdiffusion between Ge and GaAs.<sup>21</sup> A Ge-rich GaAs interfacial layer right beneath the NiGeSi was also detected by EDX. Increasing the n-type doping concentration in GaAs can help to achieve good Ohmic contact with low  $R_C$ .

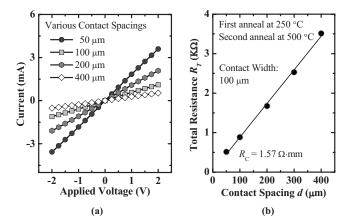

After the second anneal at 500 °C, an Ohmic contact was obtained, as shown in Fig. 7(a). *I-V* characteristics was measured between two adjacent NiGeSi/n<sup>+</sup>GaAs contact pads

FIG. 6. (Color online) SIMS analysis of NiGeSi contact on  $n^+$  GaAs gives the elemental distribution. The interface between NiGeSi and GaAs is indicated by the dashed vertical line.

FIG. 7. (a) NiGeSi Ohmic contacts were formed on  $n^+$  GaAs using a twostep anneal process. *I-V* curves measured between NiGeSi contacts with different contact spacings *d* formed on  $n^+$  GaAs show excellent Ohmic behavior. (b) Plot of total resistance  $R_T$  between two NiGeSi contacts as a function of the contact spacing *d*.

separated by various contact spacings *d*. The total resistance  $R_T$  between two contacts decreases linearly with decreasing *d*. By plotting  $R_T$  versus *d*, as shown in Fig. 7(b), one can extract the contact resistance  $R_C$  from the intercept of the linear fitting line with the vertical axis and the sheet resistance  $R_{sh,GaAs}$  of the doped substrate from the line slope.  $R_C$  and  $R_{sh,GaAs}$  were ~1.57  $\Omega$  mm and 852  $\Omega/\Box$ , respectively.

It should be noted that the  $R_C$  is not optimized in this work, and further improvement is possible. Work function tuning of the contact metal, increasing the doping concentration of n<sup>+</sup> GaAs, or forming an intermediate layer with smaller band gap could also be explored to reduce  $R_C$ .<sup>34–36</sup>

## **IV. CONCLUSION**

A self-aligned Ohmic contact metallization technology for GaAs was demonstrated. A continuous and single crystalline GeSi film was selectively grown on n<sup>+</sup> GaAs for forming a NiGeSi-based contact using a two-step anneal. Ohmic contact behavior of NiGeSi on n<sup>+</sup> GaAs regions was obtained. Contact resistivity  $\rho_c$  as low as 1.57  $\Omega$  mm was achieved. The NiGeSi Ohmic contact technology is compatible and can be integrated in III-V MOSFETs for future high speed low power logic applications.

### ACKNOWLEDGMENTS

Research grants from the National Research Foundation (NRF) (Award No. NRF-RF2008-09) and Defense Science and Technology Agency (DSTA) (Grant No. POD0713909), Singapore, are acknowledged.

<sup>1</sup>M. Hong, F. Ren, J. M. Kuo, W. S. Hobson, J. Kwo, J. P. Mannaerts, J. R. Lothian, and Y. K. Chen, J. Vac. Sci. Technol. B 16, 1398 (1998).

- <sup>2</sup>P. Chang, W. C. Lee, M. L. Huang, Y. J. Lee, M. Hong, and K. Kwo, J. Vac. Sci. Technol. B **28**, C3A9 (2010).

- <sup>3</sup>M. Zhu, C. H. Tung, and Y.-C. Yeo, Appl. Phys. Lett. **89**, 202903 (2006).

<sup>4</sup>H.-C. Chin, X. Gong, L. Wang, and Y.-C. Yeo, Electrochem. Solid-State Lett. **13**, H440 (2010).

<sup>5</sup>S. Takagi T. Irisawa, T. Tezuka, T. Numata, S. Nakaharai, N. Hirashita, Y. Moriyama, K. Usuda, T. Toyoda, S. Dissanayake, M. Shichijo, R. Na-

#### 032209-5 Zhang et al.: Self-aligned contact metallization technology

kane, S. Suqahara, N. Takenaka, and N. Suqiyama, IEEE Electron Device Lett. **55**, 21 (2008).

<sup>6</sup>R. Chau, S. Datta, M. Doczy, B. Doyle, B. Jin, J. Kavalieros, A. Majumdar, M. Metz, and M. Radosavljevic, IEEE Trans. Nanotechnol. 4, 153 (2005).

<sup>7</sup>Y. Xuan, Y. Q. Wu, and P. D. Ye, IEEE Electron Device Lett. **29**, 294 (2008).

- <sup>8</sup>R. J. W. Hill, D. A. J. Moran, X. Li, H. Zhou, D. Macintyre, S. Thoms, A. Asenov, P. Zurcher, K. Rajagopalan, J. Abrokwah, R. Droopad, M. Passlack, and I. G. Thayne, IEEE Electron Device Lett. **28**, 1080 (2007).

- <sup>9</sup>M. Heyns C. Adelmann, G. Brammertz, D. Brunco, M. Caymax, B. De Jaeqer, A. Delabie, G. Eneman, M. Houssa, D. Lin, K. Martens, C. Merckling, M. Meuris, J. Mittard, J. Penaud, G. Pourtois, M. Scarrozza, E. Simoen, S. Sioncke, and W.-E. Wang, Tenth International Conference on Ultimate Integration of Silicon, 2009, p. 83.

- <sup>10</sup>N. Waldron, D. H. Kim, and J. A. del Alamo, IEEE Trans. Electron Devices 57, 297 (2010).

- <sup>11</sup>D. H. Kim and J. A. del Alamo, IEEE Trans. Electron Devices 55, 2546 (2008).

- <sup>12</sup>R. J. W. Hill, J. Huang, J. Barnett, P. Kirsch, and R. Jammy, Solid State Technol. **53**, 17 (2010).

- <sup>13</sup>H.-C. Chin, X. Gong, X. Liu, and Y.-C. Yeo, IEEE Electron Device Lett. 30, 805 (2009).

- <sup>14</sup>U. Singisetti, M. A. Wistey, G. J. Burek, E. Arkun, A. K. Baraskar, Y. Sun, E. W. Kiewra, B. J. Thibeault, A. C. Gossard, C. J. Palmstrøm, and M. J. W. Rodwell, Phys. Status Solidi C 6, 1394 (2009).

- <sup>15</sup>U. Singisetti, M. A. Wistey, G. J. Burek, A. K. Baraskar, B. J. Thibeault, A. C. Gossard, M. J. W. Rodwell, B. Shin, E. J. Kim, P. C. McIntyre, B. Yu, Y. Yuan, D. Wang, Y. Taur, P. Asbeck, and Y.-J. Lee, IEEE Electron Device Lett. **30**, 1128 (2009).

- <sup>16</sup>M. Hong, D. Vakhshoori, J. P. Mannaerts, F. A. Thiel, and J. D. Wynn, J. Vac. Sci. Technol. B **12**, 1047 (1994).

- <sup>17</sup>A. K. Baraskar, M. A. Wistey, V. Jain, U. Singisetti, G. Burek, B. J. Thibeault, Y. J. Lee, A. C. Gossard, and M. J. W. Rodwell, J. Vac. Sci. Technol. B **27**, 2036 (2009).

- <sup>18</sup>P. D. Ye, G. D. Wilk, J. Kwo, B. Yang, H.-J. L. Gossmann, M. Frei, S. N. G. Chu, J. P. Mannaerts, M. Sergent, M. Hong, K. K. Ng, and J. Bude, IEEE Electron Device Lett. **24**, 209 (2003).

- <sup>19</sup>H.-C. Chin, M. Zhu, X. Liu, H.-K. Lee, L. Shi, L.-S. Tan, and Y.-C. Yeo, IEEE Electron Device Lett. **30**, 110 (2009).

- <sup>20</sup>H.-C. Chin, M. Zhu, C.-H. Tung, G. S. Samudra, and Y.-C. Yeo, IEEE Electron Device Lett. **29**, 553 (2008).

- <sup>21</sup>W. T. Anderson, A. Christou, and J. E. Davey, IEEE J. Solid-state Circuits 13, 430 (1978).

- <sup>22</sup>T. D. Lin, H. C. Chiu, P. Chang, L. T. Tung, C. P. Chen, M. Hong, J. Kwo, W. Tsai, and Y. C. Wang, Appl. Phys. Lett. **93**, 033516 (2008).

- <sup>23</sup>A. Dimoulas, A. Toriumi, and S. E. Mohney, MRS Bull. 34, 522 (2009).

<sup>24</sup>X. Li, R. J. W. Hill, P. Longo, M. C. Holland, H. Zhou, S. Tohms, D. S.

- Macintyre, and I. G. Thayne, J. Vac. Sci. Technol. B **27**, 3153 (2009).

- <sup>25</sup>H. Guo, X. Zhang, H.-C. Chin, X. Gong, S.-M. Koh, C. Zhan, G.-L. Luo, C.-Y. Chang, H.-Y. Lin, C.-H. Chien, Z.-Y. Han, S.-C. Huang, C.-C. Cheng, C.-H. Ko, C. H. Wann, and Y.-C. Yeo, International Symposium on VLSI Technology, System and Applications, VLSI-TSA, 2010, p. 152.

- <sup>26</sup>X. Zhang, H. Guo, C.-H. Ko, C. H. Wann, C.-C. Cheng, H.-Y. Lin, H.-C. Chin, X. Gong, P. S. Y. Lim, G.-L. Luo, C.-Y. Chang, C.-H. Chien, Z.-Y. Han, S.-C. Huang, and Y.-C. Yeo, IEEE Symposium on VLSI Technology, 2010, p. 233.

- <sup>27</sup>S. Zhu and A. Nakajima, Jpn. J. Appl. Phys., Part 2 44, L753 (2005).

- <sup>28</sup>D. P. Brunco, B. De Jaeger, G. Eneman, J. Mitard, G. Hellings, A. Satta, V. Terzieva, L. Souriau, F. E. Leys, G. Pourtois, M. Houssa, G. Winderickx, E. Vrancken, S. Sioncke, K. Opsomer, G. Nicholas, M. Caymax, A. Stesmans, J. Van Steenbergen, P. W. Mertens, M. Meuris, and M. M. Heyns, J. Electrochem. Soc. **155**, H552 (2008).

- <sup>29</sup>J. Y. Spann, R. A. Anderson, T. J. Thornto, G. Harris, S. G. Thomas, and C. Tracy, IEEE Electron Device Lett. **26**, 151 (2005).

- <sup>30</sup>W. M. Loh, S. E. Swirhun, T. A. Schreyer, R. M. Swanson, and K. C. Saraswat, IEEE Trans. Electron Devices **34**, 512 (1987).

- <sup>31</sup>D. K. Schroder, *Semiconductor Material and Device Characterization*, 2nd ed. (Wiley, New York, 1998).

- <sup>32</sup>Z.-Y. Han, G.-L. Luo, S.-C. Huang, C.-H. Ko, C. H. Wann, H.-Y. Lin, C.-T. Chung, C.-C. Cheng, C.-Y. Chang, and C.-H. Chien, Extended Abstracts of the 2009 International Conference on Solid States Devices and Materials, 2009, p. 248.

- <sup>33</sup>S.-L. Hsu, C.-H. Cheng, M.-J. Yang, R.-H. Huang, and T.-H. Yang, Appl. Phys. Lett. 86, 251906 (2005).

- <sup>34</sup>M. Murakami, Sci. Technol. Adv. Mater. **3**, 1 (2002).

- <sup>35</sup>M. Furumai, T. Oku, H. Ishikawa, A. Otsuki, and Y. Koide, J. Electron. Mater. **25**, 1684 (1996).

- <sup>36</sup>Y. Tsunoda and M. Murakami, J. Electron. Mater. **31**, 76 (2002).