# A High-Performance Thin-Film Transistor with a Vertical Offset Structure

Chun-Yen Chang, Fellow, IEEE, and Chiung-Wei Lin

Abstract—In this study, we propose a novel device structure combined with conventional hydrogenated amorphous silicon (a-Si:H) for the source and drain regions and microcrystalline silicon ( $\mu$ c-Si:H) for the channel region to obtain a high-performance thin-film transistor (TFT). This is a vertical a-Si:H offset structure used to suppress OFF-state current to a small value which is comparable to the conventional a-Si:H TFT's with a much higher drivability. The fabrication process is simple, low temperature ( $\leq$  300 °C), and low cost, with a potential for high reliability.

### I. INTRODUCTION

ECENTLY, hydrogenated amorphous-silicon thin-film R transistors (a-Si:H TFT's) have been investigated extensively for applications in large area switching devices such as active-matrix liquid crystal display (AM-LCD) [1], [2], The most serious problems of present a-Si:H TFT's are the low field-effect mobility of carriers in the a-Si:H channel and the reliability. Thus the current driving capability is low. On the other hand, polysilicon (poly-Si) TFT's improve the current drivability while sacrificing the turn-off capability. Hence, there are many investigations for improving the turnon characteristics of TFT's including double gate electrode [3], short channel device [4], and vertical structure [5]. For the improvement of drivability of poly-Si TFT's, an offset structure is proposed to reduce the OFF-current [6]. All of these technologies are complicated and costly. Meanwhile, a new crystalline material of higher band mobility (namely microcrystalline silicon, or  $\mu$ c-Si:H) is used to achieve highspeed TFT's [7]-[9]. Tsai et al. [10] proposed an H<sub>2</sub>-dilution method to deposit a high-quality  $\mu$ c-Si film which is used in the  $\mu$ c-Si TFT's. Although a higher mobility than a-Si:H TFT's can be obtained, the OFF-currents of  $\mu$ c-Si:H TFT's are still very high; therefore, the ON/OFF current ratio is only five orders of magnitude or less. An offset structure is usually used to suppress the carrier conduction effectively due to the carrier trapping. In this letter, we propose a novel structure the channel of which is composed of  $\mu$ c-Si:H film while intrinsic a-Si:H film is an offset layer to improve the performance. The high conductance of the thin  $\mu$ c-Si:H layer can increase the ON-current and field-effect mobility and the vertical a-Si:H layer suppresses the OFF-current comparable to the conventional a-Si:H device.

Manuscript received May 14, 1996; revised August 26, 1996. This work was supported by the National Science Council, R.O.C., under Contract NSC85-2215-E009-038.

The authors are with the Institute of Electronics, National Chiao-Tung University, Hsinchu 300, Taiwan, R.O.C.

Publisher Item Identifier S 0741-3106(96)08863-5.

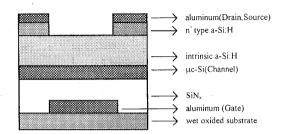

Fig. 1. A schematic diagram of the proposed novel thin-film transistor device.

### II. EXPERIMENTAL

Our novel device is shown schematically in Fig. 1. The fabrication process is similar to the conventional inverted stagger a-Si:H TFT's except for the insertion of a thin H<sub>2</sub>dilution deposited  $\mu$ c-Si:H film embedded between the gate insulator and undoped a-Si:H films. First, an aluminum film 250-nm thick is evaporated on a thermal oxide coated wafer and patterned to form the gate electrode by photolithography and wet etching. Secondly, silicon nitride,  $H_2$ -diluted  $\mu$ c-Si:H, undoped a-Si:H and n<sup>+</sup> a-Si:H films of 300-nm, 20-nm, 140-nm, and 70-nm thicknesses are deposited consecutively in a plasma enhanced chemical vapor deposition (PECVD) system without breaking the vacuum. The silicon nitride film is deposited at 300 °C, 27.78 mw/cm<sup>2</sup>, 1 torr, while undoped and n<sup>+</sup> a-Si:H films are deposited at 250 °C, 25 mw/cm<sup>2</sup>, 0.3 torr. Besides, uc-Si:H films are deposited at 250 °C. 0.55 torr, and 25 mw/cm<sup>2</sup> using the  $[H_2]/\{[SiH_4] + [H_2]\}$  flow rate ratio values of 980 sccm/(20 sccm + 980 sccm) for 98% diluted film and 990 sccm/(10 sccm + 990 sccm) for 99% diluted film, respectively. The grain size of  $\mu$ c-Si:H after final processing was approximately 20 nm for 98% diluted film while was 18 nm for the 99% diluted film, respectively. Another aluminum film of 250-nm thickness is also evaporated and patterned to form source-drain electrodes by photolithography and wet etching processes. Finally, we use CF4 plasma etching to define the device active region and remove the unwanted n+ a-Si layer region. All the devices were annealed in 200 °C N2 ambient for 25 min and the electrical properties of our TFT's are measured by a HP4145B semiconductor parameter measurement system with a PC system.

### III. RESULTS AND DISCUSSIONS

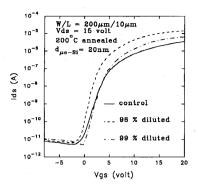

Fig. 2 shows the transfer curves for different devices we made. All the devices have good performances such as small

Fig. 2. Transfer characteristic of the proposed novel thin-film transistor device. Here W is the channel width and L is the channel length for our device

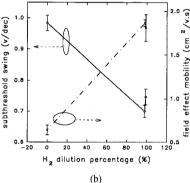

threshold voltage and sharp transition region. The novel structure devices reveal higher current driving capabilities than the control device (conventional a-Si:H TFT's). Indeed, we can make sure that our novel device improves turn-on characteristics with little degradation due to the a-Si:H. On the other hand, turn-off characteristics will not degrade due to the presence of the a-Si:H layer. The a-Si:H layer behaves like two vertical offset regions to block the carrier conduction in the turn-off state, hence the OFF-current can be suppressed as the control device possesses. As shown in Fig. 2, it is found that 98% diluted device has a better performance over 99% diluted device. We believe that some ion-bombardment damages due to the H<sub>2</sub>-plasma etching effect occur. These damages will produce new trap defects which enhance the trap assisted tunneling [11]. The large amount of H<sub>2</sub> dilution will increase the probability of trap defect formation. Hence, the 99% diluted device shows a smaller ON-current than 98% diluted one. In Fig. 2 and Fig. 3(a), the ON/OFF increases from  $7 \times 10^5$  (0% diluted device) to  $5.49 \times 10^6$  (98% diluted device) then drops to  $3.36 \times 10^6$  (99% diluted device). The highest ON-current density is due to less bulk trap density. We have measured and deduced the density of deep gap states  $(N_{\rm deep})$  according to the equation:  $N_{\rm deep}=C_{\rm ins}S(qkt)^{-1}$  decreases from  $4.11\times 10^{12}~cm^{-2}~ev^{-1}$  (0% dilution) to  $2.54 \times 10^{12} \ cm^{-2} \ ev^{-1}$  (98% dilution) then increases to  $2.87 \times 10^{12} \ cm^{-2} \ ev^{-1}$  (99% dilution), where S is the subthreshold swing. From 0% to 98% H<sub>2</sub>-plasma, the annealing effect prevails which fills the dangling bonds in the amorphous film. Then plasma damage occurs beyond 98% to 99% which produces more bulk trap density. This trend of trapped charge occurs simultaneously in the dielectric film. However, the interface trap is monotonically improved by H<sub>2</sub>-plasma. The large amount of H<sub>2</sub> gas fills the growth ambient such that the growth rate for  $\mu$ c-Si:H is very slow. This produces a smooth interface between gate insulator and  $\mu$ c-Si:H. The 98% diluted device has a smaller threshold voltage of 0.74 V, due to less trapped charges, than 1.19 V for the 99% diluted one. In Fig. 3(b), the conductance of 98% diluted  $\mu$ c-Si:H film is superior to 99% diluted  $\mu$ c-Si:H film such that 98% H<sub>2</sub> diluted device has a higher field-effect mobility of 1.87 cm<sup>2</sup>/v·s, presumably due to less interface state scattering, than 99% diluted device of

Fig. 3. The dependence of  $H_2$ -dilution percentage on (a) threshold voltage, ON/OFF current ratio and (b) subthreshold swing, field-effect mobility of the proposed thin-film transistor device.

$1.80~{\rm cm^2/v\cdot s}$  which are measured in the saturated region and deduced from the equation:  $I_{ds}=\mu_{fe}C_{\rm ins}W(V_{gs}-V_{th})^2/2L$ . The subthreshold swing is also relative to the interface state. The smallest subthreshold swing value of 0.70 V/dec occurs on 98% diluted device which is less than that for the 99% diluted device of 0.75 V/dec. In conclusion, we have made the novel structure devices which demonstrate high performance over the conventional a-Si:H TFT's. The 20-nm thick  $\mu$ c-Si:H in our device operates well so far. It maybe further improved by optimizing the  $\mu$ c-Si:H thickness in the future.

## IV. CONCLUSION

We have proposed a novel vertical offset structure device for the first time to improve the thin-film transistor performance. A thin  $\rm H_2$ -diluted  $\mu c$ -Si:H film is used to increase the turn-on driving current which can enhance operation speed while the vertical a-Si:H offset structure can suppress the OFF-current.

# ACKNOWLEDGMENT

The authors would like to thank Dr. T. Y. Huang for his stimulating discussions.

### REFERENCES

- N. Ibaraki, "Technical issues for 40-inch a-Si:H TFT," in AM-LCD'95 Dig., Japan, 1995, pp. 67–70.

- [2] Y. Tsuji, M. Ikeda, Y. Ogawa, and K. Suzuki, "Low resistance Mo-W gate linematerial for a-Si:H TFT-LCD's," in AM-LCD'95 Dig., Japan, 1995, pp. 71–74.

574

- [3] Y. Kaneko, K. Tsutsui, H. Matsumaru, H. Yamamoto, and T. Tsukada, "Amorphorus silicon thin film transistor with a buried double-gate structure," in *IEDM Tech. Dig.*, 1989, pp. 337–340.

[4] Y. Uchida and M. Matsumura, "Short channel a-Si:H thin-film MOS

- transistor," IEEE Trans. Electron Devices, vol. ED-36, pp. 2940-2943,

- [5] Y. Uchida, Y. Nara, and M. Matsumura, "Proposed vertical-type amorphous-silicon field-effect transistor," IEEE Electron Device Lett.,

- vol. EDL-5, pp. 105–107, 1984. [6] T. Y. Huang, I. W. Wu, A. G. Lewis, A. Chiang, and R. H. Bruce, "A simple 100-V polysilicon TFT with improved turn-on characteristics,"

- IEEE Electron Device Lett., vol. 11, pp. 244–246, 1990.

[7] S. S. He and G. Lucovsky, "A low temperature plasma-assisted deposition process for microcrystalline thin film transistor, TFT's," in Mater. Res. Symp. Proc., 1994, vol. 336, pp. 25-30.

- [8] K. C. Hsu, B. Y. Chen, H. T. Hsu, K. C. Wang, T. R. Yew, and H. L.

- Hwang, "Thin film transistor made from hydrogenated microcrystalline silicon," *Jpn. J. Appl. Phys.*, vol. 33, pp. 639–642, 1994.

C. W. Liang, W. C. Chiang, and M. S. Feng, "Microcrystallinity of undoped amorphous silicon film and its effects on the transfer characteristics of thin-film transistor," *Jpn. J. Appl. Phys.*, vol. 34, pp. 5943-5948, 1995.

- [10] C. C. Tsai, G. B. Anderson, and R. Thompson, "Growth of amorphous, microcrystalline, and epitaxial silicon in low temperature plasma deposition," in *Mater. Res. Proc.*, vol. 192, pp. 475–480, 1990. See for example, S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed.

- New York: Wiley, 1981, pp. 440, 442, 447.