## 行政院國家科學委員會專題研究計畫 期中進度報告

## 新式低溫複晶矽薄膜電晶體之結構與技術在電抹除可程式 唯讀記憶體的應用(1/3)

計畫類別: 個別型計畫

計畫編號: NSC94-2215-E-009-064-

執行期間: 94年08月01日至95年07月31日

執行單位: 國立交通大學電子工程學系及電子研究所

計畫主持人: 雷添福

報告類型: 精簡報告

報告附件: 出席國際會議研究心得報告及發表論文

處理方式: 本計畫可公開查詢

中華民國95年5月28日

# 行政院國家科學委員會補助專題研究計畫 ■期中報告

新式低溫複晶矽薄膜電晶體之結構與技術在電抹除可程式 唯讀記憶體的應用(1/3)

| 計畫             | 編號:               | NSC    | 國別型計<br>94−22<br>-8月01 | 15—E-             | -009-            | -064 | _            |             |      |               |  |

|----------------|-------------------|--------|------------------------|-------------------|------------------|------|--------------|-------------|------|---------------|--|

| 計畫             | 主持人               | :雷     | 添福                     | 國立交               | 通大學              | 基電子  | 工程研          | 究所教         | 授    |               |  |

| 成果             | 報告類               | [型(在   | <b>衣經費</b> 核           | <b>泛定清單</b>       | 見規定統             | 激交)  | : <b>二</b> 精 | <b>青簡報告</b> | - □完 | 之整報告          |  |

| □赴<br>□赴<br>■出 | 國外出<br>大陸地<br>席國際 | 差或品出學術 | 以研差會計                  | 得報告<br>習心得<br>得報告 | 一份<br>報告-<br>及發表 | 之論   |              | -份          |      |               |  |

| 處理             | 方式:               | 列管     | 計畫及                    | 下列情               | 形者外              | 、,得  | 立即公          | 開查詢         |      | T究計畫、<br>公開查詢 |  |

| 執行             | 單位:               | 國立     | 交通大                    | 學電子               | 工程研              | 究所   |              |             |      |               |  |

| 中              | 華                 | 民      | 國                      | 95 年              | 05 月             | 31 日 |              |             |      |               |  |

## 行政院國家科學委員會專題研究計畫成果報告

新式低溫複晶矽薄膜電晶體之結構與技術在電抹除可程式 唯讀記憶體的應用(1/3)

# New Structure and Technology of Low-Temperature Poly-Si TFTs for EEPROM Devices Application

計畫編號: NSC 94-2215-E-009-064

執行期限:94年8月1日至95年7月31日 主持人:雷添福 交通大學電子研究所教授

#### 一、中文摘要

利用複晶矽薄膜電晶體製作畫素元件 及週邊驅動電路於大面積玻璃基板並積體 化已是未來製作平面主動式陣列液晶顯示 器的趨勢。除了驅動電路外,低溫複晶矽 薄膜可電抹除可電程式唯讀記憶體更被認 為可以將系統一起整合至面板上,達成系 統面板(System-On-Panel)的夢想。

本期中報告中我們研究發展新穎鍺記憶捕獲層與矽/氧化矽/氮化矽/氧化矽/勾(SONOS)兩種記憶體電容技術應用於低溫複晶矽薄膜記憶體元件上。

緒捕獲層複晶矽薄膜記憶體元件利用 緒取代矽當作載子捕獲層的材料,鍺因具 有低溫沉積與再結晶特性,非常適合使用 在複晶矽薄膜電晶體中。本計劃研究鍺捕 獲層複晶矽薄膜記憶體元件的可行性;由 於鍺比矽具有較深的捕陷電荷能量深度 (Trapping Energy Level),預期有易捕陷電 荷與電荷捕捉效率高的特性,可增加電荷 的保存能力,預期此元件能有良好的資料 的持久性(Data retention) 以及高寫入、抹 除操作忍耐力 (Endurance)。

關鍵詞:複晶矽薄膜電晶體;可電抹除可電程式唯讀記憶體;鍺捕獲層;矽/氧化矽/ 氮化矽/氧化矽-矽;寫入抹除操作忍耐力。

#### **Abstract:**

Utilizing polycrystalline silicon thin film transistors (Poly-Si TFTs) as on-glass pixel switch element and peripheral coupling is the future trend for fabricating active - matrix liquid-crystal displays (AMLCD's). In addition to driving circuits, it is believed that all system can be integrated to panel using low temperature poly-Si thin film transistor. Poly-Si TFT EEPROMs are very attractive in nonvolatile poly-Si thin film memory devices application.

In this report, we have developed the novel germanium (Ge) memory trapping layer and Si/SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub>/Si (SONOS) capacitor technologies to fabricate nonvolatile poly-Si thin film memory devices.

We replace silicon (Si) floating gate with germanium (Ge) trapping layer in the poly-Si thin film memory devices. Ge is suitable for poly-Si thin film memory because low recrystallization temperature and deep trapping energy level. In this report, we propose that poly-Si TFT EEPROMs with Ge trapping layer have the improved data retention and high program/erase endurance.

**Keywords**: Poly-Si TFTs, EEPROMs, Germanium trapping layer, SONOS, Endurance.

#### 二、緣由與目的

關於複晶矽薄膜電晶體應用在非揮發記憶體方面,除了電晶體本身特性外,還有其他的更大困難需要克服。其中包括記憶體元件結構的設計,載子捕獲材料(Trapping Layer)之選擇與沉積方式,元件製程之開發...等等。

複晶矽薄膜電晶體之記憶體元件 (Poly-Si TFT EEPROMs)的實現只要取決 於薄膜電晶體特性、記憶體元件結構,捕 獲材料(Trapping Layer)之選擇與沉積,元 件製程技術開發等四項。其中,製程溫度 將是最大的挑戰,低溫複晶矽薄膜電晶體 之製程溫度受限於玻璃基版,必須降到攝 氏六百度以下。在這樣低溫下,要沉積高 品質的薄膜材料是一個很大的挑戰。元件 是否具有高記憶忍耐力取決於穿隧閘極氧 化層的品質,所以低溫成長高品質穿隧閘 極氧化層的將是未來熱門的研究重心。未 來我們能否發展出於低溫複晶矽薄膜成長 高品質穿隧閘極氧化層之關鍵製程,將是 薄膜電晶體可電抹除可電程式唯讀記憶體 能否實際應用的最大挑戰。

除了低溫成長高品質之穿隧閘極氧化層外,選擇具有夠深的捕陷電荷能量深度之載子捕獲材料是非常重要的,我們研究發展鍺捕獲層(Ge trapping layer)與矽/氧化矽/氮化矽/氧化矽/矽(SONOS)兩種記憶體元件技術在低溫複晶矽薄膜電晶體可電抹除可電程式唯讀記憶體之可行性[1]。另外,其他具有較深的捕陷電荷能量深度(Trap Energy Level)之材料,如高介電常數絕緣材料(high-k dielectric) [2],也可能會加入未來之研究,同時研究發展新的元件結構以解決薄膜電晶體可能遭遇的高漏電情形。

本次報告中,我們發展鍺為捕獲材料 之鍺捕獲層複晶矽薄膜記憶體元件技術, 將傳統堆疊閘極結構式複晶矽薄膜電晶體 的矽浮接閘極換成鍺捕獲層;由於鍺容易 在高溫揮發與結晶,在晶片清潔時容易長

出易溶於水之氧化物,所以一直不能應用 於需要高溫之製程元件中,所以鍺在低溫 複晶矽電晶體的應用是非常值得進一步研 究的。鍺捕獲層複晶矽薄膜記憶體元件 (Poly-Si thin film memory devices with Ge trapping layer )利用鍺取代矽當作載子捕獲 的材料,鍺因具有低溫沉積與再結晶特 性,非常適合使用在複晶矽薄膜電晶體 中。本次報告研究鍺捕獲層在複晶矽薄膜 記憶體元件的可行性,我們首先在矽基板 上成功製作出鍺捕獲層記憶體電容,由於 鍺比矽具有較深的捕陷電荷能量深度 (Trapping Energy Level),有易捕陷電荷與 電荷捕捉效率高的特性並增加電荷的保存 能力,此元件能有良好的資料的持久性 (Data retention) 以及高寫入、抹除操作忍 耐力 (Endurance)[3]。

另外,我們亦設計未來新的低溫複晶薄膜電晶體可電抹除可電程式唯讀記憶體元件結構:具氧/氮/氧捕獲層之堆疊式矽/鍺T型閘極複晶矽薄膜電晶體(Stacked Si/Ge T-Gate Poly-Si TFTs with ONO trapping layer):此元件靠近汲極/源極兩端之閘極介電層是沉積氧化矽/氮化矽/氧化矽(ONO)之捕獲材料,可將電子捕獲在靠近汲極/源極兩端之閘極介電層之堆疊式矽/鍺T型閘極複晶矽薄膜電晶體是利用靠近汲極/源極兩端之閘極介電層厚度增加來降低閘極之垂直電場,進而使汲極端的橫向電場降低並減少通道關閉漏電流(Off-current)而不會使通道導通電流(On-current)明顯減少[4],[5]。

我們預期完成的複晶矽薄膜電晶體是 具有汲極遠離閘極結構(Offset TFTs)般低 的通道關閉漏電流(Off-current)與傳統元件 般高的通道導通電流(On-current),所以此 元件適合於一般的驅動電路元件,而當成 記憶體操作時能有良好的程式-抹除窗口 (program-erase windows),因為同時可當作 驅動電路元件與記憶體元件,非常適合在 未來系統面板整合上。

#### 三、結果與討論

#### (1)鍺捕獲層記憶體電容製作與特性

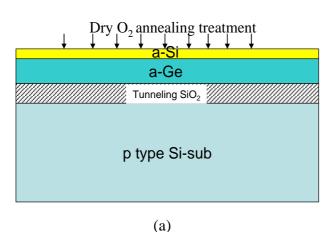

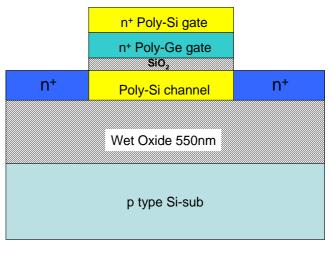

圖一是豬捕獲層記憶體電容結構製程流程而意圖,為了探討豬捕獲層的載子捕獲的載子捕獲的,我們先在ptype矽基板上成長高的質的熱二氧化矽穿隧(tunneling)層別數一個人類,我們在了一個人類,為了所有人。 在空氣中氧化。如果在一個人類,為了所有。 在空氣中氧化,我們在豬之上又沉積將一個人。 一個人。在一個人。在一個人。在一個人。 一個人。在一個人。在一個人。在一個人。 一個人。在一個人。在一個人。 一個人。在一個人。 一個人。在一個人。 一個人。 一個人

(b)

圖一 鍺捕獲層記憶體電容結構製程 流程示意圖

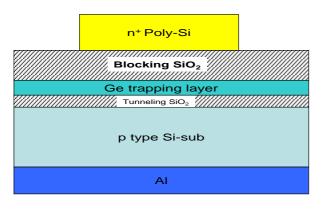

捕獲層之處理後,接著利用低壓化學氣相 沉積爐管來沉積覆蓋於鍺捕獲層上方之阻 障氧化層(blocking oxide),此阻障氧化層 的目的是防止電子從上電極注入/拉出,影 響在鍺捕獲層中已儲存電子的狀態,多餘 的電子注入或拉出會使得記憶狀態(0或1) 誤判;最後,成長複晶矽 n<sup>+</sup>上電極(poly-Si n<sup>+</sup> gate)與鋁下電極,完成的電容結構見圖 一(b)。

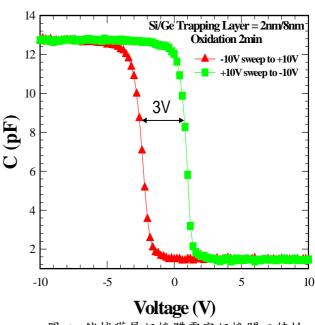

圖二為實際量測到的鍺捕獲層記憶體電容之特性曲線圖,寫入是以掃描電壓+10V到-10V,而抹除是掃描電壓-10V到+10V,由圖可看出其記憶開口(memory window)電壓大小約 3V,由此可證明此鍺捕獲層能有效地捕獲載子(電子或電洞),造成電容的平帶電壓(flatband voltage)向正電壓移動或向負電壓移動的記憶結果。

圖二 鍺捕獲層記憶體電容記憶開口特性 曲線圖

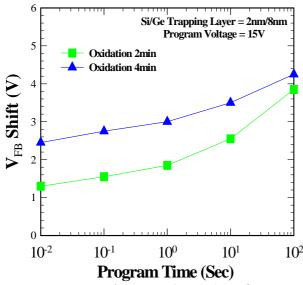

圖三是鍺捕獲層記憶體電容寫入時間對平帶電壓改變量關係特性曲線,此記憶體電容的寫入的方式是以FN-穿隧機制 (Fowler-Nordheim tunnel)來完成。 圖中可看出當氧化時間適當長時,其寫入的平帶電壓將會有較大的改變量,在相同寫入的條件下,也具有較快的寫入速度。這可能

是因為當氧化夠長時,透過乾氧使得鍺與 矽的分離析出越明顯,鍺捕獲層品質將會 得到改善。

圖三 鍺捕獲層記憶體電容寫入時間對 平帶電壓改變量關係特性曲線

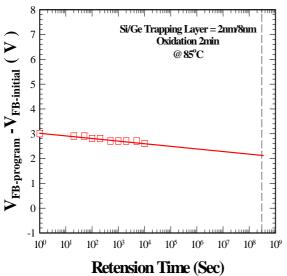

圖四是緒捕獲層記憶體電容於85°C下量測之資料持久度(data retention)特性曲線,當溫度升高時,原本儲存於捕獲層的載子容易因為受熱獲得能量而躍過二氧氧化矽穿隧層位能障,造成記憶資料的流失,其記憶開口將會漸漸縮小,當記憶捕獲層具有較深的捕陷電荷能量深度時,其高溫之資料持久度表現將會越好,圖中可看出此鍺捕獲層記憶體電容具有相當不錯的高溫資料持久度表現。

圖四 鍺捕獲層記憶體電容於 85°C 下 量測之資料持久度特性曲線

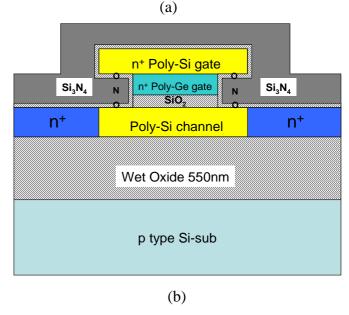

# (2) 具氧/氮/氧捕獲層之堆疊式矽/绪 T 型 閘極複晶矽薄膜電晶體

圖五 具氧/氮/氧捕獲層之堆疊式矽/鍺 T 型閘 極複晶矽薄膜電晶體製程流程示意圖

就失去對通道的控制能力,而整體閘極的 阻抗也會相對地變大,元件的臨界電壓也 會相對地變大。

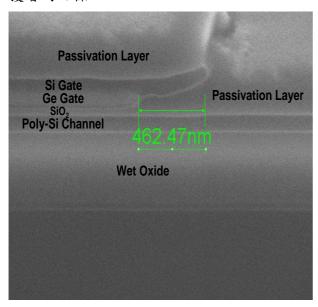

定義出閘極後,見圖五(a),接著做鍺側 向過蝕刻的步驟,我們是利用矽/鍺對蝕刻 溶液選擇比的不同來達成,此元件的成敗 與否就在鍺過蝕刻的控制; 過蝕刻步驟之 後完成汲極/源極 n<sup>+</sup>離子佈值與汲極/源極 活化,進行清洗步驟後依序沉積氧化矽 (10nm) 與 氮 化 矽 (200~300nm) 披 覆 層 (passivation layer)來完成氧/氮/氧捕獲 層,最後做金屬連線步驟,元件即可完成, 見圖五(b)。圖六是實際完成的元件剖面結 構掃瞄式電子顯微鏡影像圖(scanning electron microscope- SEM), 由圖我們可以 清楚地看到閘極是呈T型,而此T型閘極 是由矽/鍺堆疊所完成的,這證明我們成功 地完成堆疊式矽/绪T型閘極;除此之外, 鍺的側向過蝕刻也被證明能得到良好的控 制度,圖中的鍺側向過蝕刻距離約為 460nm,適當的過蝕刻距離可以降低元件的 關閉漏電流,進而使氧/氮/氧捕獲層能填 充到所設計的閘極左右兩端正下方位置, 達到載子儲存在閘極左右兩端氧/氮/氧捕 獲層的目標。

複晶矽薄膜電晶體之剖面結構 SEM 圖

在未來下一年的研究中,具氧/氮/氧 捕獲層之T型閘極元件將被實際製作出來 並量測其記憶體特性,預期將有良好的資 料的持久性以及高寫入、抹除操作忍耐力。 四、成果自評

本次計畫之執行,皆達預期成果,並 已在相關學術期刊上發表論述,茲列於下:

- [1]Shieh M.S., Chen P.S., Tsai M.J., Lei T.F., "The CMP process and cleaning solution for planarization of strain-relaxed SiGe virtual substrates in MOSFET applications," Journal of The Electrochemical Society, Vol.153 Issue 2, pp. G144-G148, 2006.

- [2]You H.C., Ko F.H., Lei T.F., "Fullereneincorporation for enhancing the electron beam resist performance for contact hole patterning and filling," Thin Solid Films, vol. 500, pp. 214-218, Apr. 2006.

- [3]Lin Y.H., Chien C.H., Lin C.T., Chang C.Y., Lei **T.F.**, "Novel two-bit HfO<sub>2</sub> nanocrystal nonvolatile flash memory," IEEE Transactions on Electron Devices, vol. 53, no. 4, pp.782-789, Apr., 2006.

- [4]Kuo P.Y., Chao T.S., Wang R.J., Lei T.F., "High-performance poly-Si TFTs with fully Ni-self-aligned silicided S/D and gate structure," IEEE Electronics Device Letters, vol. 27, no. 4, pp 258-261, Apr., 2006.

- [5]You H.C., Fu H. K., Lei T.F., " Physical characterization and electrical properties of sol-gel-derived zirconia films," Journal of The Electrochemical Society, vol.153 Issue 6, pp. F94-F99, 2006.

#### 五、參考文獻

- [1] Reisinger H., et al., in Symp. VLSI Tech. Digest, pp. 113-114,1997.

- [2] Lin Y.H., et al., IEEE Trans. Electron Devices, vol.53, no.4, pp.782-789, 2006.

- [3] Chen J.H., et al., IEEE Trans. Electron Devices, vol51, no.11,pp.1840-1848,2004.

- 圖六 具氧/氮/氧捕獲層之堆疊式矽/鍺 T 型閘極 [4]Lin H.C. et al.,IEEE Electron Device Letters, vol. 22, no.1,2001.

- [5]Kurimoto K., et al.in IEDM Tech.Digest. pp.541-544, 1991.