# Temperature-Dependent Remote-Coulomb-Limited Electron Mobility in n<sup>+</sup>-Polysilicon Ultrathin Gate Oxide nMOSFETs

Ming-Jer Chen, Senior Member, IEEE, Sou-Chi Chang, Shin-Jiun Kuang, Chien-Chih Lee, Student Member, IEEE, Wei-Han Lee, Student Member, IEEE, Kuan-Hao Cheng, and Yi-Hsien Zhan

Abstract-Additional electron mobility due to remote scatterers in n<sup>+</sup>-polysilicon 1.65-nm gate oxide (SiO<sub>2</sub>) n-channel metal-oxide-semiconductor field-effect transistors is experimentally extracted at three different temperatures (i.e., 233, 263, and 298 K). The core of the extraction process consists of simulated temperature-dependent universal mobility curves and Matthiessen's rule in a mobility universality region. Resulting additional mobility for the first time experimentally exhibits a negative temperature coefficient, confirming interface plasmons in a polysilicon depletion region to be dominant remote Coulomb scatterers. We also present corroborative evidence as quoted in the literature, including: 1) calculated temperature-dependent remote Coulomb mobility due to ionized impurity atoms in a polysilicon depletion region; 2) experimentally assessed additional mobility at room temperature; and 3) simulated remote Coulomb mobility due to interface plasmons in a polysilicon depletion region as well as its temperature coefficient. Validity of Matthiessen's rule used in this paper is verified.

Index Terms—Gate oxide, high-k, interface plasmons, metal gate, mobility, metal—oxide—semiconductor field-effect transistors (MOSFETs), phonons, polysilicon, remote Coulomb, scattering, surface roughness.

# I. INTRODUCTION

N n<sup>+</sup>-polysilicon gate oxide n-channel metal-oxide—semiconductor field-effect transistors (nMOSFETs), Takagi *et al.* [1] have experimentally found that inversion layer electron mobility is a combination of three distinct scattering mechanisms: 1) Coulomb scattering due to ionized impurity atoms in a substrate; 2) acoustic-optical phonon scattering in an inversion layer; and 3) surface roughness scattering

Manuscript received October 21, 2010; revised December 2, 2010 and January 6, 2011; accepted January 12, 2011. Date of publication February 14, 2011; date of current version March 23, 2011. This work was supported by the National Science Council of Taiwan under Contract NSC 98-2221-E-009-164-MY3. The review of this paper was arranged by Editor M. J. Kumar.

- M.-J. Chen is with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan...

- S.-C. Chang is with the Department of Electrical Engineering and Computer Science, University of Michigan, Ann Arbor, MI 48109 USA.

- S.-J. Kuang, C.-C. Lee, and W.-H. Lee are with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: chenmj@faculty.nctu.edu.tw).

- K.-H. Cheng is with the Ministry of Defense, Taipei 100, Taiwan.

- Y.-H. Zhan is with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan. He is also with the Ministry of Defense, Taipei 100, Taiwan.

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2107519

near a SiO<sub>2</sub>/Si interface. However, mobility degradation was frequently encountered in a scaling direction, which means that additional scattering mechanisms exist. On the one hand, electron plasmons in a source/drain highly doped region can be significant according to Fischetti and Laux [2], as demonstrated in recent experiments by Cros *et al.* [3] and Barral *et al.* [4], [5]. On the other hand, degraded mobility with decreasing gate oxide thickness has been observed, particularly in moderate and high vertical effective field regions [6]–[8]. Because a long-channel device was used in mobility measurement [6]–[8], hence, the effect of source/drain electron plasmons can be insignificant; scattering mechanisms responsible for observed mobility degradation should in principle stem from scatterers in a remote region situated away from that of Takagi *et al.* [1].

However, origins of remote scatterers remained controversial in the past decades [7], [9]–[12]. In the beginning, Krishnan et al. [9] ascribed remote scattering to ionized impurity atoms in a polysilicon depletion region. Following that, Yang et al. [7] applied a remote Coulomb mobility model due to Stern and Howard [13] and found that corresponding remote Coulomb scattering (RCS) is too weak to constitute measured mobility degradation. In contrast, Fischetti [10] favored electron counterparts in a polysilicon depletion region, which can act as plasmons at a poly/SiO2 interface. Excitation and absorption of interface plasmons will further affect underlying 2-D electrons via long-range Coulomb interactions, a well-known phenomenon also called the Coulomb drag effect [14]. Simulated remote Coulomb mobility in a coupled interface plasmons/inversion layer system [10], [15] appeared to elucidate observed mobility degradation in [7] and [8]. In addition, the remainder of remote scatterers such as remote surface roughness [16] received somewhat attention [11], [12]. Through Monte Carlo simulation, Gámiz and Roldan [11] argued that remote surface roughness scattering is insignificant in moderate and high vertical electric field regions.

Recently, there have been two specially designed experiments concerning validity of an interface plasmon or a drag hypothesis [17], [18]. Again, these two experiments led to controversial arguments. In the first experiment dedicated to drag measurement, Solomon and Yang [17] claimed that in a gate oxide thickness range of 1.9-2.5 nm, interface plasmons in a polysilicon region did not appear to explain oxidescaling-induced mobility degradation. Oppositely, throughout a calibrated C-V splitting technique, the second experiment by Lime *et al.* [18] pointed out that mobility degradation is not due

to increased surface roughness but due to interface plasmons, which is valid for gate oxide thicknesses down to 1.2 nm.

Thus, reexamination of remote scattering sources in polysilicon ultrathin gate oxide nMOSFETs is essential and crucial. Additionally, it is worth noticing that the aforementioned experiments [6]–[8], [17], [18] were all conducted at room temperature only. In other words, so far, temperature dependence of remote scattering mechanisms was not experimentally taken into account in the case of polysilicon ultrathin SiO<sub>2</sub> gate stacks. However, a temperature-dependent experiment was shown to be useful in an analysis of remote scatterers in high-k gate stacks [19]–[21].

In this paper, we elaborate on a temperature-oriented experimental method dedicated to polysilicon ultrathin gate oxide stacks. The core of the method comprises two main parts: simulated temperature-dependent universal mobility curves, without conventional thick gate oxide test vehicle fabrication [6]–[8], [17], [18], and Matthiessen's rule, particularly in a mobility universality region. Additional scattering of inversion layer electrons by remote scatterers in a polysilicon region can straightforwardly be assessed. For the first time, temperature dependence of additional mobility is experimentally obtained, making possible the clarification of remote scattering mechanisms. In addition, presented is corroborative evidence in terms of a remote Coulomb mobility model, as cited in [7]; simulated values of the additional mobility and its temperature coefficient, as drawn from [10]; and experimental mobility degradation data at room temperature as available elsewhere [6]-[8]. Validity of Matthiessen's rule used in this paper is addressed as well.

# II. EXPERIMENT, VALIDATION, AND EXTRACTION

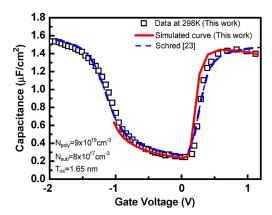

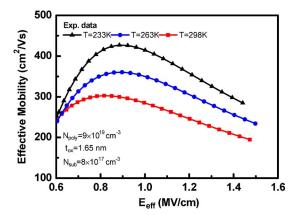

An n-channel device under test was fabricated in a conventional 90-nm process. In this process, a SiO<sub>2</sub> film was thermally grown, followed by NO annealing. A measured C-V characteristic is depicted in Fig. 1. A self-consistent Schrödinger and Poisson's equation solver, as constructed elsewhere [22], was employed to fit the C-V data, leading to the following process parameters of the device: the n<sup>+</sup>-polysilicon doping concentration  $N_{\text{poly}} = 9 \times 10^{19} \text{ cm}^{-3}$ , the gate oxide thickness  $t_{\rm ox} = 1.65$  nm, and the p-type substrate doping concentration  $N_{\mathrm{sub}} = 8 \times 10^{17} \mathrm{~cm^{-3}}$ . The fitting quality, as demonstrated in Fig. 1, is good. In addition, shown in the figure for comparison is another fitting line by the available self-consistent Schrödinger and Poisson's equations solver Schred [23], with the same process parameters as inputs. The channel width and length of the device had the same value of 10  $\mu$ m. Inversion layer mobility was measured using a conductance method [1] over two  $V_D$  points of 10 and 25 mV. Measured effective mobility is plotted in Fig. 2 versus the vertical effective electric field  $E_{\rm eff}$  for three measurement temperatures of 233, 263, and 298 K. Here, the formula  $E_{\rm eff} = q(0.5N_{\rm inv} + N_{\rm dep})/\varepsilon_s$  was used, in which  $\varepsilon_s$  is the silicon permittivity, and the inversion layer electron density  $N_{\rm inv}$  and the depleted bulk density  $N_{\rm dep}$ were both obtained through self-consistent Schrödinger and Poisson's equations solving [22].

To produce temperature-dependent universal mobility curves, we performed the self-consistent Schrödinger and Poisson's

Fig. 1. Comparison of the measured (symbol) and simulated (lines) gate capacitance versus gate voltage. The lines came from the self-consistent Schrödinger and Poisson's equation solvers [22], [23].

Fig. 2. Measured electron effective mobility (solid lines with symbols) versus vertical effective electric field for the three temperatures.

equations solving [22] to deliver subband levels and wave functions. Straightforwardly, universal mobility was calculated based on published formalisms of both phonon scattering and surface roughness scattering [24], [25]. Material parameters used were all the same as or close to those in [26]–[28], e.g., the acoustic deformation potential  $D_{\rm ac}=12$  eV, the deformation potential of the kth intervalley phonon  $D_k=8\times 10^8$  eV/cm, the energy of the kth intervalley f-type phonon  $E_{k(f)}=59$  meV, and the energy of the kth intervalley g-type phonon  $E_{k(g)}=63$  meV. In a universal mobility calculation, the following formula was used:

$$\frac{1}{\mu_{\text{univ}}^i} = \left\langle \frac{1}{\mu_{\text{ph}}^i(E)} + \frac{1}{\mu_{\text{sr}}^i(E)} \right\rangle \tag{1}$$

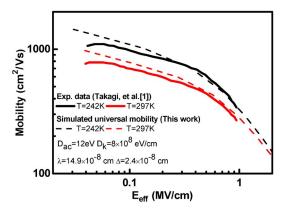

where  $\mu^i_{\mathrm{univ}}$  is the universal mobility of the subband i due to phonon and surface roughness scattering mechanisms, and brackets  $\langle \rangle$  represent averaging over energy for the microscopic phonon mobility  $\mu^i_{\mathrm{ph}}$  and the surface roughness mobility  $\mu^i_{\mathrm{sr}}$ . Detailed simulation work can be found elsewhere [22]. The resulting universal mobility for a correlation length of the surface roughness  $\lambda$  of 14.9 Å and a root mean square height of the surface roughness amplitude  $\Delta$  of 2.4 Å was found to fit the experimental data well for two different temperatures [1], as depicted in Fig. 3. This confirms the validity of the temperature-dependent universal mobility simulation work. Since different manufacturing processes may lead to different mobility

Fig. 3. Comparison of the experimental (solid lines) electron universal mobility curves for two temperatures of 242 and 297 K [1] with the simulated ones in this paper (dotted lines).

universality [29], the varying surface roughness amplitude  $\Delta$ , with the other material parameters kept unchanged, was taken into account. Subsequently, we quoted a physically based Coulomb-limited mobility model due to ionized impurity atoms in a substrate [30] as follows:

$$\mu_C = \frac{1.1 \times 10^{21} T_n^{1.5}}{\ln\left(1 + \gamma_{\rm BH}^2\right) - \frac{\gamma_{\rm BH}^2}{1 + \gamma_{\rm BH}^2}} \frac{1}{N_{\rm sub}}$$

(2)

where  $\gamma_{\rm BH}^2 (= (2\times 10^{19}/N_{\rm inv}/z)T_n^2)$  is the Brooks–Herring coefficient,  $T_n (= T/300~{\rm K})$  is the normalized temperature T with respect to 300 K, and z is the average inversion layer thickness as can be determined by simulated wave functions. Consequently, the thick oxide effective mobility can be obtained according to Matthiessen's rule as

$$\frac{1}{\mu_{\text{thick}}} = \frac{1}{\mu_C} + \frac{1}{\mu_{\text{univ}}}.$$

(3)

Care must be taken while experimentally applying Matthiessen's rule [31], [32]. This issue will be addressed later.

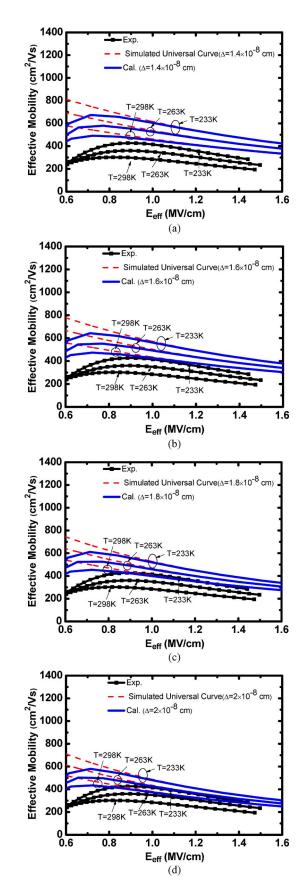

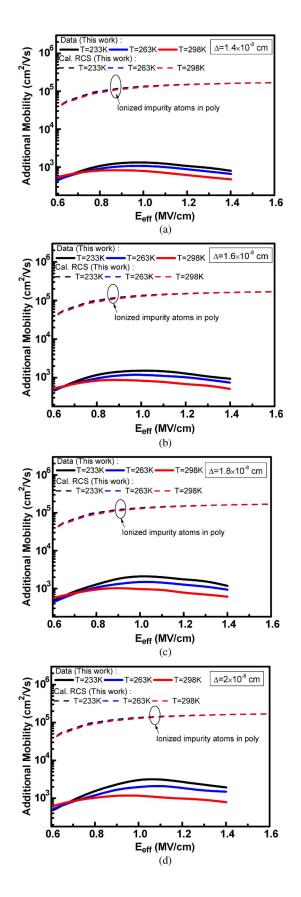

With the aforementioned process parameters as inputs, thick oxide effective mobility was obtained for three temperatures of 233, 263, and 298 K, as plotted in Fig. 4, versus  $E_{\rm eff}$  for  $\Delta$  of 1.4, 1.6, 1.8, and 2 Å. It can be seen that for  $E_{\rm eff}>0.7$  MV/cm, the calculated effective mobility approaches the universal one, as expected. While comparing the measured effective mobility  $\mu_{\rm eff}$  in the figure, the additional scattering of inversion layer electrons by remote scatterers in the polysilicon region can be assessed according to Matthiessen's rule as follows:

$$\frac{1}{\mu_{\text{eff}}} = \frac{1}{\mu_{\text{thick}}} + \frac{1}{\mu_{\text{add}}} \tag{4}$$

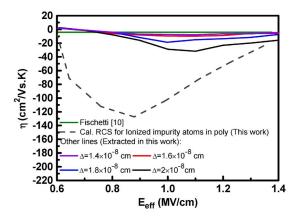

where  $\mu_{\rm thick}$  is the thick gate oxide mobility in the absence of remote scatterers, and  $\mu_{\rm add}$  is the additional mobility caused solely by remote scatterers. Again, the validity of (4) will be treated later. The resulting additional mobility values are shown in Fig. 5 for the three temperatures versus  $E_{\rm eff}$  with the surface roughness amplitude  $\Delta$  as a parameter. In addition, produced simultaneously is the temperature coefficient  $\eta$ , as defined by

$$\eta = \frac{\mu_{\text{add}}(233 \text{ K}) - \mu_{\text{add}}(298 \text{ K})}{233 \text{ K} - 298 \text{ K}}.$$

(5)

Fig. 4. Calculated effective mobility (solid lines), simulated universal mobility curves (dotted lines), and measured effective mobility (lines with symbols) for the three temperatures of 233, 263, and 298 K, plotted versus vertical effective electric field for (a)  $\Delta=1.4$  Å, (b)  $\Delta=1.6$  Å, (c)  $\Delta=1.8$  Å, and (d)  $\Delta=2$  Å.

Fig. 5. Experimentally assessed additional mobility for the three temperatures, plotted versus the vertical effective electric field for (a)  $\Delta=1.4$  Å, (b)  $\Delta=1.6$  Å, (c)  $\Delta=1.8$  Å, and (d)  $\Delta=2$  Å. In addition, shown is the calculated RCS-limited mobility (dotted lines) due to ionized impurity atoms in a polysilicon depletion region for three different temperatures.

Fig. 6. Comparison of the temperature coefficient of the extracted additional mobility (solid lines) in this paper with that of the calculated RCS-limited mobility (dotted lines) due to ionized impurity atoms in a polysilicon depletion region. In addition, labeled is the possible range where the simulated temperature coefficient [10] yielded a value of  $-4.15\ {\rm cm^2/V\cdot s\cdot K}.$

The calculated temperature coefficient  $\eta$  is given in Fig. 6, plotted versus  $E_{\rm eff}$  for different  $\Delta$  values.

### III. ORIGIN AND EVIDENCE

From Fig. 5, it can be seen that in a universal mobility dominant region, as aforementioned  $(E_{\rm eff}>0.7~{\rm MV/cm}),$  additional mobility increases with decreasing temperature, regardless of  $\Delta$  used. This constitutes the merits of the proposed method, without the knowledge of realistic surface roughness parameters. We attribute the observed increasing trend with decreasing temperature to interface plasmons [6] in the presence of electrons in a polysilicon depletion region. The explanations are given below.

First, a positive temperature coefficient may be expected for ionized impurity atoms in a poly side, but owing to decreased screening with increasing temperature, the trend is likely to be reversed [30]. To examine this, we quoted the detailed formula by Yang *et al.* [7] to calculate remote-Coulomb-limited mobility due to ionized impurity atoms in a polysilicon depletion region. The results are separately plotted in Figs. 5 and 6. Fig. 5 clearly points out that the calculated remote-Coulomb-limited mobility due to ionized impurity atoms in a poly side is around two orders of magnitude larger than the experimentally extracted one. In Fig. 6, the calculated  $\eta$  value due to ionized impurity atoms in a polysilicon depletion region also exhibits a large discrepancy. Thus, we must rule out the possibility of ionized impurity atoms in a polysilicon depletion region.

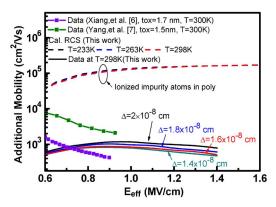

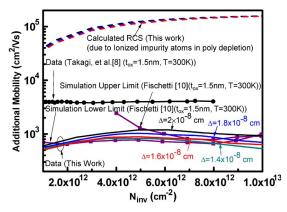

Then, remote surface roughness scattering can be insignificant in a mobility universality dominant region ( $E_{\rm eff}>0.7~{\rm MV/cm}$ ), as drawn from the Monte Carlo simulation by Gámiz et al. [11]. Thus, the origin of mobility degradation in this paper is determined to be interface plasmons [6]. This is reasonable because an increase in temperature can enhance absorption and emission of interface plasmons, which will in turn reduce inversion layer mobility. Extra evidence does exist. First, the published experimental [6]–[8] and simulated [10] mobility degradation values at room temperature [6]–[8] can deliver the additional mobility for comparison, as shown in Figs. 7 and 8. In the two figures, one can see that these additional mobility data created from different sources [6]–[8], [10] are all

Fig. 7. Comparison of the experimentally extracted additional mobility (solid lines) near room temperature versus the effective field with that (lines with symbols) of [6] and [7]. In addition, shown is the calculated RCS-limited mobility (dotted lines) for the three different temperatures due to ionized impurity atoms in a polysilicon depletion region.

Fig. 8. Comparison of the experimentally assessed additional mobility (solid lines) near room temperature, plotted versus inversion layer electron density, with the simulated (lines with squares) remote-Coulomb-limited mobility due to interface plasmons [10], the experimentally extracted (line with circle) additional mobility from [8], and the calculated RCS-limited mobility (dotted lines for the three different temperatures) due to ionized impurity atoms in a polysilicon depletion region.

comparable with or close to ours, within the error of Matthiessen's rule, as will be explained later. In addition, it is noteworthy that the calculated remote Coulomb limited mobility due to ionized impurity atoms in a polysilicon depletion region is still too large to match the data [6]–[8], [10]. Particularly, we noticed that in the simulation study by Fischetti [10], simulated temperature-dependent mobility was available but only under limited conditions: the average electron density  $n_g$  of  $3\times 10^{19}~{\rm cm}^{-3}$ , the inversion layer electron density  $N_{\rm inv}$  of  $10^{13}~{\rm cm}^{-2}$ , and the gate oxide thickness  $t_{\rm ox}$  of 1 nm. The corresponding  $\eta$  value was estimated to be  $-4.15~{\rm cm}^2/{\rm V}\cdot{\rm s}\cdot{\rm K}$  using the extracted values in [10]:  $\mu(233~{\rm K})\sim 900~{\rm cm}^2/{\rm Vs}$  and  $\mu(298~{\rm K})\sim 630~{\rm cm}^2/{\rm Vs}$ . Strikingly, this value obtained in the context of interface plasmons is quite close to ours as long as the  $\Delta$  value is smaller than 1.8 Å, as demonstrated in Fig. 6.

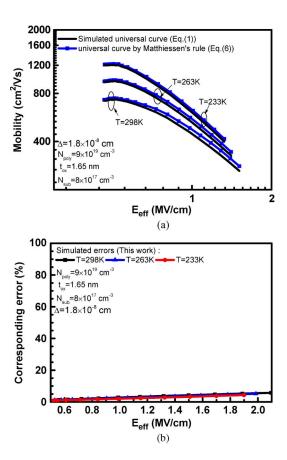

Finally, we want to stress that the use of Matthiessen's rule in this paper is adequate. The primary reasons are that this paper is focused on a high  $E_{\rm eff}$  value. To give a quantitative estimate of the error, extra work was done in calculating universal mobility according to Matthiessen's rule as follows:

$$\frac{1}{\mu_{\text{univ}}^{i}} = \left\langle \frac{1}{\mu_{\text{ph}}^{i}(E)} \right\rangle + \left\langle \frac{1}{\mu_{\text{sr}}^{i}(E)} \right\rangle. \tag{6}$$

Fig. 9. (a) Comparison of the simulated universal mobility from two different formalisms (1) and (6), plotted versus  $E_{\rm eff}$  with temperature as a parameter, and (b) the corresponding errors.

The results are given in Fig. 9 for comparison with those of (1), which are plotted versus  $E_{\rm eff}$  with temperature as a parameter. Evidently, the maximum error of the universal mobility caused by the use of Matthiessen's rule is below merely 5%. This error is much less than the relative difference between the measured effective mobility and the simulated universal mobility in Fig. 3. Thus, the validity of Matthiessen's rule used in this paper is verified. Straightforwardly, the induced error may lead to the uncertainty of the extracted additional mobility. In this sense, the additional mobility data created from different sources [6]–[8], [10] all fall within the error of Matthiessen's rule.

## IV. CONCLUSION

We have experimentally extracted the temperature-dependent additional electron mobility due to remote scatterers in  $n^+$ -polysilicon ultrathin gate oxide nMOSFETs. Experimentally validated temperature-dependent universal mobility simulation has been highlighted. The resulting additional mobility has exhibited a negative temperature coefficient for the first time, thus confirming interface plasmons in a polysilicon depletion region to be the underlying remote Coulomb scatterers. The experimental and simulation evidence, as quoted in the open literature, has been demonstrated. The validity of Matthiessen's rule used in this paper has been verified.

### REFERENCES

- [1] S. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the universality of inversion layer mobility in Si MOSFETs: Part I—Effects of substrate impurity concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, Dec. 1994.

- [2] M. V. Fischetti and S. E. Laux, "Long-range Coulomb interactions in small Si devices. Part I: Performance and reliability," *J. Appl. Phys.*, vol. 89, no. 2, pp. 1205–1231, Jan. 2001.

- [3] A. Cros, K. Romanjek, D. Fleury, S. Harrison, R. Cerutti, P. Coronel, B. Dumont, A. Pouydebasque, R. Wacquez, B. Duriez, R. Gwoziecki, F. Boeuf, H. Brut, G. Ghibaudo, and T. Skotnicki, "Unexpected mobility degradation for very short devices: A new challenge for CMOS scaling," in *IEDM Tech. Dig.*, 2006, pp. 663–666.

- [4] V. Barral, T. Poiroux, J. Saint-Martin, D. Munteanu, J.-L. Autran, and S. Deleonibus, "Experimental investigation on the quasi-ballistic transport: Part I—Determination of a new backscattering coefficient extraction methodology," *IEEE Trans. Electron Devices*, vol. 56, no. 3, pp. 408–419, Mar. 2009.

- [5] V. Barral, T. Poiroux, D. Munteanu, J.-L. Autran, and S. Deleonibus, "Experimental investigation on the quasi-ballistic transport: Part II— Backscattering coefficient extraction and link with the mobility," *IEEE Trans. Electron Devices*, vol. 56, no. 3, pp. 420–430, Mar. 2009.

- [6] Q. Xiang, G. Yeap, D. Bang, M. Song, K. Ahmed, E. Ibok, and M. R. Lin, "Performance and reliability of sub-100 nm MOSFETs with ultra thin direct tunneling gate oxides," in *VLSI Symp. Tech. Dig.*, Jun. 1998, pp. 160–161.

- [7] N. Yang, W. K. Henson, J. R. Hauser, and J. J. Wortman, "Estimation of the effects of remote charge scattering on electron mobility of n-MOSFETs with ultrathin gate oxides," *IEEE Trans. Electron Devices*, vol. 47, no. 2, pp. 440–447, Feb. 2000.

- [8] S. Takagi and M. Takayanagi, "Experimental evidence of inversion-layer mobility lowering in ultrathin gate oxide metal—oxide—semiconductor field-effect-transistors with direct tunneling current," *Jpn. J. Appl. Phys.*, vol. 41, pt. 1, no. 4B, pp. 2348–2352, Apr. 2002.

- [9] M. S. Krishnan, Y. C. Yeo, Q. Lu, T. J. King, J. Bokor, and C. Hu, "Remote charge scattering in MOSFETs with ultra-thin gate dielectrics," in *IEDM Tech. Dig.*, 1998, pp. 571–574.

- [10] M. V. Fischetti, "Long-range Coulomb interactions in small Si devices. Part II. Effective electron mobility in thin-oxide structures," *J. Appl. Phys.*, vol. 89, no. 2, pp. 1232–1250, Jan. 2001.

- [11] F. Gámiz and J. B. Roldan, "Scattering of electrons in silicon inversion layers by remote surface roughness," *J. Appl. Phys.*, vol. 94, no. 1, pp. 392–399, Jul. 2003.

- [12] S. Saito, K. Torii, Y. Shimamoto, S. Tsujikawa, H. Hamamura, O. Tonomura, T. Mine, D. Hisamoto, T. Onai, J. Yugami, M. Hiratani, and S. Kimura, "Effects of remote-surface-roughness scattering on carrier mobility in field-effect-transistors with ultrathin gate dielectrics," *Appl. Phys. Lett.*, vol. 84, no. 8, pp. 1395–1397, Feb. 2004.

- [13] F. Stern and W. E. Howard, "Properties of semiconductor surface inversion layers in the electric quantum limit," *Phys. Rev.*, vol. 163, no. 3, pp. 816–835, Nov. 1967.

- [14] A. G. Rojo, "Electron-drag effects in coupled electron systems," *J. Phys.: Condens. Matter*, vol. 11, no. 5, pp. R31–R52, Feb. 1999.

- [15] F. Gámiz and M. V. Fischetti, "Remote Coulomb scattering in metal-oxide-semiconductor field effect transistors: Screening by electrons in the gate," *Appl. Phys. Lett.*, vol. 83, no. 23, pp. 4848–4850, Dec. 2003.

- [16] J. Li and T. P. Ma, "Scattering of silicon inversion layer electrons by metal/oxide interface roughness," J. Appl. Phys., vol. 62, no. 10, pp. 4212– 4215, Nov. 1987.

- [17] P. M. Solomon and M. Yang, "Relevance of remote scattering in gate to channel mobility of thin-oxide CMOS devices," in *IEDM Tech. Dig.*, 2004, pp. 143–146.

- [18] F. Lime, C. Guiducci, R. Clerc, G. Ghibaudo, C. Leroux, and T. Ernst, "Characterization of effective mobility by split C(V) technique in N-MOSFETs with ultra-thin gate oxides," *Solid State Electron.*, vol. 47, no. 7, pp. 1147–1153, Jul. 2003.

- [19] W. J. Zhu and T. P. Ma, "Temperature dependence of channel mobility in HfO<sub>2</sub>-gated NMOSFETs," *IEEE Electron Device Lett.*, vol. 25, no. 2, pp. 89–91, Feb. 2004.

- [20] R. Chau, S. Datta, M. Doczy, B. Doyle, J. Kavalieros, and M. Metz, "High-κ/metal-gate stack and its MOSFET characteristics," *IEEE Electron Device Lett.*, vol. 25, no. 6, pp. 408–410, Jun. 2004.

- [21] M. Cassé, L. Thevenod, B. Guillaumot, L. Tosti, F. Martin, J. Mitard, O. Weber, F. Andrieu, T. Ernst, G. Reimbold, T. Billon, M. Mouis, and F. Boulanger, "Carrier transport in HfO<sub>2</sub>/metal gate MOSFETs: Physical insight into critical parameters," *IEEE Trans. Electron Devices*, vol. 53, no. 4, pp. 759–768, Apr. 2006.

- [22] K. H. Cheng, A Fast Quantum Simulator for the Two-Dimensional Inversion Layers, Master Thesis. Hsinchu, Taiwan: Nat. Chiao-Tung Univ., Sep. 2010.

- [23] Schred. [Online]. Available: http://nanohub.org/resources/schred

- [24] S. Takagi, J. L. Hoyt, J. J. Welser, and J. F. Gibbons, "Comparative study of phonon-limited mobility of two-dimensional electrons in strained and unstrained Si metal—oxide–semiconductor field-effect transistors," *J. Appl. Phys.*, vol. 80, no. 3, pp. 1567–1577, Aug. 1996.

- [25] S. Yamakawa, H. Ueno, K. Taniguchi, C. Hamaguchi, K. Miyatsuji, K. Masaki, and U. Ravaioli, "Study of interface roughness dependence of electron mobility in Si inversion layers using the Monte Carlo method," *J. Appl. Phys.*, vol. 79, no. 2, pp. 911–916, Jan. 1996.

- [26] D. K. Ferry, Semiconductors. New York: Macmillan, 1991.

- [27] G. Mazzoni, A. L. Lacaita, L. M. Perron, and A. Pirovano, "On surface roughness-limited mobility in highly doped n-MOSFETs," *IEEE Trans. Electron Devices*, vol. 46, no. 7, pp. 1423–1428, Jul. 1999.

- [28] A. Pirovano, A. L. Lacaita, G. Ghidini, and G. Tallarida, "On the correlation between surface roughness and inversion layer mobility in Si-MOSFETs," *IEEE Electron Device Lett.*, vol. 21, no. 1, pp. 34–36, Jan. 2000.

- [29] D. W. Lin, M. L. Cheng, S. W. Wang, C. C. Wu, and M. J. Chen, "A novel method of MOSFET series resistance extraction featuring constant mobility criteria and mobility universality," *IEEE Trans. Electron Devices*, vol. 57, no. 4, pp. 890–897, Apr. 2010.

- [30] J. R. Hauser, "Extraction of experimental mobility data for MOS devices," IEEE Trans. Electron Devices, vol. 43, no. 11, pp. 1981–1988, Nov. 1996.

- [31] F. Stern, "Calculated temperature dependence of mobility in silicon inversion layers," *Phys. Rev. Lett.*, vol. 44, no. 22, pp. 1469–1472, Jun. 1980.

- [32] M. V. Fischetti, F. Gámiz, and W. Hänsch, "On the enhanced electron mobility in strained-silicon inversion layers," *J. Appl. Phys.*, vol. 92, no. 12, pp. 7320–7324, Dec. 2002.

- [33] D. K. Ferry and S. M. Goodnick, Transport in Nanostructures. Cambridge, U.K.: Cambridge Univ. Press, 1997.

Ming-Jer Chen (S'78–M'79–SM'98) received the B.S. degree in electrical engineering (with highest honors) from National Cheng Kung University, Tainan, Taiwan, in 1977 and the M.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1979 and 1985, respectively.

In 1985, he was with the Department of Electronics Engineering, NCTU, and, in 1993, became a Full Professor. From 1987 to 1992, he was a Consultant with Taiwan Semiconductor Manufacturing Com-

pany (TSMC), Hsinchu, where he led a team from NCTU and the Electronics Research and Service Organization/Industrial Technology Research Institute to build up a series of process windows and design rules. From 2000 to 2001, he was a Visiting Professor with the Department of Electrical Engineering and the Center for Integrated Systems, Stanford University, Stanford, CA. He is the holder of eight U.S. patents and six Taiwanese patents in the field of high-precision analog capacitors, single-transistor memory cells, dynamic threshold metal—oxide—semiconductor, electrostatic discharge protection, and Flash memory. He has graduated 16 Ph.D. students and more than 100 M.S. students. His current research interests include device physics, trap physics, and reliability physics, all in the area of nanoelectronics.

Dr. Chen is a member of the Phi Tau Phi.

**Sou-Chi Chang** received the B.S. degree in electrical and control engineering from National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 2008. He is currently working toward the M.S. degree in electrical engineering and computer science with the University of Michigan, Ann Arbor.

Shin-Jiun Kuang received the B.S. degree in electrical engineering from National Chung Hsing University, Taichung, Taiwan, in 2009. She is currently working toward the M.S. degree in electronics engineering with National Chiao Tung University, Hsinchu, Taiwan.

Her research interests include characterization and modeling of nanoscale devices.

**Kuan-Hao Cheng** was born in Kaohsiung, Taiwan, in 1984. He received the B.S. degree in electrical engineering from National Chung Cheng University, Chiayi, Taiwan, in 2008 and the M.S. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2010.

He is currently performing the military service in Taiwan. His research interests include quantum simulation of the strained devices.

Chien-Chih Lee (S'07) was born in Taipei, Taiwan, in 1981. He received the B.S. degree in physics from National Chung Hsing University, Taichung, Taiwan, in 2004. He is currently working toward the Ph.D. degree in electronics engineering at National Chiao Tung University, Hsinchu, Taiwan.

His research interests include characterization and modeling of strained devices, development of quantum simulators, and study of trap physics in nanoscale devices.

**Yi-Hsien Zhan** received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 2008 and 2010, respectively.

He is currently performing the military service in Taiwan. His research interests include characterization and modeling of nanoscale metal-oxidesemiconductor field-effect transistors.

**Wen-Han Lee** (S'09) received the B.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2005, where he is currently working toward the Ph.D. degree in electronics engineering.

His research interests include characterization and modeling of strained-Si metal—oxide—semiconductor field-effect transistors and variability in nanoscale devices.