# Channel Film Thickness Effect of Low-Temperature Polycrystalline-Silicon Thin-Film Transistors

William Cheng-Yu Ma, Tsung-Yu Chiang, Chi-Ruei Yeh, Tien-Sheng Chao, Senior Member, IEEE, and Tan-Fu Lei

Abstract—In this paper, the channel-film-thickness effect of low-temperature polycrystalline-Si thin-film transistors (LTPS-TFTs) is investigated. Greater channel film thickness can provide a higher field-effect mobility  $\mu_{\rm FE}$ , rising from 14.33 to 22.33 cm²/V · s, as the channel film thickness increases from 55 to 120 nm, due to grain-size effect. In addition, varying the channel film thickness of LTPS-TFTs results in different junction leakage current due to the source/drain (S/D) junction area effect. Moreover, the S/D series resistance also significantly increases when the channel film thickness is reduced from 120 to 35 nm, leading to poor field-effect mobility  $\mu_{\rm FE}$  and driving current. Consequently, the optimum channel film thickness for active-matrix liquid-crystal displays may be identified.

*Index Terms*—Channel film thickness, low-temperature polycrystalline-Si thin-film transistors (LTPS-TFTs), scaling down.

#### I. INTRODUCTION

OW-TEMPERATURE polycrystalline-silicon thin-film matrix liquid-crystal displays (AMLCD) with integrated peripheral circuits as the pixel array on the glass substrate [1]–[5]. In addition, the 3-D integration of very large scale integration (VLSI) technology by the employment of LTPS-TFTs has been developed to increase the device density [6], [7]. However, polycrystalline-silicon channel film has many grain boundaries between the poly-grains, resulting in large numbers of defects and trap density state in the channel [8]-[10]. The defects in the trap density of the grain boundary create potential barriers that lower the conductance of polycrystalline silicon [11]. In order to increase the conductance of the polycrystalline silicon, a great quantity of carriers is required to lower the potential barrier, resulting in a large operating voltage for the LTPS-TFTs [8]–[10]. Therefore, the behavior and distribution of the trap density state in the channel are strongly related to the performance of LTPS-TFTs.

Manuscript received July 15, 2010; revised October 14, 2010, November 24, 2010, and December 21, 2010; accepted December 22, 2010. Date of publication March 3, 2011; date of current version March 23, 2011. This work was supported by the National Science Council, Taiwan, under Contract NSC-97-2221-E-009-153-MY3. The review of this brief was arranged by Editor H. S. Momose.

W. C.-Y. Ma is with the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan.

T.-F. Lei is with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan.

T.-Y. Chiang, C.-R. Yeh, and T.-S. Chao are with the Department of Electrophysics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: tschao@mail.nctu.edu.tw).

Color versions of one or more of the figures in this brief are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2104362

Grain size enlargement of the polycrystalline-silicon channel film is a direct method for improving the performance of TFTs by reducing the defects and trap density of the polycrystalline-silicon channel film. Different grain sizes of polycrystalline-Si channel film may be fabricated by controlling the deposition pressure of polycrystalline Si [12]. A comprehensive grain-size effect has been studied by Dimitriadis and Tassis [12]. However, conventional LTPS-TFTs are fabricated by depositing an amorphous-silicon film and then crystallizing. Many crystallization methods, such as the solid-phase crystallization (SPC), metal-induced lateral crystallization, and excimer laser crystallization [13]–[15], have been used to enhance the performance of LTPS-TFTs.

In addition to the crystallization method, the channel film thickness also affects the grain size of the polycrystalline-silicon film [16]. Therefore, the optimum channel film thickness of LTPS-TFTs requires investigation. In this paper, the channel-film-thickness effects of LTPS-TFTs are studied. In addition to the grain-size effect found in previous research [16], the channel film thickness induces a series resistance effect and an anomalous leakage current trend. Moreover, the rolloff behavior of the field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. are also investigated. Consequently, the optimum channel film thickness of LTPS for the application of AMLCD and 3-D integration of VLSI technology may be found.

# II. EXPERIMENTAL PROCEDURE

The devices used in this paper were first fabricated by depositing an undoped amorphous Si ( $\alpha$ -Si) layer at 550 °C in a low-pressure chemical vapor deposition (LPCVD) system on Si wafers capped with a 500-nm thick thermal oxide layer. Three thicknesses of  $\alpha$ -Si, i.e., 35, 55, and 120 nm, are chosen for the study of channel-film-thickness effect. Then, the  $\alpha$ -Si layer was recrystallized by SPC process in a furnace at 600 °C for 24 h in N<sub>2</sub> ambient. After crystallization of the channel film, the active region was patterned by dry etching. A 50-nm gate oxide was then deposited using a plasma-enhanced chemical vapor deposition (PECVD) system at 300 °C. In situ N<sup>+</sup> doped  $\alpha$ -Si of 250 nm was deposited by LPCVD at 550 °C as the gate electrode. After the patterning of the gate stack, the gate and source/drain (S/D) regions were implanted with phosphorus (15 keV at 5  $\times$  10<sup>15</sup> cm<sup>-2</sup>) and activated at 600 °C for 24-h annealing in N2 ambient. A 500-nm PECVD oxide was deposited for the passivation layer. After patterning of contact holes, aluminum was deposited by thermal evaporation system and patterned as the probe pads to complete the TFT devices. In order to study the intrinsic electrical properties of the LTPS-TFTs,

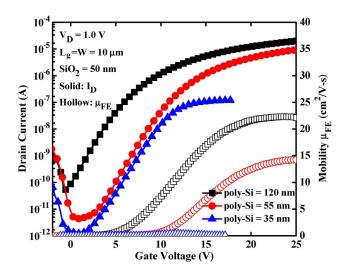

Fig. 1. Transfer curves  $(I_D - V_G)$  and field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with different channel film thicknesses and 50-nm gate oxide thickness.

there was no passivation process in our fabrication of LTPS-TFTs. The threshold voltage  $V_{\rm TH}$  was defined as the  $V_G$  at which the  $I_D$  reaches 100 nA  $\times$  ( $W/L_g$ ) and  $V_D=1.0$  V. The field-effect mobility  $\mu_{\rm FE}$  was extracted from the maximum transconductance  $G_m$ .

# III. RESULTS AND DISCUSSION

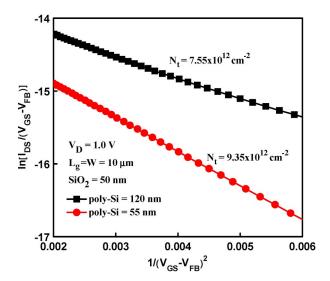

The transfer curves  $(I_D-V_G)$  and the field-effect mobility  $\mu_{\rm FE}$  of LTPS-TFTs with different channel film thicknesses and 50-nm gate oxide thickness are depicted in Fig. 1. Fig. 1 shows that the channel film thickness significantly affects the fieldeffect mobility  $\mu_{\rm FE}$  from 0.35 to 22.33 cm<sup>2</sup>/V·s when the channel film thickness grows from 35 to 120 nm. The greater channel film thickness enables the formation of larger polygrains after the crystallization of  $\alpha$ -Si [16], [17]. The grain boundary trap state value  $N_{\rm trap}$  is estimated by the Levinson and Proano method [18], [19], in which  $N_{\text{trap}}$  is extracted from the plot of the  $\ln \left[ I_{DS}/(V_{GS}-V_{\rm FB}) \right]$  versus  $1/(V_{GS}-V_{\rm FB})^2$ curves at  $V_{DS} = 1.0 \text{ V}$  and high  $V_{GS}$ , as shown in Fig. 2. The flatband voltage  $V_{\rm FB}$  is defined as the  $V_{GS}$ , yielding the minimum  $I_{DS}$  from the transfer characteristics  $I_D$ – $V_G$  curve. Larger grain sizes of polycrystalline silicon have fewer grain boundaries and traps in the channel, resulting in higher fieldeffect mobility  $\mu_{\rm FE}$  of inversion carriers [20]. For TFTs of 120- and 55-nm channel film thickness, the latter have the smaller grain size, resulting in a high density of trap states and high barrier height of grain boundaries. A trap density state decreases the free charge, while a high grain boundary barrier height severely decreases the effective mobility.

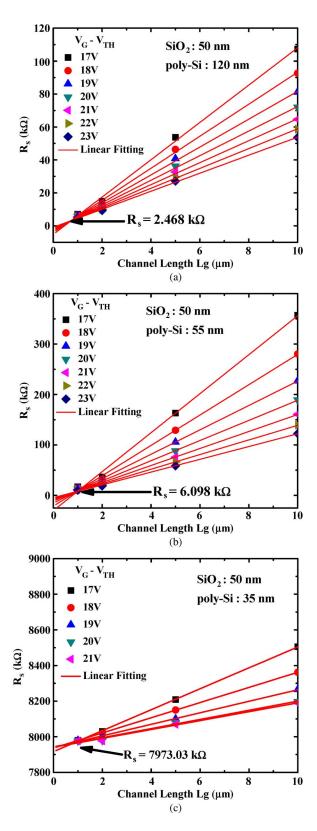

In addition to the grain-size effect of channel film thickness on LTPS-TFTs, series resistance effect is also observed in the LTPS-TFT with 35-nm channel film thickness. The series resistance in the device with 35-nm channel film thickness causes a lower driving current and field-effect mobility  $\mu_{\rm FE}$ , as shown in Fig. 1. Fig. 3(a)–(c) show the S/D series resistances  $R_s$  extractions with the channel film thicknesses of 120, 55, and 35 nm, respectively. However, the  $V_{\rm TH}$  of the 35-nm device may be misjudged due to its much lower driving current. In order to

Fig. 2. Plot of  $\ln[I_{DS}/(V_{GS}-V_{\rm FB})]$  versus  $1/(V_{GS}-V_{\rm FB})^2$  curves at  $V_{DS}=0.1$  V and high  $V_{GS}$ .

successfully extract the series resistance of the 35-nm device, we lower the definition current of  $V_{\rm TH}$  to 10 nA  $\times$  ( $W/L_g$ ) for the 35-nm device. Compared with devices with channel film thicknesses of 55 and 120 nm, of which S/D series resistances  $R_s$  were 6.098 and 2.468 k $\Omega$ , respectively, a large S/D series resistance of  $\sim$ 7973 k $\Omega$  is observed in the 35-nm channel film, as shown in Fig. 3(c). In addition, the subthreshold swing S.S. of the 35-nm channel film is also slightly higher than that of the 55- and 120-nm channel film, due to the impact of the large S/D series resistance  $R_s$ . In order to distinguish the impacts of the trap density and series resistance effects on the field-effect mobility  $\mu_{\rm FE}$  of the 35-nm channel film TFTs, the modified field-effect mobility  $\mu_{\rm FE}'$  is extracted by taking the series resistance into account as follows:

$$I_D = \frac{W}{L} C_{\text{ox}} \mu_{\text{eff}} (V_g - V_{\text{TH}}) V_D \tag{1}$$

$$I_D = \frac{W}{L} C_{\text{ox}} \mu'_{\text{eff}} (V_g - V_{\text{TH}}) V'_d$$

(2)

$$V_d' = V_D - I_D \times R_s \tag{3}$$

$$\mu'_{\rm eff} = \mu_{\rm eff} \times \frac{V_D}{V_D - I_D \times R_s}.$$

(4)

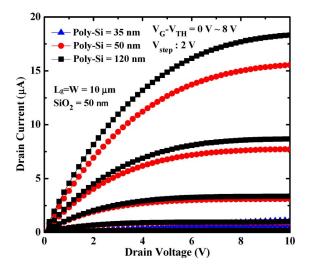

$V_D$  is the total applied voltage. The voltage drop should occur in the series resistance and conductive channel of TFTs.  $V_d'$  is thus the real applied voltage across the channel of TFTs. Therefore, the modified field-effect mobility  $\mu_{\rm FE}'$  can be extracted without the impact of the series-resistance  $R_s$  effect, as shown in Table I. The important device parameters of the LTPS-TFTs with different channel film thicknesses are listed in Table I. The field-effect mobility  $\mu_{\rm FE}$  degrades about 4.6%, 6.8%, and 59.3% for TFTs with 120-, 55-, and 35-nm channel film thickness, respectively. Fig. 4 shows the  $I_D$ - $V_D$  curve for LTPS-TFTs with 35-, 55-, and 120-nm channel film thickness. The driving current of the device with the 35-nm channel film thickness shows a lower current due to its low field-effect mobility  $\mu_{\rm FE}$  and poor S/D series resistance. In addition, the 120-nm channel film thickness device shows a higher current

Fig. 3. (a)–(c) Extraction of S/D series resistances  $R_s$  for channel film thicknesses of 120, 55, and 35 nm, respectively.

due to the higher field-effect mobility  $\mu_{\rm FE}$  and a lower S/D series resistance.

In addition to the field-effect mobility  $\mu_{\rm FE}$  effect and the S/D series resistance effect of channel film thickness, the leakage current  $I_{\rm min}$  is also affected by the channel film thickness. As

TABLE I IMPORTANT DEVICE PARAMETERS OF LTPS-TFTs WITH DIFFERENT CHANNEL FILM THICKNESSES, 50-nm GATE OXIDE THICKNESS, AND  $W/L_g=10~\mu\mathrm{m}/10~\mu\mathrm{m}$

| Channel film<br>thickness<br>(nm) | V <sub>TH</sub> (V) | S.S.<br>(V/dec.) | μ <sub>FE</sub><br>(cm <sup>2</sup> /V-s) | μ' <sub>FE</sub><br>(cm <sup>2</sup> /V-s) | $R_s \ (k\Omega)$ | I <sub>on</sub> /I <sub>min</sub> (x10 <sup>5</sup> ) | I <sub>min</sub><br>(pA) |

|-----------------------------------|---------------------|------------------|-------------------------------------------|--------------------------------------------|-------------------|-------------------------------------------------------|--------------------------|

| 120                               | 5.92                | 1.813            | 22.33                                     | 23.40                                      | 2.468             | 4.53                                                  | 53                       |

| 55                                | 10.87               | 1.797            | 14.33                                     | 15.37                                      | 6.098             | 27.96                                                 | 4.4                      |

| 35                                | N/A                 | 1.867            | 0.35                                      | 0.86                                       | 7973.03           | 0.99                                                  | 1.2                      |

Fig. 4.  $I_D$ – $V_D$  curve of LTPS-TFTs for 35-, 55-, and 120- nm channel film thicknesses

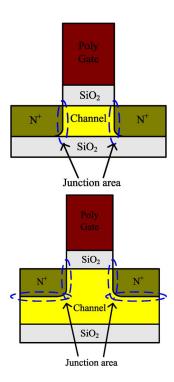

shown in Fig. 1 and Table I, the device with 120-nm channel film thickness shows the highest leakage current  $I_{\rm min} \sim 53~{\rm pA}$ , whereas the 55- and 35-nm devices show a lower leakage current  $I_{\min}$  and  $\sim$ 4.4 and 1.2 pA, respectively. The leakage current would be strongly related to the trap emission, which is a function of the electric field in the drain depletion region and the trap density of the grain boundaries [21]. When the channel film thickness decreases from 55 to 35 nm, the S/D series resistance significantly increases, as shown in Fig. 3(b) and (c), which decreases the lateral electric field in the drain depletion region [21], resulting in lower leakage current. On the other hand, the trap density of the grain boundary decreases when the channel film thickness increases from 55 to 120 nm due to the larger grain size. In addition, devices with thicker channel film show lower lateral electric fields in the drain depletion region [21], [22]. However, the leakage current  $I_{\min}$  increases from 4.4 to 53 pA when the channel film thickness increases from 55 to 120 nm. Therefore, this high leakage current cannot be attributed to the traditional lateral electric field and trap density effects. The 120-nm channel film thickness provides a larger area of source and drain junction region in which the phosphorous of the S/D implantation is not distributed through whole polycrystalline-silicon thickness, as shown in Fig. 5, resulting in a higher junction leakage current for the 120-nm channel film thickness than the thinner channel film thicknesses of 55 and 35 nm [23]. Consequently, the 55-nm channel film thickness provides the highest  $I_{\rm on}/I_{\rm min}$  ratio of the three sizes in this paper, as shown in Fig. 1 and Table I.

Fig. 5. Cross section of LTPS-TFTs with various channel film thicknesses.

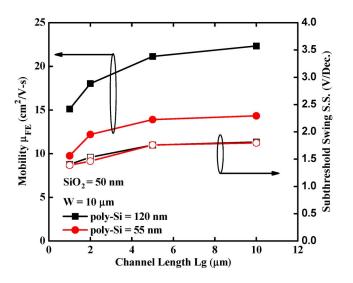

Fig. 6. Channel length  $L_g$  dependence of field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. for 55- and 120-nm channel film thicknesses.

Fig. 6 shows the channel length  $L_g$  dependence of the field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing S.S. for the 55- and 120-nm channel film thicknesses. The rolloff behavior of the field-effect mobility  $\mu_{\rm FE}$  is dominated by the S/D series resistance effect. As the channel length becomes smaller, the S/D series resistance decreases the drain voltage drop across the channel, resulting in lower driving current and field-effect mobility  $\mu_{\rm FE}$  [24]. Therefore, the rolloff percentage of the field-effect mobility  $\mu_{\rm FE}$  and the rolloff of the subthreshold swing S.S. is comparable for both 55- and 120-nm channel film TFTs, due to their similar S/D series resistance.

In sum, different channel film thicknesses between 50 and 120 nm of LTPS-TFTs would show comparable rolloff behavior of field-effect mobility  $\mu_{\rm FE}$  and subthreshold swing.

### IV. CONCLUSION

The impacts of channel film thickness on LTPS-TFTs have been investigated in this paper. Significant grain size, junction leakage, and S/D series resistance effects have been observed. Devices with a thicker channel film thickness have lower S/D series resistance and large grain size of channel film, providing higher field-effect mobility  $\mu_{\rm FE}$  and driving current. However, greater channel film thickness has a larger S/D junction area, resulting in higher junction leakage. By contrast, lower channel film thickness has smaller grain sizes and higher S/D series resistance, resulting in poor driving current. The comparison of the electrical behavior of LTPS-TFTs with different channel film thicknesses shows that a channel thickness of about 55 nm appears to be the optimum choice for AMLCDs and 3-D integration.

#### ACKNOWLEDGMENT

The authors would like to thank the process support from the National Nano Device Laboratories and the Nano Facility Center, National Chiao Tung University.

#### REFERENCES

- [1] G. K. Guist and T. W. Sigmon, "High-performance thin-film transistors fabricated using excimer laser processing and grain engineering," *IEEE Trans. Electron Devices*, vol. 45, no. 4, pp. 925–932, Apr. 1998.

- [2] Y. W. Choi, J. N. Lee, T. W. Jang, and B. T. Ahn, "Thin-film transistors fabricated with poly-silicon films crystallized at low temperature by microwave annealing," *IEEE Electron Device Lett.*, vol. 20, no. 1, pp. 2–4, Jan 1999

- [3] C. W. Lin, M. Z. Yang, C. C. Yeh, L. J. Cheng, T. Y. Huang, H. C. Cheng, H. C. Lin, T. S. Chao, and C. Y. Chang, "Effects of plasma treatments, substrate types, and crystallization methods on performance and reliability of low temperature polysilicon TFTs," in *IEDM Tech. Dig.*, 1999, pp. 305–308.

- [4] K. M. Chang, W. C. Yang, and C. P. Tsai, "Electrical characteristics of low temperature polysilicon TFT with a novel TEOS/oxynitride stack gate dielectric," *IEEE Electron Device Lett.*, vol. 24, no. 8, pp. 512–514, Aug. 2003.

- [5] J.-H. Jeon, M.-C. Lee, K.-C. Park, S.-H. Jung, and M.-K. Han, "A new poly-Si TFT with selectively doped channel fabricated by novel excimer laser annealing," in *IEDM Tech. Dig.*, 2000, pp. 213–216.

- [6] F. Hayashi, H. Ohkubo, T. Takahashi, S. Horiba, K. Noda, T. Uchida, T. Shimizu, N. Sugawara, and S. Kumashiro, "A highly stable SRAM memory cell with top-gated P-N drain poly-Si TFTs for 1.5 V operation," in *IEDM Tech. Dig.*, 1996, pp. 283–286.

- [7] H. J. Cho, F. Nemati, P. B. Griffin, and J. D. Plummer, "A novel pillar DRAM cell for 4 Gbit and beyond," in VLSI Symp. Tech. Dig., 1998, pp. 38–39.

- [8] S.-D. Wang, W.-H. Lo, and T.-F. Lei, "CF<sub>4</sub> plasma treatment for fabricating high-performance and reliable solid-phase-crystallized poly-Si TFTs," *J. Electrochem. Soc.*, vol. 152, no. 9, pp. 703–706, 2005.

- [9] C.-H. Tu, T.-C. Chang, P.-T. Liu, C.-H. Chen, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, L.-T. Chang, C.-C. Tsai, S. M. Sze, and C.-Y. Chang, "Electrical enhancement of solid phase crystallized poly-Si thin-film transistors with fluorine ion implantation," *J. Electrochem. Soc.*, vol. 153, no. 9, pp. 815–818, 2006.

- [10] C.-H. Tu, T.-C. Chang, P.-T. Liu, H.-W. Zan, Y.-H. Tai, C.-Y. Yang, Y.-C. Wu, H.-C. Liu, W.-R. Chen, and C.-Y. Chang, "Enhanced performance of poly-Si thin film transistors using fluorine ions implantation," *Electrochem. Solid State Lett.*, vol. 8, no. 9, pp. 246–248, 2005.

- [11] J. Y. W. Seto, "The electrical properties of polycrystalline silicon films," *J. Appl. Phys.*, vol. 46, no. 12, pp. 5247–5254, Dec. 1975.

[12] C. A. Dimitriadis and D. H. Tassis, "On the threshold voltage and chan-

- [12] C. A. Dimitriadis and D. H. Tassis, "On the threshold voltage and channel conductance of polycrystalline silicon thin-film transistors," *J. Appl. Phys.*, vol. 79, no. 8, pp. 4431–4437, Apr. 1996.

- [13] C.-P. Lin, Y.-H. Hsiao, and B.-Y. Tsui, "Process and characteristics of fully silicided source/drain (FSD) thin-film transistors," *IEEE Trans. Electron Devices*, vol. 53, no. 12, pp. 3086–3094, Dec. 2006.

- [14] C.-C. Tsai, H.-H. Chen, B.-T. Chen, and H.-C. Cheng, "High-performance self-aligned bottom-gate low-temperature poly-silicon thin-film transistors with excimer laser crystallization," *IEEE Electron Device Lett.*, vol. 28, no. 7, pp. 599–602, Jul. 2007.

- [15] N.-K. Song, M.-S. Kim, S.-H. Han, Y.-S. Kim, and S.-K. Joo, "The electrical properties of unidirectional metal-induced lateral crystallized polycrystalline-silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 54, no. 6, pp. 1420–1424, Jun. 2007.

- [16] A. J. Walker, S. B. Herner, T. Kumar, and E.-H. Chen, "On the conduction mechanism in polycrystalline silicon thin-film transistors," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1856–1866, Nov. 2004.

- [17] G. Fortunato, "Polycrystalline silicon thin-film transistors: A continuous evolving technology," *Thin Solid Films*, vol. 296, no. 1/2, pp. 82–90, Mar. 1997.

- [18] J. Levinson, F. R. Shepherd, P. J. Scanlon, W. D. Westwood, G. Este, and M. Rider, "Conductivity behavior in polycrystalline semiconductor thin film transistors," *J. Appl. Phys.*, vol. 53, no. 2, pp. 1193–1202, Feb. 1982.

- [19] R. E. Proano, R. S. Misage, and D. G. Ast, "Development and electrical properties of undoped polycrystalline silicon thin-film transistor," *IEEE Trans. Electron Devices*, vol. 36, no. 9, pp. 1915–1922, Sep. 1989.

- [20] A. T. Voutsas, D. N. Kouvatsos, L. Michalas, and G. J. Papaioannou, "Effect of silicon thickness on the degradation mechanisms of sequential laterally solidified polycrystalline silicon TFTs during hot-carrier stress," *IEEE Electron Device Lett.*, vol. 26, no. 3, pp. 181–184, Mar. 2005.

- [21] K. R. Olasupo, W. Yarbrough, and M. K. Hatalis, "The effect of drain offset on current-voltage characteristics in sub micron polysilicon thinfilm transistors," *IEEE Trans. Electron Devices*, vol. 43, no. 8, pp. 1306– 1308, Jun. 1996.

- [22] K. P. Anish Kumar and J. K. O. Sin, "Influence of lateral electric field on the anomalous leakage current in polysilicon TFTs," *IEEE Electron Device Lett.*, vol. 20, no. 1, pp. 27–29, Jan. 1999.

- [23] A. Pecora, M. Schillizi, G. Tallarida, G. Fortunato, C. Reita, and P. Migliorato, "OFF-current in polycrystalline silicon thin film transistors: An analysis of the thermally generated component," *Solid State Electron.*, vol. 38, no. 4, pp. 845–850, Apr. 1995.

- [24] A. Valletta, L. Mariucci, and G. Fortunato, "Surface-scattering effects in polycrystalline silicon thin-film transistors," *Appl. Phys. Lett.*, vol. 82, no. 18, pp. 3119–3121, May 2003.

William Cheng-Yu Ma was born in Taipei, Taiwan, in 1980. He received the B.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2002 and the M.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University in 2004 and 2008, respectively.

He changed his name from Ming-Wen Ma to William Cheng-Yu Ma in 2009. He is currently working for the research and design of 28-nm node complementary metal—oxide—semiconductor technology with the Institute of Electronics, National Chiao

Tung University. His research interests are the fabrication and characterization of low-temperature polycrystalline thin-film transistor, silicon-on-insulator device, metal-gate/high-k technology, and radio frequency metal-insulator-metal capacitor.

**Tsung-Yu Chiang** was born in Yunlin, Taiwan, in 1984. He received the B.S. degree in physics from National Chung Cheng University, Chiayi, Taiwan, in 2006. He is currently working toward the Ph.D. degree in the Department of Electrophysics, National Chiao Tung University, Hsinchu, Taiwan.

His research interest includes the studies of semiconductor device physics, including low-temperature polycrystalline-silicon thin-film transistor, metal gate/high-k technology, strain technique, and nonvolatile Flash memories.

**Chi-Ruei Yeh** was born in Taipei, Taiwan, in 1985. He received the M.S. degree in electrophysics from National Chiao Tung University, Hsinchu, Taiwan, in 2009

He is currently with the Department of Electrophysics, National Chiao Tung University. His research interests include low-temperature polycrystalline-silicon thin-film transistors and metal gate/high-k technology.

**Tien-Sheng Chao** (SM'01) was born in Penghu, Taiwan, in 1963. He received the Ph.D. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1992.

He joined the National Nano Device Laboratories as an Associate Researcher in July 1992 and became as a Researcher in 1996. He was engaged in developing the thin dielectrics preparations, cleaning processes, and complementary metal—oxide—semiconductor device fabrication. He has been with the Department of Electrophysics, National Chiao

Tung University, since 2001.

**Tan-Fu Lei** was born in Keelung, Taiwan, on September 17, 1944. He received the B.S. degree in electrical engineering from National Cheng Kung University, Tainan, Taiwan, in 1967 and the M.S. and Ph.D. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1970 and 1979, respectively.

From 1970 to 1972, he was with the Fine Products Microelectronics Corporation, Taiwan, as an Engineer working on the fabrication of small-signal transistors. From 1980 to 1982, he was the Plant

Manager of Photronic Corporation, Taiwan. In 1983, joined the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University, as an Associate Professor. From 1984 to 1986, he was the Director of the Semiconductor Research Center. From 1991 to 1998, he was also the Deputy Director of the National Nano Device Laboratories. He is currently a Professor with the Department of Electronics Engineering and the Institute of Electronics, National Chiao Tung University. His research interests include semiconductor devices and very large scale integration technologies.