# 行政院國家科學委員會專題研究計畫 期中進度報告

總計畫:高效率智慧型面板之研究(1/3)

計畫類別: 整合型計畫

計畫編號: NSC93-2215-E-009-072-

<u>執行期間</u>: 93 年 08 月 01 日至 94 年 07 月 31 日 <u>執行單位</u>: 國立交通大學光電工程學系(所)

計畫主持人:謝漢萍

報告類型: 精簡報告

處理方式: 本計畫可公開查詢

中華民國94年5月24日

# 行政院國家科學委員會補助專題研究計畫 □ 成 果 報 告 □ 期中進度報告

# 高效率智慧型面板之研究

計畫類別:□個別型計畫 整合型計畫

計畫編號: NSC93 - 2215 - E - 009 - 072 -

執行期間: 93 年 8 月 1 日至 94 年 7 月 31 日

計畫主持人:謝漢萍

共同主持人: 計畫參與人員:

成果報告類型(依經費核定清單規定繳交): 精簡報告 □完整報告

本成果報告包括以下應繳交之附件:

- □赴國外出差或研習心得報告一份

- □赴大陸地區出差或研習心得報告一份

- □出席國際學術會議心得報告及發表之論文各一份

- □國際合作研究計畫國外研究報告書一份

處理方式:除產學合作研究計畫、提升產業技術及人才培育研究計畫、列管

計畫及下列情形者外,得立即公開查詢

□涉及專利或其他智慧財產權,□一年□二年後可公開查詢

執行單位:國立交通大學 光電工程學系 顯示科技研究所

中 華 民 國 九十四 年 五 月 十九 日

# 摘要:

關鍵詞:背光源、液晶、薄膜電晶體、智慧型面板

智慧型面板具有亮度高,功率低,厚度薄,重量輕,反應時間快,整合度高,信賴性高,畫面品質佳的特點,為了實現這樣的先進系統,除了各領域的前瞻研究外,更需高整合性地結合顯示與半導體的先進技術,始能完成。本計畫結合光、電二個領域,液晶、光源、製程、元件、電路五個方面,以提昇平面顯示器特性及增加整合度的方式,整體性地研究智慧型面板的相關課題。本計畫研究新型快速多穩態液晶與平面型光源,配合驅動技術,以符合高亮度低功率的需求,並研究開發低操作電壓(3.3V)互補型複晶矽薄膜電晶體新型元件及高整合性製程,與具變動容許的設計能力,而達成高整合功能的目標。

#### Abstract:

Keywords: Backlight, Liquid crystal, TFT, Smart panel

Smart panel has merits of high brightness, low power consumption, thin thickness, light weight, fast response, high integration, high reliability, and good image quality. To realize such an advanced system, the integrated effort of the progressive techniques in displays and semiconductors are essential. This project incorporates both the optical and electronic domains and proceeds in five areas: liquid crystal, light source and optics, process, device, and circuit. The related issues about smart panel are studied as a whole by enhancing the features of flat displays and increasing the level of integration. The novel type fast multi-stable liquid crystal and the high efficient light source with the corresponding driving scheme are investigated for high brightness and low power consumption. Low-operation-voltage (3.3 V) CMOS poly-Si thin film transistor (TFT) novel devices will be developed and high-level integration of the fabrication process will be established, as well as the design capabilities for variation will be pursued for being highly integrated functions of the smart panel.

## ▶ 前言及研究目的

本計畫提出 "Smart Display"的前瞻觀念性構想,結合顯示技術與電子元件系統的研究專家,共同開發所需之具有致能(Enabling)性質的前瞻技術。研發的重點除了強調智慧型元件及模組整合外,並著眼於建立完整的設計、模擬、製程及量測技術,以期能在研發完成後,藉由適當的擴散機制,順利移轉產業界,提昇我國技術水準,衍生更具附加價值的新型顯示系統。

提高顯示器產品的競爭力和附加價值,有二個方向:一是進一步改善平面顯示器的既有特性,加強發揮平面顯示面板的優勢;二是增加產品的功能整合度,擴張其應用範圍。 在特性改善部份,分為液晶光電特性與高光效率面板光源進行。在功能整合部份,則由製程技術控制,新型元件研究,以及內建電路和驅動設計著手。

本計畫目標在為智慧型面板建立一套新的電路模擬技術以及新的電路設計觀念,在"Design for variation"的相關研究配合之下,所建立之智慧型面板設計技術,必可使 SoP 產品的設計成功率大增,而使系統整合顯示技術早日實現。

以下分別就各個子計畫分別說明其背景及目的:

#### 高效率整合型面板光源

現今 LCD 係以 CF 為濾光元件達成彩色顯示的目的,其將 2/3 旁波段的光波能量吸收 而變成顯示上較難克服的 " 熱 ",除此外,偏光板會吸收 1/2 未偏極化的入射光,也是光損耗的重要因素之一。在此,我們將提出一種新的 LED 背光源系統,搭配 color sequential 技術,在特定的時間由不同的 LED 分別發出 R,G 和 B 的光源。因此能取代 CF,再加上偏光轉換次波長光柵來提升偏光效率,有效降低光學損耗並達成高效能的目的。同時,結合新型背光模組技術在 TFT 製程上,整合背光模組和液晶模組於顯示器製程中,與傳統的 CCFL 背光模組相較下,在操作電壓,厚度和重量上均有著顯著的進步。以使 LCD 能達到輕、薄、高光效率和優異彩色表現能力的特色。

#### 整合型低操作功率元件製程設計

主要目的在開發適用於系統面板之低壓(3.3V)操作的 CMOS 複晶矽薄膜電晶體製程技術,希望利用複晶矽薄膜電晶體較大的載子遷移率、較大的驅動電流、以及較小的臨界電壓等特性,發展應用在顯示器週邊驅動電路的能力。本計畫提出新穎的 self-biased body (SBB) 元件結構,希望在不增加額外基板接線的前提下,利用元件的基板效應降低臨界電壓,同時引入 high-K 材料作為閘極介電層,以增加閘極控制能力,最後並藉 SBB 元件調控 P 型和 N 型元件的對稱特性,降低 CMOS 操作功率,成功完成 3.3V CMOS poly-Si TFT 的製程開發。

#### 智慧型面板內建電路設計

目前內建電路之研究大都是以製程技術改善元件特性為主,而將元件特性的改善擴張解釋為先進內建電路的實現,但實際上,電路是許多元件的組合,除了考慮單一特性,更重要的是元件差異性必須在特定的範圍內,才能保證其正常運作。由於目前電路設計絕大部份以單晶矽元件實現,電路設計不需為了元件間的差異而苦心設想。而以低溫製程形成

的元件,因為缺陷的分佈無法掌握避免,而會隨著均勻性、再現性、信賴性、與環境溫度而改變,故在智慧型面板內建電路之研究上,必須再做到 design for variation(含 reliability)。本計畫目標在為智慧型面板建立一套新的電路模擬技術以及新的電路設計觀念,在"Design for variation"的相關研究配合之下,所建立之智慧型面板設計技術,必可使 SoP 產品的設計成功率大增,而使系統整合顯示技術早日實現。

# > 文獻探討

在面板光源方面,隨著 LED 製程的不斷開發,新式的 LED 其光效率(Im/W)已大幅提升,,以 LED 光源來取代 CCFL 的時程已指日可待。在改進 LED 封裝的型態,有數種結構被發展,如直射型、兩峰值型和邊射型 LED,其光場分佈各有其特色。因邊射型 LED 其光場分佈具有高度集中性,容易與搭配的 optical cavity 進行結合設計,目前討論以邊射型 LED 為光源來設計 optical cavity 的文獻為最多,指向性的光源發展能更有效利用光,提升光使用效率。

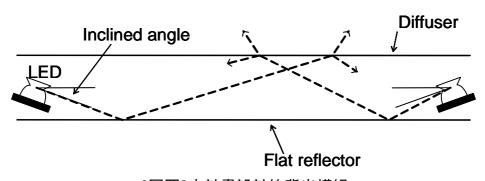

在 optical cavity 的發展,主要有直下陣列排列 LED 和側邊陣列排列 LED 兩種。直下型排列 LED,如[圖一](a),將 LED 排列於出光面之下,優點是無須額外的導光板的設計,可減輕整體背光模組的重量,缺點是需要較厚的模組厚度來達到均勻混光的效果。側邊陣列排列 LED,如[圖一](b),與傳統 CCFL 背光模組非常類似,光源在面板側邊,光進入導光板並由擴散點導出光,優點是可在較薄的模組厚度就達到可接受的均勻度,缺點是導光板增加了模組的重量。

[圖一] (a) 直下陣列排列 LED

(b) 側邊陣列排列 LED

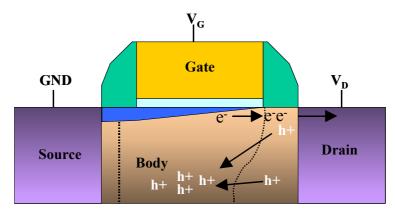

在元件製程設計,由於薄膜電晶體製作在絕緣的玻璃基板上,所以和 SOI 元件一樣,會有如同[圖二]所示的浮動基板效應產生,這是由於汲極空乏區產生的電荷或高電場撞擊游離效應產生的電荷會累積在中性的基板區域和汲極源極形成寄生的雙極性電晶體 BJT,當浮動基板所累積的電荷造成基板電位提升時,元件的臨界電壓會隨著基板電壓的上升而下降,這在 MOSFET 相關元件中是熟知的基板效應(Body Effect)的表現,然而,在 poly-Si TFT 中,發現由於基板缺陷捕捉電荷的原因,使基板電位會隨缺陷密度上升而提高,而更進一步的造成臨界電壓的下降,亦即基板累積的電荷密度可以有效降低元件的臨界電壓,目前相關 poly-Si TFT 基板效應的詳細研究並未見到,本計畫希望先從元件物理機制上著手研究其效應,同時應用此效應來有效降低臨界電壓。

[圖二] 浮動基板效應中,基板會累積由 Drain 端產生的電洞。

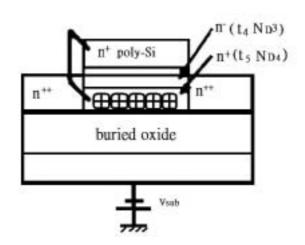

在 SOI 的技術中曾提出以 Accumulation mode EIB-DTMOS (見圖三),把閘極和基板接在一起,利用在基板電磁感應出載子,以之提高基板電壓,並降低臨界電壓,且基板部分是由反轉載子構成,可以加以控制使基板載子濃度很高,且可有一個劇烈變化的載子分佈,以達到在低臨界電壓之下獲得很大的 body effect factor (body effect factor=0.8~1、臨界電壓=0.1V),所以可得到很大的臨界電壓下降和可以抑制短通道效應的結果,而可獲得很高的電流驅動能力。對 poly-Si 而言,EIB-DTMOS 的結構不能直接套用,因為閘極電壓過高,直接和基板連接很可能造成基板和閘極的順偏產生漏電,如果另外加一個電極去控制基板電壓又會造成電路設計上的複雜以及更多的 power consumption,所以我們基於先期對 poly-Si TFT 基板效應的研究,發現在 poly-Si TFT 中臨界電壓確實會隨著基板電位上升而下降,而且基板電位的大小和複晶矽薄膜的缺陷密度成正比,也就是基板缺陷越多,捕捉的電荷越多,基板效應就越明顯。當然,位於通道頂端的缺陷同時也會造成元件特性的劣化,所以本計畫希望利用在元件下方形成 getting layer 的方式,藉著控制 getting layer (例如控制 Ge 含量增加 poly-Si Ge grain boundary 析出之 point defect) 的品質來調變基板捕捉電荷的量,並降低元件的臨界電壓。

[圖三] 在 SOI 中應用 body effect 降低 threshold voltage 的 EIB-DTSOI 元件示意圖。

本計畫的元件製作也將針對閘極控制能力加以改善,希望研發 high-K 閘極絕緣層的製程,提高閘極氧化層品質,尤其希望發展低溫製程之 high-K 材料,以高電容低漏電為研究的目標。

在內建電路設計方面,由元件模型方面的論文來看,論文著重在對元件物理的探討, 以推導最符合實際元件特性的解析性公式組和參數值,其論文建立的基礎,僅為單一個元 件的特性,即使其理論值與實際量測值的符合度再高.也不過只能代表該單一元件特性, 而無法代表以相同製程一起製作出來的所有元件特性。

另外,由元件特性改善方面的論文來看,大都是針對元件整體特性的提昇技術,僅有少數論文特別對元件的變動有所著墨;而有許多製程方面的研究計畫企圖以形成單晶通道之LTPS-TFT 來徹底解決元件變動的問題,但以目前的研究狀況,即使晶粒愈做愈大,仍無法完全解決問題,反而形成的晶粒大,其元件變動也隨之變大。

甚至,由內建電路的設計方面的論文來看,除了針對 AMOLED 的畫素設計真正地面對元件變動性,而有許多提案之外,其餘內建電路設計的相關論文,皆基於單一 LTPS-TFT 特性來作設計。另外以廣義的元件變動來看,有一個很重要的元件變動因素是元件本身的可靠度,這方面也有非常多論文探討[20~34],然而,與元件特性變動類似,並未有相對應的模擬技術與設計觀念。

本計畫目標在為智慧型面板建立一套新的電路模擬技術以及新的電路設計觀念,在"Design for variation"的相關研究配合之下,所建立之智慧型面板設計技術,必可使 SoP 產品的設計成功率大增,而使系統整合顯示技術早日實現。

## ▶ 研究方法

#### 高效率整合型面板光源

為了減少系統的複雜度與製作上精確度的要求,在同一個面板尺寸的例子中,適當的旋轉 LED 擺放角度,期望達到不加光學元件和平坦化反射板的目標。示意圖如[圖四]

[圖四]本計畫設計的背光模組

進行步驟首先以光學模擬軟體建立 LED 光場分佈, 然後建立 optical cavity 的模型, 以 22 "面板為例子,在最佳化過程中,調整光源高度、傾斜角度、LED 數目、反射面特性等參數,來找尋最佳參數。除了用光學軟體模擬之外,也用數學模型來定義光通量密度,推導出傾斜角度的通式,可將此傾斜 LED 光場的技術推廣到一般情況。

#### 整合型低操作功率元件製程設計

- (1) 首先針對希望成為 getting layer 的 SiGe 薄膜作沉積和材料分析

- (a) 在基板上成長矽鍺等薄膜為 getting center, 先利用沉積時候 SiH4和 GeH4氣體流量控制薄膜的 Ge 含量。

- (b) 利用 AFM、FTIR、Raman 等儀器來分析 getting center layer 薄膜品質,觀察鍺於不同製程條件下析出形成 getting center 的狀態。

- (2) 也針對欲開發之 high-K 薄膜做基本電性測試

- (a) 利用 E-gun 方式沉積 Ta<sub>2</sub>O<sub>5</sub>、Si<sub>3</sub>N<sub>4</sub>、Al<sub>2</sub>O<sub>3</sub>。 Ta<sub>2</sub>O<sub>5</sub> 、Al<sub>2</sub>O<sub>3</sub> 等薄膜。

- (b) 製做基本電容元件

- (c) 量測不同薄膜的電容大小和記憶效應。

- (d)測量電容漏電和崩潰電壓等閘極絕緣層特性。

#### 智慧型面板內建電路設計

- (1) 首先以相同的製程與尺寸之 TFT 為統計標的,建立元件特性變動(包括溫度變化及可靠度變化)之資料庫,以作為元件變動量的基礎。

- (2) 接著將元件變動量資料庫,以統計方式,轉化成以元件模型參數表示,以作為電路模擬的基礎。

- (3) 以 Monte Carlo 模擬技巧,依據設定出的元件參數組,評估各種基礎電路區塊(function blocks)性能與元件參數變動的相關性,來判斷出各元件參數對電路區塊特性的衝擊因素,作為高變動容許度之電路設計的研究基礎。

# > 結果與建議

#### 高效率整合型面板光源

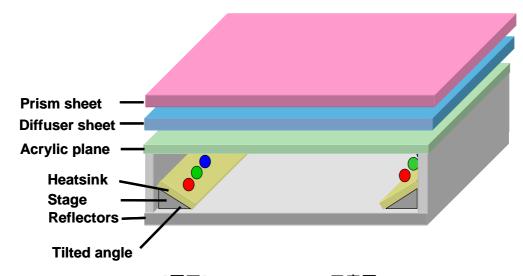

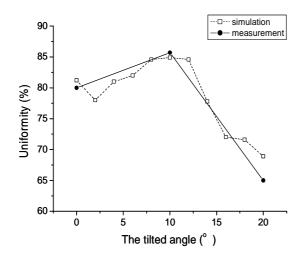

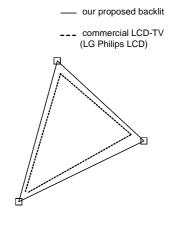

模擬結果顯示,在大尺寸 22"的例子中,LED 傾斜角度 10°是最佳值,可達到均勻度 85%。在實際製作方面,以機械加工作出 optical cavity,在其反射面貼上高反射率薄膜,如[圖五]所示。此外三個不同傾斜角度 0°、10°與 20°的平台用來支撐 LED 陣列。每個角度的實驗中,用橢圓錐光量測系統量測亮度。根據 ANSI-92 標準量測出光面上九點,取最小值和最大值的比值來表示均勻度。量測結果顯示與模擬結果接近,如[圖六](a)。此外在傾斜角度 8°~12°,可得到穩定的均勻度表現。在色彩表現方面可得到 1.3 倍於傳統色彩反差係數(color gamut)如[圖六](b)。

[圖五]optical cavity 示意圖

[圖六](a) LED 傾斜角度對均勻度的 模擬與量測結果

(b)LED 背光與傳統色彩反差係數 比較圖

### 整合型低操作功率元件製程設計

(1) SiGe 薄膜 AFM 特性分析:

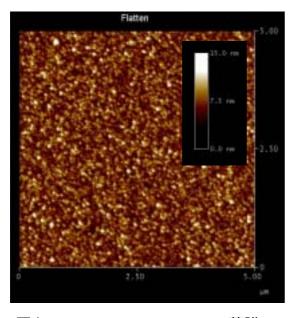

首先利用 HDPCVD 系統成長三種不同含量之 SiGe 薄膜(Si<sub>0.85</sub>Ge<sub>.15</sub>、Si<sub>0.7</sub>Ge<sub>0.3</sub>、Si<sub>0.55</sub>Ge<sub>0.45</sub>),所成長薄膜如[圖七]所示應為 microcrystal 晶相。表面的 roughness 在不同的 Ge 含量是在 1nm 左右,可以合適於下一個步驟的薄膜沉積。

[圖八]不同 SiGe 薄膜之 Raman 分析比較圖

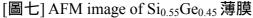

(2) SiGe 薄膜 Raman 分析其不同薄膜成長條件之 SiGe 鍵結狀況:

如[圖八]所示,在  $Si_{0.87}Ge_{0.13}$  的薄膜成長條件下,基本上沒有觀察到明顯 Si-Ge 或 Ge-Ge 鍵結的峰值,Ge 含量過低的薄膜,並無法順利產生穩定的鍵結。在  $Si_{0.79}Ge_{0.21}$  的薄膜成長條件下,觀察到明顯 Si-Ge 或 Ge-Ge 鍵結的峰值。在  $Si_{0.7}Ge_{0.3}$  的薄膜成長條件下,也觀察到明顯 Si-Ge 或 Ge-Ge 鍵結的峰值。

非晶或微晶的 SiGe 薄膜,Ge 在濃度低的時候(Ge=13%),SiGe 鍵結不易觀察到。在濃度高於某一個程度後(ex. Ge=21%),不同濃度 Ge 含量的薄膜,SiGe 鍵結和 Ge-Ge 鍵結的含量差不多,也就是過高的 Ge 含量無法增加鍵結 Ge 的成分,反而可能使多餘的 Ge 析出形成未鍵結的原子。目前結果看來,Ge 含量在 20%左右是較適當的低雜質 SiGe 薄膜。

#### (3) High-K 材料電容分析

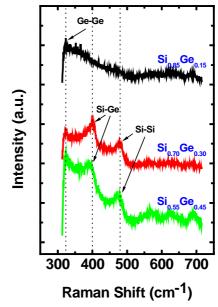

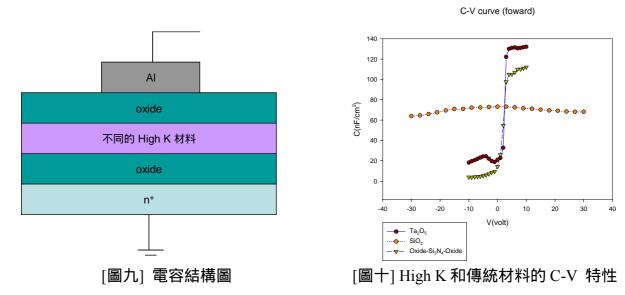

目前嘗試的 High K 材料有:Ta<sub>2</sub>O<sub>5</sub>、Si<sub>3</sub>N<sub>4</sub>、Al<sub>2</sub>O<sub>3</sub>。Ta<sub>2</sub>O<sub>5</sub> 、Al<sub>2</sub>O<sub>3</sub>都可以成功利用 E-gun 方式做薄膜鍍膜,如[圖九]。

由[圖十]比較,可以看到  $Ta_2O_5$  以及 oxide- $Si_3N_4$ -oxide 結構比起傳統  $SiO_2$  可以大幅提升 薄膜電容值 (提升兩倍), 應用在元件上可以增進閘極控制能力以及輸出電流。另外我們也 比較三種材料在閘極電壓不同向掃描時所量到的電容值,可以發現 oxide- $Si_3N_4$ -oxide 結構 以及  $Ta_2O_5$  電容比較具有 forward/reverse 量測數值的一致性,亦即比較沒有記憶效應。曲線在 inversion、accumulation 區域間的轉換也比較快速。

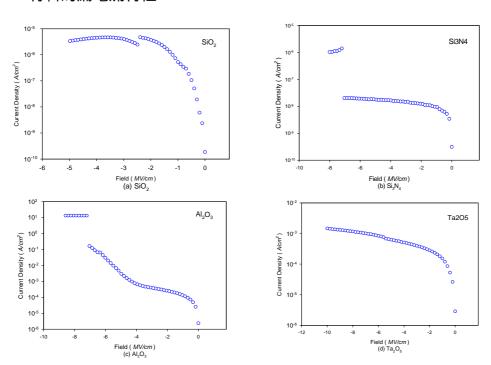

#### (4) High K 材料的漏電流特性

[圖十一] (a)SiO<sub>2</sub>薄膜電容以及(b)Si<sub>3</sub>N<sub>4</sub>薄膜(c)Al<sub>2</sub>O<sub>3</sub>薄膜電容(d)Ta<sub>2</sub>O<sub>5</sub>薄膜電容之漏電分析

觀察 high-K 薄膜的漏電特性,可以看到所沉積的 high-K 薄膜普遍有漏電問題,相較於傳統  $SiO_2$  薄膜,  $Al_2O_3$  和  $Ta_2O_5$  薄膜在電場強度 6MV/cm 的時候就有約  $mA/cm^2$  等級的漏電,基於此,我們接下來所要努力的是希望可以調整沉積條件,並結合 multi-layer 結構製作閘極絕緣層,希望在元件閘極電容值和漏電中取得最佳化。

#### 智慧型面板內建電路設計

在 IC 的經驗中,可將元件的變動分為二類。第一類為宏觀變動(macro variation):如閘極絕緣層的厚度、離子佈植量等等,其特點為元件的變動是同向的,在 LTPS TFT 中情況類似;第二類為微觀變動(micro variation):其特點為元件的變動是隨機的,在 IC 的經驗中是幾乎可以忽略的,但是在 LTPS TFT 中,由於晶粒邊界的影響,此變動量甚至會大於宏觀變動,必須特別重視。

在 IC 產業中,若想針對數位積體電路評估其訊號傳遞之效能,往往可經由 SPICE 中Worst Case 之模擬結果來進行分析,由於此種模擬技巧為針對電晶體之最好與最差參數進行整體電路之最快與最慢時間延遲分析,其優點為可快速評估數位積體電路之效能。然而,此種針對 IC 性能做評估之模擬方式卻不竟然可完全適用於 LTPS 之電路分析。以現今 LTPS 製程上的技術,在製程中會發生的製程物理變數變動是無法避免地,這同時也造成了在電路中是否每一個元件都互相匹配,亦或在同一片玻璃機板上也可能發生區域性元件不匹配之問題。有鑑於此,以 Monte Carlo 方式進行之電路模擬效能將會更適合 LTPS 之電路分析。

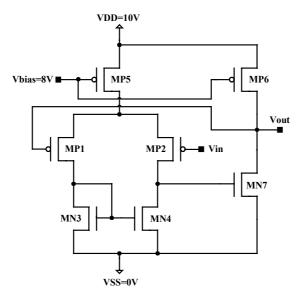

在 System on Panel 所用到的類比電路中,最重要的區塊單元即為單增益緩衝器(unigain buffer),其主要的應用,一是承接 DAC 至 sample & hold 電路,二是承接 sample & hold 電路至 data bus;其角色是以更大的驅動能力,將所要顯示的灰階電壓忠實的傳遞下去,其功能的要求是使輸出電壓等於輸入電壓,而放大對負載的推動能力,因此一方面可以應用在 DAC 與 sample & hold 之間,使 DAC 所用的電阻加大而減少功率消耗,另一方面可以應用在 sample & hold 與 data bus 之間,使 sample & hold 所用的保持電容更小,來加快資料驅動電路的操作頻率。

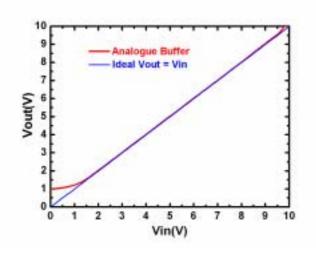

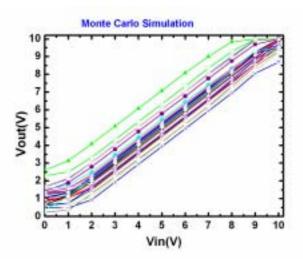

[圖十二]為一般常使用的運算放大器形式的單增益緩衝器,若只考慮元件的單一特性,[圖十三]為單增益緩衝器電路輸出電壓模擬結果,圖形顯示輸出電壓值線性度及誤差值均非常優良。但在真實情況中,LTPS TFT 元件特性隨機分佈的特點,造成即使相鄰的元件特性亦可能有很大的不同,因此電路設計時利用 Monte Carlo simulation 是當然必要的。[圖十四]所示為 Monte Carlo simulation 的輸出電壓模擬結果,圖形顯示輸出變動非常大,此為一般Worst case simulation 所無法觀察到的,而大的輸出變動將直接造成不均勻的垂直線條,因此電路設計上如何補償元件變動的影響,又使其在消耗功率仍具有競爭力,且其佈局面積可容納在封框膠內,是非常值得研究的課題,將是本計畫之後研究的重點之一。

[圖十二] OP-Amp-type 單增益緩衝器電路

LTPS TFT 面臨宏觀變動(macro variation)與微觀變動(micro variation),在應用的層面,宏觀變動造成的結果是不同模組之間的差異,具有較大的忍受空間;而微觀變動卻會直接造成電路性能很大的衝擊。

[圖十三]單增益緩衝器輸出電壓模擬結果

[圖十四]單增益緩衝器輸出電壓 Monte Carlo simulation 結果

# ▶ 計畫成果自評

本年度計畫目前完成 LED 光學模型的建立,並完成以光學追跡法計算 optical cavity 之均勻性與背光源出射角之最佳化,並推導出 optical cavity 與 LED 光場分佈與均勻度之間的一般式,也驗證有較佳的色彩表現。

第一年度的研究,提出一種新的 optical cavity 結構,除了完成電腦光學軟體模型建立,同時製作出原型並量測驗證結果,其推導的一般式可推廣到其他尺寸的設計。在設計過程中,累積了電腦光學軟體使用經驗,對往後設計光學模型有顯著的幫助。在實作過程中,所遇到 LED 散熱與 optical cavity 因應力扭曲的情況也是於接下來的設計所需要進一步考慮的。

於製程設計方面,首先在 SiGe 薄膜沉積條件控制下,我們可以得到不同鍵結模式的薄膜特性,其中可以看到,高濃度 Ge 含量確實會出現鍵結飽和的現象,而極可能在晶粒邊界

產生析出物。後續將進行薄膜再結晶動作以 SPM(Surface Potential Microscopy)分析晶 粒邊界的狀況,並配合摻雜進行薄膜電性分析。

另外,在製程溫度小於 100 的條件下,我們成功的製作出 High K 材料的電容元件。可與一般期刊的成果相比,因此在低溫的製程之下,我們是可以得到相當不錯的電容,藉由 High K 材料可以降低我們的操作電壓,最佳化低漏電的結構是接下來的研究內容。

於內建電路設計方面,目前完成元件特性變動資料庫之建立及元件變動模型參數之建立,並完成各種基礎電路區塊性能與元件參數變動的相關性評估。也利用 Monte Carlo 模擬技巧,評估移位暫存器基礎電路區塊性能與元件參數變動的相關性,來判斷出各元件參數對電路區塊特性的衝擊因素,作為高變動容許度之複雜數位電路設計的研究基礎。

第一年度的研究,已提出新的類比緩衝器電路設計技術,繼續開發具元件變動容許度 及功率消耗、佈局面積等方面皆可符合實際應用的其他各種基礎電路區塊,是非常值得研 究的課題,也是本計畫之後研究的重點之一。

在執行本計畫的過程中,亦衍生出一些與可靠度相關的發現,此有助於未來進階的元件可靠度模型之建立。

由以上具體成果,認為本年度計畫已為後續研究建立了良好的基礎。