# 行政院國家科學委員會補助專題研究計畫成果報告

## 無線通訊之時空域信號處理(一) Space-Time Signal Processing for Wireless Communication (I)

計畫類別： 個別型計畫 整合型計畫

計畫編號：NSC 89 - 2219 - E - 009 - 013

執行期間：88 年 8 月 1 日至 89 年 7 月 31 日

計畫主持人：林大衛 交通大學電子工程系所 教授

本成果報告包括以下應繳交之附件：

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

執行單位：國立交通大學電子工程系所

中 華 民 國 八十九 年 十 月 三十一 日

# 行政院國家科學委員會專題研究計畫成果報告

## 無線通訊之時空域信號處理(一)

### Space-Time Signal Processing for Wireless Communication (I)

計畫編號：NSC 89-2219-E-009-013

執行期限：88 年 8 月 1 日至 89 年 7 月 31 日

主持人：林大衛 交通大學電子工程系所 教授

計畫參與人員：周志昇、林郁男、何健豪、賴侑呈、吳俊榮 交通大學電子工程系所

#### 一、摘要

我們研究無線傳輸系統中，有效使用無線通道之技術，含時空域信號處理之方法及使用數位訊號處理器遂行實現之方法，其中著重寬頻分碼多重進接系統之上鍊傳輸。在一般時空域信號處理方面，我們考慮時空域維特比等化器之架構，研究其訓練序列與傳輸信號結構的設計、以及等化器的設計與效能。在寬頻分碼多重進接之時空域信號處理方面，我們考慮平行式干擾消除及其與天線陣列信號處理之結合架構。在數位訊號處理器發展系統之使用方面，我們研究了晶片板子上與板子間的資料傳遞方法，並用晶片板試做無線通道之模擬。

**關鍵詞：**寬頻分碼多重進接、時空維特比等化、時空域信號處理、陣列信號處理、平行式干擾消除、數位訊號處理器實現

#### Abstract

We research into techniques for efficient usage of wireless channels in wireless transmission systems, including space-time signal processing and its DSP implementation, with emphasis on WCDMA uplink transmission. On general space-time signal processing, we consider space-time Viterbi equalization. We research into the design of the training sequence and the transmitted signal structure, as well as the design of the equalizer and its performance. On space-time signal processing for WCDMA, we consider parallel interference cancellation (PIC) and its combination with antenna array signal processing. On the use of DSP development systems, we study the methods of on-board and inter-board data transfer, and we attempt wireless channel simulation on the DSP board.

**Keywords:** WCDMA, Space-Time Viterbi Equalization, Space-Time Signal Processing, Array Signal Processing, Parallel Interference Cancellation (PIC), DSP Implementation

#### 二、計畫緣由與目的

本計畫研究有效地使用無線通道之技術，含時空域信號處理之方法及使用 DSP 遂行其實現之方法，其中著重寬頻分碼多重進接(WCDMA)系統之上鍊傳輸。其一主要目的在與其他子計畫共同完成一個 WCDMA 上鍊傳收系統之設計與 DSP 實現。本計畫本年度之研究項目有三：一是般時空域信號處理技術，二是 WCDMA 上鍊傳輸之時空域信號處理技術，三是 DSP 發展系統使用方法的了解。

在一般時空域信號處理方面，我們研究有關時空域維特比等化器之設計與效能。我們探討訓練序列的設計以及傳輸信號的結構的設計，以使在不增加接收器複雜度之情形下，提升傳輸效能。我們也研究等化器長度的選擇。因為在有通道雜訊時，通道響應估計的精確度與在做通道估計時所設定之通道長度有關(不是越長越好)。這估計精確度會影響接收品質，而等化器長度又會影響等化器複雜度。

在 WCDMA 上鍊傳輸之時空域信號處理方面，我們考慮平行式干擾消除(PIC)及其與天線陣列信號處理之結合。在 CDMA 系統中，多用戶係共用同一通道傳輸，而各用戶之信號間並非完全正交，因此若透過時域信號處理來將信號之相關性造成的影響消減，就可提高傳輸品質。PIC 的原理，是對每一用戶信號做一次決策(其中可能有錯誤)，用此產生不同用戶間的相互干擾的一個估計，將之減去，再做下一次的決策，如此反覆進行。其決策方法可以是硬式(hard decision)或軟式(soft decision)，將之與天線陣列信號處理方法結合，就形成

一種特別的時空域信號處理機制，可用以提高初始接收的正確率，以提高最後接收器輸出的正確率。

在 DSP 發展系統之使用方面，由於預期總計畫最後完成的系統將使用不只一顆晶片，且將使用 fixed-point 與 floating-point 兩種 DSPs，本年此方面的研究是針對我們所採用的 DSP 板子，探討不同的 DSP 晶片之間的通訊方法，以在不同晶片之間做有效的傳輸。此外，也試在 DSP 板子上做無線通道之真時模擬。

### 三、結果與討論

#### A. 一般時空域信號處理

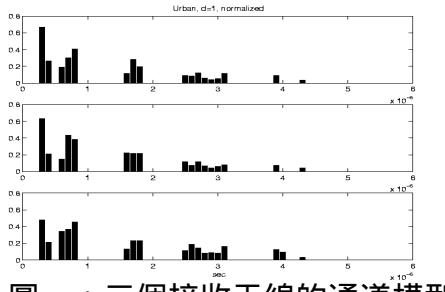

首先，我們須建構一些合適的通道響應以為模擬之用。我們參考文獻[1]中所提的通道模型，產生多組在不同的向量通道模型。此向量通道模型可適用於多天線(陣列)的傳收系統中。依此所建立的通道模型包含了多種環境，如：鬧區、郊區與山地等區域。圖一所示為一用此方法所產生之三個天線的通道脈衝響應振幅圖。

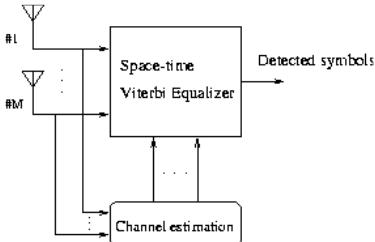

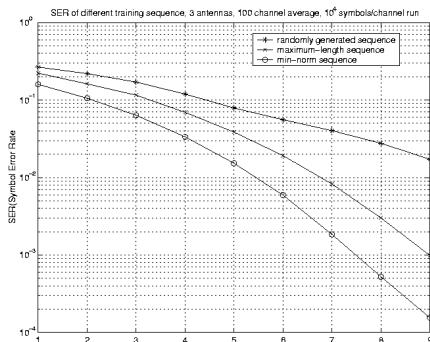

在時空域信號處理方面，我們使用一個時空域維特比(Viterbi)等化器當接收端的信號處理核心，如圖二所示。我們設計了一個最小誤差量訓練序列(min-norm training sequence)，並將之與使用隨機序列及最大長度擬真亂數序列(maximum-length pseudo random sequence)為訓練序列之結果做比較。如圖三所示，我們設計的最小誤差量訓練序列有最佳的效果。

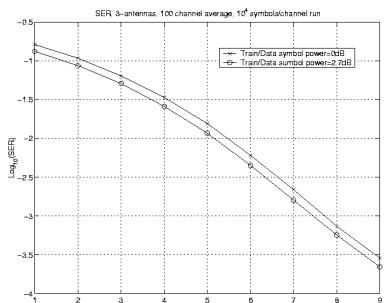

另外我們也考慮令訓練序列與資料序列中的符碼(symbol)能量有所不同。因為一般訓練序列的長度約為資料序列長度的八分之一至十分之一，所以若令訓練序列中每一符碼的能量高於資料序列中每一符碼的能量，則可能使利用訓練序列所做的通道脈衝響應估計較準確，進而使維特比等化器能有較佳之結果。圖四所示為訓練序列中每一符碼的能量略高於資料序列中每一符碼的能量約 2.7 dB 之結果。

此外，我們也研究等化器長度的選擇。因為在有通道雜訊時，通道響應估計的精確度與在做通道估計時所設定之通道長度有關。此設定之通道長度並不是越長越好，是與雜訊強度有關。通道估計之精確度會影響接收品質，而等化器長度又會影響等化器複雜度。我們研究了通道長度的選擇與接收品質的關係。

相關研究有部分已發表於[2]，另外有投

稿一篇期刊論文[3]。

#### B. WCDMA 上鍊傳輸之時空域信號處理

本部份研究考慮平行式干擾消除(PIC)及其與天線陣列信號處理結合的效果。如前述，PIC 各級之決策可為硬式或軟式。我們的研究中比較了硬式與軟式決策的品質，其中一種軟式決策為[4]所稱為 NMIC 的架構。

在使用天線陣列的系統中，用戶的特性並非只有時間上展頻碼的不同，還有空間上所形成陣列向量的不同。以線性陣列為例，從方向角  $\theta$  入射的訊號會在  $M$  根相鄰半波長的天線所形成的陣列上構成陣列向量：

$$A(\theta) = [1 \ e^{-j\frac{\pi}{\lambda} \sin\theta} \ \Lambda \ e^{-j\frac{\pi}{\lambda} (M-1) \sin\theta}]^H$$

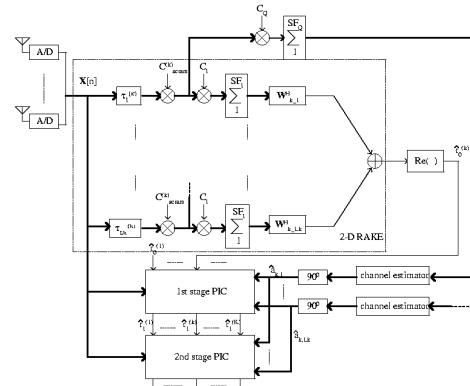

若在接收端以  $A(\theta)$  為空間上的濾波器，則在兩不同方向  $\theta$  及  $\theta + 180^\circ$  的用戶在空間上的相關性為  $A(\theta)A^H(\theta + 180^\circ)$ 。若假定所有用戶的所在位置是均勻分佈在  $60^\circ$  與  $-60^\circ$  之間，則空間向量為用戶的訊號間提供了  $M$  倍的 processing gain；也就是，經由空間濾波後的結果，會使系統的展頻係數等效增為原來的  $M$  倍。如此，我們可以傳輸  $M$  倍於原來的資料量而不至於有系統效能的衰減。我們的研究係基於 3GPP 的標準 WCDMA 規格。由於此規格中，在 Q channel 中定義了 pilot symbol，所以我們可以利用之來估測陣列向量及路徑係數而用於 2-D rake 的架構上。由於我們考慮的傳輸速率遠大於第二代的系統，因此，展頻係數必然不能太大。對 NMIC 等軟式決策 PIC 接收法，我們推導出了適用於天線陣列及多重路徑下的決策曲線形式。

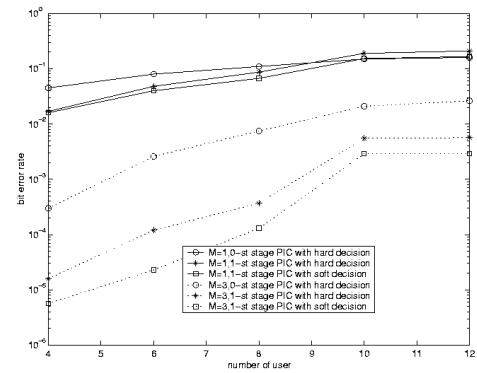

完整的接收器架構如圖五所示。圖六是部份在 3GPP 規格下的模擬結果，以位元錯誤率為評量的標準。其中所謂 hard decision 即為標準的 PIC，而 soft decision 則為 NMIC 架構。從模擬的結果可看出，在未使用天線陣列的情況下，由於初始訊號的正確率未達一定標準，所以 PIC 並無法提供消除干擾的效能。因此，以天線陣列提高初始正確率，再搭配 PIC 的接收器架構應是不錯的選擇架構。

以上部分結果已刊載於國際會議論文集[5]。

#### C. DSP 發展系統的使用

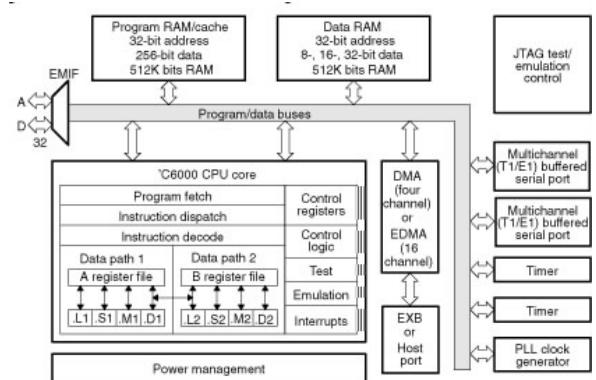

我們所採用的 DSP 板是 Blue Wave Systems 的 PCI6600，其上裝置德州儀器公

司出品的 TMS320C62xx fixed-point 或 C67xx floating-point DSP chips 二顆(參圖七)。它是透過主機板上的 PCI 汱流排和 PC 做連接，由 PC 控制 DSP 晶片的運作，包括程式的載入和執行，並可由 PC 端做運算結果的驗證。

在硬體實現方面，目前已初步完成基頻的通道以及調變和解調的模擬。這幾個部分放在同一顆 DSP，可以避免在不同 DSP 之間大量資料傳輸所損耗的時間。至於接收器部分需要等到通通方面整個架構完成才能進入硬體模擬的階段，目前只是在 PC 上作一些演算法驗證的動作。

在通道方面，規格為 3.84 Mchips/s 以上。現階段我們的軟體達到的速度，在通道情況為一個使用者三條路徑以及在接收部分使用三個天線的時候，約為 1.024 Mchips/s。和標準尚有一段差距。

處理速度不足的原因主要有兩點：

1. 在 DSP 存取記憶體浪費太多時間。DSP 的記憶體可分作內部和外部兩種；內部記憶體較小，大約只有 64 Kbytes，但是由於就在 DSP 裡面，所以存取速度極快。而外部記憶體較大，有 32 Mbytes，但存取較慢。由於程式中所需的記憶體極大，內部記憶體放不下，必須放到外部。若是用一般的存取法而不用 DMA(直接記憶體存取)，就會把絕大部分的時間(約 95%)花在記憶體的存取方面，而拖慢處理速度。採用 DSP 提供的 DMA 機制來做資料的輸入與計算結果的輸出以後，發現速度提高約十倍，達到上述之 1.024 Mchips/s。但是 DMA 還是會消耗一定的時間在存取方面。根據簡單的測量，約有三分之一的時間花在這上面。

2. 通道模擬需要複雜的運算。由於我們所模擬的通道是時變的，且所有的數值都是複數，所以每一個 chip 平均需要約一百個乘加運算。按照標準規定的 chip rate，我們的模擬器在每秒就要作 384M 個乘加運算。雖然我們所用的 DSP 號稱每秒可以達到 1G 的乘加運算，不過這是在六個運算單元都同時在工作才會有的表現。實際上，在經過編譯器轉換後，大部分的運算通常只會用到兩個左右的運算單元。這方面的改進方法是可以將幾個較大的迴圈改用組合語言寫，而不靠編譯器來轉換。這樣可以提高平行處理的程度，以提昇速度。不過這一方面牽涉到細部的變動，另方面除錯時也較麻煩，所以必須等到接收器也完

成後才能作更進一步的改善。

為提高通道部分的計算速度以求能應付系統所需，未來除了改進程式以外，還可以考慮將不同的傳輸路徑分到不同 DSP 來算。在接收器的實現部分，目前接收演算法的研究已有相當成果，可以逐漸進入 DSP 實現的階段。目前規劃是暫時只考慮用一個 DSP 來實現接收器，將來視情況需要再考慮將工作分到不同的 DSP，以求速度能符合所需。

#### 四、計畫成果自評

研究內容與原計畫相符程度：大體相符，細節有些出入。在一般時空域信號處理方面，原考慮之架構為多級時空結合的架構，現調整為維特比等化器，以期能有較佳之效能。相符程度 80%。

達成預期目標情況：創新之發現、理論之推導與模式建立、計算機模擬軟體之建立、實驗系統之初步建立、人才培育。

成果之學術與應用價值等：學術價值高，部分成果已發表於國際會議、部分在投稿中。應用價值方面，WCDMA 之時空域信號處理及無線通道之 DSP 模擬二者之應用價值高，亦將於下二年計畫中繼續演算法之研究與 DSP 實現。一般時空域信號處理方法之應用價值為中等，亦將繼續進一步之研究。

綜合評估：本計畫獲得一些具有學術與應用價值的成果，符合三年期總計畫之 WCDMA 上鍊傳收系統研究與 DSP 實現之目標，並達成人才培育之效。自評為「佳」。

#### 五、參考文獻

- [1] H. Hashemi, "Simulation of the urban radio propagation channel," *IEEE Trans. Vehicular Technology*, vol. 28, no. 3, pp. 213-225, Aug. 1979.

- [2] C.-S. Chou and D. W. Lin, "Training techniques of space-time Viterbi equalizer for high speed mobile communication," in *Proc. Int. Symp. Circuits Syst.*, May 2000.

- [3] C.-S. Chou and D. W. Lin, "Signal design and receiver dimensioning for space-time Viterbi equalization," submitted to *IEE Proc.-Communications*, Dec. 1999.

- [4] D. Divsalar, M. K. Simon, and D. Raphaeli, "Improved parallel interference cancellation for CDMA," *IEEE Trans. Commun.*, vol. 46, no. 2, Feb. 1998.

[5] Y.-N. Lin and D. W. Lin, "Performance comparison of several parallel interference cancellation techniques under the 3GPP WCDMA specifications," to appear in *Proc. Asia Pacific Conf. Commun.*, Nov. 2000.

## 六、圖表

圖一：三個接收天線的通道模型

圖二：時空域維特比等化器架構

圖三：使用不同訓練序列時的符碼錯誤率

圖四：訓練符碼與資料符碼的能量不同時的符碼錯誤率

圖五：陣列天線接收器的架構

圖六：位元錯誤率之比較

圖七：TI TMS320C6x 之架構圖(取自 TI 文獻)