# 行政院國家科學委員會專題研究計畫 期中進度報告

子計畫五:針對無線通訊上佈局驅動的資料路徑合成器之研 究(2/3)

計畫類別:整合型計畫

計畫編號: NSC92-2220-E-009-022-

執行期間: 92 年 08 月 01 日至 93 年 07 月 31 日

執行單位: 國立交通大學電子工程學系

計畫主持人: 周景揚

報告類型: 完整報告

報告附件: 出席國際會議研究心得報告及發表論文

處理方式:本計畫可公開查詢

中華民國93年6月1日

# 行政院國家科學委員會補助專題研究計畫 成果報告 期中進度報告

計畫名稱:針對無線通訊上佈局驅動的資料路徑合成器之研究(2/3)

計畫類別: 個別型計畫 整合型計畫

計畫編號: NSC 92 - 2220 - E - 009 - 022

執行期間: 92年 8月 1日至 93年 7月 31日

計畫主持人:周景揚

共同主持人: 計畫參與人員:

成果報告類型(依經費核定清單規定繳交): 精簡報告 完整報告

本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

處理方式:除產學合作研究計畫、提升產業技術及人才培育研究計畫、列管計

畫及下列情形者外,得立即公開查詢

涉及專利或其他智慧財產權, 一年 二年後可公開查詢

執行單位:

中 華 民 國 93 年 5 月 20 日

# 針對無線通訊上佈局驅動的資料路徑合成器之研究 (2/3)

"The Study on Layout-Driven Datapath Synthesizer for Wireless Communication"

計畫編號: NSC 92 - 2220 - E - 009 - 022

執行期間:92年8月1日至93年7月31日

主持人:周景揚 交通大學電子工程系教授

#### 1. 中文摘要

由於半導體技術的突飛猛進,單晶片系統 (SoC)已經變成了二十一世紀裡的主流科技,藉由單晶片系統的技術,可以加速促成三 C(電腦、通訊、民生家電)之間的整合,這不管對企業或是科技來說,都是一股不可避免的潮流,對整個人類社會來說,三 C 的整合應用更是一個非常重要的進步。

以往人們的期望只是一個快速、可靠且容易使用的無線通訊系統,但現在人們的要求已不僅僅如此,他們期待能有更快速的方法來透過無線通訊存取資料,以便應付現在的各種應用,例如收發電子郵件、檔案傳輸協定、網路瀏覽器、甚至即時影像傳輸等等,對無線服務提供的廠商來說,它們若想繼續保有競爭力,就必須跟上這個時代潮流。在這個整合計畫中,我們主要就是針對 Beyond 3G(B3G)的無線通訊網路來做研究,特別是其中的單晶片系統技術。

快速傅利葉轉換處理器與逆向快速傅立 葉轉換是正交分頻多工通訊系統(OFDM)中重 要的元件,如數位電視(HDTV),xDSL modem 等, 再者,由於超大型積體電路逐漸複雜以及系統 晶片的觀念,設計者必須在短時間內完成複雜 的系統,如何使用設計自動化的方式將快速傅 利葉轉換處理器設計時程降低成為一個重要 的課題。

到目前為止還有很多研究進行中以改善 其效能。另外,由於硬體中有效字元長度的影 響,量化誤差的選擇在系統設計上也是一項精 確度與硬體資源消耗的取捨。因此如何在一定 的量化誤差之下盡量減少硬體資源也是一個 值得探討的問題。在本篇論文中,我們提出了 一個方法,針對了管線化快速傅利葉處理器每 級架構規律的特性,試著自動化快速傅利葉處 理器的設計流程。利用系統設計者所提供的快 速傅利葉處理器點數、訊號對量化雜訊比 (SQNR)和處理器速度限制,我們可以藉著調整 每級之字元長度,而對特定的管線化快速傅利 葉處理器的面積或功率作最佳化。為了減少使 用者的設計時程,在我們提出的流程中,自動 產生一個擁有週期準確度可模擬的模型,提供 設計者方便靈活的模擬環境。

# 英文摘要

With the advent of semiconductor technology, the System-on-a-chip (SoC) becomes a mainstream and focus of technologies on coming 21<sup>st</sup> century. The integration of Computing, Communication and Consumer Electronics will be speeded up through SoC, which causes the unavoidable trend of new era for technology and enterprises. Especially, the application of 3C integration is very important to the progress of human being society.

People all over the world have come to expect fast, reliable, and easily accessible wireless communications and now they are demanding faster ways to access data with applications as diverse as e-mail, file transfer protocol, Internet browsers, and even real-time video teleconferencing. Wireless service providers who want to remain competitive must keep pace with this demand. In this integrated project, we are targeting on the study of beyond 3G wireless networks. Particularly, we are focusing SoC technologies for on **OFDM-based SDR baseband processing.**

FFT and IFFT are important components of Orthogonal Frequency Division Multiplexing (OFDM) systems in many communication applications such as HDTV, xDSL modem, and wide band mobile terminals. With the increasing complexity in modern Very Large Scale

Integrated circuit (VLSI) design and the conception of system-on-chip (SOC), designers have to complete a complicated system design in a short time. Therefore, it is a key issue to reduce design time of FFT processors through design automation.

Much research is still undertaken to improve its performance. Furthermore, subject to the effect of finite wordlength in hardware, a trade-off between precision and hardware resource has to be made. Accordingly, it is a key issue to maximize the precision at the minimal cost of hardware complexity. This thesis presents a solution to automate the design flow for pipelined FFT processors that are characterized by the regularity in each stage. We can adjust the wordlength in each stage to obtain the optimization of the area or the power for specified pipelined FFT processors by using the of constraints of FFT. point signal-to-quantization-noise ratio (SQNR), and speed of processors. To decrease the design time, our flow is capable of generating automatically a timing accuracy model which can be simulated. This feature provides designers a flexible simulation environment.

# 2. 計畫的緣由與目的

不同的演算法及其架構會有不同的特性,使用於不同的應用,如何選擇一個最適合的架構,會是系統設計者最重要的任務,而複雜的交互關係,使得設計者難以找到最佳解,一般找到適當的解,可以滿足所需條件,但晶片面積不一定是最小。

再者,有效字元長度也是一個最佳化的問題,如何讓晶片面積做最有效的運用,影響結果精確度重要的地方,就應該資料長度多一點,這方面的問題需要使用電腦輔助分析,才能很精準的獲得最佳解。

#### 3. 研究方法及成果

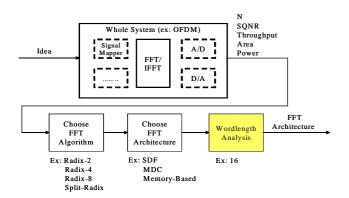

#### (1) Overall Design Flow of FFT Processors

上圖是整個 FFT 處理器的設計流程,首先,整個系統會作完整的分析,獲得系統所需要的規格,如點數,SQNR,Throughput...等等的資訊,當我們有這些資訊,我們可以選擇適當的 FFT 演算法,FFT 架構,這些 Design Space Exploration 的部分,會影響整個系統的效能,以及所需的硬體,而選擇這些架構是需要

很有系統的分析,才能找出最佳解,傳統上,經由架構設計者去分析整個系統,試著尋找適當的架構,這樣的做法,非常需要設計經驗,而且有些複雜的分析設計者無法系統化的分析。因此使用電腦輔助去最佳化,會試著找出最佳解。架構上確定之後,可以使用模擬分析的方式,找出最有效率的使用硬體。

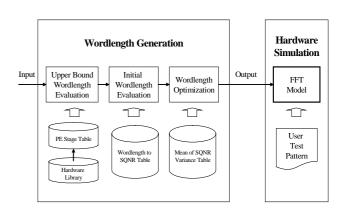

# (2) Word Length Generation Flow

設計者可藉由一些機率的分析,找出系統 效能與資料表示所需長度的關係,但是這樣的 分析都是經由一些假設,因為複雜的交互關 係,會使得設計者很難找出簡單的描述關係 式,進而很難找到最佳解。

#### (3) Library and Table

我們需要底層的資訊,經由抽象化的過程,建立所需要的資料,這些的資料可以作為 我們系統分析所需要的資訊。我們會對這些抽 象化過程中最重要的參數尋找出來,作為我們 最佳化時所需要更改的參數。這些底層的建 構,我們使用合成軟體,合成出各式各樣的元 件,再經由分析軟體去找出他們的特性。建立 所需的資料庫。經由這些資料,我們可以分析 一個設計可以工作的時脈,所需要的記憶體, 所使用的面積,系統的效能,這些的資訊都可 以經由資料建構出。

# (4) Upper Bound Word Length Evaluation

因為系統所要求的處理速度是給定的,所以在一特定架構下,就會有工作所需的時脈,而元件的工作時脈跟資料的長度有關,所以這時脈就會限制資料的長度,如果資料長度超過允許值,工作時脈就無法達到需求,而系統要求的處理速度也就無法達到。如果這樣的資料長度無法滿足所需,表示應該選擇另一個處理能力更強的架構,但是相對的就會花費更多的面積來達到要求。

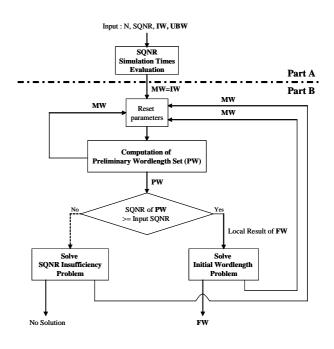

#### (5) Initial Word length Evaluation

為了減少最佳化時,所需要執行的時間,尋找一個與最佳解相近的初始解是非常重要的。因為與最佳解接近,表示只要經過幾次的尋找,就可以找到最佳解,而如果離最佳解很遠的話,就要經過很多步驟,才能達到最佳解,甚至如果走到小區域裡的最佳解,並不會是真正的系統最佳解。我們會經由我們之前建立的資料尋找最適當的值,但是這個適當的值是整個系統都是一致時所表現出來的效能。之後我們會對它的每一個可更改的地方作最佳化

# (6) Word Length Optimization

在逼近最佳解的過程中,我們會試圖 尋找最有利的地方,作最佳化的方向,在最佳 化的過程中,逐漸讓資料長度變小,在這裡我 們定義最有利是 SQNR / Area 最大, SQNR 越 大越好,而面積越小越好,當我們找到目前最 好的解的時候,我們會把每一個參數都加一, 然後再由相同的方式進行最佳化,這樣可以避 免有些初始長度不夠的狀況,如果加一之後尋 找的最佳解,與之前的最佳解一樣,就表示我 們已經找到最佳解了。

#### (7) Infrastructure

使用 SystemC 的環境,作 SQNR 的分析, Area 的分析, Timing 的分析,整個環境都建構在單一的平台上,在系統設計上,使用一致的設計環境,並在此環境下作設計最佳化

的演算法,作design space exploration。

#### 4. 結論與討論

在本報告中,我們提出了一個完整的流程,可以產生出各種 FFT,初步的成果相當令人滿意。

表一簡列近年本研究群的相關研究成果。89年發表會議論文5篇,期刊論文6篇。90年發表會議論文8篇,期刊論文3篇,並有3篇論文於IEEE期刊發表,91年發表會議論文2篇,期刊論文3篇,並有3篇論文於IEEE期刊發表,92年及以後發表會議論文12篇,期刊論文4篇,並有1篇論文於IEEE期刊發表。

|       | Number of Papers |         |               |           |     |

|-------|------------------|---------|---------------|-----------|-----|

| Year  | r Domestic       |         | International |           | SCI |

|       | Conference       | Journal | Conference    | Journal   |     |

| 2000  | 0                | 0       | 5             | 6         | 6   |

|       |                  |         |               | (IEEE:4)  |     |

| 2001  | 2                | 0       | 8             | 3         | 3   |

|       |                  |         |               | (IEEE: 3) |     |

| 2002  | 3                | 0       | 2             | 3         | 3   |

|       |                  |         |               | (IEEE:2)  |     |

| 2003> | 4                | 0       | 8             | 4         | 4   |

|       |                  |         |               | (IEEE: 1) |     |

表一、本研究群近年相關研究成果

#### 5. 參考文獻

[1] Cheng-Yeh Wang, Ya-Chi Yang and Jing-Yang Jou, "An Automatic Layout-Driven Multiplier Generator," the 13th VLSI Design/CAD Symposium, Hsinchu, August 2002.

- [2] Cheng-yeh Wang, Tson-Yee Lin and Jing-yang Jou, "On Automation of Wordlength Optimization in Pipelined FFT Processors," submitted to IEEE Trans. on VLSI.

- [3] Cheng-Yeh Wang, Ya-Chi Yang and Jing-Yang Jou, "An Effective Physical Synthesis Technique for Multiplier," International symposium on VLSI technology, systems, and applications, 2003.