### 行政院國家科學委員會專題研究計畫 成果報告

### SOC 系統整合設計驗證及測試環境建置

計畫類別: 個別型計畫

計畫編號: NSC92-2220-E-009-001-

執行期間: 92年04月01日至93年03月31日

執行單位: 國立交通大學電子工程學系

計畫主持人:周景揚

共同主持人:蘇朝琴,孟慶宗,陳紹基

報告類型:精簡報告

處理方式:本計畫可公開查詢

中華民國93年9月3日

# 行政院國家科學委員會補助專題研究計畫 成果報告

計畫名稱:SOC 系統整合設計驗證及測試環境建置

計畫類別: 個別型計畫 整合型計畫

計畫編號: NSC 92 - 2220 - E - 009 - 001

執行期間: 92年 04月 01日至 93年 03月 31日

計畫主持人:周景揚

共同主持人: 計畫參與人員:

成果報告類型(依經費核定清單規定繳交): 精簡報告 完整報告

本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

處理方式:除產學合作研究計畫、提升產業技術及人才培育研究計畫、列管計

畫及下列情形者外,得立即公開查詢

涉及專利或其他智慧財產權, 一年 二年後可公開查詢

執行單位:國立交通大學 電子工程學系

中 華 民 國 93 年 9 月 2 日

#### SOC 系統整合設計驗證及測試環境建置

"Infrastructure Construction for System Integration, Verification and Testing for SOC"

計畫編號: NSC 92 - 2220 - E - 009 - 001

執行期間: 92 年 04 月 01 日 至 93 年 03 月 31 日

主持人:周景揚 交通大學電子工程系教授

#### 1. 中文摘要

關鍵詞:測試、混合信號、系統晶片、遠距、 射頻積體電路、設計驗證

本計畫的主要目標在於建構 SOC 中心下二個實驗室之基礎環境建置,其相關說明如下:

第一個子計畫的主要目標在於建構一個 SOC 整合之驗證環境,使得複雜之系統晶片設 計流程能快速、正確的完成,並得到高效能的 結果。隨著系統單晶片時代的來臨,設計的層 次已經從 RTL Level 提升到 System Level, 傳統 ASIC 設計及驗證流程已經無法有效率的 考慮到系統單晶片設計各個影響設計的變 因。尤其現今複雜的系統,無論是通訊系統, 嵌入式系統,都有軟體及硬體的部分。如果缺 乏一個軟硬體共同的設計及驗證平台,整個計 畫的執行將很難成功。

第二個子計畫的主要目標在於建構一個透過網路執行的遠距混合信號 SOC 測試環境,使用者可以透過網路介面操控儀表,對遠端待測電路進行測試。主要的目的在於提供 SoC 測試相關研究人員一個測試技術開發與發展平台。測試儀器的建構以測試基頻類比與數位電路為主,主要的應用在於語音與影信處理的類比數位信號以及晶片間的介面電路。透過網路的延伸,本計畫服務的對象不只是區域性的相關教師,更能涵蓋全國測試相關的師生,建構一套適用測試技術發展之混合信號測試環境。

#### 英文摘要

Keywords: Testing, Mixed Signal, System on Chip, Remote, Radio Frequency, Design Verification

This project is aimed at constructing basic infrastructures for advanced research in NCTU SOC Research Center. It includes two sub-projects.

The first sub-project is aimed to establish and deploy an integrated SOC design, verification and validation environment for fast, efficient and correct design of an SOC system. With the advent of SOC era and huge demand of high-performance computing devices, conventional RTL Level design methodology quickly migrates to system level (on a chip) methodology. Traditional ASIC design and verification flow is inefficient for SOC design.

The second sub-project is to build a remote testing infrastructure for mixed signal SoC. Users are able to adjust the control panel of the instrument to test the circuit remotely. The instrument for the basic infrastructure include mostly basic digital and analog test equipment and instrument. The target applications include audio, video, power electronics, and interface integrated circuits. The main purposes of this lab is to support not only the testing itself but also the mixed signal test technology development. Through remote testing concept, it will not only cover regional faculties and students but also those all over the island.

#### 2. 計畫的緣由與目的

晶片系統(SOC)國家型科技計畫之總目標為整合我國 SOC 科技相關之研究人才與技術資源,推動 SOC 科技整合,以建立台灣成為全球 SOC 設計研發中心。而 SOC 基礎環境建置以支援晶片系統國家型科技計畫為主要目的。所建立共用設備,除提供相關研究所需之外,並需對外開放服務,並兼具人才培育之功能。

交通大學在 SOC 領域之研發能量是國內數一數二,且其近年來之輝煌研究成果也是有目共睹的事實。值此國家大力推動 SOC 計畫以提升我國科技競爭力,本校深感責無旁貸,必當全力配合,共襄盛舉。最近本校亦整合所有相關系所研究群,共同成立 SOC 中心,期能有效整合人力及設備資源以從事傑出研究並培養相關人才。

國立交通大學晶片系統(System-On-Chip, SOC)研究中心整合校內教師及相關資源,配合國家『矽導計畫』之執行,有效推動 SOC設計之研究發展、智產推廣、學程推動、與人才培訓等工作。中心將以尖端研究建立 SOC設計所需之核心技術及其各項應用。所涵蓋的領域包含計算機輔助設計、積體電路設計、微機電系統、通訊系統、網路系統、計算機系統、即時操作系統、以及多媒體處理等等。除了發表論文外,中心的研發成果將包含各種輔助設計軟體、矽智產、晶片、與應用系統雛型等。

從 91 年起,本校已有一進行中之晶片系統國家型科技計畫"The Study of SOC Design Technologies for OFDM-Based SDR Baseband Processing"以及 92 年起本校預計還有三個 SOC 整合型計畫,為了能充分發揮研究能量,造就相關頂尖人才,並進而提供尖端技術服務以提升其他研究團隊之研發效能,本中心經幾次集思廣益之討論,決定逐年建立上述 SOC 相關之尖端實驗室,因而本校這次共提 SOC 中心下三個實驗室之基礎環境建置,其背景以及目的說明如下:

# I. **子計畫**一 晶片系統整合驗證實驗室基礎環境建置

Establishment of Basic Lab Environment for

SOC Design, Integration, Verification and Validation

隨著系統單晶片時代的來臨,設計的層次已經從RTL Level 提升到 System Level,傳統ASIC 設計及驗證流程已經無法有效率的考慮到系統單晶片設計各個影響設計的變因。尤其現今複雜的系統,無論是通訊系統,嵌入式系統,都有軟體及硬體的部分。如果缺乏一個軟硬體共同的設計及驗證平台,整個計畫的執行將很難成功。

所以對於「軟硬體並行設計、驗證」的相關研究,其中包含從系統的規格書到系統的模型,效能的估計,軟硬體的分割,設計後的軟硬體共同模擬等等工作,需要一個有效率,合理並實際的設計驗證流程及平台,使其可以在設計初期可以確認規格書及系統模型的正確性,系統效能的初期分析,再進入有效率及合理的軟硬體分割,之後還可以方便的執行軟硬體共同模擬驗證。在中、後期也可以快速的作Simulation 或 Emulation 來驗證整個 SOC Design,而其中我們除了必要的商業 EDA Tool外,還需要一些相關的硬體特別是 SOC 設計及驗證平台之建立。

#### II. **子計畫二** 遠距混合信號 SOC 測試環境 建置

Remote Mixed Signal SoC Testing Infrastructure

混合信號測試為 SOC 測試之基礎。一個 SOC 晶片,必定包含有數位類比與混合信號電路部份。以三年的近期而言,基頻中的語音與影像處理所使用到的 1MHz 至 200MHz 間的類比信號與頻率在 1GHz 以下的數位傳輸仍會是 SOC 的主流。此一方面的測試技術的開發與測試環境的發展。因此,此一計畫的目的在建制使用最為廣泛的 1GHz 以下的一個完整的混合信號電路測試環境。有鑒於網路的發達,遠距測試已經是以個較為經濟的測試模式。使用者可以在遠端操控儀表已達成測試的目的。此學與研發團隊使用,以達到資源集中、資源共享、經費節約的目的。

除了設計的族群,台灣測試技術相關的族群也相當的龐大。VTTF台灣超大型積體電路測試論壇就集合了全國二十六位師資。測試技術的開發與設計驗證的測試同樣需要大量的設備。由於測試相關的教師分佈於全台各地,設備共用不易。遠距測試的建構可以解決測試上設備取得的問題。

目前全國各校各系或多或少都有部分之基礎混合信號測試能力,然而年代久遠,多數

都面臨淘汰換新的階段。再者,除了測試技術日新月異,儀表的功能快速增加,網路與通訊的功能也被視為是儀表的基本配備,這一切都是傳統儀表所無法提供的功能。因此,建構一個完整的網路遠距測試環境,藉由儀表共用減少重複的建置,藉由專業的管理與操作減少儀器的損壞,最能符合經濟效益的,而且是刻不容緩的。

#### 3. 研究方法

#### I. **子計畫**一 晶片系統整合驗證實驗室基礎環境建置

Establishment of Basic Lab Environment for SOC Design, Integration, Verification and Validation

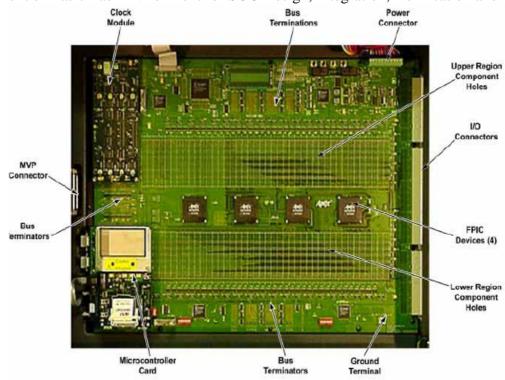

# (1). Aptix System Explorer 的硬體架構可分成下列部份(如上之附圖):

- Component hole area

- User buses

- Global interconnects

- I/O connections

- Power distribution

- Clock generation and distribution

- Microcontroller

#### (2). 利用 MVP 加速系統整合設計模擬時效步

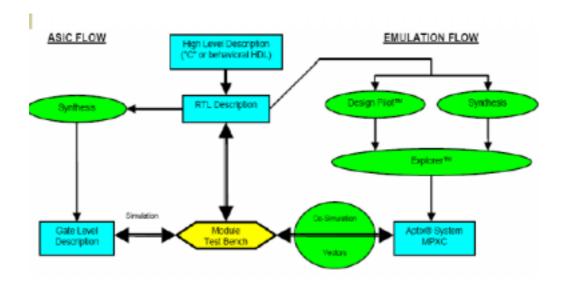

驟與流程,如下頁附圖所示。

系統經由 C 或者是 HDL 這種較為抽象的語言把整體行為描述出來,經由 EMULATION FLOW 可以快速驗證其想法以及初步得到其效能以及所需硬體的估算,如果有些部份設計是不可合成的,可以經由 co-simulation 的部份整合,驗證完成之後可以經由 ASIC FLOW 實作出電路。經由製造廠生產的 IC 亦可整合到APTIX 上,做最後面的驗證。

#### II. **子計畫二** 遠距混合信號 SOC 測試環境 建置--Remote Mixed Signal SoC Testing Infrastructure

遠距混合信號 SOC 測試環境,是將所有的測試儀表直接或間接的透過電腦與網路相連接,而代測電路則透過標準介面載板 Standard Interface Board 與測試儀表相聯結。在測試實務上是由一位技術員將混合信號 SOC 晶片放置於標準介面載板,並將所需要的測試儀表連接上載板。使用者可以集結在一個研討室內或在分別的研究室內,透過網路操控儀表,對待測電路作逕行測試。

透過此一遠距測試混合信號 SOC 測試環境,SOC 設計團隊可以在各自的研發環境直接參與測試。各個模組的設計人員可以不用親臨測試實驗室,在設計實驗室透過網路就可以逕行測試並即時更改測試項目及測試參數,並可以同步實行電路模擬與電路實測,以驗證對照測試的結果,作為設計更正之依據。此一環境亦可提供外界設計測試專家,透過網路參與晶片測試,提供測試與設計更正的意見。

#### 已建構之設備環境

- 邏輯分析系統 Logic Analysis System 400MHz

- 信號及任意波形產生器 Arbitrary Waveform Generator 80MSPS

- 頻譜分析儀 Spectrum Analyzer 3GHz

- 高頻示波器 High Frequency Oscilloscope 20GHz

- 時域反射量測儀 Time-Domain Reflectometer

- 電源供應器 Power Supply

- 脈衝產生器 Pulse Generator (1GHz, 20ps)

- 網路分析儀 Network/Spectrum Analyzer

3GHz

- 混合信號示波器 Oscilloscope 600MHz 4A+16D

#### 4. 結論與討論

Aptix 已使用於交通大學電子所研究群 Software Defined Radio OFDM 相關研究,使用 此系統作為發展環境,整合各子計畫之成果, 用以達到整個系統軟硬體整合,並使用於展現 其整體成果。

遠距混合信號 SOC 測試環境的基本建置已經完成,其環境可適用於大部分混合信號測試所需,已由相關研究人員使用此環境做研究發展,未來會有更多的相關人員使用此系統作為平台,經由網路的無遠弗屆來達到共享實驗室資源以達到有效使用儀器。