# 行政院國家科學委員會補助專題研究計畫期末報告

## 適用於印刷電路板製程之三度空間緊耦合器之研究

計畫類別：個別型計畫      整合型計畫

計畫編號：NSC 92 - 2213 - E - 009 - 080

執行期間：92 年 8 月 1 日至 93 年 7 月 31 日

計畫主持人：張志揚

本期中報告包括以下應繳交之附件：

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

執行單位：國立交通大學

中華民國 93 年 8 月 12 日

# 行政院國家科學委員會專題研究計畫期末報告

## 適用於印刷電路板製程之三度空間緊耦合器之研究

### Three dimensional tight coupler suitable for PCB process

計畫編號：NSC 92-2213-E-009-080

執行期限：92年8月1日至93年7月31日

主持人：張志揚 交通大學電信系

計畫參與人員：

陳慧婷，江俊賢，許志偉 交通大學電信系

#### 一、中文摘要

本計劃對印刷電路板上之緊耦合器(耦合量高於-3dB)提出一種以立體方式的解決方法。一般印刷電路板的介電常數均不高，例如常用的FR4電路板約4.47，其他的微波用印刷電路板大多低於4，使得傳統的耦合線式的緊耦合器(couple-line type coupler)在這麼低的基板介電常數限制下很難實現，而使用分支線式的耦合器(branch-line type coupler)頻寬過小且佔用過大的面積。本計劃乃針對這些限制提出改進方案。首先利用一片子基板垂直鋸於母印刷電路板上，調整子基板與母基板之佈局及在子基板旁放置介電材質補償基偶模相速即可設計出一寬頻且高性能的緊耦合器。其次利用子基板之佈局及印刷電路板常見的導電穿孔(plated through hole)可以改變輸出埠的物理位置以便利其他電路之應用。最後則利用這種緊耦合器進一步設計出三節超寬頻九十度混成器。

**關鍵詞：**印刷電路板緊耦合器，三度空間耦合器，九十度混成器

#### Abstract

In this project, we utilize a three dimensional method to implement a tight coupler (coupling greater than -3dB) on conventional printed circuit board (PCB). Usually PCBs are with low dielectric constant. For example, the conventional FR4 PCB is with dielectric constant of 4.47, and most of microwave PCBs are with dielectric constant lower than 4. A tight coupler uses parallel coupled-line method is difficult to implement because of low substrate dielectric. On the other hand, a tight couplers use branch-line design is too narrow band and consumes too large circuit board area. One of the main purposes of this program is to try to solve these problems. First, a small substrate with spectacular layout is soldered perpendicularly on the corresponding layout on the main substrate. Applying dielectric materials to compensate the even- and odd-mode phase velocity's difference, a high performance and broadband coupler could be

achieved. Second, utilize plated through hole on the small substrate (it is common in PCB process) may change physical position of the output ports so that they can fit the layout of other circuits. Last, a 3-section ultra-broadband 90° hybrid can be developed using the proposed structure.

**Keywords:** PCB tight coupler, three-dimensional coupler, 90° hybrid.

#### 二、緣由與目的

緊耦合器(特別是-3dB 耦合器)常常被運用在無線通訊系統中平衡式IQ混波器、平衡式放大器、雷達追蹤系統等等的設計。傳統單節耦合線式的耦合器[1][2]受限於蝕刻之精度及印刷電路板的介電常數常常不高，其耦合量僅適用於-10至-30dB，此一耦合器的耦合埠(Coupling port)與貫穿埠(through port)的分量振幅不一致，不適用於平衡式電路設計上。

雖然分支線式的耦合器[3]可以在一般印刷電路板上實現出-3dB 之緊耦合器但是頻寬太窄與所佔面積太大常常限制其運用範圍。例如：運用分支線式的耦合器所設計出的平衡式混波器，其可使用之頻寬即受限於分支線式的耦合器本身之頻寬。而且分支線式的耦合器其所佔之面積也遠大於傳統單節耦合線式的耦合器常常造成使用上的限制。另外；分支線式的耦合器的耦合埠與貫穿埠必定是在同側的位置，有時不利於電路佈局。

另一個常常使用的緊耦合器為籃吉最早提出籃吉耦合器(Lange Coupler)[4]，藍吉在高介電基材上運用指交式耦合線(inter-digital coupling line)及在特定位址利用跳線(bound wire)連接即可實現寬頻的-3dB 耦合器但是在低介電基材上則仍然受限於蝕刻之精度而無法實現出緊耦合器，而且在跳線連接時常常因跳線之位置及長度而影響其耦合器特性，使得在製作過程需要數次的微調方能達到設計時所預期的特性，如此更增加製作上的困難。

運用垂直裝置平板電路結構(Vertically Installed Planar circuit structure)的耦合器，簡稱VIP 耦合器[5]，可於一般低介電基材上

運用傳統印刷電路板的製程製作出寬頻-3dB 耦合器，原創者 YOSHIHIRO KONISHI 提出運用不同介電係數的子基板垂直裝置在母基板上可達成寬頻-3dB 耦合器之設計，但藉由改變子、母基板的介電係數有時卻有製作上的困難。Chuandong Zhao [6] 進一步使用單一子、母基材且藉由改變子、母基材線路來補償奇、偶模相速度差，提高耦合器的指向性(Directivity)；但是其頻寬卻因此縮小。

VIP 結構之耦合器具有體積小、便於製作、易於達成緊耦合與 90 度相位差之特性，但是其嚴重的奇、偶模相速度差常常破壞其指向性與反射係數的特性，若用窄頻的相位補償方式雖能改善指向性與反射係數特性，但其頻寬將會縮小。因此本計劃將利用在子基板旁放置介電材質的方式來使奇、偶模相速在所有頻率皆能相等，提高耦合器之指向性與反射係數特性。另外經由導電穿孔來改變耦合埠於貫穿埠的位置以便於平衡式電路設計時電路的佈線。

### 三、理論

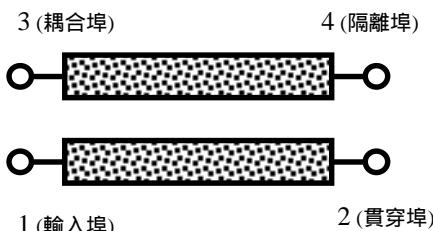

對稱性結構的耦合器(圖一)常常利用奇、偶模來分析其特性，在考慮均質介質傳輸狀態下(奇、偶模相速度一樣)整體四埠網路之 S 參數與奇、偶模態之 S 參數可表示成

$$S_{12} = S_{21} = S_{34} = S_{43} = S_{21e} = S_{21o} = \frac{\sqrt{1-k^2}}{\sqrt{1-k^2} \cos \theta + j \sin \theta}$$

$$S_{13} = S_{31} = S_{24} = S_{42} = S_{11e} = -S_{11o} = \frac{jk \sin \theta}{\sqrt{1-k^2} \cos \theta + j \sin \theta}$$

其中  $K = \frac{Z_{0e} - Z_{0o}}{Z_{0e} + Z_{0o}}$  表示耦合器之耦合係數，至於

$Z_{0e}$ 、 $Z_{0o}$  分別表示奇、偶模態的特性阻抗，在滿足阻抗匹配(反射係數等於零)的條件下， $Z_{0e}$ 、 $Z_{0o}$  必須滿足  $Z_0 = \sqrt{Z_{0e} Z_{0o}}$ ， $Z_0$  則是埠阻抗。

在此定義幾項耦合器的特性

$$\text{耦合量 } C \quad C(dB) = -20 \log_{10} K.$$

$$\text{隔離度 } I \quad I(dB) = -20 \log_{10} S_{41}$$

$$\text{指向性 } D \quad D(dB) = 20 \log_{10} \left( \frac{S_{31}}{S_{41}} \right)$$

圖一：對稱性耦合器之結構

在 VIP 的結構上欲實現一緊耦合器(-3dB)需要調整子基板的結構使得  $Z_{0o} = 20.7\Omega$ ，再調整子基板對母基板的等效電容使得  $Z_{0e} = 120.5\Omega$ 。但是在非均質介質傳輸時，因為奇、偶模相速度的不同導致耦合器無法實現良好的反射係數與高指向性的

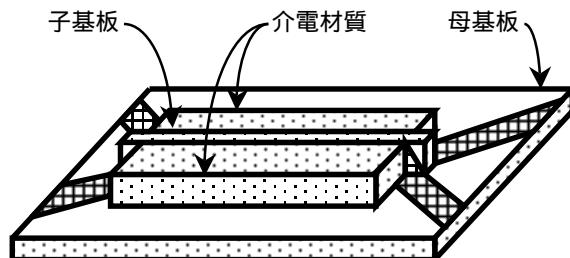

特性。由散佈在 VIP 結構的截面電場分布來看，奇模電場皆集中在子基板中間而偶模場則散佈在子基板兩旁空氣中，因此奇模波速將比偶模慢。解決的方法為在直立的子基板旁放置介電材質(如圖二所示)來降低偶模的波速則可實現高性能寬頻的3dB 緊耦合器。

圖二：三度空間緊耦合器電路結構

### 四、設計流程

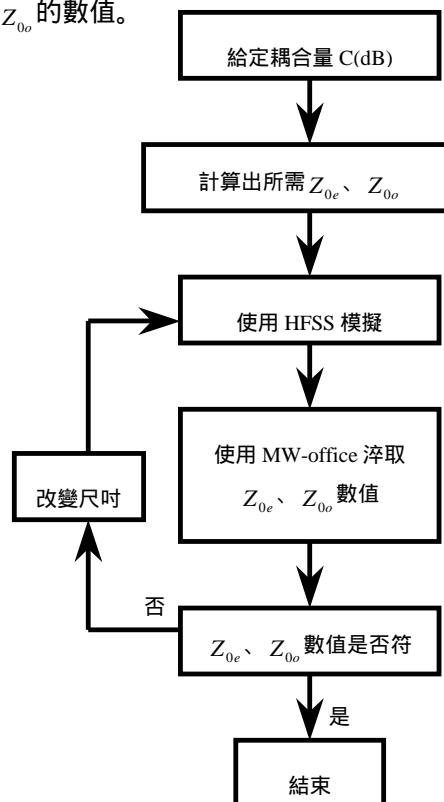

在設計三度空間之耦合器時，本計劃利用三度空間電磁模擬軟體-HFSS 來做模擬，再將所得結果匯出至電路模擬軟-MW-office 來淬取  $Z_{0e}$ 、 $Z_{0o}$  的數值。若淬取出之  $Z_{0e}$ 、 $Z_{0o}$  數值未能符合期望則依照：(1)增加子基板的面積或減小子基板版厚將降低  $Z_{0o}$  的數值。(2)提高子基板與母基板之間的距離即可增加  $Z_{0e}$  的數值。調整結構尺寸來達到所須之  $Z_{0e}$ 、 $Z_{0o}$  的數值。

圖三：耦合器之設計流程圖

### 五、結果與討論

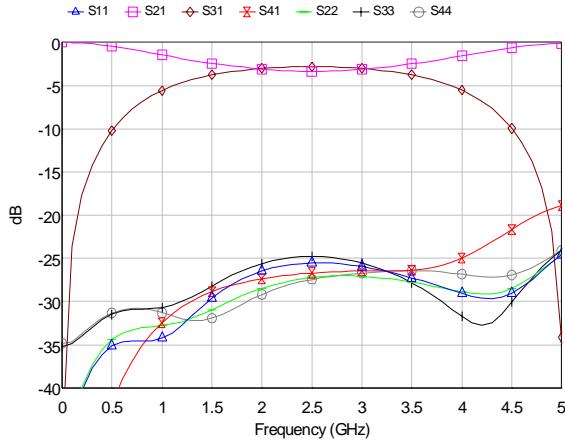

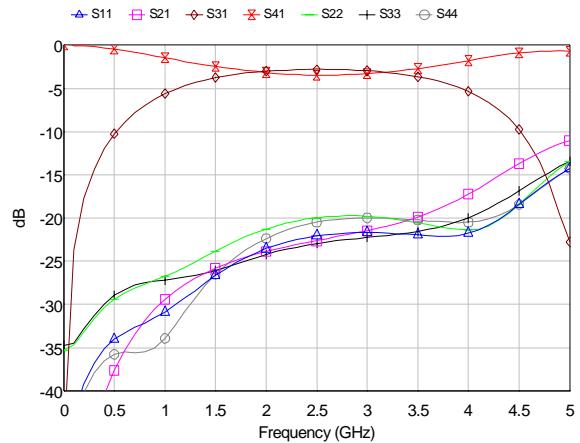

利用三度空間電磁模擬軟體 - HFSS 所模擬的三度空間緊耦合器散射參數特性如圖三所示。中

心頻率設計在 2.5GHz，耦合量為-3dB，其結果顯示反射係數、隔離度到 4.5GHz 皆有-20dB 的表現。圖五所呈現的是由三度空間所製作完成的耦合器外觀圖，而量測結果則呈現在圖六。雖然在高於 3.5GHz 其反射係數與隔離度以大於-15dB，但是中心頻率、耦合埠與貫穿埠的量測結果與模擬相符。

圖四：單一階三度空間緊耦合器的模擬結果

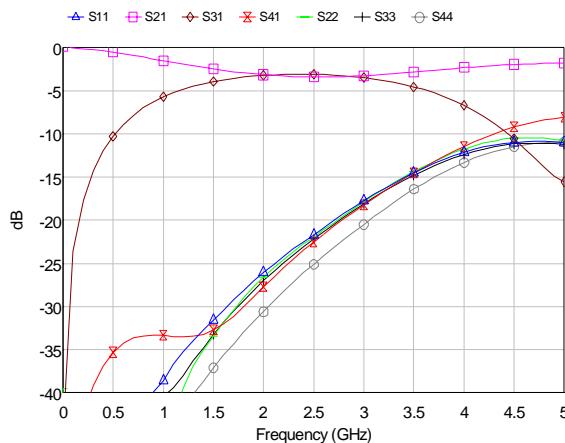

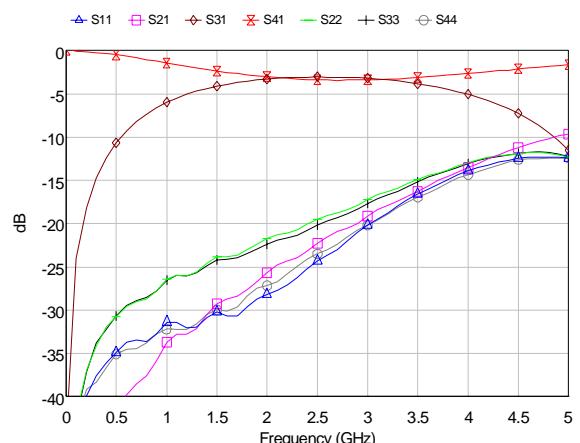

(即圖一中 2 與 4 埠互換)其模擬結果(如圖七所示)與原來相差不遠，只是反射係數與隔離度因為不連續效應而降低，但是整體上能維持-20dB 得性能。而實際量測的結果(如圖八所示)與未利用導電穿孔來改變耦合埠與貫穿埠的位置的結果(圖六)相當一致，其整體反射係數與隔離度以大於 -10~-15dB，而且中心頻率與耦合量皆與模擬符合。

圖七：耦合埠與隔離埠對調的模擬結果

圖六：單一階三度空間緊耦合器量測結果

圖八：耦合埠與隔離埠對調的量測結果

圖五：實際製作的濾波器外觀圖

利用導電穿孔來改變耦合埠與貫穿埠的位置

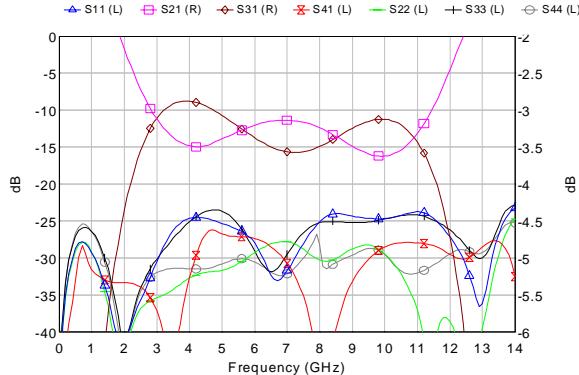

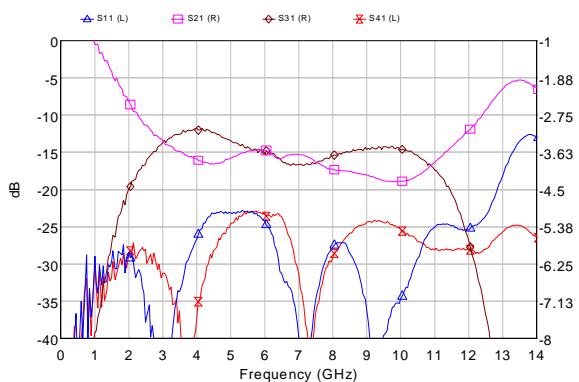

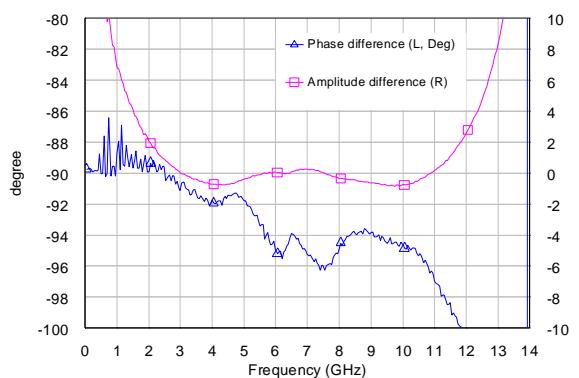

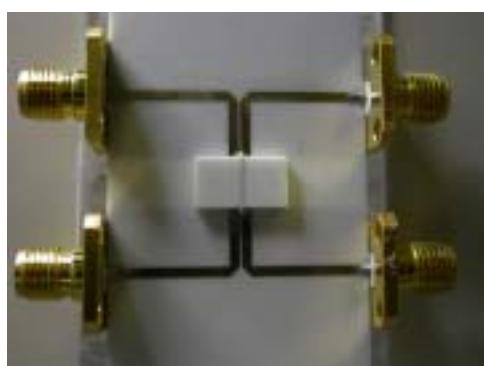

多階串接式耦合器結構可以有效增加耦合器頻寬，根據 Cristal E. G 與 L. Young[7]所求得的表格，如果想設計頻寬為 3-11GHz，整體耦合量為-3dB，漣波為 +/-0.2dB 的三階耦合器。其設計所需的參數為：第一階耦合器為  $Z_{0e} = 60.39\Omega$   $Z_{0o} = 41.40\Omega$ ，第二階耦合器為  $Z_{0e} = 170.62\Omega$   $Z_{0o} = 14.65\Omega$ ，第一階耦合器運用傳統耦合線式的耦合器即可達到所要的奇、偶模阻值、第二階部分則需運用本計劃所提出之三度空間緊耦合結構方可達到所要的奇、偶模阻值。所得模擬結果顯示在圖九中，其反射係數與隔離度在 0-14GHz 將近有 -25dB 的表現。圖十為量測的數值其結果與模擬非常相近，其耦合埠與貫穿埠大小相差再 +/-0.5dB 左右，而相位差則維持在 90 度誤差 10 度。實體圖則顯現在圖十二。

## 六、計畫成果自評

圖九：三階串接式 3dB 耦合器的模擬結果

圖十：三階串接式 3dB 耦合器的量測結果

圖十一：三階串接式 3dB 耦合器的耦合埠與貫穿埠的大小禹相位差。

圖十二：三階串接式 3dB 耦合器實體圖

本計劃目前已經藉由實驗驗證所提出的方法可在一般印刷電路板上實現三度空間之緊耦合器，並且藉由在直立的子基板旁放置介電材料來使得極為寬頻的範圍內獲得不錯的奇、偶模相速度補償，進而得到良好的隔絕度或指向性。

透過導電穿孔來改變耦合埠於貫穿埠的位置，雖然會因為結構的不連續而降低耦合器的性能，但是本計劃中已成功透過導電穿孔來改變耦合埠於貫穿埠的位置而且維持原來的耦合器特性。

在超寬頻的應用上（如 UWB 之應用），多階  $90^\circ$  混成器為一理想之結構，本研究所提出的方法更能適用於多階結構中，中間的緊耦合需求，也因為寬頻的奇、偶模相速度補償方式使得整體結果能具有寬頻與高性能的特性。

## 七、參考文獻

- [1] David Pozar, *Microwave Engineering*, 2'nd Edition, John Wiley & Sons, N. Y. 1998

- [2] J. K. Shimizu and E. M. T. Jones., “Coupled-Transmission-Line Directional Couplers”, *IEEE Transactions on Microwave Theory & Techniques*, vol. MTT-6, No.4, October 1958

- [3] J.W. Gipprich, “A New Class of Branch-Line Directional Couplers” IEEE MTT-S Digest 1993.

- [4] Lange J. “Interdigitated strip-line quadrature hybrid.” 1969 *G-MTT International Microwave Symposium*, Institute of Electrical and Electronics Engineers, Inc. 1969, pp.10-13.

- [5] Y. K. Konishi, I. Awai, Y. Fukuoka, and M. Nakajima, “A directional coupler of vertically installed planar circuit structure,” *IEEE Transactions on Microwave Theory & Techniques*, vol. 36, no. 6, pp. 1057-1063, June 1988.

- [6] Chuandong Zhao and Ikuro Awai, “ Application of the Finite Difference Techniques to the Compensated VIP 3 dB Directional Coupler,” *IEEE Transactions on Microwave Theory & Techniques*, vol. 44, no. 11, pp.2045-2052, Nov. 1996.

- [7] E.G. Cristal “ Theory and Tables of Optimum Symmetrical TEM-Mode Coupled Transmission Line Directional Couplers ” *IEEE Transactions on Microwave Theory & Techniques*, vol.MTT-13, no.5, September 196