# Investigation of High-Frequency Noise Characteristics in Tensile-Strained nMOSFETs

Sheng-Chun Wang, Pin Su, *Member, IEEE*, Kun-Ming Chen, Bo-Yuan Chen, Guo-Wei Huang, *Member, IEEE*, Cheng-Chou Hung, Sheng-Yi Huang, Cheng-Wen Fan, Chih-Yuh Tzeng, and Sam Chou

Abstract—For the first time, the high-frequency noise behavior of tensile-strained n-channel metal—oxide—semiconductor field-effect transistors, including their temperature dependency, is experimentally examined. Our experimental results show that with similar saturation voltages, the strained device is found to have larger channel noise than the control device at the same bias point. For given direct-current power consumption, however, due to enhanced transconductance, the strained device has better small-signal behaviors (higher  $f_t$  and  $f_{\rm max}$ ) and noise characteristics (smaller  ${\rm NF}_{\rm min}$  and  $R_n$ ) than the control device.

Index Terms—Metal-oxide-semiconductor field-effect transistors (MOSFETs), noise, radio frequency (RF), temperature, tensile strained, van der Ziel model.

#### I. INTRODUCTION

S THE GATE length of complementary metal—oxide—semiconductor (CMOS) transistors is down-scaled to a decananometer regime, device scaling is becoming extremely difficult due to many physical and technological problems [1]. Strain engineering technology is one way to maintain scaling trends of CMOS devices. It is well known that strained-channel MOS field-effect transistors (MOSFETs) have larger carrier mobility and drain current than unstrained counterparts [2]–[6]. It is expected that improved direct-current (dc) performances can also enhance radio-frequency (RF) performances.

Recently, CMOS technologies with incorporation of hightensile contact etch stop layer (CESL) stressors have been demonstrated for RF applications, and a very high cutoff frequency  $f_t$  has been shown [7], [8]. There have been many studies on high-frequency noise characterization and modeling of conventional MOSFET devices [9]–[17]. However, the effects

Manuscript received August 3, 2010; revised October 8, 2010 and November 5, 2010; accepted December 15, 2010. Date of current version February 24, 2011. This work was supported in part by the National Science Council of Taiwan. The review of this paper was arranged by Editor 7. Celik-Butler.

S.-C. Wang is with the National Nano Device Laboratories, Hsinchu 300, Taiwan and also with Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: scwang@ndl.narl.org.tw).

P. Su is with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan (e-mail: pinsu@faculty.nctu.edu.tw).

K.-M. Chen and B.-Y. Chen are with the National Nano Device Laboratories, Hsinchu 300, Taiwan.

G.-W. Huang is with the National Nano Device Laboratories, Hsinchu 300, Taiwan, and also with the Department of Electronics Engineering and Institute of Electronics, National Chiao Tung University, Hsinchu 300, Taiwan.

C.-C. Hung, S.-Y. Huang, C.-W. Fan, C.-Y. Tzeng, and S. Chou are with the United Microelectronics Corporation, Hsinchu 300, Taiwan.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2010.2104153

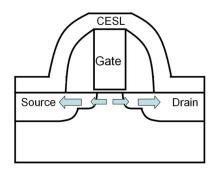

Fig. 1. Tensile stress in the channel of a high-strained nMOSFET.

of highly tensile stressors on high-frequency noise characteristics have rarely been known. In this brief, high-frequency noise characteristics of tensile-strained n-channel MOSFETs (nMOSFETs), including their temperature dependence, will be investigated and analyzed for the first time.

# II. DEVICES AND MEASUREMENTS

Multifinger CMOS transistors were fabricated using a 65-nm generation technology with a  $\langle 100 \rangle$ -channel orientation on a (100) wafer. For enhancing the electron mobility of the channel, an 850-Å-thick  $\mathrm{SiN}_x$  CESL was grown as a high-tensile stressing layer. As indicated in Fig. 1, this eventually applied a lateral tensile stress of 1.5 GPa in the device's channel. In addition, for the control device, a conventional low tensile strength ( $\mathrm{SiN}_x = 360~\text{Å}$ ) CESL was used.

The gate length of the test devices is 60 nm, and the total gate width of the test devices is 128  $\mu$ m (4  $\mu$ m by 32 gate fingers). The noise parameters of the MOSFET under different temperatures were measured using Auriga noise and scattering parameter measurement system. The dummy OPEN and SHORT deembedding technique was used to eliminate parasitic contributions from probing pads and metal interconnections [12]. Finally, the intrinsic channel noise current was extracted following the approach presented in [13].

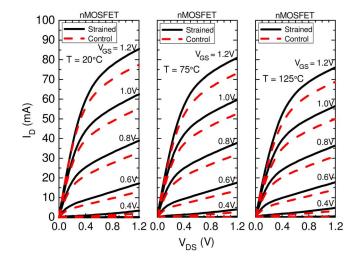

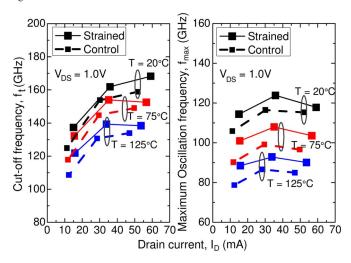

Fig. 2 compares the dc characteristics of the tensile-strained and control devices. The strained device presents larger drain current than the control one for each ambient temperature because of its enhanced carrier mobility, which can also help to boost the cutoff frequency  $f_t$  and maximum oscillation frequency  $f_{\rm max}$ , as shown in Fig. 3.

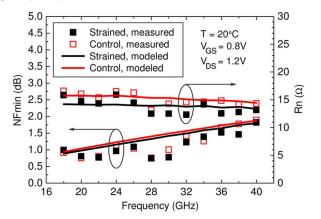

Fig. 4 compares the noise measurement results in terms of the minimum noise figure  $NF_{\min}$  and equivalent thermal noise resistance  $R_n$  for the strained and control devices. The strained device shows a better high-frequency noise performance than the control one. The good match between measured and

Fig. 2. I-V characteristics for the strained and control devices.

Fig. 3.  $f_t$  and  $f_{max}$  versus drain current for the strained and control devices.

Fig. 4. Measured and modeled results for  $NF_{\min}$  and  $R_n$ .

modeled results based on the equivalent circuit in [14] also indicates the validity of the extracted noise parameters shown in this brief.

## III. CHANNEL NOISE CHARACTERIZATION

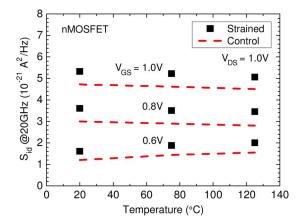

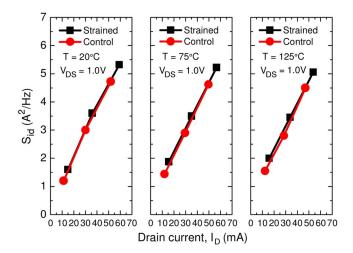

The extracted power spectral density of channel noise  $S_{\rm id}$  is shown in Fig. 5. It shows that the strained device has larger  $S_{\rm id}$  than the control one for a given bias point. This phenomenon

Fig. 5. Power spectrum density of channel noise  $S_{\rm id}$  versus temperature for the strained and control devices.

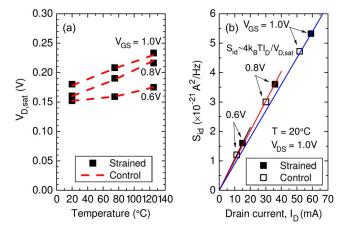

Fig. 6. (a) Similar drain saturation voltage  $V_{D,\,\mathrm{sat}}$  for the strained and control devices at each temperature, and (b) the good match between measured  $S_{\mathrm{id}}$  and the Asgaran model [see (1)].

can be explained by the following model equation developed by Asgaran *et al.* [15]:

$$S_{\rm id} = 4k_BTI_D\left(\frac{1}{V_{D,\,\rm sat}} + \frac{\alpha^2V_{D,\,\rm sat}}{3V_{CT}^2}\right) \approx \frac{4k_BTI_D}{V_{D,\,\rm sat}}$$

(1)

where  $k_B \approx 1.38 \times 10^{-23}$  J/K is the Boltzmann's constant, T is the ambient temperature in Kelvin,  $V_{D,\,\mathrm{sat}}$  is the drain saturation voltage,  $V_{\mathrm{GT}}$  is the gate overdrive voltage, and  $\alpha$  is the bulk charge coefficient.

This model indicates that in the saturation region, channel length modulation is the main mechanism responsible for excess channel noise. Since the impact of tensile strain on  $V_{D,\,\mathrm{sat}}$  is negligible, as shown in Fig. 6(a), the larger drain current  $I_D$  present in the strained device is responsible for larger  $S_{\mathrm{id}}$ . The validity of Asgaran model has been verified in our previous study [14] and also reconfirmed in Fig. 6(b).

On the other hand, the well-known van der Ziel model [11], which uses the white noise gamma factor to characterize  $S_{\rm id}$ , can be written as

$$S_{\rm id} = \gamma 4k_B T g_{d0} \tag{2}$$

where  $g_{d0}$  is the channel conductance at zero drain bias, and  $\gamma$  is the noise factor. For long-channel devices,  $\gamma$  would approach

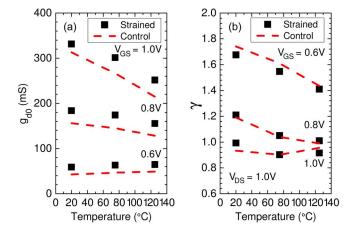

Fig. 7. (a) Channel conductance at zero drain bias  $g_{d0}$  and (b) noise factor  $\gamma$  versus temperature.

2/3 in the saturation region. For short-channel devices, however, it would be greater than 2/3, and can be considered as a figure of merit used to assess excess channel noise.

Fig. 7(a) shows the extracted  $g_{d0}$  value versus temperature. The larger  $g_{d0}$  value for the strained device results from its higher mobility. In addition, two different temperature dependence values can be observed. At lower  $V_{GS}$ , the lowered threshold voltage at higher temperature contributes to the positive temperature coefficient of  $g_{d0}$ . At higher  $V_{GS}$ , however, degraded carrier mobility overwhelms the threshold voltage lowering effect at higher temperature, causing  $g_{d0}$  to decrease with increasing temperature.

Fig. 7(b) shows that both the strained and control devices have nearly the same noise factor  $\gamma$ , which means they suffer approximately the same short-channel effect on high-frequency noise performance. In addition, since both  $S_{\rm id}$  and  $I_D$  (or  $g_{d0}$ ) scale with mobility, the results of similar  $\gamma$  for both the strained and control devices can be expected, as indicated in (1).

It is worth noting that for the 65-nm technology node,  $S_{\rm id}$  tends to decrease with increasing temperature at high  $V_{GS}$  (see Fig. 5). This is consistent with the result presented in [16] for the medium-long-channel device ( $L=0.36~\mu{\rm m}$ ) for the severe decrease in  $g_{d0}$  counterbalancing the increase in temperature [see (2)]. However, the temperature dependence is not so obvious for the 65-nm device in this brief.

#### IV. NOISE PARAMETER CHARACTERIZATION

The minimum noise figure  $NF_{min}$  and equivalent thermal noise resistance  $R_n$  can be approximately expressed by the following equations [14], [17]:

$$NF_{\min} \approx 1 + \frac{2}{g_m^2} \sqrt{(R_s + R_g) \frac{S_{id}}{4kT_0}}$$

$$\times \left\{ \omega C_{gg} g_m + \omega^2 C_{gg}^2 R_g \sqrt{\frac{S_{id}}{4kT_0}} \right\}$$

(3)

$$R_n \approx \frac{T}{T_0} (R_g + R_s) + \frac{S_{\rm id}}{4k_B T_0 g_m^2}$$

(4)

where  $T_0=290~{\rm K}$  is the reference temperature, and  $C_{gg}=C_{gs}+C_{gd}$  is the gate capacitance. Note that since the induced

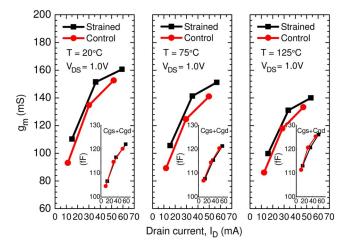

Fig. 8. Transconductance  $g_m$  versus drain current for the strained and control devices. The insets show the gate capacitance versus drain current.

Fig. 9.  $S_{\rm id}$  versus drain current for the strained and control devices.

gate noise current has been found to be insignificant at a 65-nm node even in the millimeter-wave application [14], it has been neglected in the above derivation.

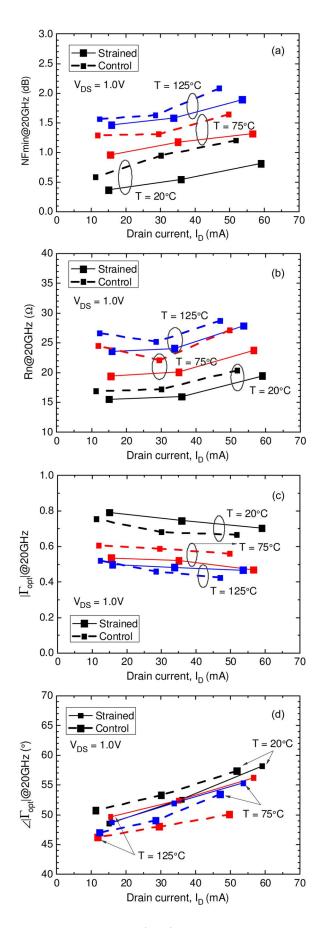

For given dc power consumption, compared with the control device, since the strained device exhibits larger transconductance but comparable  $S_{\rm id}$ , as shown in Figs. 8 and 9, respectively, (3) and (4) imply that the strained device would have smaller NF  $_{\rm min}$  and  $R_n$ , as shown in Fig. 10(a) and (b), respectively. In addition, the magnitude and phase of the optimum source reflection coefficient ( $|\Gamma_{\rm opt}|$  and  $\angle\Gamma_{\rm opt}$ ) versus drain current are respectively depicted in Fig. 10(c) and (d) for the reader's reference.

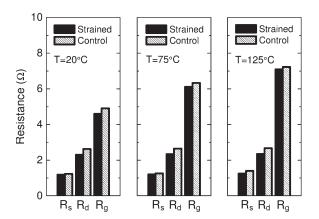

Note that the similar access resistance and gate capacitance values shown in Fig. 11 and the insets in Fig. 8, respectively, indicate the little impact of tensile strain on them for these two different fabrication processes. Therefore, they cannot be attributed to the discrepancy of the high-frequency small-signal and noise performance between these two devices.

## V. CONCLUSION

In this brief, we have investigated the high-frequency noise behavior of the tensile-strained nMOSFET. With nearly the same saturation voltages and noise factors, the strained device

Fig. 10. (a) NF<sub>min</sub>, (b)  $R_n$ , (c)  $|\Gamma_{\rm opt}|$ , and (d)  $\angle\Gamma_{\rm opt}$  versus drain current for the strained and control devices.

Fig. 11. Access resistance values for the strained and control devices.  $R_s$ ,  $R_d$ , and  $R_g$  are access resistance values associated with the source, drain, and gate terminals, respectively.

presents larger  $S_{\rm id}$  than the control device due to its enhanced mobility for a given bias point. In addition, both the strained and control devices have the same temperature dependence of  $S_{\rm id}$ . Finally, for a given dc power consumption, due to enhanced transconductance, our experimental results show that the strained device has better NF<sub>min</sub> and  $R_n$  than the control device.

#### ACKNOWLEDGMENT

The authors would like to thank United Microelectronics Corporation for providing the devices used in this brief.

#### REFERENCES

- [1] D. J. Frank, R. H. Dennard, E. Nowak, P. M. Solomon, Y. Taur, and H.-S. P. Wong, "Device scaling limits of Si MOSFETs and their application dependencies," *Proc. IEEE*, vol. 89, no. 3, pp. 259–288, Mar. 2001.

- [2] S. E. Thompson, M. Armstrong, C. Auth, S. Cea, R. Chau, G. Glass, T. Hoffman, J. Klaus, Z. Ma, B. Mcintyre, A. Murthy, B. Obradovic, L. Shifren, S. Sivakumar, S. Tyagi, T. Ghani, K. Mistry, M. Bohr, and Y. El-Mansy, "A logic nanotechnology featuring strained-silicon," *IEEE Electron Device Lett.*, vol. 25, no. 4, pp. 191–193, Apr. 2004.

- [3] K. Rim, S. Koester, M. Hargrove, J. Chu, P. M. Mooney, J. Ott, T. Kanarsky, P. Ronsheim, M. Ieong, A. Grill, and H.-S. P. Wong, "Strained Si NMOSFETs for high performance CMOS technology," in VLSI Symp. Tech. Dig., 2001, pp. 59–60.

- [4] L. Washington, F. Nouri, S. Thirupapuliyur, G. Eneman, P. Verheyen, V. Moroz, L. Smith, X. Xu, M. Kawaguchi, T. Huang, K. Ahmed, M. Balseanu, L.-Q. Xia, M. Shen, Y. Kim, R. Rooyackers, K. De Meyer, and R. Schreutelkamp, "pMOSFET with 200% mobility enhancement induced by multiple stressors," *IEEE Electron Device Lett.*, vol. 27, no. 6, pp. 511–513, Jun. 2006.

- [5] S. Pidin, T. Mori, K. Inoue, S. Fukuta, N. Itoh, E. Mutoh, K. Ohkoshi, R. Nakamura, K. Kobayashi, K. Kawamura, T. Saiki, S. Fukuyama, S. Satoh, M. Kase, and K. Hashimoto, "A novel strain enhanced CMOS architecture using selectively deposited high tensile and high compressive silicon nitride films," in *IEDM Tech. Dig.*, Dec. 2004, pp. 213–216.

- [6] C. T. Lin, Y. K. Fang, W. K. Yeh, C. M. Lai, C. H. Hsu, L. W. Cheng, and G. H. Ma, "Impacts of notched-gate structure on contact etch stop layer (CESL) stressed 90-nm nMOSFET," *IEEE Electron Device Lett.*, vol. 28, no. 5, pp. 376–378, May 2007.

- [7] I. Post, M. Akbar, G. Curello, S. Gannavaram, W. Hafez, U. Jalan, K. Komeyli, J. Lin, N. Lindert, J. Park, J. Rizk, G. Sacks, C. Tsai, D. Yeh, P. Bai, and C.-H. Jan, "A 65 nm CMOS SOC technology featuring strained silicon transistors for RF applications," in *IEDM Tech. Dig.*, Dec. 2006, pp. 1–3.

- [8] D. V. Singh, K. A. Jenkins, J. Sleight, Z. Ren, M. Ieong, and W. Haensch, "Strained ultrahigh performance fully depleted nMOSFETs with  $f_t$  of 330 GHz and sub-30-nm gate lengths," *IEEE Electron Device Lett.*, vol. 27, no. 3, pp. 191–193, Mar. 2006.

- [9] M. J. Deen, C. H. Chen, S. Asgaran, G. A. Rezvani, J. Tao, and Y. Kiyota, "High-frequency noise of modern MOSFETs: Compact modeling and measurement issues," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2062–2081, Sep. 2006.

- no. 9, pp. 2062–2081, Sep. 2006.

[10] J. Gao and A. Werthof, "Scalable small signal and noise modeling for deep submicron MOSFETs," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 4, pp. 737–744, Apr. 2009.

- [11] A. F. Tong, W. M. Lim, K. S. Yeo, C. B. Sia, and W. C. Zhou, "A scalable RFCMOS noise model," *IEEE Trans. Microw. Theory Tech.*, vol. 57, no. 5, pp. 1009–1019, May 2009.

- [12] G. Knoblinger, "RF-noise of deep-submicron MOSFETs: Extraction and modeling," in *Proc. Eur. Solid-State Device Res. Conf.*, 2001, pp. 331–334.

- [13] C.-H. Chen, M. J. Deen, Y. Cheng, and M. Matloubian, "Extraction of the induced gate noise, channel noise, and their correlation in submicron MOSFETs from RF noise measurements," *IEEE Trans. Electron Devices*, vol. 48, no. 12, pp. 2884–2892, Dec. 2001.

- [14] S.-C. Wang, P. Su, K.-M. Chen, K.-H. Liao, B.-Y. Chen, S.-Y. Huang, C.-C. Hung, and G.-W. Huang, "Comprehensive noise characterization and modeling for 65-nm MOSFETs for millimeter-wave applications," *IEEE Trans. Microw. Theory Tech.*, vol. 58, no. 4, pp. 740–746, Apr. 2010.

- [15] S. Asgaran, M. J. Deen, and C.-H. Chen, "Analytical modeling of MOSFETs channel noise and noise parameters," *IEEE Trans. Electron Devices*, vol. 51, no. 12, pp. 2109–2114, Dec. 2004.

- [16] S.-C. Wang, P. Su, K.-M. Chen, C.-T. Lin, V. Liang, and G.-W. Huang, "Temperature dependence of high frequency noise behaviors for RF MOSFETs," *IEEE Microw. Wireless Compon. Lett.*, vol. 18, no. 8, pp. 530–532, Aug. 2008.

- [17] J. Jeon, I. Song, I. M. Kang, Y. Yun, B.-G. Park, J. D. Lee, and H. Shin, "A new noise parameter model of short-channel MOSFETs," in *Proc. IEEE Radio Freq. Integr. Circuits Symp.*, Jun. 2007, pp. 639–642.

**Kun-Ming Chen** received the M.S. and Ph.D. degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 1996 and 2000, respectively.

In 2000, he joined the National Nano Device Laboratories, Hsinchu, as an Associate Researcher and, in 2007, became a Researcher. He was engaged in research on microwave device process and characterization.

**Bo-Yuan** Chen was born in Miaoli, Taiwan, in 1980. He received the M.S. degree in materials science and engineering from the National Dong Hwa University, Hualien, Taiwan, in 2006.

In 2006, he joined the National Nano Device Laboratories, Hsinchu, Taiwan, as an Assistant Researcher. He was engaged in research on III–V compound semiconductors and radio-frequency device characterization.

semiconductor devices

Sheng-Chun Wang received the B.S. and M.S. degrees in electrical engineering from the National Cheng Kung University, Tainan, Taiwan, in 1999 and 2001, respectively. He is currently working toward the Ph.D. degree with the National Chiao Tung University, Hsinchu, Taiwan.

In 2001, he joined the National Nano Device Laboratories, Hsinchu, as an Assistant Researcher. His current research interests include small-signal and noise characterization and modeling for radio-frequency complementary metal-oxide-

**Guo-Wei Huang** (S'94-M'97) was born in Taipei, Taiwan, in 1969. He received the B.S. and Ph.D. degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, in 1991 and 1997, respectively.

In 1997, he joined the National Nano Device Laboratories (NDL), Hsinchu, where he is currently a Researcher and the Manager of High-Frequency Technology Division. Since August 2008, he has been an Adjunct Associate Professor with the Department of Electronics Engineering, National Chiao

Tung University. His current research interests include characterization and modeling techniques of high-frequency devices and characterization and verification of radio-frequency/monolithic microwave integrated circuit.

**Pin Su** (S'98–M'02) received the B.S. and M.S. degrees in electronics engineering from the National Chiao Tung University, Hsinchu, Taiwan, and the Ph.D. degree from the University of California at Berkeley, Berkeley.

From 1997 to 2003, he conducted his doctoral and postdoctoral research in silicon-on-insulator (SOI) devices with the University of California at Berkeley. He was also one of the major contributors to the unified Berkeley short-channel insulated-gate field-effect transistor (FET) SOI model, the first indus-

trial standard SOI metal—oxide—semiconductor (MOS) FET model for circuit design. Since August 2003, he has been with the Department of Electronics Engineering, National Chiao Tung University, where he is currently an Associate Professor. He has authored or coauthored over 100 research papers in refereed journals and international conference proceedings in these areas. His research interests include silicon-based nanoelectronics, modeling and design for exploratory complementary MOS (CMOS) devices, and device/circuit interaction and cooptimization in nano-CMOS.

**Cheng-Chou Hung** received the B.S. and M.S. degrees in electrical engineering from the National Cheng Kung University, Tainan, Taiwan, in 1996 and 1999, respectively.

Currently, he is with the Advanced Technology Department Division, United Microelectronics Corporation, Hsinchu, Taiwan, as a radio-frequency (RF) Device Development Manager. His current research interests include RF complementary metal-oxide-semiconductor technology characterization/delivery, including active and passive devices.

Sheng-Yi Huang received the B.S. degree in electrical engineering from the National Cheng Kung University, Tainan, Taiwan, in 2001 and the M.S. and Ph.D. degrees in electronics engineering from the National Chiao Tung University Hsinchu, Taiwan, in 2003 and 2007, respectively.

Since 2003, he has been with the Advanced Technology Development Division, United Microelectronics Corporation, Hsinchu, working on radiofrequency (RF)-related technologies. His current research interests include advanced mixed-mode and

RF complementary metal—oxide—semiconductor design, including device modeling, noise characterization, power behavior, and reliability studies.

**Cheng-Wen Fan** was born in Chiayi County, Taiwan, in 1972. He received the M.S. degree in material science and engineering (major field is on the plasmaenhanced chemical vapor deposition process) from the National Chiao Tung University in 1995.

Since 1998, he has been with the semiconductor manufacturing industry, where his first job was as an Etch Module Process Engineer with the Powerchip Technology Corporation. Afterward, he joined the United Microelectronics Corporation (UMC), working on dynamic random-access memory, logic, and analog and radio-frequency complementary metal-oxide-semiconductor. Most of his time in the UMC was in the MM&RF department and research and development with handling customer's advance-technology products.

**Chih-Yuh Tzeng** was born in Chenghua, Taiwan, in 1971. He received the B.S. and M.S. degrees in physics and electronics engineering from the National Cheng Kung University, Tainan, Taiwan, in 1993 and 1998, respectively.

From 1998 to 2000, he was with Winbond Electronics Corporation, Hsinchu, Taiwan, where he was engaged in deep-trench dynamic random-access memory (RAM) process development integration and manufacture. Then, he joined the United Microelectronics Corporation (UMC), Shin Chu, Taiwan,

working in the areas of logic, Flash, field-programmable gate array, static RAM, analog and radio-frequency complementary metal-oxide-semiconductor (RF CMOS) process integration and manufacture. In 2002, he was a Program Manager with the Research and Development department, UMC, where he was in charged of 130-nm-and-beyond technology analog and RF CMOS process, and device development and characterization. Since 2006, he has been the Department manager of the Research and Development department, UMC, responsible for advance analog and RF CMOS technology development.

**Sam Chou** was born in Taiwan in 1968. He received the B.S. degree in electronic physics from the National Chiao Tung University, Hsinchu, Taiwan, in 1990, and the M.S. degree in electrical engineering from the National Tsing Hua University, Hsinchu, in 1992.

Since 1994, he has been with the United Microelectronics Corporation, Hsinchu, Taiwan, where he is currently the Manager responsible for advanced device development.