# 國科會微電子學門研究發展及推動小組 92 年度結案報告

學門召集人:李鎮宜 教授

92年11月

# 前言:

随著全球經濟緩步復甦之際,各國政府皆不約而同地思考如何強化科技產業的競爭優勢,我國亦然。藉由國家型計畫的推動與科技政策的宣導,以便能掌握到這一波的經濟成長的動能與契機。

半導體產業是「兩兆雙星」中的政策所規劃的一兆產業,依目前成長的趨勢,預估在 2006 年可達到兆元以上的產值。為維持此一產業的持續成長,並符合晶片系統國家型科技計畫的規劃目標,微電子學門所規劃的重點研究領域包含奈米級元件及製程,高速元件,射頻電路,單晶片系統,極低功率設計技術...等,這些重點將以整合型計畫推動為主,藉由團隊合作的研究模式,來提昇整體的研發能量和掌握關鍵的技術。

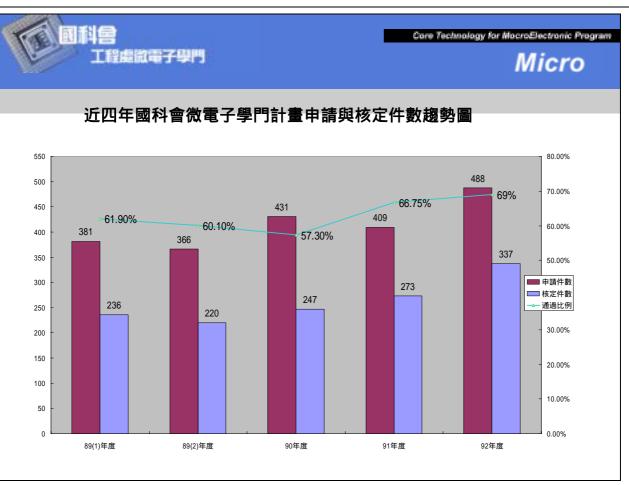

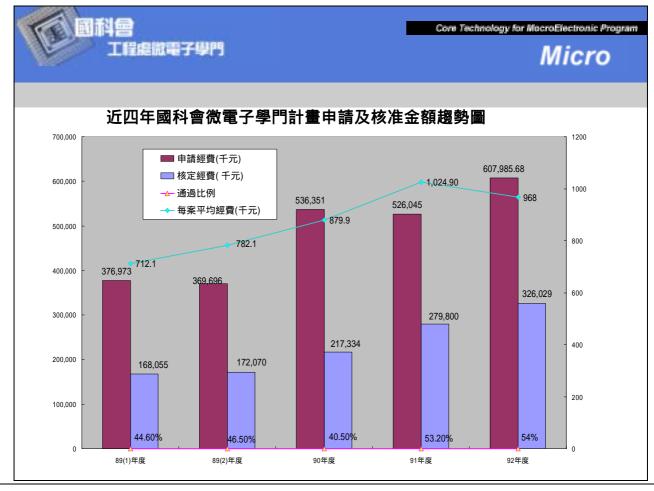

92 年度微電子學門專題研究計畫總共通過 337 件,總金額為三億二仟六佰零二萬九仟一佰元整。通過的件數較去年成長 28%,而通過的金額也較去年成長 26%。期盼未來在大家的努力下,所產生的研發成果能轉化為國內半導體產業持續成長的動能。

Micro

# 九十二年度國家科學委員會 微電子學門概況

召集人:李鎮宜

Core Technology for MocroElectronic Program

Micro

# Outline

- ♥92年學門規劃重點

- ♥92年學門成果總覽

- ♥92年度會議紀錄

- ◎矽導計劃—晶片系統國家型科技計劃

- ◎92年度專題計劃成果發表會

Micro

# 92年微電子學門規劃重點

- ♥ 元件與製程

- --前瞻性技術

- --化合物半導體

- --矽基元件與製程技術

- VLSI/CAD

- --晶片系統模組及介面設計

- --類比、 混合訊號及RF模組設計

- --晶片系統之設計、驗證自動化與EDA特色研究

- --極低功率設計技術

Core Technology for MocroElectronic Program

Micro

# 計劃申請總覽

| 微電子學門              | 案數             | 補助金額(NT)    |  |  |

|--------------------|----------------|-------------|--|--|

| 矽半導體材料與元件          | 149            | 132,754,097 |  |  |

| VLSI/CAD           | 210            | 196,549,359 |  |  |

| 化合物半導體             | 46             | 72,465,269  |  |  |

| 晶片系統設計研究計<br>劃推動專案 | 24群            | 132,754,079 |  |  |

| 總 計                | 488 607,985,68 |             |  |  |

| 平均每案               | 1,245,872      |             |  |  |

# 計劃通過總覽

| 微電子學門              | 案數        | 補助金額(NT)    |  |  |  |

|--------------------|-----------|-------------|--|--|--|

| 矽半導體材料與元件          | 93        | 95,865,000  |  |  |  |

| VLSI/CAD           | 130       | 103,606,400 |  |  |  |

| 化合物半導體             | 26        | 30,704,500  |  |  |  |

| 晶片系統設計研究計<br>劃推動專案 | 14群       | 95,853,200  |  |  |  |

| 總 計                | 337       | 326,029,100 |  |  |  |

| 平均每案               | 967,445.4 |             |  |  |  |

Core Technology for MacroElectronic Program

Micro

# 各子學門計劃申請/通過狀況

| 砂半導體材料<br>與元件    |     | VLSI/CAD     |     | 化合物          | 勿半導體 | 晶片系統設計<br>研究計劃推動<br>專案 |    |              |

|------------------|-----|--------------|-----|--------------|------|------------------------|----|--------------|

| 項目<br> <br>      | 案數  | 申請金額<br>(千元) | 案數  | 申請金額<br>(千元) | 案數   | 申請金額<br>(千元)           | 案數 | 申請金額<br>(千元) |

| 申請               | 149 | 132,754      | 210 | 196,549      | 46   | 72,465                 |    |              |

| 通過               | 93  | 95,865       | 130 | 103,606      | 26   | 30,705                 | 88 | 95,853       |

| 通過率              | 62% | 72%          | 62% | 53%          | 57%  | 42%                    |    |              |

| 平均每<br>件通過<br>金額 | 1,  | ,030,807     |     | 796,969      |      | 1,180,961              |    | ,089,239     |

Micro

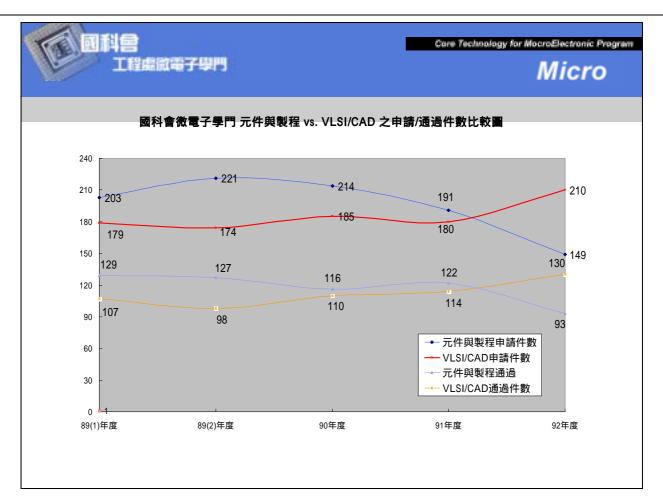

# 近四年VLSI元件與製程件數比

| 年度   | VLSI | /CAD | 元件與 | <b>製程</b> | VLS<br>元件∮ |        |

|------|------|------|-----|-----------|------------|--------|

|      | 申請   | 通過   | 申請  | 通過        | 申請         | 通過     |

| 89-2 | 174  | 98   | 221 | 127       | 1:1.27     | 1:1.30 |

| 90   | 185  | 110  | 214 | 116       | 1:1.16     | 1:1.05 |

| 91   | 180  | 111  | 191 | 116       | 1:1.06     | 1:1.04 |

| 92   | 210  | 130  | 149 | 93        | 1.4:1      | 1.4:1  |

Core Technology for MocroElectronic Program

Micro

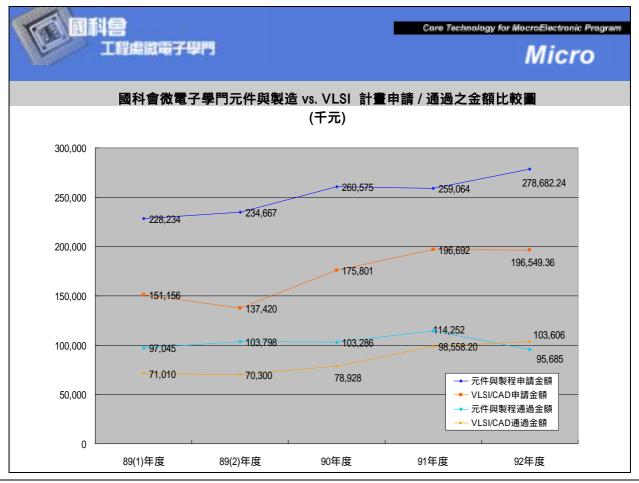

# 近四年VLSI元件與製程金額比(千元)

| 年度   | VLSI    | /CAD    | 元件與     | <b>與程</b> | VLSI:<br>元件與製程 |        |  |

|------|---------|---------|---------|-----------|----------------|--------|--|

|      | 申請      | 通過      | 申請      | 通過        | 申請             | 通過     |  |

| 89-2 | 137,420 | 70,300  | 234,667 | 103,798   | 1:1.71         | 1:1.48 |  |

| 90   | 175,801 | 78,928  | 260,575 | 103,286   | 1:1.48         | 1:1.31 |  |

| 91   | 196,692 | 95,709  | 259,065 | 126,703   | 1:1.31         | 1:1:32 |  |

| 92   | 196,549 | 103,606 | 132,754 | 95,865    | 1.5:1          | 1.1:1  |  |

# 計劃預核總覽

| 微電子學門               |                         | 93年度         | 94年度 |             |  |

|---------------------|-------------------------|--------------|------|-------------|--|

|                     | 案數                      | 補助金額<br>(NT) | 案數   | 補助金額(NT)    |  |

| 矽半導體材料與元件           | 21                      | 27,982,500   | 4    | 3,489,700   |  |

| VLSI/CAD            | 34                      | 42,725,400   | 8    | 8,691,600   |  |

| 化合物半導體              | 8                       | 12,971,900   | 4    | 4,945,200   |  |

| 晶片系統國家型暨目標<br>導向型計劃 | 75                      | 92,952,400   | 68   | 83,198,800  |  |

| 總 計                 | 138                     | 176,632,200  | 84   | 65,956,040  |  |

| 平均每案                | 1,279,943.5 1,194,348.8 |              |      | 1,194,348.8 |  |

Core Technology for MocroElectronic Program

Micro

# 近五年計劃核定情形

| 年度   | 申請件數 | 核定件數 | 通過比例  | 申請經 <b>費</b><br>(千元) | 核定經 <b>費</b><br>(千元) | 每案平均經<br>費(千元) |

|------|------|------|-------|----------------------|----------------------|----------------|

| 88   | 293  | 194  | 66.2% | 278,098              | 146,685              | 756.1          |

| 89-1 | 381  | 236  | 61.9% | 376,973              | 168,055              | 712.1          |

| 89-2 | 366  | 220  | 60.1% | 369,696              | 172,070              | 182.1          |

| 90   | 431  | 247  | 57.3% | 536,351              | 217,334              | 879.9          |

| 91   | 409  | 264  | 64.5% | 526,047              | 259,282              | 982.1          |

| 92   | 488  | 337  | 69%   | 607,986              | 326,029              | 967.5          |

Micro

# 近六年研究人力分析

| 年   | 師   |      | 資         | 學    | 生   |     |      |      |

|-----|-----|------|-----------|------|-----|-----|------|------|

| 年 度 | 教授級 | 副教授級 | 助理<br>教授級 | 其他   | 總人力 | 博士生 | 碩士生  | 總人力  |

| 87  | 133 | 131  | 11        | 3    | 278 | 232 | 425  | 657  |

| 88  | 156 | 127  | 35        | 1    | 319 | 240 | 470  | 710  |

| 89  | 161 | 117  | 50        | 4    | 332 | 244 | 478  | 722  |

| 90  | 183 | 150  | 74        | 6    | 413 | 280 | 541  | 821  |

| 91  | 191 | 145  | 104       | 8    | 448 | 384 | 830  | 1214 |

| *92 | 213 | 141  | 135       | 12   | 510 | 396 | 1035 | 1431 |

|     |     | *9   | 2年度數據     | 基準數( |     | Х 3 | ı    |      |

國科會 工程處放電子學門

Care Technology for MacroElectronic Program

Micro

# 執行研究成果

|        |     | 已  | 發表之詞 | 已獲之專利項數 |     |     |     |     |

|--------|-----|----|------|---------|-----|-----|-----|-----|

| 年度<br> | 或   | 內  | 國外   |         | SCI | EI  | 國內  | 國外  |

|        | 會議  | 期刊 | 會議   | 期刊      |     |     |     |     |

| 1999   | 240 | 26 | 299  | 336     | 287 | 111 | 48  | 38  |

| 2000   | 382 | 75 | 441  | 576     | 424 | 216 | 148 | 80  |

| 2001   | 346 | 66 | 466  | 590     | 480 | 175 | 99  | 47  |

| 2002   | 301 | 52 | 263  | 442     | 226 | 182 | 100 | 171 |

| *2003  | 321 | 69 | 315  | 492     | 282 | 189 | 126 | 153 |

<sup>\*\*92</sup>年度數據基準數(回函數) X 3

# 推動「矽半導體元件及製程前瞻技術」座談會 會議紀錄

會議時間: 2003年3月14日 12:00 am ~ 1:30 pm

地 點: 新竹煙波飯店明湖園中餐廳

主 席: 國科會微電子學門召集人李鎮宜教授

出席人員: 國家奈米實驗室林鴻志副主任及趙天生副主任、工研院電子所蔡銘

進組長、欣詮科技盧志遠董事長、聯華電子盧火鐵副部長、台積電甘萬達副處長、

台大胡振國教授、交大雷添福教授

紀 錄: 周伶霞

#### 一、 召集人綜合說明:

就整個大環境垂直分工的角度來看,不管國內最近最熱門的 IC design 產業,或最近國家大力推行的矽島計畫,晶圓製造工業都扮演著極為重要的 fundamental 及支援的角色。也就是說在台灣要有蓬勃發展的 IC 設計產業是必須仰賴一個具有競爭力的晶圓製造業做為基礎。希望透過這次座談會的開始,建立一個經常性的機制(每三到四個月召開一次座談會),將產學業界的意見彙整之後,由微電子學門這方面來推動。期使微電子學門在制定元件與製程方面的相關計畫及方向時,更能符合整個產業界的脈動與需求,進而強化晶圓製造之優勢。

#### 二、討論決議:

1. 加強奈米領域在微電子學門裡的種要性:

在奈米國家型計畫方面」奈米科技的研究在微電子領域中是未來發展的趨勢之一。同時,此範疇的技術與研究對於提昇國家電子產業的競爭優勢的前景也令人期待,所以雖然國科會工程處有支援部分的經費於奈米國家型計畫中,是否除了在經費注浥外,微電子學門可以在此項國家型計畫中扮演更積極的角色;如爭取在奈米國家型計畫中納入微電子學門部份的重要性及正當性,或加強微電子學門成員在此一國家型計畫所申請的專案計畫比例。

在微電子學門方面,增加奈米研究專案計畫的比例 近年來因學門增有晶片系統國家型計畫的補助,所以在 VLSI/CAD 子學門中各項研究計畫經費的撥支比例也應有所調整

- 2. 雖然學門所推動的 giga scale integration 有其執行層面上的困難 , 但這項整合元件製造與設計資源的計畫 , 是走在業界的先端 , 確有其繼續推行的必要。

- 3. 人才培育的問題:近年來台灣在國外期刊所投的論文篇數有明顯的提升,但是否可維持下去才是重點。所以人才的培養及避免師資的流失相對的就重要許多。另一方面,業界普遍遇到 a. 人力素質的降低 b. 留不住人才,往往將晶圓製造業當作進入 IC design 界的跳板的問題。

<u>人才的培養</u> 是否應考慮放寬外國學生來台就學及研究,並鬆綁其在台就業之相關程序及法令。

師資的流失 正視及檢討大型國家型計畫推動的同時也會造成師資結構的改變。

4. 下次開會時間正值提報 94 年度科技計畫預算編列時期,希望到時大家能提出更具體的建議及方向,以供微電子學門在編列計畫預算時重要的參考。

### SOC 北中南推動方案會議記錄

時間:92年7月17日

地點:國家晶片系統設計中心 大會議室

紀錄:周伶霞

出席人員:李鎮宜主任、劉濱達教授、任建葳教授、陳少傑教授、蔡加春教授、吳誠文主任

討論內容:

1. 南區 SOC 推動現況報告

2.中區 SOC 推動現況報告

3.北區 SOC 推動現況報告

#### 結論:

- 甲、舉辦一 project oriented 的研討會透過此一會議加強新進老師及北中南成員對微電子學門的認識,使下年度國科會專題研究計畫申請時,能導入更多的 SoC 成員申請本學門的計畫,以達到成立此推動方案之初衷。由劉濱達教授主辦。

- 乙、因新進老師及科技大學或技術學院的老師們比較不易申請到專題研究計畫的補助,未來還是希望由資深的老師帶領的方式,增加這些新進教師、科技大學及技術學院老師們申請到經費的機會,也較易建立起良好的 credit。

- 丙、現今在推廣所遇到的共同問題是經費比例上的問題。因經費設計上的不易變動(而後已解釋 20%流入 30%流出的規定)尤其是人事費上的不足,往往造成好不容易申請到計畫但執行人手又不夠的窘境。

- 丁、於年底的成果發表會多設一議程有關 SoC 北中南成果討論會議,由各區域召集人推薦一至兩名成員做報告,另在 post 時間也設立 SoC 北中南專區,以顯示具體成果。

#### 93 年度國科會晶片系統國家型科技計畫目標導向型整合研究專案研究領域

#### 規劃書討論會議

時間:92年9月4日(四) 地點:交大工程四館424R

出席人員:交大電子系李鎮宜主任、交大電子所任建葳教授、

交大電子所溫瓌岸教授、交大電子周景揚教授 交大電子吳介琮教授、台大電機汪重光教授

清大電機系林永隆教授、成大電機系劉濱達教授、 中原資工系陳美麗教授、清大電機系吳誠文主任

中央電機周世傑教授、中正電機王進賢教授

工研院電子所徐爵民所長

記錄: 周伶霞

#### 目標:

依據 ISSCC 研討會所發表之 論文,並參考 IC 設計趨勢,制訂明確技術指標,作為計畫成果驗收之評估標準,藉以提昇學術界創新技術之能量。

#### 重點:

技術指標包含極低功率設計,超高速傳輸電路,多媒體處理器以及奈米製程之實體自動化等。每一總計畫必須包含陳述國內外現狀以及三年內所欲達成的標的,並分年陳述如何與世界同步(或超前)進而以一前瞻系統載具驗證所研發技術之可行性。

#### 時程:

分兩階段公開徵求

第一階段 9/8 公開徵求, 10/8 計畫書截止。(92/11/1 - 95/7/31): 10/31 書面及口頭報告, 11/1 核定並執行。

第二皆段(93/8/1 - 96/7/31): 9/8 公開徵求, 12/31 截止

#### 晶片系統國家型科技計畫

#### 『目標導向型研究專案』 - 公開徵求研究計畫書

#### 壹、前言

國科會工程處已於 91 年度開始推動晶片系統整合型研究計畫,並於 92 年度配合晶片系統國家型科技計畫的執行,目前有十多件核准案件執行中;內容包含前瞻性系統、平台以及矽智財等研究計畫,帶動學術界的晶片及系統研究。

為進一步呈現具體的推動成效,國科會將另推動『目標導向型研究專案』,將國際一流會議的技術指標,作為本專案的參考標的,期望藉由技術層次的提昇,一方面培育更多相關領域的高科技人才,另一方面,以期帶動國內產業界在國際上的競爭優勢。

#### 貳、推動目標

以國際一流會議(如 ISSCC, DAC,ITC,...等)所發表之論文,並參考 IC 設計趨勢,制定明確技術指標,作為計畫成果驗收之評估標準,藉以提昇學術界創新技術之研發能量。

#### 參、推動重點

- (一)極低功率設計

- (二)高效能類比電路

- (三)處理器

- (四) 奈米製程之實體設計(EDA 及 Testing)

#### 肆、計畫內涵

| 每一總計畫必須包含陳述國內外現狀以及三年內所欲達成的標的及技術指標,並分年陳述如 | | |何與世界同步(或超前),進而以一前瞻系統載具驗證所研發技術之可能性。

#### 伍、推動時程

92/09/10 正式公告

92/10/13 計畫書截止收件

92/10/14 92/10/24 計畫書審查

92/10/25 92/10/31 會議審查

|92/11/01 | 93/07/31 計畫開始執行

#### 陸、申請辦法

『目標導向型研究專案』申請案,請於 10月 13日前(以郵戳為憑),提送計畫書(含 1.一式四份,2.計畫書電子檔案(MS Word 格式)),備函向國科會提出申請,計畫書撰寫時,請採用國科會專題研究計畫申請書格式,惟請於申請袋上及計畫書首頁加註「晶片系統國家型科技計畫---目標導向型研究專案」字樣,並於計畫歸屬處別勾選「工程處」。

#### 柒、專案推動工作小組

#### 計畫規劃人:

李鎮宜教授(交通大學電子工程系主任)

Tel: (03)571-2121ext.54110

E-mail: cylee@cc.nctu.edu.tw

計畫聯絡人:

潘敏治先生(國科會工程處)

Tel: (02)2737-7983

E-mail: mcpan@nsc.gov.tw

林晏妃小姐(NSoC 專任助理)

Tel: (02)2737-7371

E-mail: yflin@nsc.gov.tw

## 晶片系統國家型科技計畫--公開徵求 93 年度研究計畫書

#### 壹、前言

國科會工程處已於 91 年度開始推動晶片系統整合型研究計畫,並於 92 年度配合晶片系統國家型科技計畫的執行,目前有十多件核准案件執行中;內容包含前瞻性系統、平台以及矽智財等研究計畫,藉由這些整合型計畫的推動,已促成學術界在積體電路及系統設計的活躍研究。

93 年度工程處仍將持續推動相關前瞻性技術的整合型計畫,包含一般型及目標導向型研究專案,一方面培育更多相關領域的高科技人才,另一方面,落實並提昇技術層次,進而強化國內積體電路及系統設計產業在國際上的競爭優勢。

#### 貳、推動目標

以國際一流會議所發表之論文技術層次,並參考 IC 設計趨勢,制定明確技術指標,作為計畫成果驗收之評估標準,藉以提昇學術界創新技術之研發能量。

#### 參、推動重點

- (五)極低功率設計技術

- (六)高頻與高效能類比電路

- (七)處理器及相關軟體技術

- (八) 奈米級製程之實體設計(EDA 及 Testing)

#### 肆、計畫內涵

計畫性質分一般型及目標導向型整合研究計畫,其中目標導向型需符合上述所規劃之推動重點。

每一總計畫必須包含陳述國內外現狀以及執行期限內所欲達成之標的和技術指標,並分年陳 述如何與世界同步(或超前),進而以一前瞻系統載具驗證所研發技術之可能性。

#### 伍、推動時程

92/10/10 正式公告

92/12/31 計畫書截止收件

93/3/1 93/4/10 計畫書審查

93/4/10 93/4/30 會議審查(目標導向型計畫須進行口頭報告)

93/8/1 計畫開始執行 -- 依 NSC 一般作業時程

#### 陸、申請辦法

研究計畫書請於 12 月 31 日前(以郵戳為憑),提送計畫書(含 1.一式四份,2.計畫書電子檔案(MS Word 格式),備函向國科會提出申請,計畫書撰寫時,請採用國科會專題研究計畫申請書格式,若屬於目標導向型計畫,請於申請袋上及計畫書首頁加註「晶片系統國家型科技計畫---目標導向型研究專案」字樣,並於計畫歸屬處別勾選「工程處」。

柒、專案推動工作小組

計畫規劃人:

李鎮宜教授(交通大學電子工程系主任)

Tel: (03)571-2121ext.54110

E-mail: cylee@cc.nctu.edu.tw

周伶霞小姐 (微電子學門專任助理)

Tel; (03)5712121 ext.54251; (03)5731849

E-mail: lhchou@si2lab.net

計畫聯絡人:

|潘敏治先生(國科會工程處)

Tel: (02)2737-7983

E-mail: mcpan@nsc.gov.tw

林晏妃小姐(NSoC 專任助理)

Tel: (02)2737-7371

E-mail: yflin@nsc.gov.tw

# 九十一年度國科會微電子學門專題計畫研究成果研討會

主 辦 單 位: 國 科 會微電子學門

承辦單位 : 長庚大學電子系

協辦單位 : 國科會工程處工程科技推展中心

時 間 : 九十二年十一月二十九 日(六)~ 三十日 (日)

地 點:台北縣深坑鄉 麗園會館教育訓練中心

# 會議議程簡表

會議名稱: 九十一年度國科會微電子學門專題研究計畫成果研討會

會議日期: 92 年 11 月 29 日(六)至 92 年 11 月 30 日(日) 會議地點: 麗園會館 台北縣深坑鄉北深路 3 段 265 號

| 日期 | 時間              | 地點                          |                  |                      | 內容      |        | 註 |

|----|-----------------|-----------------------------|------------------|----------------------|---------|--------|---|

|    | 13: 30 ~ 14: 30 | 1F Lobby                    | 報至               | 報到及 check in         |         |        |   |

|    | 14: 30 ~ 14: 45 | B1 嘉賓廳                      | 微                | NSC 工程處長<br>微電子學門召集人 |         |        |   |

| 92 | 14: 45 ~ 15: 00 | B1 嘉賓廳                      |                  | 論文獎頒獎                |         |        |   |

| 年  | 15: 00 ~ 15: 15 | B1 嘉賓廳                      |                  | NDL 業務說明             |         |        |   |

| 11 | 15: 15 ~ 15: 30 | B1 嘉賓廳                      |                  | CIC 業務說明             |         | 眷屬     |   |

| 月  | 15: 30 ~ 15: 50 | B1 嘉賓廳外<br>走廊               | 休息時間             | /Coffee Break        |         | 旅<br>遊 |   |

| 日  | 15: 50 ~ 17: 30 | B1 嘉賓廳/3F<br>翡珍廳/3F 琥<br>珀廳 | 學術分組<br>VLSI/CAD | 報告討論<br>Si/Compound  | 廠商演講    |        |   |

|    | 17: 40 ~ 19: 00 | 2F 中餐廳                      | 晚餐(              | <u> </u>             |         |        |   |

|    | 19: 00 ~ 20: 00 | B1 嘉賓廳/3F<br>翡珍廳/3F 琥<br>珀廳 | 重要會議             | 參與報告                 | 廠商      |        |   |

|    |                 |                             | VLSI/CAD         | Si/Compound          | 演講      |        |   |

|    | 20: 00 ~ 21: 00 | B1 嘉賓廳/3F<br>翡珍廳/3F 琥<br>珀廳 |                  | 業界交流討論會              | 廠 商 演 講 |        |   |

|    | 21: 00 ~ 22: 00 | B1 嘉賓廳<br>/3F 翡珍廳           |                  | 業界交流討論會              | 廠 商 演 講 |        |   |

附帶會議: 21:00 ~ 22:00 3F琥珀廳 積體電路設計學會指導委員會議

| 日期 | 時間            | 地點                           | 內容                |          | 註 |

|----|---------------|------------------------------|-------------------|----------|---|

|    | ~7:00         |                              | 晨遊                |          |   |

|    | 7:00 ~ 8:00   | 1F 西餐廳                       | 早餐                | <u> </u> |   |

| 92 | 8:00 ~ 9:00   | B1 嘉賓廳/<br>3F 翡珍廳/<br>3F 琥珀廳 | Poster 討論時間       |          |   |

| 年  | 9:10 ~10:10   | B1 嘉賓廳                       | 邀請演講(1)           | 眷屬       |   |

| 11 | 10:10 ~ 10:30 | B1 嘉賓廳外<br>走廊                | 休息時間/Coffee Break | 旅遊       |   |

| 月  | 10:30 ~ 11:30 | B1 嘉賓廳                       | 邀請演講(2)           |          |   |

| 30 | 11:30 ~ 12:10 | B1 嘉賓廳                       | 綜<br>合座談          |          |   |

| 日  | 12:20 ~ 14:00 | 2F 中餐廳                       | 午餐 (自助式)          |          |   |

|    | 14:00         |                              | 圓滿                | 結束       |   |

# VLSI/CAD 學術分組報告討論

時間: 11/29 3:50 ~ 5:30 PM 地點: B1 嘉賓廳

主持人: 清大資工 林永隆教授

A) 3:50 ~ 4:10 PM

台大電子所 陳良基教授

「多媒體通訊系統中可重組化運算技術之研究(1/3)」

B) 4:10 ~ 4:30 PM

清大資工 林永隆教授

「高性能低功率數位訊號處理核心」

C) 4:30 ~ 4:50 PM

交大電子 吳介琮教授

「高性能混合訊號式介面積體電路(1/3)」

D) 4:50 ~ 5:10 PM

中原資工 陳美麗教授

「時序驅動之實體設計系統」

E) 5:10 ~ 5:30 PM

成大電機 郭泰豪教授

「5GHZ無線區域網路(WLAN)接收機之前端CMOS電路設計」

# Si/Compounds 學術分組報告討論

時間: 11/29 3:50 ~ 5:30 PM 地點: 3F 翡珍廳

主持人: 交大電子 雷添福教授

A) 3:50 ~ 4:10 PM

成大電機 王永和教授

「液相氧化法在砷化鎵系列材料元件上的應用(1/3)」

B) 4:10 ~ 4:30 PM

中央電機 詹益仁教授

「利用感應耦合電漿蝕刻技術製作在磷化銦基板之上之毫米波積體 電路」

C) 4:30 ~ 4:50 PM

交大電子 曾俊元教授

「新世代鐵電非揮發性記憶元件(2/3)」

D) 4:50 ~ 5:10 PM

中山電機 李明逵教授

「以MOCVD成長ZnSSe自聚性量子點(2/2)」

E) 5:10 ~ 5:30 PM

交大電子 黃調元教授

「蕭特基能障SOI金氧半電晶體元件研製與分析(II)」

### VLSI/CAD 參與國外重要會議報告

時間: 11/29 7:00~7:40 PM 地點: B1 嘉賓廳

主持人: 台大電子所 張耀文教授

A) 7:00 ~ 7:10 PM

CIC 邱進峰組長 報告參與 ISSCC 會議心得成果

B) 7:10 ~ 7:20 PM

CIC 王鴻猷組長 報告參與 VLSI Sym.會議心得成果

C)  $7:20 \sim 7:30 \text{ PM}$

CIC 王仁傑組長 報告參與 ICCAD 會議心得成果

D)  $7:30 \sim 7:40 \text{ PM}$

CIC 黃俊銘組長 報告參與 DAC 會議心得成果

## Si/Compounds 參與國外重要會議報告

|時間: 11/29 7:00 ~ 7:40 PM 地點: 3F 翡珍廳

主持人: 成大電機 王永和教授

A)  $7:00 \sim 7:20 \text{ PM}$

交大電子 荊鳳德教授 報告參與 IEDM 會議心得成果

B) 7:20 ~ 7:40 PM

中央電機 詹益仁教授 報告參與 SSDM 會議心得成果

### 北中南SOC專題成果報告

時間: 11/29 7:40~8:40 PM 地點: B1 嘉賓廳

主持人: 台北科大 蔡加春教授

A) 7:55~8:10 PM 北區

聖約翰技術學院(原新埔技術學院) 電機系 簡忠漢 副教授 「嵌入式內核系統應用於可程式系統晶片之除錯架構研究」

B) 8:10~8:25 PM 中區

國立聯合大學 電子系 陳宏偉教授

「射頻通訊數位類比轉換器的系統設計與實作」

C) 8:25 ~8:40 PM 南區

義守大學 資訊工程系 金明浩副教授

「提昇高性能系統核心之速度.可靠度和私密性之 IP 研究」

## Si/Compounds 專題演講及業界交流討論

|時間: 11/29 7:40 ~ 10:00 PM 地點: 3F 翡珍廳

主持人: 交大電子 莊紹勳教授

A)7:40-8:10 專題演講 聯電 廖寬仰部長

Advanced Foundry Technology Challenges

B)8:10-8:40 專題演講 工研院電子所 蔡銘進組長

奈米應用技術與半導體產業-產學研合作的新契機

8:40-8:50 Break

### C)8:50-9:20 專題演講 臺積電 梁孟松協理

Advanced Gate Stack and Cu/Low-k Interconnect

Technologies

D)9:20-10:00 Panel discussio

Si/Compounds 專題演講

# **Advanced Foundry Technology Challenges**

廖寬仰部長 聯華電子公司 中央研究發展部/先進模組暨先期技術開發

#### Abstract

The migration to Cu interconnects technology and manufacturing with 300 mm wafers have been successfully achieved at 0.13um technology node. While carrying the experience learned, 90nm generation would resume the pace of CMOS scaling down without any major technology difficulties insight. However, significant technological difficulties lay ahead for continuous CMOS scaling to generations beyond 65nm node. New materials/ transistor schemes are proposed to overcome these technology barriers with examples such as high k dielectrics as a solution to high gate leakage current, metal gate for work function adjustment, strain silicon to increase mobility and drive current, and ultra low k dielectrics for increased RC delay issues. In addition, advanced lithography solution remains unclear for high N.A. process beyond 193nm wavelength. All these new materials/technologies create new set of challenges and would need extensive research efforts before being implemented in mass production. This talk will describe UMC view on these challenges for advanced foundry technology.

# Si/Compounds 專題演講

### 奈米應用技術與半導體產業-產學研合作的新契機

# 工業技術研究院電子工業研究所 奈米電子元件技術組 蔡銘進組長

#### **Abstract**

The progress of nano-science and nano-technology has brought great impact on practically every aspect of the industry involving modification and improvement of materials. The earnest needs to combine science and technology also serves as a good driving force for industry, academia and research groups to co-work more closely and intensively. It is especially prominent for an industry like the semiconductor which is primarily based on the nanoelectronics technology. The allocation of the R&D resources on topics at various stages of development has to be carefully planned. In this presentation, the research topics, including Non-volatile Memory Devices (MRAM, OUM and OBD), CMOS-related processes (High K and Strained Si) and New materials/Devices (CNT/Si NW FET), conducted at ERSO/ITRI will be addressed with the latest results. New models of collaboration by newly implemented programs in ITRI with the academia (自主性前瞻計畫,學研合作計畫) and industry (奈米檢測與製程共同實驗室者聯盟,奈米電子共同實驗室使用者聯盟) will also be presented with examples and for further discussion.

### Si/Compounds 專題演講

## Advanced Gate Stack and Cu/Low-k Interconnect Technologies

梁孟松 協理

臺灣積體電路製造公司研究發展部

#### **Abstract**

Technology migration below 130nm-node requires several new materials introduction. 300mm

manufacturing for better economy scale also imposts new production risk and huge R&D investment. Therefore, a smooth transition to cope with all challenges is critical to maintain competitive.

Key barrier in advanced front-end process is thin gate dielectric in the range of 1nm with low leakage. Incorporation of nitrogen into thermal oxide can effectively suppress direct tunneling current. However, it introduces the unexpected device damages, such as mobility degradation and NBTI. Further scaling of gate dielectric thickness requires implementation of hi-K dielectrics due to its thicker dimension. Hf oxide has been a prime candidate for the industry so far. The integration with conventional CMOS process still requires breakthroughs in the areas of film trapped charges, interface property, & long-term reliability.

Further metal pitch scaling brings undesired interconnect RC performance degradation. The implementations of Cu and low-K dielectric are the must to alleviate the trend. Low-K materials in general are in the porous forms, and therefore have less density, and modulus. These weak chemical and mechanical properties result in the complicated integration flow. Besides, poor interface with metal film could have severe die package and reliability issues.

The presentation will be focused on front-end hi-K integration as well as back-end Cu/low-K interconnect, from device, reliability, and manufacturing aspects.

# 邀請演講及學門座談

## 邀請演講 (一)

時間: 11/30 9:10 ~ 10:10 AM 地點: B1 嘉賓廳

引言人: 台大電子所 陳良基教授

主講者: 工研院 徐爵民副院長

講 題:微電子技術的未來

## 邀請演講 (二)

時間: 11/30 10:30~11:30 AM 地點: B1 嘉賓廳

引言人: 長庚電子 馮武雄教授

# 學門綜合座談

時間: 11/30 11:30~12:10 AM 地點: B1 嘉賓廳

主持人: 交大電子 李鎮宜教授

九十一年度國科會微電子學門專題計畫研究成果研討會

住宿:麗園會館台北縣深坑鄉北深路3段265號

Tel: (02)2217-5361 Fax: (02)2662-7428

會議室: B1嘉賓廳、3F翡珍廳、3F琥珀廳

用 餐: 2F中餐廳、1F西餐廳 住房: 5F~ 17F

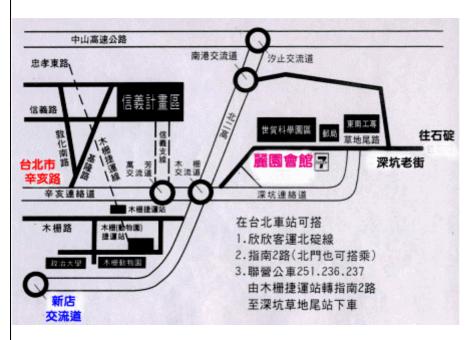

### 交通資訊

#### 停車場說明

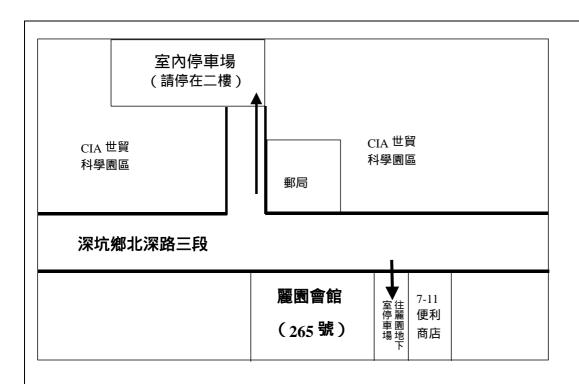

- 1. 麗園會館右側可通往麗園地下室停車場(有五十個車位)。

- 另在麗園對面的巷子(郵局旁邊)直走50公尺,可通往一室內停車場,其中停車場<u>二樓</u>(有 200個以上車位)會開放給參加微電子學門研討會的來賓使用。請來賓儘量使用此停車場<u>二樓</u>

設施簡介:住宿者免費使用休閒設施包括健身房、撞球、卡拉OK及文山 活水館 (SPA、藥浴養生池、游泳池、烤箱三溫暖)

# <u>餐飲</u>

用餐請隨身攜帶餐券及大會識別證,工作人員將管制進出。

餐廳: 29日晚餐(合菜)及30日午餐(自助式) 在 2F 中餐廳

30日早餐(自助式) 在 1F 西餐廳

眷屬旅遊: 為不影響議程進行, 僅限眷屬參加。

行程: 深坑老街 古蹟巡禮(永安居) 2:40~5:30 PM

集合時間地點: 11月29日 2:40 PM 麗園會館大門口

行程: 動物園 8:10~12:00 AM

集合時間地點: 11月30日 8:10 AM 麗園會館大門口

行程: 鶯歌陶瓷博物館 8:10~11:30 AM

集合時間地點: 11月30日 8:10 AM 麗園會館大門口

<u>交通車</u>: 回程

路線一: 台中、台南、高雄

集合時間地點: 11月30日 2:10 PM 麗園會館大門

路線二: 中壢、新竹

集合時間地點: 11月30日 2:20 PM 麗園會館大門

聯絡資訊

承辦單位 : 長庚大學電子工程學系

桃園縣333龜山鄉文化一路259號

電話: 03-2118800 ext. 5801

傳真: 03-2118507

網頁: <a href="http://www.elec.cgu.edu.tw">http://www.elec.cgu.edu.tw</a>

電子信箱: nscmicro@mail.cgu.edu.tw

大會網址: http://163.25.97.26/nsc2003/index.html

工作組織

活動主持人 馮武雄 (長庚大學工學院)

行政助理 林玟璣 (長庚大學電子工程學系)

張素卿 (長庚大學電子工程學系)

秘書組 周煌程 (長庚大學電子工程學系)

論文與議程組 賴朝松 (長庚大學電子工程學系)

張睿達 (長庚大學電子工程學系)

網路與出版組 陳思文 (長庚大學電子工程學系)

詹曉龍 (長庚大學電機工程學系)

總務與產品展示組 梁新聰 (長庚大學電子工程學系)

張孟洲 (長庚大學電機工程學系)

財務與服務組 張本秀 (長庚大學電子工程學系)

鄭瑞清 (長庚大學電子工程學系)