# 行政院國家科學委員會專題研究計畫 成果報告

# 以電子迴旋共振化學氣相沈積技術成長超薄閘極絕緣膜及 可靠性之研究(3/3)

計畫類別: 個別型計畫

計畫編號: NSC91-2215-E-009-014-

執行期間: 91年08月01日至92年07月31日

執行單位: 國立交通大學電子工程學系

計畫主持人: 張國明

報告類型: 完整報告

處理方式: 本計畫可公開查詢

中 華 民 國 93年2月10日

# 行政院國家科學委員會補助專題研究計畫成果報告

| ****      | , , , , , .  | , , ,           | , , , | , , ,        | , , . | , ,         |     | .,,.         | .,,.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |

|-----------|--------------|-----------------|-------|--------------|-------|-------------|-----|--------------|---------------------------------------|

| <b>*</b>  | 以電子          | ·迴旋共·           | •     | ≧氣相が<br>「靠性≥ |       | - · · · · · |     | 閘極           | <b>*</b>                              |

| *<br>**** | <b>**</b> ** | <b>.</b>        |       | 31           | - ,   |             |     | <b>{</b> *** | ,•                                    |

| 言         | 十畫類別         | : ■個別           | 1型計   | 畫            | □整.   | 合型言         | 十畫  |              |                                       |

| 言         | 十畫編號         | : NSC           | 89-22 | 215-E-0      | 09-08 | 39          |     |              |                                       |

| 书         | 九行期間         | : 89 至          | E 8   | 月 1          | 日     | 至 92        | 年 7 | 月 31         | 日                                     |

|           | 計畫主持         | 人:張口            | 國明    |              |       |             |     |              |                                       |

| 4         | 共同主持         | 人:              |       |              |       |             |     |              |                                       |

| 1         | 計畫參與         | 人員:             | 易文誌   | <b>、朱俊</b>   | 定宜、   | 趙高          | 段、陳 | 伯寧           |                                       |

|           |              |                 |       |              |       |             |     |              |                                       |

|           |              |                 |       |              |       |             |     |              |                                       |

|           |              |                 |       |              |       |             |     |              |                                       |

|           |              |                 |       |              |       |             |     |              |                                       |

| +         | 成果報          | <b>上台</b> 红 : 1 | 1 下 旌 | 始六つ          | 以从    | •           |     |              |                                       |

| 4         |              | 百巴福<br>國外出差     |       |              |       |             |     |              |                                       |

|           |              | 因开山z<br>大陸地區    | - '   |              | ., .  |             | - 份 |              |                                       |

|           |              | 席國際學            |       |              |       |             |     | 文各一          | 份                                     |

|           |              | <b>医</b> 合作品    |       |              |       |             | •   |              |                                       |

執行單位:國立交通大學電子工程系

中華民國92年7月31日

# 以電子迴旋共振化學氣相沉積技術成長超薄閘極絕緣膜及可靠性 之研究(3/3)

# Fabrication and Reliability of Ultra-thin Gate Dielectrics by ECR-CVD Technique (3/3)

計畫編號: NSC 89-2215-E-009-089

執行期限:89年8月1日至92年7月31日 主持人:張國明 國立交通大學電子工程系

計畫參與人員:楊文誌、朱俊宜、趙高毅、陳伯寧國立交通大學電子工程系

## 一、中文摘要

在最後一年的計畫裡,我們進一步成 功地使用電子迴旋共振化學氣相沉積系統 之 N<sub>2</sub>O plasma 成長二氧化矽超薄閘極絕緣 層,並進一步調整製程條件與製程時間將 超薄氧化層的厚度從 1.6 nm 縮小到 1.0 nm, 而且實驗證明 ECR-CVD 顯示極佳的超 薄氧化層厚度控制能力,成長極超薄的1.0 nm 氧化層也可在合理的控制範圍內,成長 出均匀的氧化層薄膜,其氧化層的厚度誤 差僅在 5% 以內。另外我們更進一步使用 ECR-CVD 做 N2 氮化處理,改善超薄氧化層 完整度,將超薄氧化層的漏電流降低至 0.1A/cm2, 並且提升其可靠度。以 № 氣體 對超薄化層進行 plasma 氮化處理,實驗結 果顯示氮原子可以有效的進入超薄氧化層 中,並與氧原子形成良好的鍵結,大幅的 改善超薄氧化層的特性,並可以抵禦 p<sup>+</sup>-poly 閘極的硼原子穿透進入氧化層,因 此經過氮化處理後的 ECR-CVD №0-plasma 之 1.0 nm 超薄 oxynitride 絕緣層,顯示 極佳的 QBD 的可靠度,以及僅僅 0.1 A/cm<sup>2</sup> 的極小漏電流的絕佳電特性,並且在 PMOS 元件中 ECR-CVD N2O plasma oxide 氧化層 亦表現很強的抵抗硼穿透氧化層能力,因 此 ECR-CVD 成長的超薄氧化層再經過快速 退火處理後,有效的改善元件電特性與可 靠度, 並將可大量應用於製作深次微米的 ULSI 元件之絕緣層。

**關鍵詞**:電子迴旋共振化學氣相沉積、超 薄氧化層、硼穿透、氮化處理

#### **Abstract**

At last year, we have developed a process of growing ultra-thin oxide by using Electron Cyclotron Resonance (ECR) N<sub>2</sub>O plasma. A 1.0 nm ultrathin oxide was grown characterized for gate dielectric applications. The ECR-CVD shows excellent controlled ability of ultra-thin oxide thickness. The ECR-CVD grows 1.0 nm oxide thickness variations within 5%. We used state-of-the-art direct N<sub>2</sub> plasma nitridation methods to heavily nitrided and high quality ultrathin oxynitride film. We show that gas-phase and thin-film oxygen nitrogen incorporation chemistries facilitate the processing of layered oxynitride nanostructures with desirable electrical properties. The nitrogen is incorporated into the thin gate oxide to improve the gate oxide qualities and also prevents the boron penetration from p<sup>+</sup>-poly gate. It clearly shows the effects of nitrogen in the thin gate oxide. These ultra-thin high quality oxides had very high charge-to-breakdown QBD value of 10<sup>4</sup> C/cm<sup>2</sup> and only 0.1 A/cm<sup>2</sup> tiny current. The strong penetration resistance of the high quality oxynitride dielectric allows gate **PMOS** improve p+-poly-gate for performance. These ECR-CVD ultra-thin plasma oxides are good candidates for deep submicron devices gate-dielectrics in future.

**Keywords**: ECR-CVD · Electron Cyclotron Resonance (ECR) · thin oxide · boron penetration · Nitridation

#### Treatment

### 二、緣由與目的

在未來深次微米極大型積體電路 (ULSI)中,MOS 元件尺寸持續縮小,其閘極 介電層的厚度已經相當的薄,將持續縮小 至 1nm~4nm,特別在 PMOS 中如此薄的氧化 層將使硼相當容易穿透閘極介電層,而導 致可靠度的問題。低溫低壓電子迴旋共振 化學氣相沉積(ECR-CVD)技術,提供多項優 點,例如:低溫低壓成長適合低溫製程、 减少擴散、污染、摻雜物重新分配、以及 低電漿離子傷害等問題。因此,在未來的 ULSI 元件中,不管是作為動態隨取記憶體 (DRAM)的深溝槽(deep trench)絕緣層、高 密度高性能極大型積體電路(ULSI)元件之 絕緣層、以及低溫多晶矽薄膜電晶體閘極 氧化層之應用上,都相當的重要。但是隨 著 CMOS 閘極氧化層的厚度越來越薄,超薄 閘極界電層的品質與可靠度問題顯得越形 重要,但是要將此超薄氧化層 (<3 nm) 整 合應用到 ULSI 積體電路時,超薄閘極氧化 層的完整度(gate oxide integrity, GOI) 將是影響 CMOS 元件性最為重要的關鍵技 術。因此改善超薄氧化層的完整度已經變 成今日ULSI 積體電路製程技術中最重要的 一環,於是我們利用低能量電漿氮化處理 技術,以 ECR-CVD N-radical 進行氮化處 理以改善我們於所完成的超薄 (1.0 nm) ECR-CVD N<sub>2</sub>O-plasma oxynitride 的完整 度。

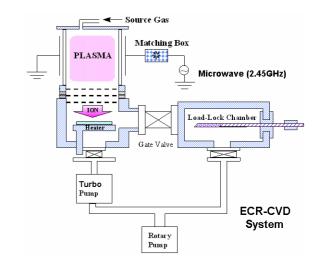

為此,我們將利用自行研發的電子迴旋共振化學氣相沉積系統,如圖一所示。有系統地研究 ECR-CVD 不同製程參數、不同氣體與不同製程溫度組合,形成的絕佳的二氧化矽絕緣膜結構,並加上 in-situ ECR-CVD  $N_2-plasma$  氮化技術,使用 ECR 系統產生的高活性離子 N-radical 對超薄氧化層進行氮化處理,並以 TEM 、 SIMS 、 Auger、ESCA 等材料分析儀器來分析元素分佈,以及物理厚度,最後以此絕緣膜製作 MOS-C 元件,並量測電性研究超薄氧化物及氮化物之電性與可靠度分析。

圖一、自行研發之電子迴旋共振化學 氣相沉積系統(ECR-CVD)示意圖,用以成長 1.0 nm 超薄氧化層,並進行氮化處理。

## 三、實驗方法

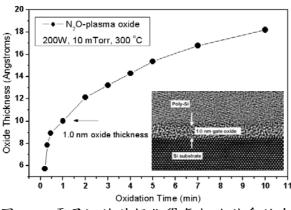

為了研究 ECR-CVD N2O plasma oxide 形成的 oxynitride 電特性與抵抗硼穿透能 力,以及加入快速退火處理後,對於超薄 氧化層薄膜特性的影響,我們製作硼摻雜 多晶矽閘極之 PMOS,該 PMOS 結構為 A1/p+ poly-gate/oxynitride/Si。首先我們用 標準 RCA clean 步驟,清洗矽晶片,接著 將晶片送進 ECR-CVD 真空腔體中, ECR-CVD N<sub>2</sub>O plasma oxide 成長條件為,使用 Ar 5 sccm/N<sub>2</sub>O 5 sccm 混合氣體作為來源氣體, 基板温度 300 °C、壓力 10 mTorr、微波功 率 200 W、微波頻率 2.45GHz 條件下成長 10 秒,獲得厚度僅 1.0 nm 之 oxynitride 超薄絕緣層,圖二依據是不同製程時間所 對應成長的氧化層厚度圖,由圖中可清楚 看出,在1分鐘以前,氧化層厚度會隨著 成長時間增長而急速增加,但是 1 分鐘以 後成長的速度會趨緩甚至變成線性

2~3Å/min,這是由於 ECR-CVD plasma oxide self-limited 效應所造成,當薄膜厚度成長變厚後,活化離子將很難穿透氧化層進而與下層的 Si 基板反應成二氧化矽,所以後續的成長速度會趨緩而成線性。

成長超薄氧化絕緣層後,不破真空的 情況下,立刻於當地進行 N2-plasma 氮化處 理進行, 氮化時間分別為 1, 3, 5 分鐘, 用以研究不同氮化處理時間對超薄氧化層 的電性與可靠度影響。接著在矽晶圓表面 覆蓋 100 nm 厚的低溫多晶矽,此多晶矽膜 乃利用低壓化學氣相沉積系統(LPCVD)在 550 ℃成長,接著進行第一道光罩定義 MOS 元件區域,形成 MOS 結構,然後以離子佈 植技術在能量 10 KeV、掺雜計量  $2 \times 10^{15} \text{ cm}^{-2}$ 條件下,植入硼離子到多晶矽膜中。完成 離子佈植後,將晶片送入高溫爐管,在900 °C通氮氣的環境下,活化硼離子30分鐘, 完成 PMOS 元件之閘極製作。最後利用金屬 熱蒸鍍方式,蒸鍍500 nm 厚之鋁,並進行 光罩製作金屬墊(Metal pad)以利量測。完 成 PMOS 元件製作後,以電容-電壓量測技 術(C-V measurement) 與 HP 4156 元件參 數量測儀器,分析 PMOS 元件之電性與可靠 度。

圖二、電子迴旋共振化學氣相沈積系統在 Ar 5 sccm/ $N_2O$  5 sccm 混合氣體作為來源氣體,基板溫度 300 ℃、壓力 10 mTorr、微波功率 200 W、微波頻率 2.45GHz 條件下依不同製程時間所對應成長的氧化層厚度圖。插圖則為 1.0 nm 超薄氧化層的 TEM 照片。

#### 四、實驗結果與討論

如圖二所示,超薄閘極氧化層的厚度,是利用穿透式電子顯微鏡製作 TEM 圖片所得到的實際厚度,上一年度我們所成長的氧化層厚度最小控制到  $1.6\,\,\mathrm{nm}$ ,這一年度我們可以利用 ECR-CVD 系統更精準的將氧化層厚度控制到  $1.0\,\,\mathrm{nm}$ ,並且厚度均勻度誤差不超過  $5\,\,\%$ 。

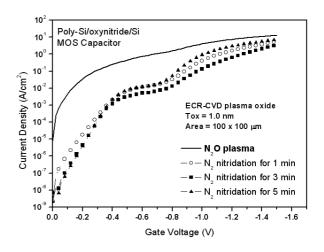

圖三、 ECR-CVD №0-plasma 1.0 nm 超薄 氧化層與氮化後結果的漏電流比較圖。

在圖三顯示 ECR-CVD 超薄氧化層 oxvnitride 經過 № 氮化處理後的電流密度 -電壓特性曲線,該 PMOS 元件的主動區面 積大小是:1x10<sup>-4</sup>cm<sup>2</sup>。我們可以清楚的看 出,經過 N2 氮化處理的 PMOS 元件大幅地降 低了閘極漏電流,對於原始 1.0 nm 超薄氧 化層以及經過氮化時間 1, 3, 5 分鐘的樣 品其漏電流密度在閘極電壓為 -1.0 V 時,分別為 4.4 A/cm², 0.42 A/cm², 0.14 A/cm², 0.9 A/cm², 和僅以 ECR-CVD N<sub>2</sub>O-plasma 方式成長沒有經過 N<sub>2</sub>氮化處理 的氧化層相較之下,漏電流密度足足降低 了約10倍。ECR-CVD in-situ 氮化處理後 會造成如此極佳的氧化層特性乃是, ECR-CVD N2-plasma 所提供的 N-radical 會 修補超薄氧化層與矽基板介面層的斷鍵 (dangling bond),或者填補超薄氧化層中 的空位 (vacancies) 與斷鍵,因為這些斷 鍵被氮原子所修補,所以大幅降低SiO<sub>2</sub>/Si 介面的缺陷密度並且在介電層中形成很強 的 Si-N 鍵結,因此不容易讓在電場作用下

產生的熱載子撞擊而產生斷鍵(dangling bond),而造成大量漏電,所以經過 ECR-CVD  $N_2$ 0一月asma 超薄氧化层理的 ECR-CVD  $N_2$ 0一月asma 超薄氧化層的 PMOS 元件擁有極低的漏電流特性。但是值得注意的是,隨著氮化時間增長 5分鐘,漏電流密度反而增加,這是因為太長的氮化處理時間,反而會引致plasma-induced-damage,而造成超薄氧化層有些微劣化現象。

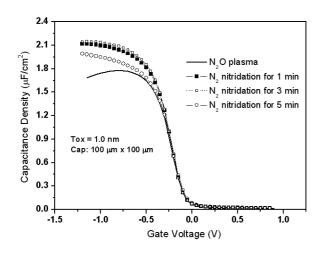

圖四、ECR-CVD 成長 1.0 nm 超薄氧化層之 PMOS 元件之 C-V 特性曲線。Control Sample 是未經過  $N_2$  氮化處理的試片、其餘三個試片是分別經過 1, 3, 5 分鐘 in-situ 氮化 處理的 samples。

圖四所示的是 PMOS 元件的 C-V 量測 圖,可以清楚的看出,經過 № 電漿氮化處 理的 ECR-CVD N<sub>2</sub>O plasma 超薄氧化層比沒 有經過退火處理的 PMOS 元件,有較高的電 容值,並有更接近和理想氧化層一樣的 C-V 特性曲線,由此可知經過氮化處理的 ECR-CVD N<sub>2</sub>O-plasma 超薄氧化層,再經過 in-situ №-plasma 氮化處理後,可明顯的 改善超薄氧化層的薄膜特性,特別是經過 № 電漿氮化處理 3 分鐘後的試片其 fixed oxide charge (Q<sub>f</sub>), mobile ionic charge (Qm), 和 oxide trapped charge (Qot)在 ECR-CVD N<sub>2</sub>O plasma 成長的 oxynitride 絕 緣層中所佔的比例非常小,由此可見快速 退火氮化處理機制可以有效的修補超薄氧 化層中的斷鍵,並且形成很強的 Si≡N 鍵 結,可以大幅改善超薄氧化層的漏電流與崩潰電壓以及可靠度等特性。並且顯示經過氮化處理的超薄 ECR-CVD  $N_2O$  plasma oxynitride 有極佳的抵擋硼穿透氧化層能力。而讓 oxynitride 氧化層具備抵擋硼穿透能力的主因就是,大量的氮原子累積在超薄氧化層的上層表面以及氧化層中,在高溫作用下也不會穿透氧化層到矽基板,而造成 PMOS 元件特性衰退。

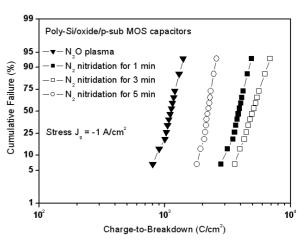

圖五、ECR-CVD 成長  $1.0\,$  nm 超薄氧化層之 PMOS 元件之 Charge-to-Breakdown 之  $Q_{BD}$  可靠度曲線圖,Control Sample 是未經過  $N_2$  氮化處理的試片、其餘三個試片是分別 經過  $1,\ 3,\ 5$  分鐘 in-situ 氮化處理的 samples。

從可靠度的觀點來看,在圖五中,經過氮化處理後的  $ECR-CVD \ N_2O-plasma\ 1.0$  nm 超薄氧化層,其 QBD 大幅提昇將近快  $3\sim4$  倍,特別是經過 3 分鐘氮化處理的試片表現最佳的可靠度特性,由此可知,氮化時間 3 分鐘為最佳條件,我們可以藉此製程條件獲得電性最佳與可靠度最佳的超薄氧化層。

#### 五、結論

我們已成功地用電子迴旋共振化學氣相沉積系統之  $N_2O$  plasma 成長僅 1.0 nm 之超薄閘極絕緣層,並且利用 ECR-CVD in-situ  $N_2$ -plasma 氮化處理對超薄氧化層

的影響進行研究。實驗結果顯示 ECR-CVD 顯示極佳的氧化層厚度控制能力,足以解 決未來極大型積體電路(ULSI)元件,超薄 氧化層的厚度越來越薄 1~3 nm, 導致均勻 度不易控制的問題。而且再經過氮化處理 過後的 ECR-CVD №0 plasma oxynitride 超薄氧化層,具備低缺陷密度與 Si≡N 強 鍵結的特性,使得PMOS 元件擁有 0.1A/cm<sup>2</sup> 極低的漏電流以及高達 4x103 C/cm2的 QBD 高可靠度特性,並擁有接近理想熱成長氧 化層的 C-V 特性曲線。除此之外,經過氮 化處理機制可以有效的修補超薄氧化層中 的斷鍵,並且形成很強的 Si≡N 鍵結,因 此 ECR-CVD 成長的超薄氧化層還有極佳的 抵擋硼穿透氧化層能力,因此 ECR-CVD 成 長的超薄氧化層將可大量應用於製作未來 深次微米 ULSI 元件之閘極超薄氧化層。

## 六、計劃成果自評

本研究內容已經完成國科會計劃第三 年度規劃進度,提供更完善的低溫低壓 ECR-CVD 超薄氧化層之最佳成長條件、分 析及測試研究,並對其抵抗硼穿透氧化層 的能力進行完整的分析,並已提出 ECR-CVD 超薄氧化層防止硼穿透技術專 利申請,證明 ECR-CVD 超薄氧化層確實 可應用於極大型積體電路(ULSI)元件之閘 極超薄氧化層。另外我們使用 ECR-CVD in-situ 氮化處理,將 ECR-CVD 成長之超薄 氧化層做氮化處理,結果顯示大量的高活 性 N-radical 將可修補超薄氧化層中的斷鍵 或填補空位,讓超薄氧化層的缺陷密度大 幅下降,有效的修補 fixed oxide charge (Q<sub>f</sub>) 和 oxide trapped charge (Q<sub>ot</sub>), 使 得超薄氧化層有接近理想氧化層的薄膜特 性,由此我們也得出 N2-plmasa 氮化處理最 佳條件為3分鐘,將可以大幅改善ECR-CVD N<sub>2</sub>O plasma 成長的超薄氧化層的電特性, 並應用於對於未來低溫深次微米 ULSI 元件 之閘極超薄氧化層製程技術的開發,可見 ECR-CVD 系統在未來先進製程技術中佔 據舉足輕重的關鍵技術與實用價值。

### 七、參考文獻

- [1] P. A. Kraus, K. Ahmed, T. C. Chua, M. Ershov, H. Karbasi, C. S. Olsen, F. Nouri, J. Holland, R. Zhao, G. Miner and A. Lepert, "Low-energy nitrogen plasmas for 65-nm node oxynitride gate dielectrics a correlation of plasma characteristics and device parameters," *Symp. VLSI Tech.*, pp. 143-144, 2003.

- [2] S. Inaba, T. Shimizu, S. Mori, K. Sekine, K. Saki, H. Suto, H. Fukui, M. Nagamine, M. Fujiwara, T. Yamamoto, M. Takayanagi, I. Mizushima, K. Okano, S. Matsuda, H. Oyamatsu, Y. Tsunashima, S. Yamada, Y. Toyoshima and H. Ishiuchi, "Device performance of sub-50 nm CMOS with ultra-thin plasma nitrided gate dielectrics," *IEDM Tech. Dig.*, pp. 651-654, 2002.

- [3] Jung-Yeal Lee, Chul-Hi Han, and Choong-Ki Kim, "ECR plasma oxidation effects on performance and stability of polysilicon thin film transistors," *IEDM Tech. Dig.*, 1994.

- [4] Chuan H. Liu, Hsiu-Shan Lin, Yu-Yin Lin, "Extending the reliability scaling limit of gate dielectrics through remote plasma nitridation of N<sub>2</sub>O-grown oxides and NO RTA treatment," *IEEE 40th Annual International Reliability Physics Symposium*, 2002.

- [5] Sangyeon Han and Hyungcheol Shin, "Ultrathin Oxide Grown on Polysilicon by ECR (Electron Cyclotron Resonance) N<sub>2</sub>O Plasma," *International Symposium on Plasma Process-Induced Damage*, 5<sup>th</sup>, May 2000.

- T. Yamamoto, T. Ezaki, K. Watanabe, M. Togo, A. Morioka, M. Hane, T. Tatsumi and T. Mogami, "Improved TDDB reliability of 1.5 nm thick gate dielectrics grown by radical oxynitridation," *International Workshop on Gate Insulator*, IWGI, pp. 220-223, 1-2 Nov. 2001.