# 行政院國家科學委員會專題研究計畫 期中進度報告

## 總計劃(1/3)

計畫類別: 整合型計畫

計畫編號: NSC91-2215-E-009-072-

執行期間: 91年08月01日至92年07月31日

執行單位: 國立交通大學電子工程學系

計畫主持人: 吳介琮

共同主持人: 荊鳳德, 柯明道, 吳重雨, 吳錦川

報告類型: 精簡報告

處理方式:本計畫可公開查詢

中 華 民 國 92 年 5 月 28 日

### 高性能混合訊號式介面積體電路

### **High-Performance Mixed-Signal Interface ICs**

計畫編號 : NSC-91-2215-E-009-072

**執行期限** : 自 91 年 8 月 1 日起至 92 年 7 月 31 日止

主持人 : 吳介琮 交通大學電子研究所

共同主持人 : 荆鳳德、柯明道、吳重雨、吳錦川 交通大學電子研究所

Email: jtwu@mail.nctu.edu.tw http://www.cc.nctu.edu.tw/~jtwu

#### 一、摘要

本計畫以整合資源方式,配合政府政策,因應產業需求,研發類比數位混合訊號式積體電路之設計技術。本計畫共分成六個子計畫。分別是(1)矽射頻元件模型與技術;(2)射頻電路之靜電放電防護技術與高速高低壓界面電路之研發;(3)5 GHz 高性能無線通訊系統中主要積體電路的設計與整合;(4)高性能類比數位介面積體電路;(5)低電壓差動信號傳輸接收器之設計與量測;(6)光纖傳輸之類比前端積體電路。子計畫一將建立主動與被動元件之射頻模型供電路設計與模擬。子計畫二則在設計晶片與電路板之間的可靠介面。計畫三將研究射頻無線電波與類比訊號之介面電路。計畫四將研究類比與數位訊號之介面電路。計畫五將研究數位與數位訊號之晶片介面電路。計畫六將研究光纖傳輸中光與數位訊號之介面電路。本計畫所研發的成果將會是積體電路設計之核心技術,有助於國內積體電路產業升級,尤其是無線及光纖通訊方面。而所訓練的設計人才也是國內目前迫切需求的。

關鍵詞:混合訊號式積體電路、介面、CMOS。

#### **Abstract**

This project combines the resources of several researchers to investigate the mixed-signal integrated circuit design techniques, so as to promote the government policy and satisfy the industry's need. There are 6 projects in this combined effort: (1) Si RF Device Modeling and Technology; (2) Development of On-Chip ESD Protection Technique for GHz RF Circuits and High-Speed Mixed-Voltage Interface Circuits; (3) The Design and Integration of Key Component ICs for 5 GHz High Performance Wireless Communication System; (4) High-Performance Analog-Digital Interface Integrated Circuits; (5) The Design and Testing of High Performance LVDS Transceiver; and (6) Analog Front-End Integrated Circuits for Optical-Fiber Transmission. Project 1 will build the high-frequency models for active and passive

components suitable for circuit design and simulation. Project 2 investigates the reliable interfaces between chips and circuit boards. Project 3 investigates the interface circuits between wireless electro-magnetic waves and the analog domain. Project 4 investigates the interface circuits between the analog and the digital domains. Project 5 investigates the chip-to-chip digital interfaces. Project 6 investigates the interfaces between the optical-fiber light signals and the digital domain. The topics are all fundamental technologies for the design of high-performance integrated circuits, especially for wireless and optical fiber communications. In addition, the participated personnel will be trained to satisfy the need of the IC design industry.

Key Words: Mixed-Signal Integrated Circuits, Interfaces, CMOS.

#### 二、緣由與目的

本整合型研究計畫係依據工程處微電子學門 VLSI/CAD 推動小組提出的「類比、混合訊號及 RF 模組設計」規畫書中的「子系統設計研究」項目規畫而成。計畫的主題為高性能之混合訊號介面積體電路。此處所謂的介面包括通訊傳輸媒介(如無線、光纖等)與積體電路之間的介面,類比與數位積體電路之間的介面,數位與數位積體電路之間的介面,以及積體電路與周遭環境之間的介面。這些介面電路都需要使用混合訊號式積體電路設計技術。而本計畫就是研究其中的基本卻又先進的設計技術。而其成果將是支援無線通訊與光纖通訊之核心技術。

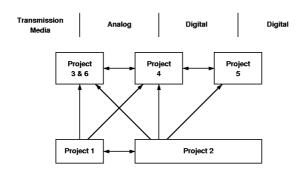

Fig. 1. 子計畫關係圖。

本計畫分成六個子計畫。分別是(1) 矽射頻元件模型與技術;(2) 射頻電路之靜電放電防護技術與高速高低壓界面電路之研發;(3) 5 GHz 高性能無線通訊系統中主要積體電路的設計與整合;(4) 高性能類比數位介面積體電路;(5) 低電壓差動信號傳輸接收器之設計與量測;(6) 光纖傳輸之類比前端積體電路。圖 12.1 顯示了子計畫之間的相互關係。子計畫一將建立 MOSFET 之射頻模型供子計畫三與六使用。子計畫二則在設計晶片與電路板之間的介面供子計畫三至六使用。計畫三將研究射頻無線電波與類比訊號之介面電路。計畫四將研究類比與數位訊號之介面電路。計畫五將研究數位與數位訊號之晶片介面電路。計畫六將研究光纖傳輸中光與數位訊號之介面電路。計畫整合的最主要目的是設

#### 備與人力資源之整合。

本計畫其中之四位主持人所共同組成之研究群共用一間實驗室,所有學生之座位及實驗設備(如工作站和量測儀器)均共同使用。即使是個別計畫申請到的儀器設備也是如此,真正做到資源共享避免機器閒置之浪費。本計畫之子計畫所使用的設備都有共通性。如子計畫1,2,3,6可使用相同的射頻量測儀器。而子計畫2,4,5則會使用相同的訊號源、示波器、與邏輯分析儀。

本計畫研究群學生的座位都在相鄰地方,學術研究會因為在一起而容易相互交流。子計畫雖各有不同的主題,但基本技能卻是共通的。例如子計畫 1,2,3,6 對於射頻元件都必須深入了解,而且也都會使用到同樣的射頻量測技術。子計畫 2,3,4,6 都須考慮到低雜訊電路的設計方法。而子計畫 4,5 會特別重視時序訊號的抖動。也因為這些共通性,更增加了彼此交流與經驗傳承的誘因。

#### 三、執行成果

### A. 子計畫一:矽射頻元件模型與技術

Multi-fingered layout of 0.18  $\mu$ m MOSFETs are used in this study. To achieve a low gate resistance, a silicide gate technology is applied. The finger width is 5 $\mu$ m and the finger number is ranged from 20 to 70 at an increment of 10. The multi-fingered structure with a small finger width enables us to reduce both the DC silicide gate resistance and the RF non-quasi-static gate resistance. The devices are first characterized by DC I-V and reliability test. Then standard 2-port S-parameters are measured using HP8510B network analyzer and on-wafer probes and de-embedded from the probe pad. The NF<sub>min</sub> and associate gain are measured using standard ATN-NP5B Noise Parameter Extraction System up to 7.2 GHz that covers the most important frequency range for wireless communication. Numerical simulation was performed by using an equivalent circuit model of intrinsic MOSFET with additional terminal resistance and shunt pass to ground at both input and output ports. To avoid non-physically based data in the equivalent circuit model, DC and low frequency data are measured and referred in circuit model.

Strong dependence of finger number on minimum noise figure (NF<sub>min</sub>) is observed in  $0.18\mu m$  MOSFETs. A lowest NF<sub>min</sub> of 0.93 dB is measured at 5.8 GHz using 50 fingers but increases as either increasing or decreasing finger number. We have used a self-consistent S-parameter and NF<sub>min</sub> model to analysis this abnormal finger number dependence, and the reason is due to the combined effect of reducing gate resistance and increasing substrate loss as increasing finger number.

The noise in the MOSFET is dominated by gate input terminal before amplified to drain output terminal. However, the influence of drain terminal becomes important at large gate fingers because of the increasing reverse feedback. Therefore, the thermal noise from gate resistance (Rg) is the primary noise source in the

MOSFET. This also explains the reduced  $NF_{min}$  as increasing gate fingers less than 50. The reason why increasing  $NF_{min}$  as increasing gate fingers above 50 is due to the increasing shunt substrate loss to ground as evidenced from the decreasing Rg-sub and increasing Cg-sub. From above discussion, further scaling down the gate length beyond  $0.18\mu m$  will be probably unable to further reduce the RF noise, because of the increasing Rg by a smaller gate area, the existing same shunt substrate loss, and the increasing reverse feedback from output terminal (short channel effect).

#### B. 子計畫二:射頻電路之靜電放電防護技術與高速高低壓界面電路之研發

本計畫的研究成果已經整理且發表了五篇 IEEE Conference 論文以及一篇 IEEE 國際期刊論文。研究的內容有應用於射頻電路的 ESD 保護電路、新型的高速高低壓界面電路和一般輸入/輸出端所使用的 ESD 保護電路。

在射頻電路的 ESD 保護電路研究中,我們首先比較了 STI 二極體及poly-gated 二極體對射頻電路特性的影響,發現poly-gated 二極體可以在相同的ESD 耐受度下,對射頻電路的功率增益 (power gain, S21) 造成較小的損耗(約-0.51 dB)。因此 poly-gated 二極體比 STI 二極體更適合做為射頻電路的 ESD 保護電路。另外,我們也成功地設計了一組可供 CMOS 射頻電路所使用的 ESD 保護電路,此保護電路主要是在輸入端的 ESD 保護電路路徑上加上一組 LC tank,此 LC tank 在共振頻率下會產生一無限大的阻抗而阻絕 ESD 保護電路的寄生電容效應對射頻電路所產生的負面影響。在靜電放電發生的情況下,又能很快地透過電感、二極體和電源線間的 ESD 保護電路將靜電排放掉。

在高速高低壓界面電路中,我們提出了一組不需要使用厚的閘氧化層就可以避免薄閘氧化層在高低壓界面電路所面臨的可靠度問題,而且所設計的閘極電壓追蹤電路 (gate-tracking circuit) 和動態 n 型井偏壓電路 (dynamic n-well bias circuit) 其所使用的電晶體數目也比之前文獻發表的電路來的少。

此外,我們也提出了幾種一般輸入/輸出端所使用的 ESD 保護電路,其中包含了利用互補式基體觸發矽控整流器 (complementary substrate-trigger SCR) 和 MOS-bounded 二極體做為 ESD 保護元件的保護電路。

#### C. 子計畫三: 5 GHz 高性能無線通訊系統中主要積體電路的設計與整合

此計劃主要是以 0.18 ~ 0.13μm 場效金氧半電晶體的製程來實現 IEEE 802.11a 的 5-GHz 高頻段無線射頻金氧半電晶體收發機元件。預計完成的電路元件包括低雜訊放大器、混波器、多相位中頻濾波器、自動增益控制器、類比至數位資料轉換器、電壓控制振盪器、功率放大器。

在 IEEE 802.11a WLAN 中,系統採用 OFDM 的調變方法,每個 Channel 頻 寬為 20MHz;而每一個 Channel 則有 52 個 sub-carrier,並且相互正交;每個 sub-carrier 頻寬約為 325KHz。最大接收訊號的功率為-30dBm,而輸出功率則根據頻段不同有不同的要求,分別為 40mW, 200mW, 800mW。理論上,最高傳輸速率可以達到每秒 54Mbits。OFDM 根據使用者不同傳輸速率的需求而採用不同

的調變方法,規格制訂者建議能達到 10dB 的 NF 以達到所有需求,而在線性的要求上,接收機的 1dB Compression point (CP1dB)需達到-26dBm (最大接收訊號功率減 4dB)。在傳送機的設計上,在達到所需的輸出功率下,訊號的頻譜需在規格中所設定的 MASK 之內,以避免對其他頻段產生干擾並避免訊號失真。

為了提供高整合性、避免 DC-Offset、flicker noise、multi-path mismatch 的影響以提高接收機性能,本計畫採用了雙正交接收機架構。此架構藉由將輸入及 LO 訊號都轉為正交形式,可以對 Multi-Path 電路製程上無法完全匹配的缺點有較大的容忍力,並降低了鏡像訊號的干擾。各子電路的功能及設計考量如下:

低雜訊放大器:此電路操作在 5-GHz,目的在降低後級電路對雜訊的影響,對整個系統的靈敏度有決定性的影響,所以需提供足夠的增益以及低的雜音指數。

混波器:將射頻訊號與本地震盪訊號相乘,使訊號頻率降至中頻或基頻,混波器需有足夠的線性度已提高動態區間(dynamic range)。

多相位中頻濾波器:具有消除鏡像訊號的功能,需要好的線性特性以及足夠 的頻寬。

電壓控制振盪器:產生本地震盪訊號供給混波器做移頻,所產生的訊號頻率 變動範圍需涵括整個頻段,相位雜訊雜訊要低。

功率放大器:將射頻訊號放大再由天線發射出去,需有足夠的輸出功率,以 及好的效能,如線性度、功率效益。

#### D. 子計畫四:高性能類比數位介面積體電路

本計畫將以 Time-Interleaved 架構設計 ADC。而此架構的主要問題包括取樣時間誤差以及子系統不匹配等。本計畫將繼續探討這些問題,並提出解決方案。

本計畫已成功設計出一個高性能的取樣電路(SHA)。此電路利用 Time-Interleaved 架構的操作特性配合創新電路,可以簡化運算放大器之設計, 進而降低功率消耗。以  $0.25~\rm um~CMOS$  製程製作出之晶片,其電路面積為  $0.35~\rm mm^2$ 。在  $2.5~\rm V$  的工作電壓下,其功率消耗僅有  $33~\rm mW$ 。此 SHA 能在  $100~\rm MHz$  之取樣頻率且  $2.7~\rm Vpp$  的輸出電壓時仍有超過  $72~\rm dB~SFDR~$ 之動態範圍。在  $1.8~\rm Vpp$  的輸出電壓時,則有  $80~\rm dB~SFDR~$ 的動態範圍。

本計畫在 Pipelined ADC 設計方面有突破性的成果。所提出的 Digital Background Calibration 技術可以解決困擾多年之 Calibration 需停止正常 A/D 轉換的問題。此技術將用於實際 ADC 的設計中以達成本計畫所訂定的 14-Bit 解析度。本技術已申請專利。

#### E. 子計畫五:低電壓差動信號傳輸接收器之設計與量測

本計畫主要於設計二種型式適用於串列式連接傳輸之傳送與接收器。此二個電路在傳送器和接收器中各採用不同的架構。傳送器部份二者使用不同方式來降低符號之間干擾以增加傳送頻寬,接收器部份則採用 3 倍超取樣方式和時脈資料回復這二種架構來完成.其傳輸頻率分別為 400 和 480Mbps,採用 TSMC 0.35um

1P4M 和 2P3M CMOS 設計完成。

在以 400Mpbs 為傳輸頻率的架構中,我們設計了一個可應用在高速串列傳輸介面的 3X Oversampling 接收器,在鎖相迴路上是正常工作的,但是在接收器部份則是因為在架構上的因素,造成會有 Missing code 的產生。因此,解決方法就是在 Phase selector 的輸入訊號要把十二個相位全部放入輸入端去選擇。這也是我們下次設計可以改進的地方。而傳輸器部份晶片還正在進行中。

在以 480Mpbs 為傳輸頻率的架構中,目前完成了傳送器方面的設計與量測 而接收器的部分還在製作中。

#### 四、發表論文(部分)

- [1] C. H. Huang, K. T. Chan, C. Y. Chen, A. Chin, G. W. Huang, C. Tseng, V. Liang, and J. K. Chen, "The minimum noise figure and mechanism as scaling RF MOSFETs from 0.18 to 0.13 um technology nodes," IEEE RF-IC International Microwave Symposium (RFIC), June 2003.

- [2] Ming-Dou Ker, C.-I. Chou, and C.-M. Lee, "A novel LC-tank ESD protection design for giga-Hz RF circuits," accepted by 2003 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, Philadelphia, Pennsylvania, USA, June 8-10, 2003.

- [3] Ming-Dou Ker and K.-C. Hsu, "Substrate- triggered SCR device for on-chip ESD protection in fully silicided sub-quarter-micron CMOS process," IEEE Trans. on Electron Devices, vol. 50, no.2, pp. 397-405, Feb. 2003.

- [4] Ming-Dou Ker, K.-H. Lin, and C.-H. Chuang, "MOS-bounded diodes for on-chip ESD protection in a 0.15-μm shallow-trench-isolation salicided CMOS process," accepted by 2003 International Symposium on VLSI Technology, Systems, and Applications (VLSI\_TSA), Taiwan, April 23-25, 2003.

- [5] Chung-Yu Wu and Chun-Yun Chou, "A 5-GHz CMOS Double-Quadrature Receiver for IEEE 802.11a Applications," Accepted by 2003 Symposium on VLSI Circuits.

- [6] C.-C. Hsu and J.-T. Wu, "A CMOS 33-mW 100-MHz 80-dB SFDR sample-and-hold amplifier," 2003 Symposium on VLSI Circuit Digest of Technical Papers, 2003.

- [7] H.-C. Liu, Z.-M. Lee, and J.-T. Wu, "A digital background calibration technique for pipelined analog-to-digital converters," 2003 IEEE International Symposium on Circuits and Systems Digest of Technical Papers, 2003.