# 行政院國家科學委員會專題研究計畫 期中進度報告

## 子計畫一--無鉛鋅錫的電遷移研究(1/2)

計畫類別：整合型計畫

計畫編號：NSC91-2216-E-009-032-

執行期間：91年08月01日至92年07月31日

執行單位：國立交通大學材料科學與工程學系

計畫主持人：陳智

報告類型：精簡報告

報告附件：國際合作計畫研究心得報告

處理方式：本計畫可公開查詢

中華民國92年6月2日

## 近五年內主要研究成果

職於 2000 八月到交大材料系任教至今兩年多，已經將實驗室建立及研究生訓練完成，現在研究已經上軌道。並且開始有研究成果發表在國際期刊及國際知名的會議中，以下將近五年內發表的論文列出以供參考：

### (A) 期刊論文

1. “The Preparation of Twist-type Bicrystals of Silicon”, Chih Chen, G.Z. Pan, and K.N. Tu, Materials Chemistry and Physics, **47**, 90 (1997).

2. “Twist-type Si Bicrystals and Compliant Substrates Prepared from Silicon-On-Insulator Wafers”, Chih Chen, K.N. Tu, C. H. Tung, T.T. Sheng, A. Ploessl, R. Scholz, and U. Gösele, Phil. Mag., **80**, 881 (2000).

3. “Dopant Activation of Heavily-doped Silicon-On-Insulator by High Density Currents” Chih Chen, J.S. Huang, C.N. Liao, and K.N. Tu, J. Appl. Phys., **86**, 1552 (1999).

4. “Direct Correlation Between Mechanical Failure and Metallurgical Reaction in Flip Chip Solder Joints”, C.Y. Liu, Chih Chen, and K. N. Tu, J. Appl. Phys., **85**, 3882 (1999).

5. “Two- and Three-dimensional arrays of magnetic microspheres”, W. Wen, D. W. Zheng, C. Chen, and K. N. Tu, J. Mater. Res., Vol. **14**, No. 4, Apr 1999.

6. “Microstructure-Electromigration correlation in a Thin Strips of Eutectic SnPb Solder Stressed between Cu Electrodes”, C. Y. Liu, Chih Chen, C. N. Liao, and K. N. Tu, Appl. Phys. Lett., **75**, 58 (1999).

7. “Thermoelectric Characterization of Si Thin Films in SOI Wafers, C. N. Liao, C. Chen and K. N. Tu., Journal of Applied Physics, **86**, 3204 (1999).

8. “Asymmetrical Heating Behavior of Doped Si Channels in Bulk Silicon and in Silicon-On-Insulator under High Current Stress.” C. N. Liao, C. Chen, J. S. Huang and K. N. Tu, J. Appl. Phys. **86**, 6895 (1999).

9. “Novel Compliant Substrate for Low Density Relaxed SiGe Growth” Y. H. Luo, J. L. Liu, G. Jin, K. L. Wang, C. D. Moore, Goorsky, C. Chih, K. N. Tu, J. of Electronic Materials, **29**, 950 (2000).

10. "Effect of current crowding on vacancy diffusion and void formation in electromigration", K. N. Tu, C. C. Yeh, C. Y. Liu, and Chih Chen, *Appl. Phys. Lett.*, **76**, 988 (2000).

11. "Electromigration in Sn-Pb solder strips as a function of alloy Composition" C. Y. Liu, C. Chen, and K. N. Tu, *J. Appl. Phys.*, **88**, 5703 (2000).

12. "Electromigration in Eutectic SnPb Solder Lines", Q. T. Huynh, C. Y. Liu, Chih Chen, and K. N. Tu, *J. Appl. Phys.*, **89**, 4332 (2001).

13. Effect of current crowding on contact failure in heavily doped n<sup>+</sup>/p<sup>+</sup>-silicon-on-insulator" Huang JS, Chen C, Yeh CC, Tu KN, Shofner TL, Drown JL, Irwin RB, Vartuli CB., *J. of Materials Research*, 15, 2387(2000).

14. " Enhanced dopant activation and elimination of end-of-range defects in BF<sub>2</sub>-implanted silicon-on-insulator by high-density current " H. H. Lin, S. L. Cheng, and L. J. Chen, ,Chih Chen, K. N. Tu, *Appl. Phys. Lett.* **79**, 3971 (2001).

15. "Stress relaxation of a patterned microstructure on a diaphragm", D.W. Zheng, X.H. Wang, K. Shyu, C. Chen, C-T. Chang, K.N. Tu, A.K. Mal, and Y.F. Guo, *J. Mater. Res.*, 1795, Vol. 17, No. 7, (2002).

16. "Tin Whisker Growth Driven by Electrical Currents" S. H. Liu and Chih Chen, submitted to *Journal of Applied Physics*.

17. "Electromigration Studies of Sn95/Sb5 Flip Chip Solder Bumps", T. L. Shao, K.C. Lin, and Chih Chen, accepted by *J. of Electronic Materials*, May, 2003.

18. "Electromigration Study in SnAg3.8Cu0.7 Solder Joints on Ti/Cr-Cu/Cu Under Bump Metallization", Ying-Chao Hsu, Tung-Liang Shao, Ching-Jung Yang, and Chih Chen, accepted by *J. of Electronic Materials*, May, 2003.

## (b)研討會論文

1. "Residual Stress in C54 Titanium Silicide Formed on Silicon-On-Insulator", Chih Chen, T. Wetteroth, S.R. Wilson, and K.N. Tu, *Proceedings of the Seventh International Symposium on Silicon-On-Insulator Technology and Devices*, Electrochem. Soc, 1996.

2. S. H. Liu, C. Chen "Tin Whisker Growth Driven by Electrical Currents"

TMS Fall Meeting,

2002.

3. 邵棟樑, 陳智 "Electromigration Studies of Sn95/Sb5 Flip Chip Solder Bumps" 2002 年中華民國材料科學年會.

4. 周重光, 黃子瑜, 陳智 "共晶錫鉛銻錫之氣密式封裝之技術研究" 2002 年中華民國材料科學年會.

5. 賴璟亮, 陳智 "Occurrence of Electromigration at High-Pb/Eutectic Solder Interface" 2002 年中華民國材料科學年會.

6. Y. C. Hsu, T. L. Shao, C. Chen "Electromigration Induced Failure in SnAg3.8Cu0.7 Solder Joints for Flip Chip Technology" EMPA, 2002.

7. I. H. Chen, T. L. Shao and Chih Chen "Electromigration in Sn96.5/Ag3.5 Flip Chip Solder Bumps. TMS Annual Meeting, 2003.

8. K. C. Lin, T. L. Shao, C. Chen "Electromigration in SnAg3.8Cu0.7 Solder Lines" TMS Annual Meeting, 2003.

9. T. L. Shao, Chih Chen "Electromigration of Sn95/Sb5 Flip Chip Solder Bumps on Cr/Cr-Cu/Cu Under Bump Metallization" TMS Annual Meeting, 2003.

10. Y. C. Hsu, T. L. Shao, Chen "Electromigration in SnAg3.8Cu0.7 Solder Joints for Flip Chip Technology" TMS Annual Meeting, 2003.

## 摘要

本研究主要針對無鉛鋅錫，SnAg3.5，SnAg3.5Cu0.7 與 SnSb 之覆晶結構在高電流密度下進行電遷移現像研究。所使用之 UBM 為 Cr/Cr-Cu/Cu(晶片端)與 Cu/Ni(P)/Au(基板端)。研究顯示 SnAg3.5 覆晶結構之毀壞主要發生於陽極處，SnAg3.5Cu0.7 與 SnSb 覆晶結構方面毀壞主要發生於陰極處，而造成覆晶結構之毀壞之主因為介金屬化合物聚集所產生之應力造成破壞，以及電流聚集效應引起。

## 實驗步驟

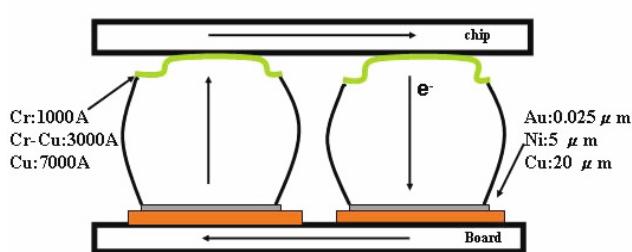

圖一為本研究之覆晶試片結構圖，晶片端之 UBM 分別為 Cr, phase-in Cr-Cu，與 Cu，其厚度分別為 1000 Å, 3000 Å 與 7000 Å。基板端之 UBM 分別為 Cu: 20 μm, Ni: 5 μm, Au: 0.25 μm。

圖一、覆晶試片結構圖。

鋅錫則在高於其熔點 30 度下首先與晶片端接合(reflow)，接著再與基板端對準進行第二次接合(reflow)。

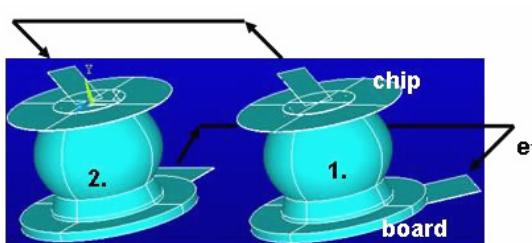

圖二為本研究之試片 3D 結構圖，電子流從二號 bump 之晶片端 45° 角進入，再由基板端之後方流出，接著由一號 bump 晶片端 45° 角進入，再由基板端後方 45° 角流出。

圖二、試片 3D 結構圖。

研究中施加高電流密度  $2 \times 10^4$  A/cm<sup>2</sup>,  $1 \times 10^4$  A/cm<sup>2</sup> 與高溫 100°C, 150 °C 下對鋅錫覆晶結構進行電遷移研究。

## 結果與討論

### SnSb5 鋅錫球之電遷移

考慮 solder bumps 在實際使用的過程中，並不是將整個 bump 切開來再加熱通電的。為此，我們將整個 flip chip 放置在加熱板上加熱並通電，等到試片變成斷路後再加以分析它的破壞模式。加熱版的溫度為 150°C；電流密度為  $1 \times 10^4$  A/

$\text{cm}^2$ 。

因為 solder bumps 在通電的過程中，整個 bump 被 underfill 完全包圍著，使得在加熱通電的過程中，高電流密度所造成 Joule heating 及加熱版所加諸的熱無法有效的排出，因此整個 solder bumps 在實驗中所處的溫度應高於加熱版的環境溫度。也因此要將此種試片通電到壞所需的時間比先前所做的將 solder bumps 切面後再通電所需的時間來的短。

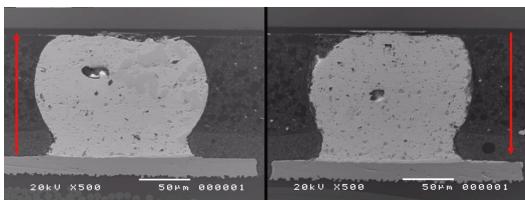

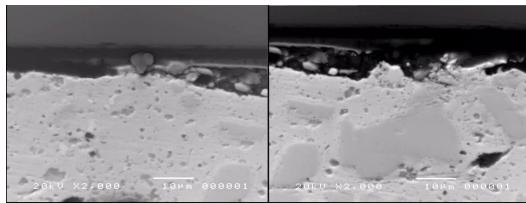

圖三、通電到壞掉後的 solder bumps 的 cross sectioned 圖，紅色箭頭微電子流的走向。

由圖三可發現兩個 bump 的 chip side 皆有損壞，但是損壞的原因卻不相同，在陰極的 chip side 即圖一右，陰極遭到高密度電子流的沖刷，而產生破壞。

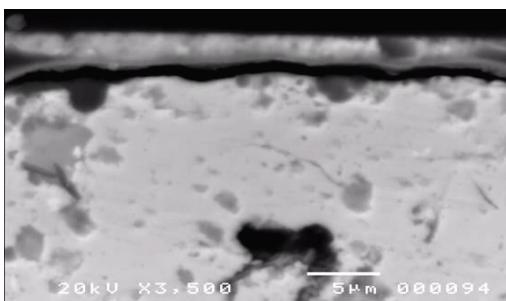

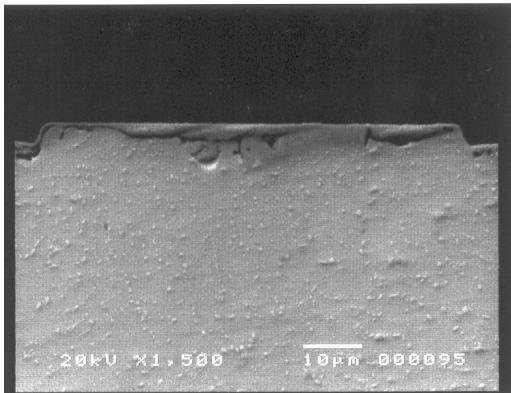

圖四、陰極 chip side 的放大圖。

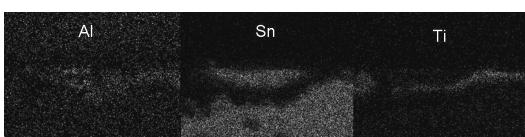

圖五、EDS mapping 圖。

圖四中可看到 solder 與 UBM 層已經分開了。從圖五中 Al 已經跑到了 Sn 下面，而 Sn 也向上跑到了 UBM 層的上方，強大的電子流將 Al 線衝進了銻錫之中。

在陽極的 chip side 這邊，可以由圖六中發現，有許多的 IMCs 在陽極附近，且裂縫是在 UBM 和 solder 之間出現的，所以裂縫的形成應該是因為 IMCs 的生成，而使得陽極介面變脆，在應力集中的情況下，裂縫便在 UBM 和 solder 之間生成。

圖六、陽極 chip side 的放大圖，圖中之 IMCs 為 $(\text{Ni}, \text{Cu})_3\text{Sn}_4$ 。

圖七是另一組在相同條件下通電的試片，發現陽極 chip side 並不一定會有裂縫的產生，但是陰極 chip side 都會有裂縫生成，可知此 flip chip 的 electromigration 損壞只要是因為在陰極 chip side 的破壞。

圖七、另一組 flip chip 試片，僅在陰極 chip side 有損壞。

### SnAg3.5Cu0.8 錫錫球之電遷移

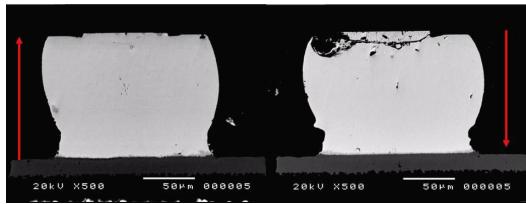

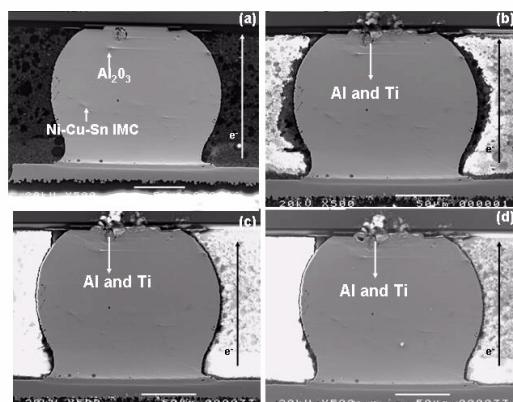

SnAgCu 錫錫球之電遷移方面主要分為兩部份進行。第一部份為將覆晶錫錠球試片表面進行拋光研磨，接著施加 0.085 安培之電流，使錫錠球在晶片端之電流密度為  $2 \times 10^4 \text{ A/cm}^2$ ，溫度為  $100^\circ\text{C}$  下進行電遷移測試，圖八與圖九為錫錠球在不同時間下(a)0hrs，(b)20hrs，(c)264hr，(d)408hrs，之測試結果，圖一之電子流方向是從晶片端流向基板，圖二則為基板流向晶片端。

圖九、錫錠球在不同時間下(a)0hrs，(b)20hrs，(c)264hr，(d)408hrs，之測試結果，電子流方向是從基板流向晶片端。

圖八、錫錠球在不同時間下(a)0hrs，(b)20hrs，(c)264hr，(d)408hrs，之測試結果，電子流方向是從晶片端流向基板。

從圖八中可發現試片在破壞前並無明顯之變化，但在 408hrs 時試片形成斷路

且破壞在晶片端之，由於破壞表面相當平整且出現一些小粒鉛錫球，故推測試片在破壞時已高達鉛錫之熔點，此乃因電子流是從晶片端之左後方進入，因此電流聚集效應所造成晶片端局部溫度升高造成破壞。而圖九中之鉛錫球並無明顯之破壞，只有在晶片端因電子流之關係將鋁與 UBM 中之鈦推擠出來，推測此與基板端之 UBM 大於晶片端，故電流密度小於  $2 \times 10^4 \text{ A/cm}^2$  以致基板端並無明顯之破壞。

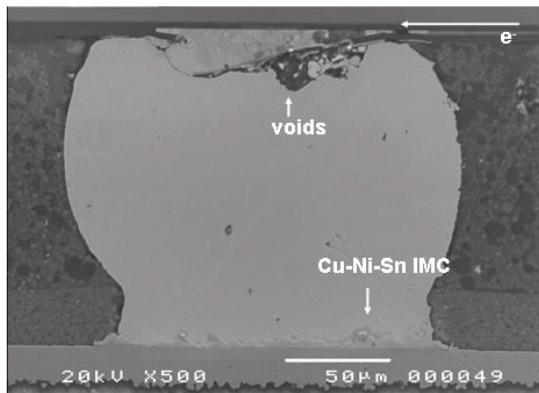

第二部份為將覆晶鉛錫球試片施加 0.567 安培之電流，使鉛錫球在晶片端之電流密度為  $1 \times 10^4 \text{ A/cm}^2$ ，溫度為  $150^\circ\text{C}$  下進行電遷移測試，待試片形成斷路後將試片表面進行拋光研磨進行觀察。

圖十、鉛錫球在 42 小時後發生毀壞之電子顯微鏡影像圖。

圖十為鉛錫球在電遷移測試後之電子顯微鏡影像圖。鉛錫球在 42 小時後發生毀壞。圖中顯示右方之孔洞大於左方，此乃因右方為電子流進入之處在電子流進入之處易造成電流聚集效應而造成更大之破壞。除此之外在右方生成之介金屬化合物厚度也大於左方，此乃因大部份之電子流會往右下方移動，造成 UBM 與鉛料中 Cu 原子隨電子流往右流動形成較厚之 Cu-Ni-Sn 金屬化合物。

### SnAg3.5 鉛錫之電遷移

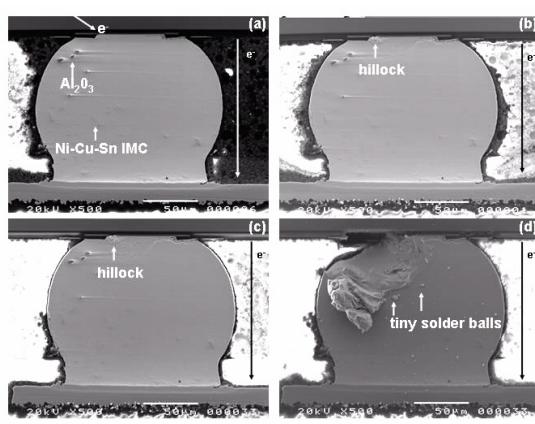

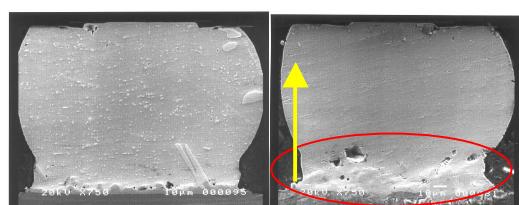

為了明白 SnAg3.5 焊料在高電流密度下電遷移的效應，我們選擇先用高電流密度的電流( $1 \times 10^4 \text{ ampere/cm}^2$ )將 SnAg<sub>3.5</sub> 焊料的覆晶錫球通到斷路，使覆晶錫球失效，為了加速試片失效的時間，試片是在  $150^\circ\text{C}$  的溫度下通電。之後研磨試片的橫截面，使用電子顯微鏡觀察 SnAg<sub>3.5</sub> 焊料的覆晶錫球失效的原因。結果如下圖。

圖八、對照組。

圖九、Chip side 陽極。

圖十、Chip side 陰極。 圖十一、圖十 Board si 之放大圖。

圖八是對照組的錫球，同樣在 150°C 下加熱，不過未施加任何電流，可以用来比較通電的效應。圖九和圖十有通電不過電子流(黃色箭頭)的極性相反，由紅色圈圈可以看到在 board 位置有大量的 IMC(界金屬化合物)生成。經由電子顯微鏡附加的 EDS 成分分析功能得知該 IMC 為 $(Ni,Cu)_3Sn_4$ 。由於 board 位置是由 Ni 和 SnAg<sub>3.5</sub> 焊料反應產生潤濕和接著的效果。然而在電遷移的效應下，大量的 Ni 被電子流帶到焊料之中形成大量的 IMC 會對焊料本身造成負面的影響。因為 IMC 比較脆，會降低焊料的機械強度。而且 IMC 在成長時會因為體積的變化產生多餘的應力。根據我們的實驗觀察，焊料球會失效也和這個應力有關。

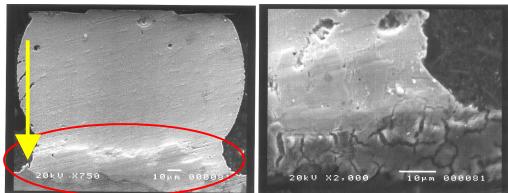

圖十二、Chip side 放大圖。

圖十二是圖九 Chip 位置焊料球接鋁導線的開口處。由 BEI 照片中可看到焊料中深色的部分就是 IMC。而且 IMC 大多集中在裂縫附近，可見應該是 IMC 成長產生的應力促使裂縫成長加速電遷移下焊料球的失效。

綜合以上的發現，我們知道 IMC 對覆晶結構的焊料球的失效有很大的影響。所以 IMC 的型態和形成的機制的研究有很大的重要性。從我們的研究中發現到高的電流密度是可以促使 IMC 的成長。因為根據我們 EDS 資料發現 Chip 位置的 IMC 主要的成分 Ni 是由電子流從 board 位置把 Ni 帶到 Chip 位置來所形成的。在未通電的對照組焊料球是看不到這種 IMC 的形成。最後我們可以知道電遷移對焊料球的可靠度有著很大的影響。

## 結論

SnAg3.5Cu 與 SnSb 之研究顯示，毀壞主要發生於陰極處，而造成覆晶結構之毀壞之主因為電流聚集效應引起。SnAg3.5 方面之研究顯示，毀壞主要發生於陽極處而造成覆晶結構之毀壞之主因為 Ni 原子在電子流推擠下聚集於陽極形成介金屬化合物所產生之應力造成破壞。