# 行政院國家科學委員會專題研究計畫 期中進度報告

子計劃三:5GHz高性能無線通訊系統中主要積體電路的設 計與整合(1/3)

計畫類別: 整合型計畫

計畫編號: NSC91-2215-E-009-080-

執行期間: 91年08月01日至92年07月31日

執行單位: 國立交通大學電子工程學系

計畫主持人: 吳重雨

計畫參與人員: 周忠昀、王文傑、廖以義

報告類型: 精簡報告

報告附件: 國際合作計畫研究心得報告

處理方式: 本計畫可公開查詢

中 華 民 國 92 年 5 月 21 日

# 行政院國家科學委員會專題研究計畫期中報告

高性能混合訊號式介面積體電路 — 子計畫三:

5GHz 高性能無線通訊系統中主要積體電路的設計與整合

計畫編號: NSC 91-2215-E-009-080

執行期限:91年8月1日至92年7月31日

主持人:吳重雨 國立交通大學電子工程學系暨電子研究所

E-mail: <u>cywu@alab.ee.nctu.edu.tw</u> 計畫參與人員: 周忠昀、王文傑、廖以義

#### 摘要

由於高傳輸速度的無線通訊系統越來越熱門,5-GHz 的免付費頻段勢必會成為下一代通訊系統設計的目標。在 1999 年國際電子電機協會 (IEEE) 802.11 委員會已根據原本的 2.4-GHz 頻段的規格,增加了 5-GHz 的版本- IEEE 802.11a;除此之外 HIPERLAN 亦已在這個頻段提出了新的規格。

此計劃主要是以 0.18~0.13µm 場效金氧半電晶體的製程來實現 5-GHz 高頻 段無線射頻金氧半電晶體收發機元件,設計從類比的射頻輸入訊號至數位輸出的 整合系統為目標。預計完成的電路元件包括低雜訊放大器、混波器、多相位中頻 濾波器、自動增益控制器、類比至數位資料轉換器、電壓控制振盪器、功率放大 器。

#### **Abstract**

In recent years, there are many existing Wireless Local Area Network (WLAN) systems operate in the 2.4-GHz ISM band. These products currently achieve maximum data rates of 1-2 Mbits/s. Due to the growing popularity of high data-rate WLAN systems, the next natural step is to extend the communications to unlicensed 5-GHz band. In fact, the IEEE 802.11 committee has supplemented its 2.4-GHz standard with a 5-GHz version in 1999. Additionally, the High Performance Radio Local Area Network (HIPERLAN) standard has been defined for operation in this band.

The purpose of this project is to develop components in RF transceiver with  $0.18 \sim 0.13 \mu m$  CMOS process for wireless applications in the 5-GHz frequency band. Besides, aim at the integration of whole chip consists of LNAs, mixers, Polyphase filters, A/D converter, VCOs, PA.

### 一、簡介

近年來,無線通訊的快速發展為人們的生活上提供了更多的便利,最為明顯的即是行動電話系統如 GSM, PHS, WCDMA 的快速發展。而在不久的將來,除了聲音之外,即時影像、資料等需要較大頻寬傳遞的訊息,也可藉由 Bluetooth、WLAN 等系統傳遞與交換。因此,如何設計無線網路系統,藉以提供更大的頻寬,以及將製作成本降低,例如單晶片整合,已經成為目前研究的熱門重點。

在 IEEE 802.11a 所制訂的無線通訊區域網路 (WLAN) 中所描述,此無線通訊系統分別操作於 5.15-5.25 GHz, 5.25-5.35 GHz 及 5.725-5.825 GHz 三個頻段;其中, 5.725-5.825 GHz 頻段僅適用於美國。

此系統採用 OFDM 的調變方法,每個 Channel 頻寬為 20MHz;而每一個 Channel 則有 52 個 sub-carrier,並且相互正交;每個 sub-carrier 頻寬約為 325KHz。最大接收訊號的功率為-30dBm,而輸出功率則根據頻段不同有不同的要求,分別為 40mW, 200mW, 800mW。理論上,最高傳輸速率可以達到每秒 54Mbits。

在 IEEE802.11a 中,OFDM 根據使用者不同傳輸速率的需求而採用不同的調變方法 (BPSK, QPSK, 16QAM, 64QAM);在設計射頻接收機時,不同的調變方法需要不同的訊雜比 (SNR),以達到 10%的 PER (Peak Error Rate),這也代表電路需要不同的雜音指數 (Noise Figure, NF)。為了避免接收機設計上的困擾,規格制訂者建議能達到 10dB 的 NF,為了確認電路能操作在線性範圍,根據經驗法則,接收機的 1dB Compression point (CP1dB) 需達到-26dBm (最大接收訊號功率減 4dB)。而在傳送機的設計上,在達到所需的輸出功率下,訊號的頻譜需在規格中所設定的 MASK 之內,以避免對其他頻段產生干擾並避免訊號失直。

在此計畫之中,我們選擇較為普遍的 5.15~5.35GHz 頻段來設計執行。並實現以下的電路模組:

- 1. 低雜訊放大器:此電路操作在 5-GHz,目的在降低後級電路對雜訊的影響,對整個系統的靈敏度有決定性的影響,所以需提供足夠的增益以及低的雜音指數。

- 2. 混波器:將射頻訊號與本地震盪訊號相乘,使訊號頻率降至中頻或基頻,混波器需有足夠的線性度已提高動態區間(dynamic range)。

- 3. 多相位中頻濾波器:具有消除鏡像訊號的功能,需要好的線性特性以及 足夠的頻寬。

- 4. 自動增益控制器:將輸入的變動訊號調整為固定振幅的輸出訊號,以利 後級的類比至數位資料轉換器轉換成數位訊號;此電路需要低雜訊、好 的線性特性、足夠的頻寬以及高動態範圍。

- 5. 類比至數位資料轉換器:預期類比至數位轉換器所需的規格為輸入頻率 40-MHz,取樣頻率為80-MHz,解析度八位元以上,低電壓、高速度的 類比至數位資料轉換器。

- 6. 電壓控制振盪器:產生本地震盪訊號供給混波器做移頻,所產生的訊號 頻率變動範圍需涵括整個頻段,且多次諧波要小、相位雜訊雜訊要低。

- 7. 功率放大器:將射頻訊號放大再由天線發射出去,需有足夠的輸出功率,以及好的效能,如線性度、功率效益。

在各元件的功能經過改進後,並進一步加以整合,再經由實際測試來確認結果。

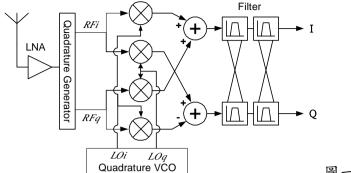

為了提供高整合性、避免 DC-Offset、flicker noise、multi-path mismatch 的影響以提高接收機性能,本計畫採用了圖(一)的接收器架構:

Mixers

圖一 雙正交接收機架構圖

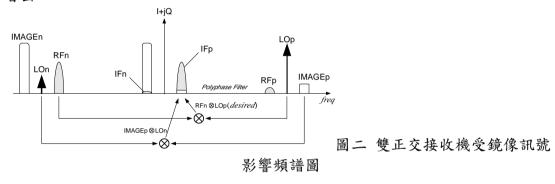

此架構由 Jan Crols 及 Michael Steyaert 於 1995 年提出,藉由將輸入及 LO 訊號都轉為正交形式,可以對 Multi-Path 電路製程上無法完全匹配的缺點有較大的容忍力,並降低了鏡像訊號的干擾。採用複數分析法,其原因可以由圖(二)中看出:

Polyphase

二、電路設計

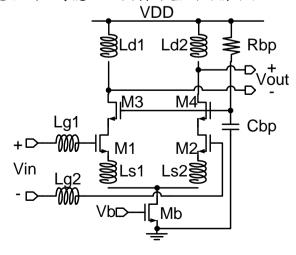

#### 1. 低雜訊放大器

如圖(三),在低雜訊放大器中,參考 Thomas H. Lee 對雜訊的分析方法。在固定功率消耗的考量下(3mW),對 M1, M2 選擇最適當的閘極寬度(W),可得到最佳的雜音指數(NF)。Spiral Inductor Ld1, Ld2 採用台積電提供的最小電感(2.307nH),此電感的 Valid Frequency 為符合要求的 6 GHz,將與位於輸出端的寄生電容在 5.2 GHz 互相諧振;而 Spiral Inductors Ls1,Ls2 及 Bondwire Inductor Lg1, Lg2 則提供阻抗匹配以利最大功率傳輸。在做電路模擬時,均將所有的Bondwire 及 PAD 電容列入考慮,以與實際量測的情形相仿。

此 5GHz 低雜訊放大器的模擬結果如下所示:

| Process           | TSMC018  |  |

|-------------------|----------|--|

| Supply Voltage    | 1.8 V    |  |

| Gain              | 21.7 dB  |  |

| Noise Figure      | 3.44 dB  |  |

| S11               | -21.4 dB |  |

| Power Dissipation | 3.321 mW |  |

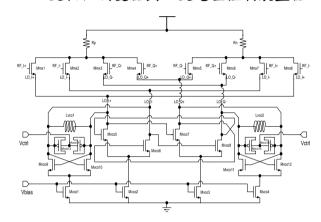

# 2. 正交相位調變器與正交電壓控制震盪器

圖四 正交混波器及正交電壓控制震盪器

圖四為此架構中採用的 I-Channel 正交相位調變器,Q-Channel 為相同的電路,但輸入的射頻訊號接線不同,並與 I-Channel 共用相同的電壓控制震盪器。因為此架構中需要四個降頻混波器,所以功率消耗將成為重要考量,在此電路中我們採用了疊加(cascode)的概念,使降頻混波器與正交電壓控制震盪器使用相同的電流,此方法將可明顯的減少功率消耗。模擬的結果如下:

| RF Frequency      | 5.2 GHz  |

|-------------------|----------|

| Power Supply      | 1.8 V    |

| OIP3              | 0 dBm    |

| Tuning Range      | 550 Mega |

| Conversion Gain   | -0.35 dB |

| Power Dissipation | 7.2 mW   |

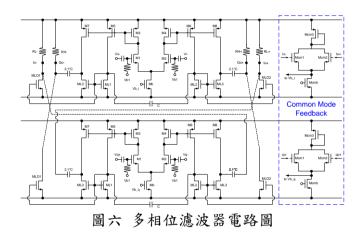

# 3. 多相位濾波器

I-Q 訊號可視為一個複數訊號 I+jQ,所以一個 Polyphase Filter 即是一個複數的濾波器。因為所需要的訊號與鏡像訊號位於相同頻率的正負兩端,作為一個具備鏡像壓縮功能的 Polyphase Filter 便必須對正負頻率有足夠的選擇性。複數濾波器的轉移函數可以以四個實數濾波器組合而成,如圖(五),

圖五 以實數濾波器來實現複數濾波器

適當的選擇實數濾波器的轉移函數即可以完成對正負頻率作篩選的功能,實現電路如圖(六)。

此多相為濾波器的研究成果已撰寫成論文並發表[1],其模擬結果如下表所示:

| Channel Bandwidth | 26 Mega Hz |

|-------------------|------------|

| Gain              | 7.2 dB     |

| THD               | -48 dB     |

| IRR               | > 60 dB    |

| Power Dissipation | 6.66 mW    |

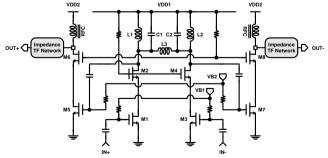

# 4. 功率放大器

圖七 功率放大器

如圖(七)所示,此功率放大器為兩級 Cascade 的架構,利用 Cascode MOS 的方式來提高兩級間的 Isolation,以提高此功率放大器的穩定度;利用 Cascode MOS

的方式,可同時降低輸出端的大訊號振幅對 Gate-Drain Oxide 的電壓降,進而減輕 Oxide Breakdown 的問題。在 IEEE802.11a 的系統定義中,諸如 M-QAM 等的調變方式,需要較大的線性操作;然而考慮到功率效益(power efficiency),所以需要在線性度與功率效益間取得平衡,故將此功率放大器的兩級都操作於Class-AB的形式。在所選取的操作的頻帶 5.15~5.25 GHz 下,需要能夠提供 200mW的輸出功率。

阻抗轉換網路(Impedance Transform Network)將 50 ohms 轉阻成 R\_optimal,以使第二級功率放大器 (M5~M8)能夠提供超過 200mW 的功率。在設計阻抗轉換電路時,需注意該網路的 Q 不可過大,以避免發生不必要的震盪情形。在此功率放大器的阻抗轉換網路中,我們設計使網路的 Q 值小於 3。

由於第二級功率放大器要提供大的輸出功率,所使用的大 Size 的 MOS 會對第一級產生很大的電容性 loading,為了要使第一級輸出的阻抗能夠在 5.2 GHz 諧振,因此除了使用 L1-C1 以及 L2-C2 的 LC tank,還在第一級兩輸出間併聯 L3,始能提供夠小的電感值,而能諧振在 5.2 GHz。電路模擬時,將 bondwire 以及 PAD 電容考慮進去後,此電路的模擬結果如下表所示:

| Technology        | TSMC 1P6M 0.18um    |  |

|-------------------|---------------------|--|

| Supply Voltage    | 1.8 V               |  |

| Output Power      | 232mW (23.6 dBm)    |  |

| Power Dissipation | 664mW               |  |

|                   | (109.8 mW + 554 mW) |  |

| Efficiency        | 34.9 %              |  |

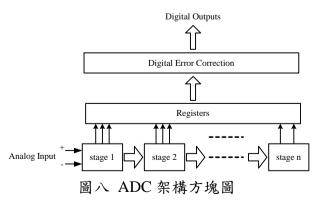

### 5. 類比至數位資料轉換器

圖(八)所示為此次設計的 ADC 架構方塊圖。整個 ADC 中包含了管線化的每一級、暫存器及數位錯誤修正等電路。此種架構中的每一級所處理的解析度為 log2 (2<sup>n</sup>-1)位元,其中 n 為每一級所產生的數位輸出。在此次設計中 n 為 3 ,故其每一級所能處理的解析度為 2.8 位元,而最後一級為 2 位元。總共需要四級來完成全部八位元的解析度。在經過每一級的訊號處理之後所有的數位輸出將同時送往暫存器及之後的數位錯誤修正電路中,最後八位元的數位輸出將平行地被送出。

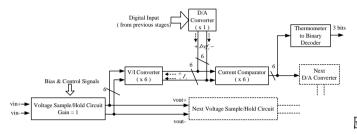

每一級的詳細電路架構如圖(九)所示,其包含了一組取樣保持電路(sample-and-hold)、六組電壓轉電流電路(VIC)、一顆電流汲取式數位類比轉換器

(current steering DAC)、六組電流比較器及一組 thermometer-to-binary 編碼器,最後同時產生三位元 Binary 碼及六位元的 Thermometer 碼。然而最後一級只需要產生2位元 Binary 碼,所以只需要三組 VICs 及電流比較器即可。圖中電壓取樣保持電路(SHC)是用來傳遞及保持輸入訊號準位,其輸出將送至 VIC 電路讓它產生相對應的電流,同時也將輸入電壓以增益為一的大小送往下一級。為了改善其速度的特性,此 SHC 電路將採用開放式架構。因為開放式架構很難實現電壓相減的功能,故此設計透過 VIC 將電壓轉成電流,使得相減的動作能夠在電流模式下輕易的被完成。

圖九 第i級詳細架構圖

因為許多高速的 DAC 都是利用電流模式架構來完成[2][3],所以此次設計亦利用此種方法來設計 sub-DAC 並產生相對應的參考電流。每一級 sub-DAC 的輸入皆為前一級的數位輸出而輸出的六組電流 Irefi 將和 VIC 的輸出 Ii 完成相減的動作。整個 ADC 的處理是採用 successive approximation 演算法,圖(十)所示為其詳細演算法的過程,為了容易說明,圖(十)所示為單端的演算法,雙端亦很容易以此類推。當輸入訊號落在落在參考電流某一區間時,即可利用本級所得到的數位訊號將下一級 sub-DAC 設定到此一區間並在此區間產生數個參考電流 Irefi+1。

經過電流相減後的剩餘電流將被送至電流比較器,用來完成 quantization 動作,最後產生的 6 位元 thermometer code 用來控制下一級的 sub-DAC,同時此數位輸出亦透過 Thermometer-to-Binary 編碼器送到數位錯誤修正電路。

圖十 successive approximation 演算法

此外為了壓低偶數次諧波失真及時脈穿透(clock feedthrough)雜訊整個路徑皆採取雙端差動電路架構。

此 ADC 動態特性亦利用 HSPICE 來模擬,並將所得到的數位碼利用 Matlab 做 FFT 分析其結果如圖(十一)所示。取樣頻率為 71.43MHz 時,輸入頻率為

20MHz,經過 FFT 分析後,其 SNDR 為 44dB,約為 7.01 位元的解析度。下表為整個 ADC 模擬特性,此開放式架構 ADC 亦已撰寫成論文發表[4]。

| Technology          | 0. 25μm 1P5M CMOS                  |           |  |

|---------------------|------------------------------------|-----------|--|

|                     | (Thick oxide is selected)          |           |  |

|                     | (Minimum channel length is 0.35µm) |           |  |

| Input Frequency fin | 10 MHz                             | 20 MHz    |  |

| Accuracy            | 8 bits                             | 7.01 bits |  |

| Pipelined Stages    | 4                                  |           |  |

| Sample Rate         | 71.4 MS/s                          |           |  |

| Full Scale Voltage  | 1.2 V                              |           |  |

| Full Scale Current  | 256 μΑ                             |           |  |

| Unit LSB Current    | 1 μΑ                               |           |  |

| Power Dissipation   | 205 mW @ f <sub>in</sub> =20 M Hz  |           |  |

| Power Supply        | 3.3 V                              |           |  |

#### 三、結論

目前已完成模擬的各電路方塊有:低雜訊放大器、正交相位混波器、正交相位電壓控制振盪器、多相位濾波電路、類比至數位資料轉換器以及功率放大器。正交相位混波器和正交相位電壓控制振盪器使用了電流重複使用的技巧,大幅的降低功率消耗,在考慮製程上的飄移,此電路在四個 Corners 模擬下,其性能皆能滿足需求。使用主動元件的方式來實現多相位濾波器,除能達到好的鏡像頻率的抑制,相較於使用被動元件 R-C 網路所實現的多相位濾波器,此主動的多相位濾波器還能夠提供額外的增益。而 ADC 電路採用開放式架構來改善類比至數位資料轉換器速度的特性。功率放大器被設計能提供足夠大的功率輸出,與單端的架構相比,使用差動架構的功率放大器,能夠有較大的電壓可運作區間、偶次諧波消除效果等優點。

#### 四、計畫成果自評

此子計畫正持續的進行中,大部分的子系統皆已模擬完成並且製作中。接下 來就是量測驗證這些電路模組,進一步改善這些模組的效能。並同時著手進行設 計自動增益控制電路。

# 五、參考文獻

- [1] Chung-Yun Chou, Chung-Yu Wu, "The Design of a New Wideband and Low-Power CMOS Active Polyphase Filter for Low-IF Receiver Applications," in Symp. on APCCAS, Singapore, Dec. 2002, pp. 241-244

- [2] Jjose Bastos et al., "A 12-Bit Intrinsic Accuracy High-Speed CMOS DAC," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 1959-1969, Dec. 1998.

- [3] C. H. Lin and Klaas Bult, "A 10-b, 500-Msample/s CMOS DAC in 0.6 mm<sup>2</sup>," *IEEE J. Solid-State Circuits*, vol. 33, no. 12, pp. 1948-1958, Dec. 1998.

- [4] Y.-Y. Liow; C.-Y. Wu, "The design of high-speed pipelined analog-to-digital converters using voltage-mode sampling and current-mode processing techniques," in the proceeding of *IEEE International Symposium on Circuits and Systems ISCAS 2002*, May 2002, vol. 3, pp. 117-120.