# 行政院國家科學委員會補助專題研究計畫成果報告

具有信號處理能力的嵌入式微處理機的實現及應用 -總計畫:具有信號處理能力的嵌入式微處理機的實現 及應用

計畫類別: 個別型計畫 整合型計畫

計畫編號: NSC 89-2218-E-009-056-

執行期間: 89年8月1日至90年7月31日

計畫主持人:吳全臨 教 授(國立交通大學/逢甲大學)

共同主持人:鍾葉青 教 授(逢甲大學)

陳德生 助理教授(逢甲大學) 李維聰 副教授(逢甲大學)

執行單位:國立交通大學資訊工程學系

逢甲大學資訊工程學系

中 華 民 國 90 年 7月 31日

# 具有信號處理能力的嵌入式微處理機的實現及應用 -

總計畫: 具有信號處理能力的嵌入式微處理機的實現及應用

計畫編號: NSC 89-2218-E-009-056-

執行期間:89年8月1日至90年7月31日

計畫主持人:吳全臨 國立交通大學資訊工程系教授 共同主持人:鍾葉青 逢甲大學資訊工程學系教授

陳德生 逢甲大學資訊工程學系助理教授 李維聰 逢甲大學資訊工程學系副教授

# 摘要

IAM2000S(Information Appliance Microprocessor with Digital Signal Processing Capability)是我們自創品牌自行設計中的 32 位元嵌入式微處理機。本文報告計畫執行的現況及一些設計的來龍去脈。

此具有信號處理能力的嵌入式微處理機, 將執行 Linux 作業系統,並在網路電話的應用系 統中,實際驗證其二合一的實際成效。在未來 家電系統中的系統晶片整合,預期其將發揮相 當大的經濟效益。

# 1.介紹

#### A.計畫簡介

由於後 PC 時代的興起,電腦、通訊、及消費電子的產業面臨革新及整合的殷切需求。全球 IC(Integrated Circuits)設計趨勢也因此發生變化。

在過去,嵌入式微處理機及數位信號 處理機為兩個分開的處理器主體。如今也 面臨整合的需求。這個二合一的技術整 合,將使應用系統只要執行一個作業系統 及使用單一的發展系統。這也使得系統可 以縮小體積及製造成本。並且有助系統晶 片之開發。

因上述的大前提趨勢,本計畫就是在 下列三個主要背景下,積極發展國內自創 品牌具關鍵性有信號處理能力的嵌入式微

#### 處理機。

- (1) 嵌入式微處理機的技術層次及使用量逐年加溫;

- (2) 信號處理器在數位時代的起跑點 取得大贏;及

- (3) 嵌入式微處理機及信號處理機在 3C系統的需求下,面臨二合一的整合 需求。

嵌入式微處理機及數位信號處理機應 用廣泛,在無線通信產業的應用上,更佔 總成本百分之二十五以上。此一市場長期 以來為歐美先進國家所壟斷。隨著 3C 市場 之快速成長,在公元 2005 年以後,市場將 有龐大的需求量。為提昇我國產品研發之 獨立自主與競爭力,我們應未雨綢繆,把 握這技術變遷的切入時機發展自創品牌之 混合式處理器,以免因智慧財產權與專利 權的爭議,及利潤的考量,影響到我國 3C 產業的經濟效益。

計畫之目標為實現一個具有信號處理能力的嵌入式微處理機IP模組、晶片、及其配套軟體,並經展示,證明其可用性。其實質目的在於訂定其微架構、指令集、發展軟核心(Soft Core)、硬核心(Hard Core)、晶片、執行作業系統、研製軟體發展系統(包括編譯器、除錯器、組合器、連接器、模擬器、軟體仿真器、及一套使用界面軟體)、評估卡、及網路電話應用。

#### B.國內外有關本計畫之研究情況

尚未發現國內學術及產業界有單位研發混合式 RISC/DSP 嵌入式微處理機。

在國外分別有 Siemens[1]、Hitachi[2]、NEC[3]、STMicroelectronics[4]、ARM[5]及 MIPS[6,7,8]正發展各自的混合式品牌。Simens 的 Tricore 之實作主要目的是驗證其架構及發展除錯工具。它用 0.35µm,3LM,及 3.3V 的製程,並且加入嵌入式 DRAM。晶片內建置有程式及資料記憶體。

Hitach 的 SH3-DSP 則是整合 RISC 及 DSP,要當作網際網路的處理器。使用 Harvard architecture。其第一個應用晶片 SH7729 是包含 Timers、DMAC、A/D、及 D/A 等的系統晶片、速度為 133MHz、有 3.3M 電晶體。

STMicroelectronics 則是發展 32-位元混合式 DSP-MCU 架構,以便提供不同performance/cost 比例的硬體系統實作。第一個晶片目標頻率為 300MHz,使用 1.8V。它並有可能發展 64 位元架構。

NEC 發展 32-位元低耗電低價位 RISC 控制器。其使用 0.25mm CMOS 4ML 製 程,預期達到 1.3w@200MHz,2.5V。

ARM 則發展 ARM9E, 提供 32-位元 RISC 單一處理器以便行使 DSP 及控制應 用。其使用 0.25µm,預期達到 160MHz。

MIPS Technologies 本身則定義 32-位元的 MIPS TM 4K 及 64 位元的 MIPS TM 5K 架構。另一家公司 Lextra 也把 DSP 的能力加到 MIPS Core 裡[6]。 MIPS Technologies 除其規劃的 Jade 及 OPAL 外,也規劃了高性能之 RUBY。

這些研發最終的目標則是使用到家電用途的系統晶片,如 National Semiconductor的 Geode SC 1400[9]。

#### C.目前進度

此二合一的嵌入式微處理機定名為IAM2000S(Information Appliance Microprocessor with Digital Signal Processing Capability)。目前進度如表一:

#### IAM2000S 特性一覽表所示。

#### 表一 IAM2000S 特性一覽表

|                            | IAM 2000S (第一版)                     | 備註(ARM9E-S 及其他)          |  |  |

|----------------------------|-------------------------------------|--------------------------|--|--|

| # of instructions          | 58                                  | With Condition Code      |  |  |

| Clock rate                 | 180MHz                              | 160MHz ( ARM 9E-S )      |  |  |

| (at .25 cell library)      |                                     |                          |  |  |

| 第二版 Clock rate             | 預計 300MHz                           |                          |  |  |

| Gate count                 | 29680 gates                         | Not sure                 |  |  |

| Power consumption          | 301.2164mW                          | 288mW(ARM 9E-S)          |  |  |

| (at 2.5V/.25 cell library) |                                     |                          |  |  |

| Bus                        | PCI for peripheral bus              | APB for ARM              |  |  |

| # of registers             | 44 general-purpose registers        | 31 general-purpose       |  |  |

|                            | 3 status registers                  | registers                |  |  |

|                            | Total: 47                           | 6 status registers       |  |  |

|                            |                                     | Total: 37 (ARM)          |  |  |

| JTAG、BIST、ICE              | 已建立                                 |                          |  |  |

| RTL code 及驗證               | 第一年已完成 Processor code,              |                          |  |  |

|                            | 並且完成一億以上之指令測試                       |                          |  |  |

|                            | 驗;已成功展示其執行應用程                       |                          |  |  |

|                            | 式能力                                 |                          |  |  |

| # of modes:                | 5 (USR,USR1,USR2,PR1,SYS)           | 6 1st: USR               |  |  |

|                            |                                     | 2nd~6th: exception modes |  |  |

|                            |                                     | (ARM)                    |  |  |

| Task switching             | 3 user mode which switch without    | Only one user mode       |  |  |

| mechanism                  | need for storing register contents. | (ARM)                    |  |  |

| 模擬器                        | 第一年已完成                              |                          |  |  |

| 編譯及組合器                     | 第一年已完成                              |                          |  |  |

| 軟體仿真器                      | 預計第二年完成                             |                          |  |  |

| 除錯器(Debugger)              | 預計第二年完成                             |                          |  |  |

| 連接器(linker& loader)        |                                     |                          |  |  |

| Embedded OS                | 預計第二年 Port Linux                    |                          |  |  |

| 發展系統                       | 預計第三年完成                             |                          |  |  |

| VOIP 評估卡                   | 預計第二年完成                             |                          |  |  |

| 網路電話應用系統                   | 預計第三年完成                             |                          |  |  |

IAM2000S 的 RTL 設計,透過一個自動比對驗證系統[10],超過一億個以上的指令已經在其模擬環境中,實際執行過;除錯及驗證的程序可謂嚴謹。表二顯示 RTL 檔暗各行的測試程度。除少數例外,所有檔案的測試都接近百分之一百。

表二 RTL 檔案測試程度

| Module Name     | Test programs for       | Total verified test |  |

|-----------------|-------------------------|---------------------|--|

|                 | auto-regression testing | programs            |  |

| Decoder.v       | 100%                    |                     |  |

| Controller. v   | 100%                    |                     |  |

| Exception. v    | 98.4%                   | 100%                |  |

| LDM_STM. v      | 100%                    | 100%                |  |

| Execute. v      | 100%                    | 100%                |  |

| R_decoder, v    | 100%                    | 100%                |  |

| R_file. v       | 100%                    | 100%                |  |

| Debug_module. v | 81.4%                   | 81.4%               |  |

| Cop1. v         | 99.6%                   | 100%                |  |

| Cpl_register. v | 100% 100%               |                     |  |

| D_memory. v     | 92.1%                   | 92.1%               |  |

| I_memory. v     | 100%                    | 100%                |  |

| IO_memory. v    | 100%                    | 100%                |  |

使用 0.25µm 製程, IAM2000S 預計可達 300MHz 以上。如果使用比較先進的製程,如 0.18 或 0.13 製程,則其速度也將可更加提高,也能達 500MHz。這些成效,與商業公司所將發展的,有過之而無不及。在家電市場上,將具有高度的競爭力。

IAM2000S 在指令集及微架構有其特殊的新發展,配合未來將發展的嵌入式 Linux 作業系統軟體發展系統及網路電話實用之驗證,此計畫將提供一個殊勝的新品牌。至於為何設計現行的指令集及微架構,則於下節說明。

#### D.模擬器及 RTL Core 交通誌號控制展示

IAM2000S 之模擬器及 RTL Core 經過 反覆完整的驗證,實際上已經能夠執行應 用程式。圖一顯示一個十字路交通誌號的 控制平面圖。控制應用程式可以分別在模 擬器及 RTL Core 上執行;交通誌號控制如 預期地依交通狀況正確運轉。

#### 圖一 交通誌號控制圖

# 2.另定指令集的成效

所定指令集已於另文中[11]說明。為了要評估新指令集對於微處理的影響,我們評估其對十七個應用程式的效能。十七個應用程式如下所示。

- (1) Image Processing :image file with bmp format quantization to bmp format

- (2) FFT(1):fast fourier transform

- (3) FFT(2):fast fourier transform

- (4) Flops:benchmark for FPU

- (5) TFFTDP:benchmark for FFT in double

precision

- (6) LPE:low pass filter

- (7) Mp3 Player:audio file with mp3 format transformation to wave format

- (8) Fib:fibonacci numbers

- (9) Traffic Light:traffic light system

- (10) Heapsort:heapsort

- (11) Queens: eight-queens chess

- (12) Nsieve:benchmark for variable sized arrays

- (13) Whetstone:benchmark

- (14) Dhrystone:benchmark

- (15) Hanoi:Hanoi

- (16) Clinpack(unroll):benchmark

- (17) Clinpack(roll):benchmark

表三顯示其與 ARM9E-S 相對的執行時間 差異及程式的長度。表三中,B,NBA,及NBNA 分別表示 Branch 的指令,不必比對的指令,及 需要比對的指令。控制性質應用程式用到比較 多需要比對的指令,反之,DSP 的應用程式用 到比較少的需要比對的指令。因為 IAM2000S 的應用程式是由 ARM 的應用程式直接轉譯過 來的;一個 ARM 指令有時要二個 IAM2000S 指令來對應,但大部份是一對一。因此之故, IAM2000S 相對應的指令較長,執行的時間也較 長。

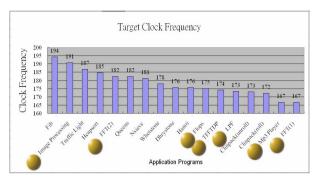

圖二顯示的時間上的差異,其中 DSP 應用程式的執行時間,差異比較少。為彌補此差異,IAM2000S 勢必要加快。圖三顯示 IAM2000S 要對各個應用程式加快的速度。只要 IAM2000S 能加快 194MHz,便可彌補其時間的差異。由我們微架構的設計及實際結果顯示,IAM2000S 可以達到 300MHz 以上。

圖二 執行時間差異的百分比

圖三 加快速度評估

表三 應用程式執行評估

| Application Program | Assembly Code Category |       |      | Penalty |       |

|---------------------|------------------------|-------|------|---------|-------|

|                     | В                      | NBA   | NBNA | Space   | Time  |

| Fib                 | 23.1%                  | 70.8% | 6.1% | 12.2%   | 21.4% |

| Image Processing    | 16.8%                  | 77.7% | 5.5% | 11.0%   | 19.3% |

| Traffic Light       | 27.1%                  | 68.0% | 4.8% | 9.6%    | 16.8% |

| Heapsort            | 17.8%                  | 77.8% | 4.4% | 8.8%    | 15.4% |

| FFT(2)              | 4.0%                   | 92.0% | 4.0% | 8.0%    | 14.0% |

| Queens              | 22.4%                  | 73.6% | 4.0% | 8.0%    | 14.0% |

| Nsieve              | 17.2%                  | 79.0% | 3.8% | 7.6%    | 13.3% |

| Whetstone           | 19.5%                  | 77.3% | 3.2% | 6.4%    | 11.2% |

| Dhrystone           | 24.5%                  | 72.7% | 2.8% | 5.6%    | 9.8%  |

| Hanoi               | 17.2%                  | 80.0% | 2.8% | 5.6%    | 9.8%  |

| Flops               | 15.3%                  | 82.0% | 2.7% | 5.4%    | 9.5%  |

| TFFTDP              | 15.3%                  | 82.2% | 2.5% | 5.0%    | 8.8%  |

| LPF                 | 7.2%                   | 90.4% | 2.4% | 4.8%    | 8.4%  |

| Clinpack(unroll)    | 16.0%                  | 81.7% | 2.3% | 4.6%    | 8.1%  |

| Clinpack(roll)      | 15.5%                  | 82.3% | 2.2% | 4.4%    | 7.7%  |

| Mp3 Player          | 12.5%                  | 86.3% | 1.2% | 2.4%    | 4.2%  |

| FFT(1)              | 10.2%                  | 88.6% | 1.2% | 2.4%    | 4.2%  |

# 3.特殊微架構之意義

我們在微架構設計中,用了一些別的微處 理機所沒有的東西,擇要如下幾項:

- (1) No. of operation modes;

- (2) Task switching mechanism;

- (3) Instruction cycle time;及

- (4) Register read/write port.

在 operation modes 方面,如表四所示,我們用了 USR, USR1, USR2,及 SYS 四個 modes 方便於多個應用程式,及系統程式的同時執行。

在 Task switching 方面,我們使用 register window 相重疊的觀念。使用 task switching 時,不必作 load/store 的運作,以減少不必要的執行運算。

我們在作 Data path 設計時,考慮到快速執行的問題,配合控制單元的時序,ALU 可以以一個時序完成絕大部分的執行;特別指令如

Multiply-long 指令,也只需要兩個時序。這比 ARM 家族系列的微處理機各減少一個時序。

為了要減少指令執行時,我們特意將暫存器的 Read ports 增加到參個,有別於 ARM9 之兩個;這使得 IAM2000S 能夠將絕大部份的指令在一個時序內完成。反觀,ARM9 則分別需要兩個及參個時序才完成指令執行。這也使得在第 2 節中所提到的執行時間差異的問題化解於無形;反而 IAM2000S 只需要 100MHz 的速度即可在絕對時間上取得優勢。

表四 IAM2000S 處理器模式

| Processor mode | Description                           |  |

|----------------|---------------------------------------|--|

| User           | Normal program execution mode         |  |

| User1          | Specific user program execution mode1 |  |

| User2          | Specific user program execution mode2 |  |

| Privileged     | Exception mode, including:            |  |

|                | 1. FIQ                                |  |

|                | 2. IRQ                                |  |

|                | 3. Supervisor                         |  |

|                | 4. Abort                              |  |

|                | 5. SWI                                |  |

|                | 6. Undefined                          |  |

| System         | Run operating system tasks            |  |

### 4.系統軟體

IAM2000S 必須配備即時作業系統的執行及一個軟體系統發展環境。

即時作業系統統籌 IAM2000S 的執行資源 及環境。它必須有一個系統核心(System Kernel)。此核心主要的工作為監督行程,主要 的目的是為了避免系統的閒置時間。而且,一 般此核心常駐於 IAM2000S 之記憶體內,由下 列四個部分組成:控制直譯程式、裝置驅動程 式、工作排序、及中斷向量。程序管理主要是 依據排程程式實作出多工作業,而所對應到 的,則是與硬體架構相關的程式碼。在系統運 轉期間,動態加入作業所需的程式碼,使之成 就作業管理。在國內只有資策會完成一種嵌入 式的即時作業系統,但是並沒有特定的應用平 台,使之備而不能用。如今 IAM2000S 的特殊 微架構,提供了一個很好的應用平台,如果能 認真經營, IAM2000S 及相對應的核心及作業系 統,將是很殊勝的國際市場競爭項目。

軟體發展環境包含了編譯器、組合器、載入器、除錯器、仿真器、及模擬器等,旨在提供視覺化的介面,讓使用者容易使用 IAM2000S 及發展應用軟體。國內在軟體的研發有相當的投入,此發展環境第一次讓國內的研發投入有機會在市場上發揮。

# 5.網路電話應用評估

IAM2000S 為二合一的晶片,在系統整合上頗為新穎。我們將利用網路電話(Voice over IP)來作 IAM2000S 的效能評估的測試平台。此VOIP 平台所量測出來之效能數據,將有利於IAM2000S 的改進及市場推廣。

應用評估執行將分為兩部分:雛形實現及 系統整合。

在雛形實現方面,將進行下列四項工作:

1. 首先將 VoIP 評估卡之 CPU 部份使用 ARM CM7TDMI , DSP 部 份 則 使 用 TMS320C54x,並實作此 3C 晶片評估卡。 然而便會面臨到一些問題需要去解決,如使 用之 CPU 與 DSP 其電路需要重新設計與繞路。另外,coding 的部份也需要重新設計與繞路。另外,coding 的部份也需要重新撰寫與 修改,來符合新的 VoIP 評估卡。然後再將 CPU 與 DSP 模組做整合與測試的動作,以 確保其能正常地運作。

- 2. 將整合 CPU 與 DSP 模組以完成 3C 晶片之測試實驗平台,並規劃硬體量測、軟體程式模擬量測及追蹤之模型。例如利用 H.323 Call Generator,它是一種裝置設備,它給予開發者模擬在 VoIP 環境中,做專業的性能試驗技術,提供服務供應者不同等級的標準檢查程式、負載測試、執行及驗證 VoIP 中的傳輸協定。

- 3. 提供 CPU 及 DSP 模組所需之功能,以作為 評估 3 C 晶片效能之參考。

- 4. 另外,將參與系統軟體之 porting。包含在 CPU 晶片模組上 OS 的 porting, TCP/IP 的 porting, packet driver and PSTN driver 在 3C 晶片上之實現,以及壓縮演算法在 DSP 模組

上之實現等。

在系統整合方面,有下列三點的執行:

- 1. 完成硬體量測、軟體程式模擬量測及追蹤模型之設計。在 VoIP 評估卡之測試環境中,利用硬體量測、軟體程式模擬量測及追蹤模型來即時得到最真實且完整正確的系統工作量追蹤,最後在研發追蹤縮減技術及方法以降低追蹤驅動模擬所需的時間。

- 2. 利用測試實驗平台來量測 3C 晶片系統效能並進行分析。利用 VoIP 評估卡所測量 3C 晶片之數據來做分析和進行其效能的評估,並尋求系統效能的效能瓶頸所在,再加以進行修改與測試,以其達到最佳系統效能的狀態。

- 3. 以系統量測結果,進行最佳化之設計,並 將其修改、測試、整合與研發,以預期得到 最佳化之 3C 晶片。

# 6.結論

IAM2000S 計畫在下列五方面創造了科技 領先的條件。

- (1) 嵌入式微處理機自創品牌,在指令集 及微架構的設計上,有創新的發揮;

- (2) 提供國內即時作業系統一個嵌入式微 處理機新平台,以發展新穎的核心及 作業系統;

- (3) 提供系統軟體研發者一個在國際市場上發揮的機會;

- (4) 率先在二合一的系統整合上,發展其技術條件及顯示其經濟效益;及

- (5) 發展二合一網路電路連接閘 (gateway),在3C市場上創造一片天。 這些技術上的創舉,解釋了我們為什麼要

這些技術工的創举,解釋了我们為什麼: 設計 IAM2000S 的嵌入式微處理機。

# 7.誌謝

本文的完成要感謝鍾葉青、李維聰、陳德 生、胡文祥、王仕杰、練彩茹、林銘豐、闕國 勳、黃明權、及蘇耀群等的技術支援。

# 參考文獻

- [1].R. Flech, :Implementation of a Microcontroller/DSP for Real-Time Application", <u>Embedded Processor Forum</u>, 1998.

- [2].J. Slagger, "Hitachi's SH3-DSP Integrated RISC CPU and DSP Optimized for Internet". <u>Embedded Processor</u> <u>Forum</u>, 1998.

- [3].D. Fuin, "The ST 100 DSP-MCU Architecture" <u>Embedded Processor Forum</u>, May 1999.

- [4].I. Kuroda, "A Superscalar Microcontroller with Advanced DSP Capability", <u>Embedded Processor Forum</u>, 1998.

- [5].J. Rayfield, "ARM's New Architectural Extensions for DSP", Embedded Processor Forum, May 1999.

- [6].W. Putrich Hays, "LX5280: High-Performance ROSC/DSP for IP Liconsing", <u>Embedded Processor</u> <u>Forum</u>, May 1999.

- [7].D. Jones, "The MIPS64 5ke: The first Synthesizable 64-bit Core", Microprocessor Forum, Oct. 1999.

- [8].O. Courtright, "Jade, The Next 32-bit RISC from MIPS Technologies". <u>Embedded Processor Forum</u>, 1999.

- [9].S. Yomtor, "Geode SC1400: An Information Applice on a chip". Microprocessor Forum, 1999.

- [10].M. C. Huang, Y. C. Su and C. Wu "Mixed Mode Verification for 32-bit Microprocessor Core", Submitted for publication, 2001.

- [11]. C. Wu, et. al., "RTL Design of an Embedded RISC Microprocessor with DSP Capability," Submitted for publication, 2001.