# 行政院國家科學委員會補助專題研究計畫成果報告

# 多媒體系統晶片設計技術之研究—總計畫(3/3)

計畫類別: 個別型計畫 整合型計畫

計畫編號: NSC89 - 2218 - E - 009 - 077 -

執行期間: 89年 8月 1日至 90年 7月 31日

計畫主持人:李鎮宜教授

共同主持人:沈文仁教授、任建葳教授、周景揚教授、陳紹基教授

## 本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份 赴大陸地區出差或研習心得報告一份 出席國際學術會議心得報告及發表之論文各一份 國際合作研究計畫國外研究報告書一份

執行單位:國立交通大學電子工程學系

中 華 民 國 九十年 十月 二十八日

# 行政院國家科學委員會專題研究計畫成果報告

多媒體系統晶片設計技術之研究—總計畫(3/3)

計畫編號:NSC89-2218-E-009-077

執行期限:89年8月1日至90年7月31日

主持人:李鎮宜 國立交通大學電子工程學系

共同主持人:沈文仁、任建葳、周景揚、陳紹基 國立交通大學

電子工程學系

## 一、中文摘要

此整合型記畫執行三年來,已產出數十篇的 國際會議和期刊論文,並有部分技術落實至產業 界。在此僅簡述有關符合多樣標準的視訊解碼器 的部分研究成果,提供參考。

此整合型計畫產出一個具有高輸出率且訊息 編碼可程式化之影像解碼器的硬體架構設計。因 為使用以記憶體為基礎的可變長度解碼器[19],所 以此影像解碼器能夠經由改變記憶體的內容達到 霍夫曼編碼表和編碼符號可程式化,影像標頭和 量化表也使用記憶體來儲存而可以修改,為了縮 短訊息解碼器和 IDCT 間的處理時間差,使用 ISDCT 來只操作非零的 DCT 係數且平行計算 8 個 點 [23],根據資料型態分析的結果,提出的高效 率管線化設計來增加處理速率和減少暫存器的使 用。本影像解碼器針對 MPEG 和 JPEG 的影像來 設計, 在採用 0.35-~m CMOS 的製程技術下, 其 在 4.38 x4.38 mm2 內整合了 125K 邏輯閘和 14K bits 記憶體,模擬的結果顯示此影像解碼器在 66MHz 的時脈頻率下,訊息解碼可以達到 56.5M symbols/sec, 而影像解碼則有 400Mpixels/sec 的輸 出率,因此所提出的影像解壓縮架構滿足系統對 效能的需求,並且有高度的適應性可以應用於多 種影像解碼程序中。

#### 英文摘要:

In this paper, a video decompression architecture with high throughput and entropy decoding programmability is presented. Due memory-based VLC decoder [9], this video decoder acquires the flexibility to program the used Huffman tables and source symbols by changing the associated memory contents. The information of image headers and quantization tables are loaded into memory modules for modification. To minimizing the operation time difference between entropy decoding and IDCT, an ISDCT that manipulates nonzero DCT coefficients only and calculates 8 pixels in parallel is employed [10]. According to the result of data type analysis, a novel pipeline scheme is developed to improve processing rate and save internal buffer space. Using 0.35-~m CMOS technology, a VLSI implementation including memory-based VLD, symbol decoders, ISDCT, and MC is shown to reconstruct MPEG and JPEG pictures. This design integrates 125K logic gates and 14K-bit memories in a 4.38 ×4.38 mm<sup>2</sup> core area. Simulation results show that it achieves 56.5M symbols/sec in entropy pixels/sec decoding and 400M in video decompression with a clock rate of 66MHz. Therefore, the proposed video decompression accomplishes both architecture satisfactory performance for advanced applications and sufficient adaptability for various video decoding procedures.

### 二、 研究動機與相關研究發展現況

多媒體應用結合了數種型態的訊息,例如文字、言詞、聲音和圖片,其中由於視訊影像的資料量龐大,成為決定系統效能最重要的部分,而近年來更由於電腦普及和通訊技術進步,數位影像已經被廣泛地使用在各種領域之中,在共續學學,對於畫面品質和解析度的要求也在持續學高,使得所要處理的資料量大幅增加,而影像不可能與解壓縮是達到降低儲存空間和通訊頻寬,並且提供高品質視訊服務的必要方法,為了方便影像資料的交換和傳遞,針對各種不同應用的國際標準也就隨之產生,例如:JPEG、MPEG、H.263等。

以實際應用的觀點來看,高效能且低成本的 影像解碼器是一個不可或缺的模組,因此也就在 文獻中被廣泛地討論[1-8]。雖然目前軟體的解決 方案可以滿足 VCD 與 DVD 等應用,但是其效能 的提昇有限,並且需要使用高效能的數位訊號處 理器,使得高階應用系統和可攜式產品,例如數 位攝影機、數位電視等,仍然使用硬體模組的實 現方式,以達到高效能和低成本的設計考量,但 是一般所採用的硬體架構是直接完成解壓縮流 程,並沒有可率可程式化的功能,使得在以 SOC 為設計導向的情況下,系統的可應用範圍和重複 使用的能力大幅降低,此外也沒有針對各個步驟 和整體演算法的關係作分析,然後再設計可以使 系統達到最佳化的功能方塊,因此解碼的動作是 以 MB-by-MB 或 block-by-block 的方式來完成,不 僅需要較大量的內部記憶體來儲存暫時性的資 料,系統的效能也會因為要存取這些記憶體而無 法有效增加。

本論文的研究目的在於發展一個高效能且高

#### 三、系統架構簡介

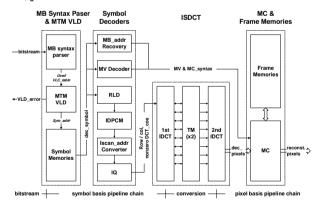

所提出之影像解碼器的系統架構如圖一所 示,其主要分成四個部分,名為MB Syntax Parser & MTM VLD, Symbol Decoders, ISDCT, and MC & Frame Memory。其中 MTM VLD 是使用以記憶體 為基礎的架構來實現,不但使可變長度編碼表和 編碼符號可以程式化,更達到固定的解碼符號速 率,所以 MB Syntax Parser & MTM VLD 和 Symbol Decoders 是設計成以符號為基礎的同步,也就是 說每一個時脈週期, MB Syntax Parser & MTM VLD 都會解開一個編碼字元並送出相對應的符 號,而 Symbol Decoders 會將一個符號回復成為原 始資料,因此 MTM VLD 所解出來的符號可以利 刻送到 Symbol Decoders, 其間的暫存記憶體就不 需要,由位元資料流到原始資料的符號解碼程序 也達到固定的符號速率,即一個時脈週期一個符 號。後面的功能方塊,如 IDCT 和 MC,是以色素 點為基礎將影像解回來,大部分的現存設計中, 是使用 Inverse Scan (Iscan)暫存記憶體來完成 symbol decoders 和 IDCT 間不同資料速率的轉換, 並將 DCT 的係數由 1D 的數列轉成 2D 的矩陣,然 而讀寫 Iscan 暫存記憶體需要相當長的時間而使系 統整體效能下降,經由觀察自然影像壓縮的結 果,可以發現 IDCT 的輸入資料通常是一個稀疏的 矩陣,即大部分的係數都是零,所以不需要提供 完整的8×8DCT係數給IDCT模組,因此所提出 的影像解碼器架構是採用 ISDCT [6-8],除了只處 理非零的 DCT 係數外,並且還完成資料速率和型 態的轉換,使用的 ISDCT 是由 2 個 1D IDCT 和 2 個轉置記憶體 (TM) 所組成, 同時 Iscan 暫存記憶 體也用 Iscan 位址轉換器取代,將 RLD 所解出來 的 Iscan address 轉成 8×8 矩陣的 row-column address, 因為 1st IDCT 是接收 symbol decoder 所 提供的非零的 DCT 係數,因此 ISDCT 的輸入可以 是固定的符號速率,而輸出則是固定的色素點速 率,以符號為基礎的解碼流程由 MB syntax parser 延伸到 ISDCT 的 1st IDCT。

根據上述的資料型態分析,影像解碼器的功能 方塊可以分成 2 類,以符號為基礎和以色素點為 基礎,MB syntax parser、VLD、symbol decoders 和 1<sup>st</sup> IDCT 每一個時脈週期處理一個符號,2<sup>nd</sup> IDCT 和 MC 是 pixels-by-pixels 地完成它們的工 作,因為解壓縮程序是依序處理壓縮的資料,所 以 2 類功能方塊可以串接成為以符號和以色素點 為基礎的管線鏈 (pipeline chain), 而 ISDCT 內的 TM 則完成 2 管線鏈間的資料速率和型態轉換。此 外,管線級內的資料只有再下一級往前進時,才 會移到下一級,不然管線級會停滯以保持其內資 料,例如當 1st IDCT 可以接受資料時, symbol decoder 才送出 DCT 係數到 ISDCT, 否則整個以 符號為基礎管線鏈會停滯來保持有效的 DCT 係 數,另一方面,ISDCT 在 MC 可以收下資料時, 才會送解壓縮後的色素點過去,否則2nd IDCT會 停止讀取 TM 以保持有效的計算結果。根據上述 的管線化設計,功能方塊並不需要使用記憶體來 暫存其輸入輸出的資料,雖然如此,但是系統外 部仍需要暫存記憶體來儲存壓縮的位元資料流和 解壓縮後的色素點,以減少整個影像解碼器的停 滯時間。

因為所有的功能方塊被設計成以符號或以色素點為基礎的管線,所提出的影像解碼器並不需要整體的管線控制器來安排每個模組的工作,此點和現有的以 MB 或以 block 為基礎的管線不同,而為了正確地完成解碼的動作,會將每個解出來的符號貼上標籤,名為符號型態號碼(symbol type I.D.),然後將符號和其相對應的型態號碼一起在管線中傳遞,因此,資料會通過正確的路徑並且被適當的功能方塊所處理,舉例來說,如果一個符號被貼上 Run-Length Pair 的標籤,則此符號會被RLD, IDPCM, Iscan address converter, and IQ 解碼成為 DCT 係數,接著送到 ISDCT,但是如果符號是 贴上 motion vector 的標籤,它就會被MV\_decoder 所處理,而所得到的 MV 也會送到MC。

Fig. 1: The proposed video decompression architecture.

#### 四、功能方塊架構簡介

此節將會說明功能方塊 MB syntax parser & MTM VLD、Symbol Decoders 和 ISDCT 的架構設計, MB syntax parser & MTM VLD 與 Symbol Decoders 的互動會影響符號解碼程序的輸出率,

而 ISDCT 因為完成符號對色素點的轉換,所以決定了影像解碼器的解壓縮率,而 MC 是接收 Symbol Decoders 和 ISDCT 的輸出,不但重建影像,更控制其他功能方塊的動作。

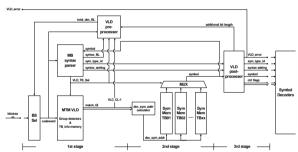

圖二為 MB syntax parser、MTM VLD 和 Symbol Decoders 的方塊圖,首先 bitstream selector (BS\_sel) 在暫存住的位元資料流中並選出編碼字 元給 MB syntax parser 和 MTM VLD, 若編碼字元 是固定長度的參數, parser 會直接解開;如果編碼 字元是可變長度編碼, parser 會認出所使用的編碼 表 (VLD TB sel), 然後編碼字元就會被 MTM VLD 解開,其編碼字元長度(CL)會回饋給 VLD pre-processor 以求得全部的解碼長度 (total\_dec\_BL),由於這些動作是在一個時脈週期 完成的,所以下一個編碼字元可以在下一個時脈 週期被 BS sel 找到,而達到一個時脈週期解出一 個符號的固定速率。在解編碼字元時, parser 會根 據位元資料流的前後文,替符號設定型態號碼, 後續的 Symbol Decoders 則根據這個訊息正確地將 送來的符號處理成 MB address, motion vector, DCT coefficient 和 row/column address。

Fig. 2: Block diagram of the MB syntax parser, MTM VLD, and symbol memories.

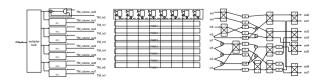

所採用的 ISDCT 包含 1st IDCT、2 個 TM 和 2nd IDCT,如圖三所示,由於 TM 必須存住 1st IDCT 的暫時計算結果,在所有的 DCT 係數都操作完畢,EOB\_in 為 1 時,TM 內的資料才是完整的 1st IDCT 結果,然後才能傳送到 2nd IDCT 作運算,而在 2nd IDCT 還沒有讀完 TM 內的 8 × 8 block 之前,1st IDCT 不可以使用這個 TM;因此使用 2個可交替的 TM,分別提供給 1st 和 2nd IDCT,ISDCT 的停滯時間大幅減少,使得解碼器的效率獲得有效的提昇。另外,2nd IDCT 使採用平行處理的架構,每次由 TM 讀取一個 column 的資料,接下來就同時處理此 8 個色素點,所以大幅增加影像解碼器的輸出率,而在降低時脈頻率時,仍然可以提供相當高的性能,以滿足低功率應用的需求。

Fig. 3: Schematic of the used ISDCT: (a) the 1<sup>st</sup> IDCT; (b) transpose memory; (c) the 2<sup>nd</sup> IDCT; (d) ISDCT with two TM.

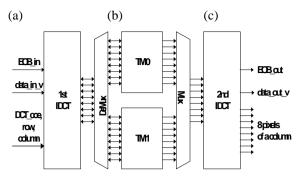

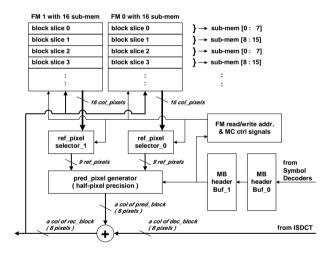

圖四為 MC & frame memories 的架構圖,為了減少其他功能方塊的停頓時間,此 MC 目標在同時接收一個符號和 8 個色素點,所以使用 2 個 MB header buffer,buf\_1 提供 header 給目前正在解碼的 MB,而 buf\_0 收集由 Symbol Decoders 傳來的下一個 MB header,使用這種設計,整個影像解碼器的停頓時間就可以大量減少;而 frame memory是由 16 個 sub-memory 所組成,一個 sub-memory 儲存一個 pixel row,因此可以一次就抓出 16 個 column pixels,選出所需要的 9 個 reference pixels,而可以一次就重建回 8×8 block 的一個 column。

Fig. 4: Block diagram of the MC & frame memories.

#### 五、結論與成果

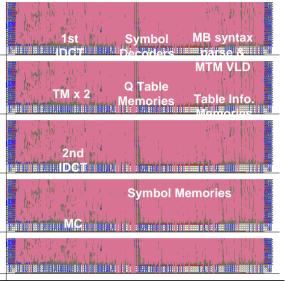

此論文提出以一個高效能影像解碼器的架構設計,其中包含 MB syntax parser & MTM VLD、Symbol Decoders、ISDCT 和 MC。因為使用以記憶體為基礎的功能方塊,此影像解碼器達到高度的可程式化,而可以滿足於各種解碼流程;功能方塊均是根據各個步驟的資料型態分析結果來設計,因此整個系統可以達到降低內部暫存記憶體需求和減少停滯時間的設計目標;然後將所有的功能方塊結合成以符號為基礎和以色素點為基礎的管線鏈,並且 ISDCT 包含 2 個 TM 和 8-in 8-out的 2nd IDCT,所以影像解碼緝獲得相當高的效

能。在使用 0.35-~m CMOS 製程的 cell library,影像解碼的時脈速率為 66MHz,此時達到 56.5Msps的符號字元解碼速率,而根據實際影像的測試結果,此解碼器的平均解壓縮率為 400M pixels/sec,所以此設計能夠滿足目前的應用需求,如數位相機、高畫質數位電視等,而所提出的硬體架構更可以被各種影像解碼系統所採用。

| Process       | TSMC 0.35~m SPQM CMOS     |          |

|---------------|---------------------------|----------|

| Cell          | TSMC 773 0.35~m 3.3V cell |          |

| Library       | library                   |          |

| Core size     | 4381 Î 4377 ~m²           |          |

|               | Parser & MTMVLD           | : 25k    |

|               | Symbol Decoders           | : 12k    |

|               | 1 <sup>st</sup> IDCT      | : 9k     |

|               | TM x 2                    | : 17k ×2 |

| Gate<br>Count | 2 <sup>nd</sup> IDCT      | : 25k    |

|               | MC                        | : 20K    |

|               | Total                     | : 125k   |

| Clock Rate    | 66MHz                     |          |

Fig. 5: Chip summary of the proposed video decoder.

### 六、參考文獻

- [1] Peter A. Ruetz, Po Tong, Daniel Luthi, and Peng H. Ang, "A Video-Rate JPEG Chip Set," *Journal of VLSI Signal Processing*, vol. 5, pp.141-150, 1993.

- [2] K. Kawahara, H. Yamauchi, and S. Okada, "A Single Chip MPEG1 Decoder," *IEEE Trans. on Consumer Electronics*, vol.41, issue 3, pp.707-715, Aug.1995.

- [3] Toshihiro Masaki, Yasuo Morimoto, Takao Onoye, and Isao Shirakawa, "VLSI Implementation of Inverse Discrete Cosine Transformer and Motion Compensator for MPEG2 HDTV Video Decoding," *IEEE Trans. on Circuits and Systems for Video Technology*, vol. 5, issue 5, pp. 387-395, Oct. 1995.

- [4] E. Brosz, R. Meyer, L. Phillips, and R. T. Ryan, "A Single-Chip HDTV Video Decoder Design," *IEEE Trans. on Consumer Electronics*, vol.44, issue 3, pp.519-526, Aug.1998.

- [5] L. Bolcioni, M. Borgatti, M. Felici, R. Rambaldi, and R. Guerrieri, "A low-power, voice-controlled, H.263 video decoder for portable applications," *IEEE Journal of Solid-State Circuits*, vol. 33, issue 11, pp. 519 526, Nov. 1998.

- [6] T. Onoye, G. Fujita, H. Okuhata, M. H. Miki, and I. Shirakawa, "Low-power implementation of H.324 audiovisual codec dedicated to mobile computing," in *Proc. of Asia and South Pacific Design Automation Conference 1998*, pp. 589-594, 1998.

- [7] Nam Ling, Nien-Tsu Wang, and Duan-Juat Ho, "An efficient controller scheme for MPEG-2 video decoder," *IEEE Transactions on Consumer Electronics*, vol. 44, issue 2, pp. 451–458, Dec.1998.

- [8] Jui-Hua Li and Nam Ling, "Architecture and Bus-Arbitration Schemes for MPEG-2 Video Decoder," *IEEE Trans. on Circuits and Systems for Video Technology*, vol. 9, issue 5, pp. 727-736, Aug. 1999.

- [9] Bai-Jue Shieh, "Area Efficient and High Throughput Memory-Based VLC Codec Designs," Ph.D Dissertation, National Chiao Tung University, June 2001.

- [10] Shu-Tzu Lin, "Analysis and Design of a High-Throughput Two Dimension Inverse Scan Discrete Cosine Transform Processor," Master Dissertation, National Chiao Tung University, June 2000.