# A Parabolic Potential Barrier-Oriented Compact Model for the $k_BT$ Layer's Width in Nano-MOSFETs

Ming-Jer Chen, Senior Member, IEEE, and Li-Fang Lu

Abstract—On the basis of a parabolic potential profile around the source-channel junction barrier of nanoscale MOSFETs, a new compact model is physically derived, which links the width of thermal energy  $k_BT$  layer (a critical zone in the context of the backscattering theory) to the geometrical and bias parameters of the devices. The proposed model is supported by experimental data and by a critical analysis of various simulation works presented in the literature. The only fitting parameter remains constant in a wide range of channel length (10–65 nm), gate voltage (0.4–1.2 V), drain voltage (0.2–1.2 V), and temperature (100 K–500 K). The confusing temperature-dependent issues in the open literature are straightforwardly clarified.

Index Terms—Backscattering, MOSFET, nanometer.

#### I. INTRODUCTION

W HILE applied to electrically saturated nanoscale MOSFETs, the channel backscattering theory [1], [2] establishes a link between the thermal energy  $k_BT$  layer, which occupies a small fraction of the conductive channel near the source, and the drive capability of the device. Thus, the ability to quantitatively determine the width of this critical zone is essential. To address the issue transparently, an analytically compact treatment is desirable. One such model can be quoted in the literature [3]

$$l \approx L \left(\frac{k_B T}{q V_D}\right)^{\alpha} \tag{1}$$

where *l* is the width of the  $k_BT$  layer, and *L* is the metallurgical channel length. However, so far, there has been some confusion as to the magnitude of the temperature power exponent  $\alpha$ . First of all, fitting of the room-temperature *I*–*V* characteristics of a simulation double-gate MOSFET has produced the apparent  $\alpha \approx 0.57$  [3]. Comparable  $\alpha \approx 0.5$  has also been obtained on experimental bulk n-MOSFETs in a temperature range of 233 K–298 K [4], [5]. In contrast, for the bulk case covering the same temperature range, a higher  $\alpha \approx 0.75$  has been

The authors are with the Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan, R.O.C. (e-mail: chenmj@faculty. nctu.edu.tw).

Color versions of one or more of the figures in this brief are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2008.919317

experimentally determined [6]. Even  $\alpha \approx 1$  has already been adopted in a temperature-dependent backscattering-coefficient extraction method [7]. This is also the case for the recent double-gate device simulation [8], which has shown that l is approximately proportional to the temperature from 100 K to 500 K. Obviously, these widespread values of the apparent  $\alpha$ must be clarified. On the other hand, a study on experimental bulk n-MOSFETs has revealed that l significantly decreases with increasing gate voltage [4], [6]; however, it is difficult for (1) to elucidate due to the lack of the gate voltage. This hurdle may be overcome by accurate modeling of the potential profile in the channel [9]; however, a simple approach without loss of accuracy is favored.

In this brief, the experimentally determined parabolic potential profile in the previous work [4], [5] will be utilized to approximate the source-channel junction barrier of nanoscale MOSFETs in saturation. Then, a new compact model will be physically derived for l with the channel length, gate overdrive, drain voltage, and temperature as input parameters. The validity and applicability of the resulting model will also be examined, followed by a significant clarification on the aforementioned  $\alpha$ differences.

### II. PARABOLIC BARRIER PICTURE

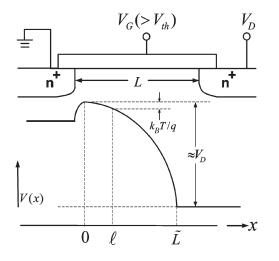

A parabolic potential profile near the source is schematically shown in Fig. 1. Its extension to the remaining channel can be described by

$$V(x) = V_D(x/L)^2.$$

(2)

The origin x = 0 indicates the peak of the barrier.  $\tilde{L}$  is the apparent channel length corresponding to a certain position where the parabolic potential drop from the top of the barrier is equal to  $V_D$ . Here, the barrier height with respect to the source side is neglected due to the large drain voltages used. By substituting x = l into (2) for a local potential drop of  $k_B T/q$  to constitute the thermal energy layer [1], [2], the following expression can be obtained:

$$l = \widetilde{L} \left(\frac{k_B T}{q V_D}\right)^{0.5}.$$

(3)

L is expected to be a function of the channel length, gate and drain voltage, and temperature. In other words, there exists a set

Manuscript received November 15, 2007; revised January 28, 2008. This work was supported by the National Science Council of Taiwan, R.O.C., under Contract NSC 96-2221-E-009-187. The review of this brief was arranged by Editor C. Jungemann.

Fig. 1. Schematic demonstration of the parabolic source-channel potential barrier picture corresponding to nano-MOSFET in saturation. The parabolic potential profile is extended to the drain side to highlight the apparent channel length designated by  $\widetilde{L}$ . Also shown is the width *l* of the  $k_BT$  layer.

of the specific gate and drain voltage denoted by  $V_{\rm Go}$  and  $V_{\rm Do}$ , respectively, at a given temperature  $T_o$ , which can ensure that L = L. The corresponding thermal energy layer has a width denoted by  $l_o$ , which can be calculated from (3) with  $L \to L$ ,  $T \rightarrow T_o$ , and  $V_D \rightarrow V_{\rm Do}$ . Then, if the temperature individually changes from  $T_o$  to T, a power-law relation can hold:  $L = L(T/T_o)^{0.5}$ . This formalism can be obtained by assuming that the potential profile does not change with temperature; that is, the local electric field across the thermal energy layer  $(\approx k_B T_o/ql_o, \text{ according to the backscattering theory [1], [2])}$ at  $T_o$  is approximately equal to that  $(\approx k_B T/ql)$  at T. As for gate-voltage factor, a similar relation can be physically derived but expressed in terms of the gate overdrive (the gate voltage  $V_G$  minus the threshold voltage  $V_{\rm th}$ ). This is achieved by twice differentiating (2) with respect to x, leading to  $d^2V(x)/dx^2 =$  $2V_D/\tilde{L}^2$ , which, according to Poisson's equation (see [3] for details), can be linearly related to the underlying inversion-layer carrier density or, equivalently, the gate overdrive. As a result, one achieves  $\tilde{L} = L((V_{\rm Go} - V_{\rm th})/(V_G - V_{\rm th}))^{0.5}$ . Here, the term  $V_{\rm Go} - V_{\rm th}$  represents the specific gate overdrive for L approaching L. Finally, if the drain voltage increases to  $V_D(>V_{\rm Do})$ , the local electric field  $[=2V_D x/\tilde{L}^2$  as from (2)] must be larger than that  $(=2V_{\rm Do}x/L^2)$  at  $V_{\rm Do}$ . As a result, one obtains  $\widetilde{L} = L(V_D/V_{\rm Do})^{\nu}$  with the power exponent  $\nu$  of no more than 0.5. This formula remains valid for  $V_D < V_{Do}$ . Indeed,  $\nu$  of around 0.25 has been experimentally determined elsewhere [4] and will be cited here.

Through the combination of the aforementioned power-law relationships, a unique expression can be created for  $\widetilde{L}$

$$\widetilde{L} = \eta L \frac{V_D^{0.25}}{(V_G - V_{\rm th})^{0.5}} \left(\frac{k_B T}{q}\right)^{0.5}.$$

(4)

Here,  $\eta = (k_B T_o/q)^{-0.5} (V_{\rm Go} - V_{\rm th})^{0.5} V_{\rm Do}^{-0.25}$ . In this brief,  $\eta$  is fixed and is also the only fitting parameter. It is expected that  $\eta$  is a constant, regardless of the channel length, gate and drain voltage, and temperature; otherwise, the applicability of the resulting model may be limited.

#### **III. CONFIRMATIVE EVIDENCE AND CLARIFICATION**

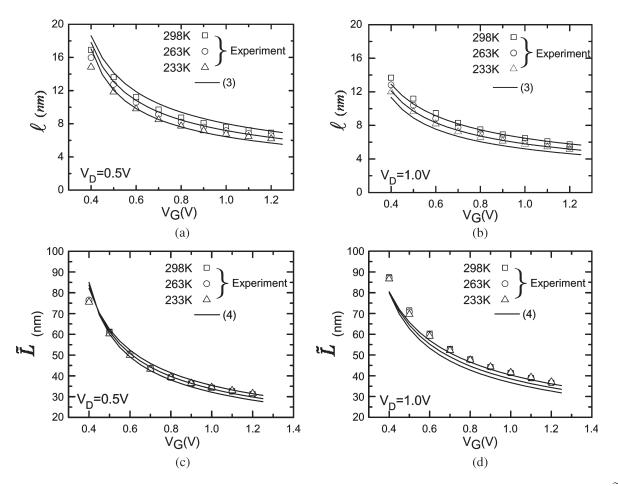

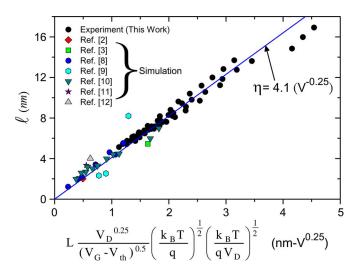

The experimental l was created from 55-nm bulk n-MOSFETs by means of a parameter extraction process detailed elsewhere [4]–[6]. The results are shown in Fig. 2 versus gate voltage for two drain voltages of 0.5 and 1.0 V and three temperatures of 233 K, 263 K, and 298 K. With known l, T, and  $V_D$ , the corresponding L can be obtained directly from (3), as shown in Fig. 2(c) and (d) versus the gate voltage. The near-equilibrium threshold voltages denoted by  $V_{\rm tho}$  are 0.360, 0.345, and 0.328 V for 233 K, 263 K, and 298 K, respectively, and the drain-induced barrier lowering (DIBL) magnitudes are 120, 123, and 130 mV/V, respectively. Throughout this brief, the threshold voltage  $V_{\rm th}$  at higher drain voltages is equal to  $V_{\rm tho} - \text{DIBL} \times V_D$  [4]–[7]. Also shown in Fig. 2 are the calculated results from (3) and (4) using a specific  $\eta$  whose value will be explained slightly later. On the other hand, the rich literature [8], [10] dedicated to double-gate device simulations is quoted. First, in [8], the extracted l at  $V_D = V_G = 1$  V is available in a wide range of the channel length from 14 to 37 nm and the temperature from 100 K to 500 K. The underlying threshold voltage  $V_{\rm tho}$  and DIBL are reasonably 0.3 V and 110 mV/V, respectively [10]. Second, the citation [10] can further provide the relevant data at 300 K: l from 2.0 to 7.0 nm, L from 14 to 65 nm,  $V_D(=V_G)$  from 1.0 to 1.2 V, and DIBL from 11 to 230 mV/V. In addition, we have also extracted l directly from the published channel potential profiles on the simulation double-gate devices [2], [3], [9], [11], [12]. The corresponding key parameters are the following: 1) L = 10 nm,  $V_{\text{tho}} \approx 0.33$  V, DIBL  $\approx 140$  mV/V,  $V_D = 0.6 \text{ V}, V_G = 0.6 \text{ V}, \text{ and } T = 300 \text{ K}$  [2]; 2) L = 20 nm, $V_{\rm tho} \approx 0.33$  V, DIBL  $\approx 25$  mV/V,  $V_D = 0.2$  V,  $V_G = 0.55$  V, and T=300 K [3]; 3) L=25 nm,  $V_{\rm tho}\approx 0.3$  V, DIBL  $\approx$ 100 mV/V,  $V_D = 0.8$  V,  $V_G = 0.5$ , 0.8, and 1.0 V, and T =300 K [9]; 4) L = 15 nm,  $V_{\text{tho}} \approx 0.2$  V, DIBL  $\approx 120$  mV/V,  $V_D = 0.7$  V,  $V_G = 0.7$  V, and T = 300 K [11]; and 5) L =15 nm,  $V_{\rm tho} \approx 0.3$  V, DIBL  $\approx 77$  mV/V,  $V_D = 0.7$  V,  $V_G =$ 0.7 V, and T = 300 K [12]. At this point, a scatter plot can be created, as shown in Fig. 3, in terms of the experimental and simulated l versus the quantity of the functional expression  $LV_D^{0.25}(V_G - V_{\rm th})^{-0.5} (k_B T/q)^{0.5} (k_B T/q V_D)^{0.5}$ . Strikingly, all data are seen to fall on or around a straight line. The slope of the line furnishes  $\eta$  with a value of 4.1 V<sup>-0.25</sup>. As expected,  $\eta$  remains constant, regardless of the channel length, gate and drain voltage, and temperature.

Some remarks can now be made to clarify the confusing  $\alpha$  values in the open literature [3]–[8]. First, it is noticed that in the case of bulk n-MOSFET, two different values of  $\alpha$  were produced: one of 0.5 [4], [5] and one of 0.75 [6]. This difference can be attributed to the different subband treatments during the parameter extraction process. A Schrödinger–Poisson equation solving was utilized in [4] and [5], whereas in [6], this was done by a triangular potential approximation [13]. Therefore, the different subband levels can lead to different average thermal injection velocities, which in turn give rise to different *l* values. Second, based on (4), the temperature range of 233 K–298 K in case of a 55-nm bulk device [4], [5] is not large enough to affect the calculated  $\tilde{L}$ . In other words,  $\tilde{L}$  is considerably

Fig. 2. Measured and calculated *l* versus gate voltage at two drain voltages of (a) 0.5 V and (b) 1.0 V for three temperatures and the corresponding  $\tilde{L}$  versus gate voltage for the drain voltages of (c) 0.5 V and (d) 1.0 V. The test device is a 55-nm bulk n-MOSFET. The calculation lines are from (3) and (4) with  $\eta = 4.1 \text{ V}^{-0.25}$ .

Fig. 3. Scatter plot of the experimental and simulated l versus the quantity of the functional expression  $L(V_D^{0.25})(V_G - V_{\rm th})^{-0.5}(k_B T/q)^{0.5}$ . Also shown is a straight line which fits the data points. The slope of the line yields  $\eta$  of 4.1 V<sup>-0.25</sup>.

insensitive to such a narrow temperature range. Consequently, the resulting apparent temperature power exponent was limited to 0.5, as reported in the previous work [4], [5]. Indeed, with the known  $\eta$  as input, fairly good reproduction can be achieved,

as shown in Fig. 2, without adjusting any parameters. The same interpretations also apply to the  $\alpha \approx 0.57$  case [3]. Only the room temperature of operation was involved, and therefore, the temperature effect of  $\tilde{L}$  can no longer be examined. In other words, only in a wide temperature range (as done in the comprehensive study of [8] and [10]) can the linear relationship of  $l \propto T$ , as shown in Fig. 3, be observed. Finally, from the aspect of temperature dependences or the excellent coincidence with a significant number of data, as shown in Fig. 3, the existing backscattering-coefficient extraction method [7] is valid.

## **IV. CONCLUSION**

Based on a parabolic potential profile that is used to approximate the source-channel junction barrier of nanoscale MOSFETs, a new compact model of the  $k_BT$  layer's width has been physically derived along with the channel length, gate overdrive, drain voltage, and temperature as input. The validity of the parabolic potential barrier picture and the applicability of the resulting compact model have been justified by experimental data and by a critical analysis of various simulation works presented in the literature. In particular, the confusing temperature-dependent issues in the open literature have been satisfactorily clarified.

#### REFERENCES

- M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," *IEEE Electron Device Lett.*, vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [2] M. Lundstrom and Z. Ren, "Essential physics of carrier transport in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 1, pp. 133–141, Jan. 2002.

- [3] A. Rahman and M. S. Lundstrom, "A compact scattering model for the nanoscale double-gate MOSFET," *IEEE Trans. Electron Devices*, vol. 49, no. 3, pp. 481–489, Mar. 2002.

- [4] M. J. Chen, R. T. Chen, and Y. S. Lin, "Decoupling channel backscattering coefficients in nanoscale MOSFETs to establish near-source channel conduction-band profiles," in *Proc. Silicon Nanoelectronics Workshop*, Jun. 2005, pp. 50–51.

- [5] M. J. Chen, S. G. Yan, R. T. Chen, C. Y. Hsieh, P. W. Huang, and H. P. Chen, "Temperature-oriented experiment and simulation as corroborating evidence of MOSFET backscattering theory," *IEEE Electron Device Lett.*, vol. 28, no. 2, pp. 177–179, Feb. 2007.

- [6] M. J. Chen, H. T. Huang, Y. C. Chou, R. T. Chen, Y. T. Tseng, P. N. Chen, and C. H. Diaz, "Separation of channel backscattering coefficients in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 9, pp. 1409–1415, Sep. 2004.

- [7] M. J. Chen, H. T. Huang, K. C. Huang, P. N. Chen, C. S. Chang, and C. H. Diaz, "Temperature dependent channel backscattering coefficients in nanoscale MOSFETs," in *IEDM Tech. Dig.*, Dec. 2002, pp. 39–42.

- [8] P. Palestri, D. Esseni, S. Eminente, C. Fiegna, E. Sangiorgi, and L. Selmi, "Understanding quasi-ballistic transport in nano-MOSFETs: Part I—Scattering in the channel and in the drain," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2727–2735, Dec. 2005.

- [9] E. Fuchs, P. Dollfus, G. L. Carval, S. Barraud, D. Villanueva, F. Salvetti, H. Jaouen, and T. Skotnicki, "A new backscattering model giving a description of the quasi-ballistic transport in nano-MOSFET," *IEEE Trans. Electron Devices*, vol. 52, no. 10, pp. 2280–2289, Oct. 2005.

- [10] S. Eminente, D. Esseni, P. Palestri, C. Fiegna, L. Selmi, and E. Sangiorgi, "Understanding quasi-ballistic transport in nano-MOSFETs: Part II—Technology scaling along the ITRS," *IEEE Trans. Electron Devices*, vol. 52, no. 12, pp. 2736–2743, Dec. 2005.

- [11] J. Saint-Martin, A. Bournel, and P. Dollfus, "On the ballistic transport in nanometer-scaled DG MOSFETs," *IEEE Trans. Electron Devices*, vol. 51, no. 7, pp. 1148–1155, Jul. 2004.

- [12] D. Querlioz, J. Saint-Martin, K. Huet, A. Bournel, V. Aubry-Fortuna, C. Chassat, S. Galdin-Retailleau, and P. Dollfus, "On the ability of the particle Monte Carlo technique to include quantum effects in nano-MOSFET simulation," *IEEE Trans. Electron Devices*, vol. 54, no. 9, pp. 2232–2242, Sep. 2007.

- [13] K. N. Yang, H. T. Huang, M. C. Chang, C. M. Chu, Y. S. Chen, M. J. Chen, Y. M. Lin, M. C. Yu, S. M. Jang, C. H. Yu, and M. S. Liang, "A physical model for hole direct tunneling current in p<sup>+</sup> poly-gate pMOSFETs with ultrathin gate oxides," *IEEE Trans. Electron Devices*, vol. 47, no. 11, pp. 2161–2166, Nov. 2000.

**Ming-Jer Chen** (S'78–M'85–SM'98) received the B.S. degree in electrical engineering (with highest honors) from the National Cheng Kung University, Tainan, Taiwan, R.O.C., in 1977, and the M.S. and Ph.D. degrees in electronics engineering from the National Chiao Tung University (NCTU), Hsinchu, Taiwan, in 1979 and 1985, respectively.

Since 1985, he has been with the Department of Electronics Engineering, NCTU, where he has been a Full Professor since 1993. From 1987 to 1992, he was a Consultant for the Taiwan Semiconductor

Manufacturing Company, where he led a team from the NCTU and the Electronics Research and Service Organization/Industrial Technology Research Institute to build up a series of process windows and design rules. From 2000 to 2001, he was a Visiting Professor with the Department of Electrical Engineering, Stanford University, Stanford, CA. He is the holder of eight U.S. patents and six Taiwanese patents in the field of the high-precision analog capacitors, 1-T memory cell, dynamic threshold MOS, electrostatic discharge protection, and Flash memory. He has graduated 14 Ph.D. students and more than 90 M.S. students. His current research interests include semiconductor device physics and nanoelectronics.

Dr. Chen is a member of the Phi Tau Phi.

Li-Fang Lu was born in Taoyuan, Taiwan, R.O.C., in 1982. He received the B.S. degree in electrophysics from the National Chiao Tung University, Hsinchu, Taiwan, in 2006, where he is currently working toward the M.S. degree in the Department of Electronics Engineering.

His main research interest is on the physics about backscattering theory in nanoscale devices.