## 量子點的電荷分佈與放射率的電性物理研究

Studies of carrier distribution and emission in quamtum dots

計畫編號: NSC89-2112-M-009-060

執行期間:89 年 08 月 01 日至 90 年 07 月 31 日個別型計畫:計畫主持人:陳振芳 交大電子物理系教授

### 一.中文摘要

[關鍵字:砷化鎵、量子點臨界厚度、單層、分子束磊晶]

本計畫用電性量測來研究不同厚度 single QD與 superlattice QDs。從I-V的量 測中我們發現superlattice QDs樣品的漏電 流比single ODs樣品的漏電流還大。C-V量 測中可觀察到InAs厚度3.4ML的single QD 樣品有載子空乏的現象,可知3.4ML的 single QD樣品已經晶格鬆弛了。我們在 InAs量子點厚度7.56Å的 Superlattice QDs 樣品中觀察到兩個載子堆積的地方,其峰 值位置相差500Å,與其InAs量子點層與層 間的距離相同,但是溫度下降時,觀察到 自由載子濃度下降,推論是晶格鬆弛所造 成的。另外Superlattice ODs RTA(rapid thermal annealing)過後樣品在變溫C-V量 測中,觀察到峰值的位移量隨RTA溫度升 高而減小。對single QD 3.4ML的樣品做 DLTS量測,觀察到3種缺陷,其中活化能 為0.63eV缺陷在彈性應變的GaAs塊材當 中也有量測到,而活化能為0.51eV和 0.37eV的缺陷則在1000ÅIn<sub>0.2</sub>Ga<sub>0.8</sub>As /GaAs單層量子井結構中也有量到類似的 缺陷,是由於晶格鬆弛所產生的缺陷。對 superlattice QDs樣品做DLTS的量測發現 了兩個缺陷能階,其中活化能為0.54eV的 缺陷就是我們在S2樣品中量測到的0.51eV 的缺陷。而活化能為0.39eV的缺陷只分布 於樣品的表面,RTA的樣品觀察到0.51eV 和0.39eV的缺陷濃度下降。

# 英文摘要

(keyword:GaAs InAs quamtum dot critical thickness, monolayer, MBE)

The samples of single InAs/GaAs QD and superlattice InAs/GaAs QDs with RTA (rapid thermal annealing) at different temperature are investigated by capacitance-voltage (C-V) and deep-level transient spectroscopy (DLTS) measurement.

TheC-V measurement shows carrier confinement for 2.3ML single QD and 7.56Å superlattice QDs samples. And the

carrier depletion by lattice relaxation is observed in 3.4ML OD sample. For the 2.3ML single QD sample, the quantum-confinement peak concentration at low temperature is higher than at room temperature. However, in superlattice QDs, the quantum peak concentration is found lower at low temperature than at room temperature. These effects are found to reduce for samples after annealing at high temperature. In contrast with the 2.3ML single QD sample which no traps is found, three traps at 0.63, 0.51 and 0.37eV are detected in the 3.4ML single QD sample. The trap at 0.63eV has been found in plastic deformation GaAs bulk material. The traps at 0.51 and 0.37eV are found similar to the traps observed in relaxed 1000Å In<sub>0.2</sub>Ga<sub>0.8</sub>As/GaAs single quantum well structure and are suspected to be related to lattice relaxation. In superlattice QDs samples, two traps at 0.39 and 0.54eV are detected. The trap at 0.54eV is similar to the 0.51eV trap found in 3.4ML single QD indicating that the superlattice QD sample is relaxed. Moreover the concentration of both

## 二.計畫源由與目的

traps can be decreased with increasing RTA

temperature.

異質接面材料,如 InGaAs/GaAs、InAs/GaAs 都存在著晶格不匹配的問題,超過臨界厚度時就會產生差排,堆疊錯誤等缺陷的產生,一般對於這種材料的長晶和光性部分的參考資料不少,但是對於電性方面的文獻卻比較缺乏,所以對於超過臨界厚度而應力鬆弛的量子點的缺陷能階是很有趣的課題。另外超過臨界厚度的DWELL 結構的量子點對樣品缺陷的影響和沒有 DWELL 結構的量子點,其缺陷在電性上有何差異,這些都是引起我們興趣

#### 的問題。

# 三.研究方法與成果 晶體成長與元件製作

多層量子點的部份一樣是以分子束 磊晶(Molecular beam epitaxy)設備來成長, 也是以 n-type 高濃度矽摻雜 GaAs 晶片為 基板、長晶過程如下

- 1) 加熱到580 ,然後成長GaAs (矽摻雜 5 x 10<sup>16</sup>cm<sup>-3</sup>)層20分鐘。

- 2) 降溫至500 ,再長InAs QDs 22秒,約 0.56Å。

- 3) 成長In<sub>0.15</sub>Ga<sub>0.85</sub>As(鈹摻雜5 x 10<sup>16</sup>cm<sup>-3</sup>) 進行覆蓋QDs的動作,時間 一樣是22秒。

- 4) 接著在相同500 溫度下成長GaAs 20 秒,然後升溫至550 ,再繼 續長GaAs至500Å。

- 5) 重複步驟2) ~ 4) 兩次,所以共有三個週 期的InAs QDs。

- 6) 最後成長GaAs Cap layer 2000 Å(矽摻雜 5 x 10<sup>16</sup>cm<sup>-3</sup>)。

之後再進行快速熱退火(RTA: Rapid Thermal Annealing)的處理,過程中以面對面的方式覆蓋 GaAs Wafer 來進行,這樣能減少在退火的過程中從表面脫離的砷量。退火分別在 600 ,700 ,800 三種不同溫度下進行,時間都是 1 分鐘。然後進行電極的製作。電極製作前要先清洗晶片,若清洗不乾淨將會影響電極金屬和半導體的接面好壞,進而影響電性量測的準確性。

#### 方法與成果

晶片清洗完後,我們開始在晶片表面製作 schottky diode,我們所鍍的材料是鋁,製作方法有兩個系統,一種是熱蒸鍍系統,將金屬光罩(mask)覆蓋在樣品表面,固定在 mask hold上,然後將 hold和欲鍍物(鋁)一起放進 chamber 中,再用pump 將 chamber 內壓力抽至 3x10<sup>-6</sup> torr,然後加熱鋁使其汽化然後鍍在樣品表面上,即完成 schottky contact 的製作。

## 四.討論與結論

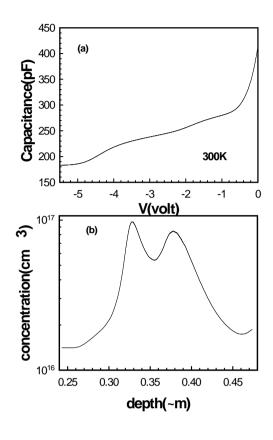

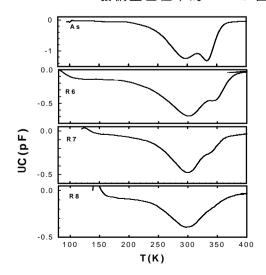

圖一(a)是As樣品的C-V圖,可以看到-1V~-2V之間有一平台,-3v~-4V有另一個平台,圖一(b)是由As樣品的C-V量測所換算出來的縱深分布圖,可以看到在有兩個載子堆積的部分,兩個峰值相距0.05 µm,剛好是在結構上兩層InAs量子點的距離,故推測是量子點的量子侷限效應,但是在結構上應該有三層量子點而我們只看到兩個峰值,這是因為我們在製作元件時

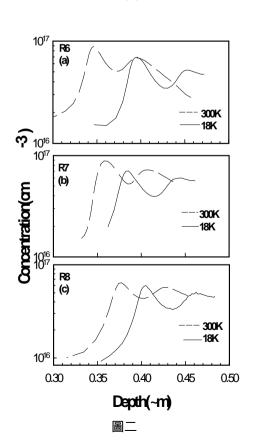

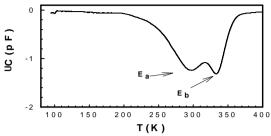

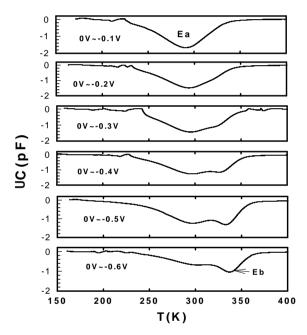

所能加的偏壓有一個極限,加太大的偏 壓,會產生很大的漏電流,對於樣品和儀 器會造成損害,所以是其量測範圍有限 制,不能量測到第三層的量子侷限效應。 另外,我們可以看到兩個峰值的濃度不 同,第一個峰值的濃度比第二個峰值的濃 度高,這種特性和電荷中和狀態有關。圖 二分別是R6、R7、R8樣品的C-V量測和縱 深分佈圖,由C-V圖可以知道,隨著RTA 溫度的升高,低溫和室溫電容的差異越 小,換算成載子濃度來看,其室溫下四片 樣品的差異性不大,但是在低溫時可以發 現,隨著RTA溫度的升高,量子侷限的峰 值位移量從600 的0.056 µ m、700 的 0.045 µ m到800 的0.027 µ m逐漸變小, 而且在低溫時量子侷限的電子濃度隨著 RTA溫度升高而越來越接近室溫時的電子 濃度,根據這些觀察到的現象,我們推測 RTA有填補樣品中缺陷的功能, 使得被缺 陷捕獲的載子數目隨著RTA溫度提高而越 來越少、故其自由載子濃度會提高。圖三 是As樣品的DLTS訊號圖,可以清楚的看 到有兩個不同的峰值E。和E。, 而圖3-18是 As樣品的阿瑞尼司圖,其活化能和捕獲截 面積分別是Ea: 0.39 eV (3.98 x 10<sup>-17</sup>cm<sup>2</sup>)、  $E_b: 0.54 \text{ eV} (9.69 \times 10^{-16} \text{ cm}^2)$ ,其中 $E_b$ 的活 化能和捕獲截面積跟我們在S2樣品中量 測到的E2缺陷很接近。圖四是量測的結 果,發現在超過-0.5V後,Ea的訊號明顯的 變小了, 而在0V~0.1V如此小的範圍內Ea 的訊號最強,而缺陷濃度和 C成正比, 由此可知Ea在As樣品內存在於樣品的表 面。圖五是As系列樣品的DLTS訊號圖 由圖中鋒值位置可以判斷並沒有新的缺陷 能階的產生,而350K附近的缺陷能階訊號 隨著RTA溫度升高而越來越小,到RTA溫 度800 時其訊號已經不是非常明顯了。從 活化能和捕獲截面積來比較, R6、R7、R8 樣品所量測到的就是Ea和Ebo

樣品 編號 退火溫 Schot tky 度( doide 面積 多 As-grown As >層量子: 0.007854 **RTA600** R6 600 RTA700 R7 700  $(cm^2)$ 點 **RTA800** R8 800

圖三 As 樣品的 DLTS 訊號圖,填充 偏壓和觸發偏壓為 0V/-0.5V

圖四 As 樣品在不同填充偏壓和觸發偏壓差值下的 DLTS 圖

圖五 As、R6、R7、R8樣品的DLTS訊號圖,填充偏壓和觸發偏壓別是0V/-0.5V