## 行政院國家科學委員會補助專題研究計畫成果報告

# 在雙極性/互補式金氧半/雙擴散金氧半(BCD)技術中雙擴散金氧半(DMOS)之最佳化設計與製造

計畫類別: 個別型計畫 整合型計畫

計畫編號:NSC 89 - 2215 - E - 009 - 109 -

執行期間: 89 年 8 月 1 日至 90 年 7 月 31 日

計畫主持人:鄭晃忠教授 國立交通大學電子工程研究所

共同主持人:徐清祥教授 國立清華大學電機工程研究所

徐永珍教授 國立清華大學電機工程研究所

## 本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份 赴大陸地區出差或研習心得報告一份 出席國際學術會議心得報告及發表之論文各一份 國際合作研究計畫國外研究報告書一份

執行單位:國立交通大學電子工程研究所

中 華 民 國 90 年 10 月 20 日

# 行政院國家科學委員會專題研究計畫成果報告

在雙極性/互補式金氧半/雙擴散金氧半(BCD)技術中雙擴散金氧半(DMOS)之最佳化設計與製造

## **Optimal DMOS Design and Fabrication in BCD Technology**

計畫編號: NSC 89-2215-E-009-109

執行期限:89年8月1日至90年7月31日

主持人:鄭晃忠教授 國立交通大學電子工程研究所

共同主持人:徐清祥教授 國立清華大學電機工程研究所

徐永珍教授 國立清華大學電機工程研究所

#### 一、中文摘要

本子計劃的目的是以雙極性/互補式金氧半/雙擴散金氧半(BCD)技術,開發出高耐壓,低導通阻抗的垂直型雙擴散金氧半電晶體(VDMOS)。本次計劃最後如預期,發展出耐壓 60v 的 VDMOS。

關鍵詞: 雙極性/互補式金氧半/雙擴散金氧半技術、垂直型雙擴散金氧半電晶體、功率電晶體

#### **Abstract**

The goal of this project was to develop a high-voltage and low on-resistance vertical double-diffuse MOSFET (VDMOS) based on bipolar/CMOS/DMOS (BCD) technology. As expected, we developed a 60v-rated VDMOS.

**Keywords**: BCD, VDMOS, power MOS

#### 二、緣由與目的

隨著系統整合的需求日益增加,如何 將功率電晶體(power MOS)整合於互補式 金氧半電晶體(CMOS)或是雙極性/互補式 金氧半電晶體(BiCMOS)的重要性也雖之 增加。本次計劃基於此緣由,希望在雙極 性/互補式金氧半/雙擴散金氧半(BCD)技術 中,開發出耐壓 60v,低導通阻抗的垂直型 雙擴散金氧半電晶體(VDMOS)。雖然去年 度計劃因人為疏失,並未如期達到目標, 今年度加以檢討改進,最後終能如期,以 BCD 技術開發出耐壓 60v 的 VDMOS。

#### 三、研究結果與討論

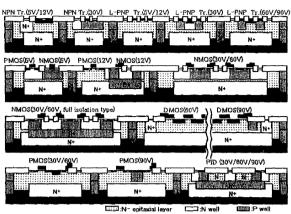

將 power MOS 整合於 CMOS 或BiCMOS 電路的構想如圖一[1]所示,這樣整合最大的好處便是無須再將電路系統、電源控制開關和控制電路結合於電路板上,如此便可大大的降低生產成本,並縮減整體電路完成的時間。

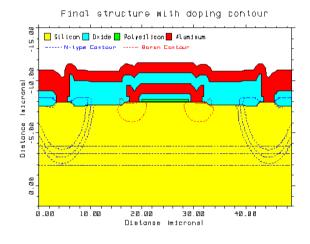

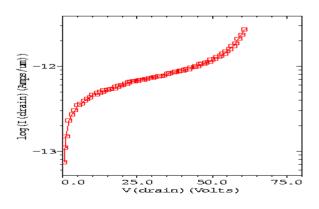

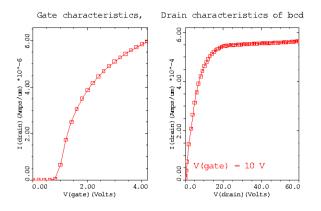

首先,我們使用 TMA[2]作製程與電性模擬,以廠商提供的製程條件模擬出符合要求的元件結構及其電特性。圖二是使用 tsuprem4 作製程模擬的 VDMOS 結構,圖中,黃色代表 silicon,水藍色是氧化層,綠色代表多晶矽,紅色是金屬層。圖三是用 medici 作電性模擬的崩潰特性,由圖可以知道這元件的崩潰電壓約在  $55v \sim 60v$  間。圖四是其導通特性,包含 Id 對 Vg 作圖(Vd=0.1v)和 Id 對 Vd 作圖(Vg=10v),從 Id 對 Vg 的圖形中可以知道這元件的臨界電壓約 0.7v 左右,可直接由 CMOS 電路控制其開關。

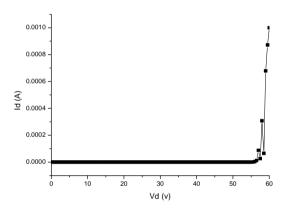

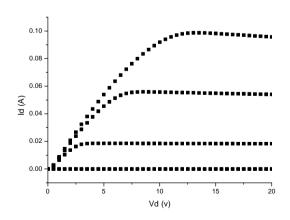

今年度本著去年度的經驗,仔細討論過後並從新佈局,終能完成元件。圖五是完成的元件的崩潰特性,如預期般,這次所得的元件的崩潰電壓約為 57v 左右,與模擬結果相若。圖六是元件得導通特性曲線,當 Vg=10v,其阻抗約為  $105\Omega$ ,再乘以元件面積(32800um2),則此元件的導通阻抗約為  $34m\Omega.cm2$ ,這個阻值比起模擬和一般文獻[3]都偏高許多,我們歸納原因,

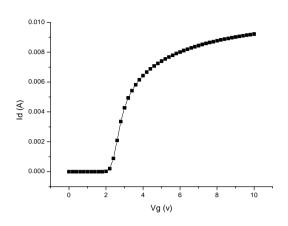

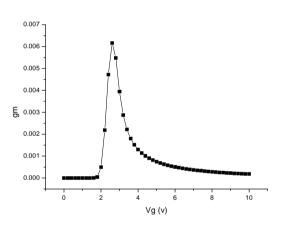

可能是由於今年佈局比較保守所致。圖七與圖八分別是 Id 對 Vg (Vd = 1v)及 gm 對 Vg (Vd = 1v)的特性曲線,由這兩圖可以知 道元件的臨界電壓為 2.1v - 1v = 1.1v,與 模擬結果相似。

#### 四、計劃成過自評

本次計劃最後終能完成預期目標,得到一個耐壓 60v 的 VDMOS。去年度的疏失,我們今年加以檢討改進,從新佈局,終能達到目標。但由於佈局時過於小心,保守,耐壓雖然達到目標,但導通阻值卻非最佳化而比模擬和一般文獻略高,算是這次計劃的最大遺憾。

### 五、參考文獻

- [1] Tomohide Terashima, Fumitoshi Yamamoto, and Kenichi Hatasato, "Multi-voltage device integration technique for 0.5um BiCMOS & DMOS process", IEEE 2000, pp.331 ~ pp.334

- [2] TMA user's manual, July 1998

- [3] Liang Y. C., Gan K. P., Samudra G..S., "Oxide-bypassed VDMOS (OBVDMOS): an alternative to superjunction high voltage MOS power devices ", IEEE 2001, pp.407 ~ pp.409

圖一 各種高耐壓電晶體(VDMOS, LDMOS)和 CMOS 與 BiCMOS 整合的示意圖

圖二 VDMOS 結構圖

圖三 模擬的崩潰特性(Bv~55v-60v)

圖四 左圖為模擬的 Id 對 Vg 曲線(Vd = 0.1v),右 圖為模擬的 Id 對 Vd 曲線(Vg = 10v)

圖七 元件的 Id 對 Vg 曲線(Vd = 1v)

圖五 元件的崩潰特性(BV = 57v)

圖八 元件的 gm 對 Vg 曲線(Vd = 1v)

圖六 元件的導通特性曲線