# 行政院國家科學委員會補助專題研究計畫成果報告

## 金屬閘極之功函數工程

Work Function Engineering of Metal Gate Electrode

計畫類別： 個別型計畫 整合型計畫

計畫編號：NSC 89 - 2215 - E - 009 - 106

執行期間：89年08月01日至90年07月31日

計畫主持人：崔秉鉞

共同主持人：無

本成果報告包括以下應繳交之附件：

赴國外出差或研習心得報告一份

赴大陸地區出差或研習心得報告一份

出席國際學術會議心得報告及發表之論文各一份

國際合作研究計畫國外研究報告書一份

執行單位：國立交通大學 電子工程學系

中 華 民 國 90 年 09 月 28 日

# 行政院國家科學委員會專題研究計畫成果報告

## 金屬閘極之功函數工程

### Work Function Engineering of Metal Gate Electrode

計畫編號：NSC 89-2215-E-009-106

執行期限：89年08月01日至90年07月31日

主持人：崔秉鉞 交通大學 電子工程學系

共同主持人：無

計畫參與人員：方國龍、黃誌鋒、楊鎮吉 交通大學電子研究所

#### 一、中文摘要

氮化鉭薄膜的功函數可以藉由調變氮/鉭的比例來調整，但調變幅度小於 0.07 電子伏特。金屬閘極如銅或鉑的熱應力對平帶電壓的控制影響很大。在製程溫度下無明顯相轉變或晶粒成長的非晶態的金屬閘極如鉭或氮化鉭可以明顯降低平帶電壓的變異。本計畫並確認平帶電壓的變異是選擇金屬閘極材料以及決定元件製程整合方式的重要因子。

**關鍵詞：**金屬閘極、功函數、臨界電壓

#### Abstract

The work function of TaNx film can be adjusted by varying the N/Ta ratio. But the magnitude of adjustment is less than 70mV. The thermal stress of metal gate, such as Cu and Pt. has great impact on the  $V_{fb}$  control such as Cu and Pt. Furthermore, amorphous metals with minimum phase transformation and grain growth such as Ta and TaN are preferred to minimize the  $V_{fb}$  deviation. The flat-band voltage deviation is an important factor to choose metal gate materials and to determine integration scheme.

**Keywords:** Metal Gate, Work Function, Threshold Foltage

#### 二、緣由與目的

1970 年代複晶矽閘(poly-Si gate)取代鋁金屬閘(Al-gate)後，因為複晶矽閘可與源極 / 沖極 (source/drain) 自動對準 (self-align) 的特性，加速金氧半場效電晶

體(MOSFET)微縮的速度[1]。二十多年來，金氧半場效電晶體成功的微縮了 100 倍。但是微縮到 0.1 微米以下時，複晶矽閘面臨許多不易克服的問題。包括複晶矽空乏(poly-Si depletion)[2-4]、P 型電晶體的硼穿透問題[5-7]、以及複晶矽的電阻係數偏高等。

金屬閘極可以同時解決上述三項問題。但是在次 0.1 微米世代元件應用上，金屬閘技術有下列問題待研究：(1) 臨界電壓(threshold voltage,  $V_{th}$ )控制、(2) 金屬與高介電常數材料相容性、(3) 金屬閘圖案化技術、(4) 金屬污染控制。這些問題中，除第一項外，均屬高度整合性的問題，部份關鍵模組在學術單位尚未建立(如嵌入式製程)。故本計畫擬自第一項著手，對金屬閘元件的臨界電壓控制進行研究。

奈米世代元件的工作電壓約 0.9V - 1.2 V 左右[8]，為維持足夠的驅動電流，臨界電壓必須控制在 0.3 伏特以下。由於臨界電壓與閘極與基板的功函數差有關，也就是與金屬閘的功函數有關，功函數的穩定性與可調變性便非常重要。但針對次 0.1 微米世代元件需求進行穩定性及精密控制研究的文獻極少[9-13]。本計畫即著重在金屬薄膜的功函數控制及調變技術，以提供後續進行金屬閘與高介電常數介電層整合時，適當控制臨界電壓的基礎。

#### 三、結果與討論

本計畫探討氮化鉭、銅/氮化鉭、鉭、鉑等金屬閘極的功函數及其穩定性。金屬閘極以物理氣相沉積方式製作，閘介電層採用 10nm 的二氧化矽。

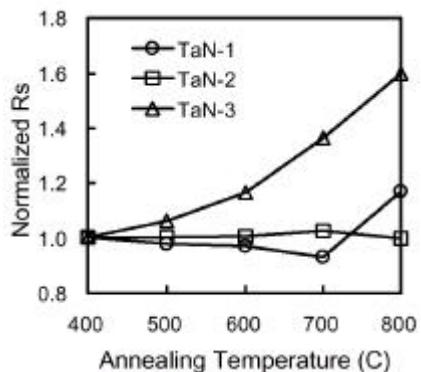

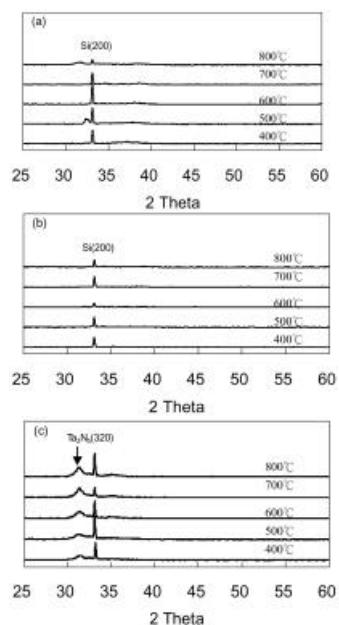

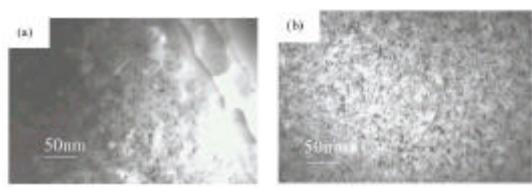

表 1 列出氮化鉭的試片編號、拉賽福背向散射測量的元素比例、以及用四點探真測量的電阻係數。圖 1 是各試片經不同溫度退火後的片電阻值。鉭/氮比最高的試片(TaN-3)的片電阻隨溫度升高而增加，其它試片則一直到 800 片電阻仍維持穩定。圖 2 是各試片的 X 射線繞射頻譜，TaN-1 及 TaN-2 試片的訊號非常微弱，幾乎處於非晶狀態，TaN-3 試片則隨溫度上升而有 Ta<sub>3</sub>N<sub>5</sub> 晶相出現，由於 Ta<sub>3</sub>N<sub>5</sub> 電阻係數很高，故應為片電阻上升之原因。圖 3 是 TaN-2 試片經 400 或 700 退火後的平面穿透式點子顯微鏡照片，可以確認除少數微晶粒外，薄膜幾乎是非晶狀態。因此要避免片電阻上升或多晶化，鉭/氮比需控制在 0.5 以下。

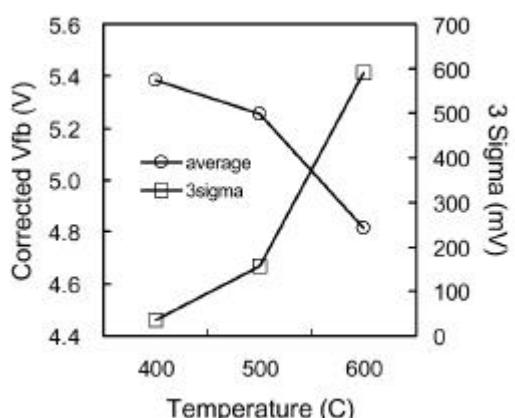

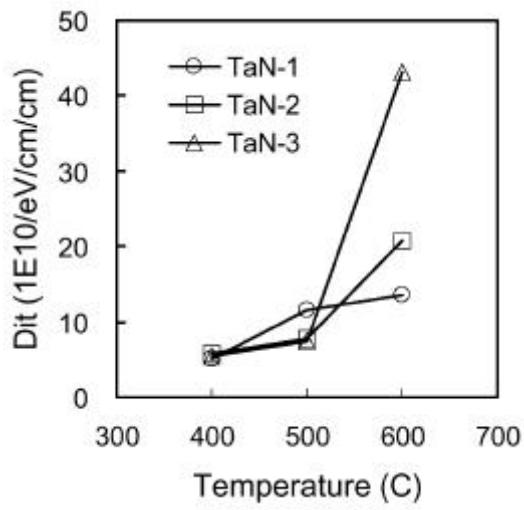

銅/氮化鉭閘極元件的平帶電壓是由 100KHz 得高便電容-電壓特性萃取，矽基板濃度及氧化層厚度的變異可藉由與理想特性的比對而消除。圖 4a-4c 分別是 TaN-1, TaN-2, TaN-3 試片校正後的平帶電壓。假設 400 退火的試片的氧化從電荷可以忽略，三種試片的功函數約在 4.15-4.20 電子伏特，氮/鉭比從 0.3 到 0.65，功函數只改變不到 70mV。當退火溫度從 400 提高到 600，平帶電壓下降，同時平帶電壓的變異在 500 以上就增加到超過 100mV。

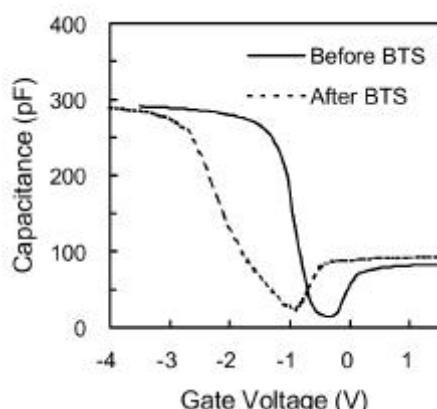

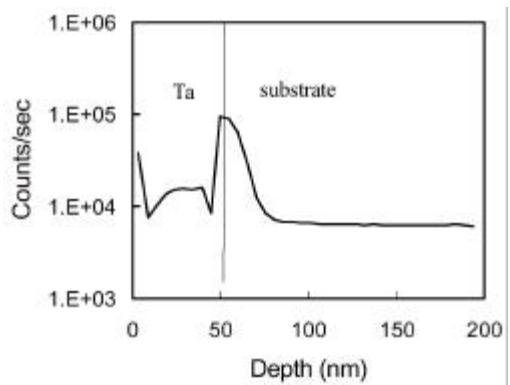

溫度-電壓應力測試(圖 5)以及二次離子質譜分析(圖 6)都顯示只有在 600 退火處理的試片發生銅穿透氮化鉭層進入閘氧化層的現象，550 以下的試片在溫度-電壓應力測試下完全沒有移動性離子造成憑待電壓飄移的現象。因此，在 600 以下的平帶電壓降低以及變異增大的問題不是因為銅污染造成。也就是說銅/氮化鉭閘極所能承受的最高製程溫度不是由銅污染決定(550)而是由平帶電壓的變異決定(500)。

圖 7 顯示試片的介面能態隨退火溫度升高而增加，這表示平帶電壓的降低很可能來自金屬閘極的熱應力。由於氮化鉭膜的晶粒極晶相在 600 以下並沒有明顯變化，平帶電壓的變異應肇因於銅膜晶粒成長造成的不均勻熱應力。表 2 列出 TaN-1, TaN-2, TaN-3 三種試片經過 400 到 600 退火的校正後平帶電壓及三倍標準差。副

晶矽閘的平帶電壓三倍標準差只有 4.8mV，遠低於銅/氮化鉭金屬閘極。

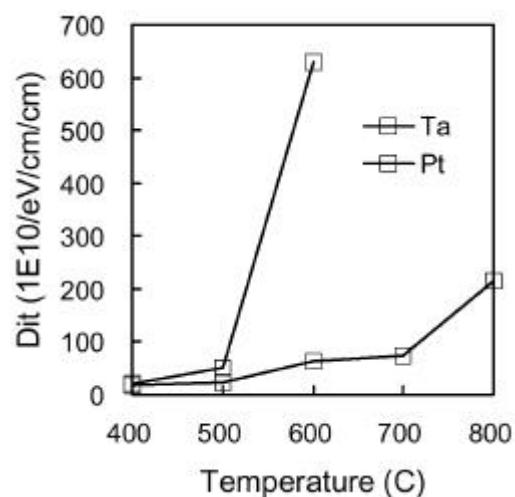

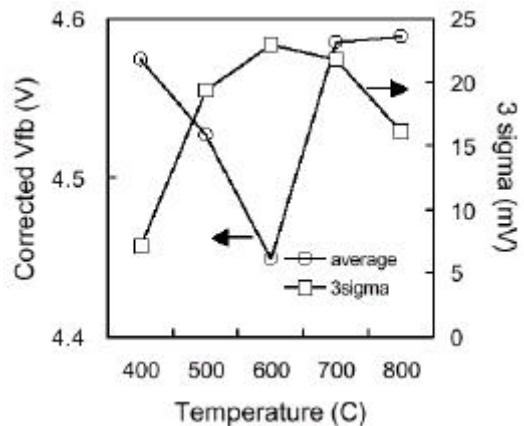

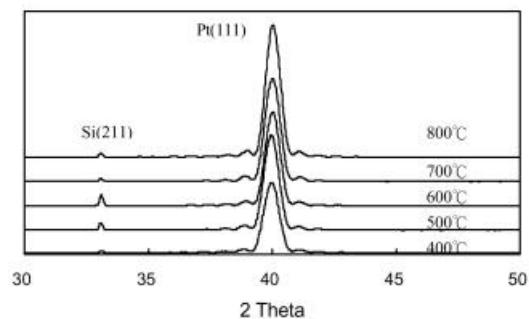

圖 8 及圖 9 分別是鉭閘極及鉑閘極元件的平帶電壓及三倍標準差。經過退火處理後，鉑閘極元件的平帶電壓下降幅度遠大於鉭閘極以及銅/氮化鉭閘極。鉑閘極元件的平帶電壓變異也遠大於鉭閘極以及銅/氮化鉭閘極。圖 10 顯示鉭閘極及鉑閘極元件的介面能態。隨退火溫度增加，鉑閘極元件的介面能態大幅增加。圖 11 是鉑薄膜的 X 射線繞射頻譜，明顯的(111)優選成長，完全不同於鉭及氮化鉭的非晶態。這些結果表示鉭閘極及鉑閘極元件的平帶電壓下降及變異也是因為熱應力所造成。

#### 四、計畫成果自評

本計畫獲致以下幾項重要結論：

1. 氮化鉭的功函數隨氮/鉭比例從 0.3 到 0.65 只有不到 70mV 的調變幅度，故只能做為 N 通道元件的閘極。

2. 銅/氮化鉭閘極的製程溫度不是由銅污染所決定，而是由銅膜熱應力所引起的平帶電壓變異所決定，最高溫度必須低於 500 。

3. 鉑的功函數適合 P 通道元件，但是晶相優選成長及熱應力造成明顯的平帶電壓飄移及變異，對量產極為不利。

4. 非晶態、無明顯晶粒成長或晶相轉變、低熱應力是選擇金屬閘極材料的重要指標。

本計畫基本上照原定計畫書進行，但在發現氮化鉭的功函數不易調變後，以離子質入方式調變功函數的部分便不再進行。另外在發現熱應力造成平帶電壓變異後，將重點修正為不同金屬材料的熱應力影響。實際執行內容與原計畫相符程度約達 80%。

本計畫執行期間除培養一名碩士班畢業生黃誌鋒先生外，另兩名研究助理亦獲得基本的研究訓練。計畫成果正在整理為學術論文中，預計可發表至少一篇短篇(或研討會)論文及一篇長篇論文。前述結論對後續研究及工業界選擇閘極材料均有重要貢獻。

## 五、參考文獻

- [1]. R. H. Dennard, F. H. gaensslen, H. Yu, V. L. Rideout, E. Bassous, and A. R. Leblanc, "Design of Ion Implanted MOSFET's with Very Small Physical Diemensions", IEEE J. Solid State Circuits, vol.SC-9, pp.256, 1974.

- [2]. C. Y. Wong, J. Y. C. Sun, Y. Taur, C. S. Oh, R. Angelucci, and B. Davari, "Doping of n+ and p+ Polysilicon in a Dual-Gate Process", IEEE International Electron Devices Meeting (IEDM '88), San Francisco, pp.238, 1988.

- [3]. S. H. Lo, D. A. Buchanan, and Y. Taur, "Modeling and Characterization of Quantization, Polysilicon depletion, and direct tunneling effects in MOSFETs with Ultra Thin Oxides", IBM J. Res. Develop., vol.43, No.3, pp.327, 1999.

- [4]. Y. Taur, D. Buchanan, W. Chen, D. J. Frank, K. I. Ismail, S.-H. Lo, G. A. Sai-Halasz, R. G. Viswanathan, H.-J. C. Wann, S. J. Wind, and H.-S. Wong, "CMOS Scaling into the Nanometer Regime", Proc. IEEE 85, 486 (1997).

- [5]. J. R. Pfeister, K. F. Bake, T. C. Mele, H. H. Tseng, P. J. Tobin, J. D> Hayden, J. W. Miller, C. D. Gunderson, and L. C. Parrillo, "The Effecs of Boron Penetration on p+ Polysilicon Gates MOS Devices", IEEE Trans. Electron Devices, vol.ED-37, pp.1842, 1990.

- [6]. B. Y. Kim, I. M. Liu, H. F. Luan, M. Gardner, J. Fulford, and D. L. Kwong, "Impact of Boron Penetration on Gate Oxide Reliability and Device Lifetime in p<sup>+</sup> Poly pMOSFET's," presented at the IEEE International Electron Devices Meeting (IEDM '97), Washington, DC, 1997.

- [7]. K. A. Ellis and R. A. Buhrman, "Boron Diffusion in Silicon Oxides and Oxynitrides," J. Electrochem. Soc. 145, 2068 (1998).

- [8]. "International Technology Roadmap for Semiconductors", Semiconductor Industry Association, pp.87, 1999.

- [9]. H. Wakabayashi, Y. Saito, K. Takeuchi, T. Mogami, and T. Kunio, "A Novel W/TiNx Metal Gate CMOS Technology using Nitrogen Concentration Controlled TiNx Film", IEEE International Electron Devices Meeting (IEDM '99), Washington D.C., pp. 253, 1999.

- [10]. A. Yagishita, T. Saito, K. Nakajima, S. Inumiya, K. Matsuo, Y/ Akasaka, Y. ozawa, H. Yano, G. Minamihaba, Y. Matsui, Y. Tsunashima, K. Suguro, T. Arikado, and K. Okumura, "Reduction of Threshold Voltage Deviation in Damascene Metal Gate MOSFETs", IEEE International Electron Devices Meeting (IEDM '99), Washington D.C., pp. 257, 1999.

- [11]. K. Nakajima, Y. Akasaka, M. Kaneko, M. Tamaoki, Y. Yamada, T. Shimizu, Y. Ozawa, and K. Suguro, "Work Function Controlled Metal Gate Electrode on Ultrathin Gate Insulator", in proceeding of VLSI symposium, Kyoto, pp.96, 1999.

- [12]. Q. Lu, R. Lin, P. Ranade, T. J. Kin, and C. Hu, "Metal Gate Work Function Adjustment for Future CMOS Technology", in proceeding of VLSI symposium, Kyoto, pp.45, 2001.

- [13]. Y. S. Suh, G. Heuss, H. Zhong, S. N. Hong, and V. Misra, "Electrical Characteristics of TaSixNy Gate Electrode for Dual Gate Si-CMOS Devices", in proceeding of VLSI symposium, Kyoto, pp.47, 2001.

表 1. 氮化鉻的試片編號、元素比例、以及電阻係數。

| Sample ID                                | TaN-1 | TaN-2 | TaN-3 |

|------------------------------------------|-------|-------|-------|

| N/Ta ratio                               | 0.30  | 0.50  | 0.65  |

| Resistivity ( $\Omega \cdot \text{cm}$ ) | 463   | 480   | 1299  |

表 2. 三種試片經過 400 到 600 退火的校正後平帶電壓及三倍標準差。

|     |                               | TaN-1 | TaN-2 | TaN-3 |

|-----|-------------------------------|-------|-------|-------|

| 400 | Corrected V <sub>fb</sub> (V) | 4.139 | 4.196 | 4.209 |

|     | deviation (mV)                | 21    | 15    | 36    |

| 500 | Corrected V <sub>fb</sub> (V) | 4.093 | 4.130 | 4.194 |

|     | deviation (mV)                | 84    | 57    | 78    |

| 600 | Corrected V <sub>fb</sub> (V) | 3.972 | 3.999 | 4.045 |

|     | deviation (mV)                | 120   | 84    | 135   |

圖 1. 各試片經不同溫度退火後的片電阻值。

圖 2. (a) TaN-1, (b) TaN-2, (c) TaN-3 試片的 X 射線繞射頻譜。

圖 3 是 TaN-2 試片經(a) 400 或(b) 700 退火後的平面穿透式點子顯微鏡照片。

圖 4. (a) TaN-1, (b) TaN-2, (c) TaN-3 試片校正後的平帶電壓與退火溫度的關係。

圖 5. Cu/TaN-2 試片經 600 退火後之溫度-電壓應力測試結果。

圖 6. Cu/TaN-2 試片經 600 °C 退火後之二次離子質譜分析結果。

圖 9. 鉑閘極元件的平帶電壓及三倍標準差。

圖 7. 試片的介面能態與退火溫度之關係。

圖 10. 鉑閘極及鉻閘極元件的介面能態與退火溫度之關係。

圖 8. 鉑閘極元件的平帶電壓及三倍標準差。

圖 11. 鉑薄膜的 X 射線繞射頻譜。

## 附件：出席國際學術會議心得報告

(本次出席國際會議並未發表論文，故僅附心得報告如下)

### 一、出國事由：

赴日本參加在京都舉行的 2001 Symposium on VLSI Technology 研討會，並順便參加在同一地點舉行的 2001 Silicon Nanoelectronics Workshop。

### 二、行程安排：

- 6/9 搭機赴日，自關西機場入境。

- 6/10-6/11 參加 2001 Silicon Nanoelectronics Workshop。

- 6/12-6/14 參加 2001 Symposium on VLSI Technology。

- 6/15 搭機返國。

### 三、心得摘要：

#### 1. 2001 Silicon Nanoelectronics Workshop 紀要

此行為本人首度參加此研討會。參加人數不多，約數十位，論文水準亦不如稍後的 Symposium on VLSI Technology，但仍有一些有趣的先期研究的成果。兩天的議程收錄了 27 論文，將近二分之一是 quantum dot, quantum wire, single electron transistor 方面的論文。上述元件在近幾年頗受重視，但是因為體積微小，在製作的穩定性以及組成電路或系統的架構方面都極不成熟，元件本身固然有其引人入勝之處，但從本次研討會幾篇論文討論利用此類元件的電路架構來看，要在未來 5-10 年內廣泛使用並不容易。但所提出的一些技術則有機會運用在其它元件上。例如以三角形通道形狀減低短通道效應、以微突起的矽表面作為場發射源等等，應該都還有繼續發展的空間。

#### 2. 2001 Symposium on VLSI Technology 紀要

Symposium on VLSI Technology 的性質類似 International Electron Device Meeting，但是所涵蓋的範圍比較小，多集中在與 VLSI 有關的技術上，所以沒有高功率元件或是化合物半導體元件方面的論文。今年的論文範圍更是特別，除了幾個 DRAM 及記憶體 IC 的 sections 外，有超過三分之一的 sections 都在探討 MOS 元件的閘電極以及介電層的問題。在過去幾年相當受到重視的多層導線技術方面，今年只剩下一個 section，連同開幕當天早上的一篇論文，總共只有五篇論文。推究原因可能是多層導線製程在五年前進

入銅導線及低介電常數材料領域，面臨材料更新以及製程技術更替的局面，但隨著銅導線製程進入量產，整體發展方向已無大幅度的改變，所帶探討的是如何微小化、如何提高良率及可靠度，以及持續降低介電材料的介電常數。反觀在前段製程部分，截至目前為止，仍沿用複晶矽為閘極材料，介電材料則沿用二氧化矽再加以氮化處理，但這樣的做法已走到極限，未來幾年需要的材料更替及製程技術則尚無定論，遂成為今年度研討會的重點課題。

在二氧化矽的替代材料方面，今年度沒有新的材料發表，比較受重視的仍是高溫穩定性較好的  $HfO_2$  及  $ZrO_2$ 。值得注意的是雖然發表的幾篇論文都宣稱得到特性不錯的元件，但都只是測量結果，尚缺乏適當的物理模型。可靠度的數據更少，分析方式沿用  $SiO_2$  的模型，對新材料來說是否正確尚有疑問。國內從事這方面研究的人員應特別留意的是不同方法所沉積出來的薄膜，其性質差異很大，今年的論文已經都是用 CVD 方式製作的，似乎 JVD 或 ALD 又比傳統 CVD 方式好，國內在這部份的設備非常缺乏，不僅在製程技術開發上必然落後，連進行測試分析及模型建立都可能面臨無法取得高品質材料的困境，毫微米實驗試在這方面應加速設備的更新。

在複晶矽閘電極的替代材料方面，今年有幾篇有意思的論文。調變 TiN 的 N 的比例可以改變功函數是已知的事情，今年 Berkley 的研究群發表在 Mo 中植入 N 也可以調變功函數達  $0.42eV$ ，但是其植入條件可能會損傷到閘介電層，這個因素在論文中沒有考慮到，金屬閘極的功函數調整是愈來愈迫切的事。同一個研究群的另一篇論文討論到金屬閘極與介電層介面反應會影響等效功函數是非常值得注意的現象。到目前為止發表的金屬閘極元件，都未能同時兼顧 NMOS 及 PMOS 的臨界電壓，原因當然很多，功函數無法確實掌握是一個主要因素。如果介面鍵結會有影響，在分析的時後必須納入考慮。部份金屬閘極的論文有顯示功函數或平帶電壓的變異量，遠高於可容許的元件臨界電壓變異量，這和本人這一年度的研究結果相符，恐怕會是金屬閘極另一個棘手問題。

第二天晚上的討論會也有一些重要的訊息。本人主要參加 High k Dielectrics : Is It Necessary ? If so, When, What, How ? 的討論。幾乎可以確定 high k 材料是不可避免的路，時間點則在 2005-2007 之間。材料的選擇目前看好  $HfO_2$  及  $ZrO_2$ ,  $Al_2O_3$  因為 k 值不夠高，大部份人並不看好，但是也有些單位如 IMEC 持不同的看法。CVD 是必然的選擇，但是是 ALD 或 JVD 或是有更好的技術則尚無定論。High k 材料的引進會不會造成新的污染是大家都有興趣的問題，但似乎沒有人仔細的研究過。另一個問題則是目前的量產廠幾乎都不能進行 high k 及金屬閘的製程，大部份的研究工作是在設備商或研究單位進行，如何在短時間內將廠外研究結果結合到廠內，並完成整合及驗證，似乎已經迫

在眉睫了。快結束的時後轉到討論 Cu/low k 的會場，討論的重點在於 k 值在 2.0 左右的材料的成熟度問題，看來如前面所述，這個方向就是持續降低介電層的介電常數，短期內沒有其它突破性的發展。

今年度的研討會有我國單位參與的論文有三篇，除一篇是交通大學與臺積電共同所發表，另兩篇是聯華電子與 IBM 及 Infineon 共同發表，令人遺憾的是該兩篇論文雖列出某幾位共同作者屬聯華電子，但國家名稱卻標示為美國。

我國在 IC 領域的影響力以不容小覷，但在此類一流研討會所發表的論文篇數始終遠低於美日韓歐，足見研究不夠前瞻亦不夠深入。政府投入預算不足，研究單位無法即時更新設備；廠商彼此間只有競爭沒有合作，研發仍以服務生產為導向。此兩者若無法改善，我國將只能維持技術的緊密追隨者的角色，以勤奮的勞工及效率的生產管理賺取利潤，卻永遠無法超前成為共同領導者。

撰寫人

崔秉鉞

助理教授

交通大學 電子工程學系