## Formation of cobalt-silicide nanocrystals in Ge-doped dielectric layer for the application on nonvolatile memory

Chih-Wei Hu, Ting-Chang Chang, Po-Tsun Liu, Chun-Hao Tu, Sheng-Kai Lee, Simon M. Sze, Chun-Yen Chang, Bi-Shiou Chiou, and Tseung-Yuan Tseng

Citation: Applied Physics Letters 92, 152115 (2008); doi: 10.1063/1.2908916

View online: http://dx.doi.org/10.1063/1.2908916

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/92/15?ver=pdfcov

Published by the AIP Publishing

## Articles you may be interested in

Formation of iridium nanocrystals with highly thermal stability for the applications of nonvolatile memory device with excellent trapping ability

Appl. Phys. Lett. 97, 143507 (2010); 10.1063/1.3498049

NiSiGe nanocrystals for nonvolatile memory devices

Appl. Phys. Lett. 94, 062102 (2009); 10.1063/1.3080201

Nonvolatile memory characteristics influenced by the different crystallization of Ni–Si and Ni–N nanocrystals Appl. Phys. Lett. **92**, 062112 (2008); 10.1063/1.2841049

Highly thermally stable TiN nanocrystals as charge trapping sites for nonvolatile memory device applications Appl. Phys. Lett. **86**, 123110 (2005); 10.1063/1.1890481

Nickel nanocrystal formation on HfO 2 dielectric for nonvolatile memory device applications Appl. Phys. Lett. **86**, 103505 (2005); 10.1063/1.1881778

## Formation of cobalt-silicide nanocrystals in Ge-doped dielectric layer for the application on nonvolatile memory

Chih-Wei Hu, <sup>1</sup> Ting-Chang Chang, <sup>2,a)</sup> Po-Tsun Liu, <sup>3</sup> Chun-Hao Tu, <sup>1</sup> Sheng-Kai Lee, <sup>1</sup> Simon M. Sze, <sup>1</sup> Chun-Yen Chang, <sup>1</sup> Bi-Shiou Chiou, <sup>1</sup> and Tseung-Yuan Tseng <sup>1</sup> Institute of Electronics, National Chiao Tung University, Hsin-Chu, 300 Taiwan, Republic of China <sup>2</sup> Department of Physics and Institute of Electro-Optical Engineering, and Center for Nanoscience and Nanotechnology, National Sun Yat-Sen University, Kaohsiung, 804 Taiwan, Republic of China <sup>3</sup> Department of Photonics and Display Institute, National Chiao Tung University, Hsin-Chu, 300 Taiwan, Republic of China

(Received 10 August 2007; accepted 24 March 2008; published online 18 April 2008)

In this work, Ge-doped cobalt-silicon thin film was synthesized using a cosputter system (Co and  $Si_{0.5}Ge_{0.5}$ ). The deposited film was annealed in oxygen ambient at 650 °C to form cobalt-silicide nanocrystals. The formation of isolated silicide nanocrystals was confirmed by transmission electron microscopy and x-ray photoelectron spectroscopy analysis. In metal-oxide-insulator-oxide-silicon structure, a significant electrical hysteresis is observed and attributed by the presence of the cobalt-silicide nanocrystals and the oxidized Ge elements. © 2008 American Institute of Physics. [DOI: 10.1063/1.2908916]

Recently, floating-gate (FG) structure devices are the mainstream technology for the nonvolatile memory. It was invented by Kahng and Sze at Bell Labs in 1967. However, the conventional FG devices have some drawbacks for the demand of scaling down devices hereafter.<sup>2</sup> With scaling down, tunneling oxide thinning will bring the storage to easily lose charge as there is leakage path existing in the tunneling oxide. The structure with distributed storage elements is considered the solution for this issue. Therefore, Tiwari et al. presented using Si nanocrystals (NCs) instead of conventional FG continuous storage layer.<sup>3</sup> To date, several methods and materials have been widely studied on the formation of NCs for the nonvolatile memory application. 4-6 Among several kinds of NC devices, the metal and metal silicide NCs are considered to be beneficial in its variable work function, higher density of states around the Fermi level.<sup>7–9</sup> In addition, the dielectric layer that NCs embedded in can also contribute the charge storage sites by defects or traps created in the interfaces between different materials. 10,11 In this letter, the formation of cobalt-silicide NCs was investigated by adding Ge elements into the cobaltsilicide film using cosputtered Co and Si<sub>0.5</sub>Ge<sub>0.5</sub> targets on tunnel oxide. After thermal oxidation process, the cobaltsilicide NCs are formed and the additional Ge elements are oxidized. Furthermore, the oxidized Ge elements contribute extra charge trap sites.

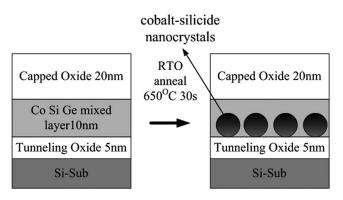

Figure 1 exhibits the process flow in this work. First, a 5-nm-thick thermal oxide was grown as the tunneling oxide on *p*-type Si substrate by dry oxidation in atmospheric pressure chemical vapor deposition furnace. Subsequently, a 10-nm-thick Ge-doped cobalt-silicon thin film was deposited by sputtering the Co and Si<sub>0.5</sub>Ge<sub>0.5</sub> targets simultaneously. The dc sputter power of cobalt and Si<sub>0.5</sub>Ge<sub>0.5</sub> are 50 and 75 W, respectively. The process pressure was set at 7.6 mTorr, which yielded the deposition rate of 0.03 nm/s. Then a 20-nm-thick capped oxide was deposited by plasmaenhanced chemical vapor deposition (PECVD) before rapid

thermal oxidation (RTO) process. After RTO at 650 °C for 30 s, the cobalt-silicide NCs nucleated in the dielectric layer. Afterwards, a 30-nm-thick blocking oxide (SiO<sub>2</sub>) was capped by PECVD system. Finally, Al gate electrode was patterned and annealed. In addition, the electrical characteristics were performed in terms of capacitance-voltage (C-V) and current-voltage (J-V). Transmission electron microscopy (TEM) and x-ray photoelectron spectroscopy (XPS) reveal the material composition and formation of NCs after thermal oxidation process.

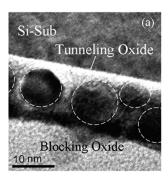

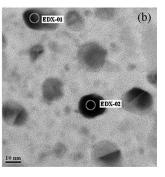

Figure 2 shows (a) the cross-sectional and (b) the plane-view TEM image of the fabricated device sample. It can be found that the average diameter of cobalt-silicide NCs is around 8-10 nm from the cross-sectional TEM image and the area density of NCs is estimated to be about  $1.03 \times 10^{11}$  cm<sup>-2</sup> from the plane-view TEM image. According the reported paper, the Ge elements tend to segregate at interface during the formation of the NCs. With the segregation of Ge elements, the component of NCs is nearly cobalt silicide. Moreover, according to the thermodynamic analysis, the Si and Ge elements are prior to be oxidized in the mixed film. Therefore, the cobalt-silicide NCs nucleate in the thin dielectric film mixed with silicon oxide and oxidized Ge elements.

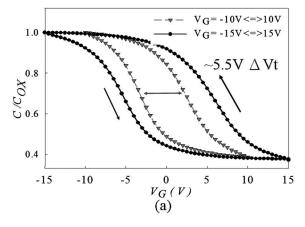

Figure 3(a) shows the *C-V* hysteresis after bidirectional sweeps, which implies the electron charging and discharging

FIG. 1. The process flow proposed in this work.

<sup>&</sup>lt;sup>a)</sup>Electronic mail: tcchang@mail.phys.nsysu.edu.tw.

FIG. 2. The cross-sectional TEM micrographs of the MOIOS structure using thermal oxidized Ge-doped cobalt-silicon layer as trapping layer. The size of cobalt-silicide NCs are about 8-10 nm and the density of the nanocrystals is estimated to be about  $1.03 \times 10^{11}$  cm<sup>-2</sup>.

effects of the metal-oxide-insulator-oxide-silicon (MOIOS) structure with cobalt-silicide NCs embedded in dielectric layer. The bidirectional C-V sweeps were performed from deep inversion to deep accumulation and in reverse, which exhibited a threshold voltage shift  $(\Delta V_t)$ , indicating carriers charging effect. In Fig. 3(a), it is found that the memory window of 5.5 V is observed under ±10 V gate voltage operation. As the swept voltage is increased to  $\pm 15$  V, a more pronounced C-V shift is observed. The charge storage ability of Ge-doped cobalt-silicon memory devices is attributed to the presence of cobalt-silicide NCs and the oxidized Ge elements, which provide extra charge trap sites. Moreover, the

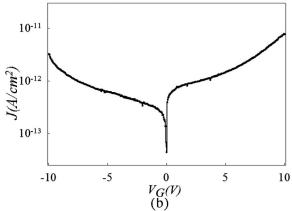

FIG. 3. (a) Memory effect obtained from C-V characterization of the MOIOS structure. The electrical C-V measurements are performed by bidirectional voltage sweeping (1) from 10 to -10 V and -10 to 10 V; (2) from 15 to -15 V and -15 to 15 V. (b) The current density measurement by voltage sweeping from (1) 0 to 10 V and (2) 0 to -10 V.

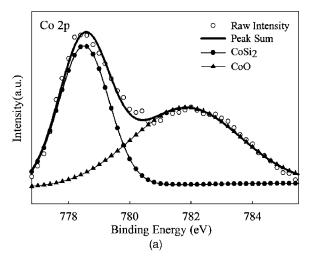

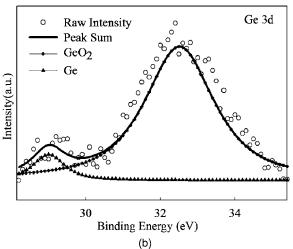

FIG. 4. (a) Co 2p XPS spectrum of the charge trapping layer after 650 °C thermal oxidation process. The main peak can be composed into two components which center at ~778.5 and ~782 eV corresponding to cobaltsilicide and cobalt oxide. (b) Ge 3d XPS spectrum of the charge trapping layer. The main peak at 32.5 eV can be assigned to the oxidation of Ge elements.

leakage current in the MOIOS structure is shown in Fig. 3(b). The lower leakage current could avoid the stored charge leaking into gate through the blocking oxide for the MOIOS structure. According to the reported paper, the asymmetry of J-V characteristics in the figure is because when the applied voltage is swept from 0 to +10 V, some negative charges are trapped in the defects of the dielectric layer, leading to an increase of the injection barrier height and, therefore, to a decrease of the oxide conductivity.

Figure 4 demonstrates the results of XPS analysis for Ge-doped cobalt-silicon thin film after thermal oxidation process. In Fig. 4(a), it can be found that the Co 2p XPS spectrum shows two peaks corresponding to cobalt silicide and cobalt oxide at  $\sim$ 778.5 and  $\sim$ 782 eV, respectively. 15 The result indicates that cobalt-silicide NCs are formed and partly cobalt elements are oxidized to cobalt oxide during thermal oxidation process. Furthermore, the Ge 3d XPS spectrum is displayed in Fig. 4(b) which clearly indicates the peak at  $\sim$ 32.5 eV. <sup>16</sup> It is believed that the thermal oxidation process causes the formation of cobalt-silicide NCs and the oxidation of Ge elements.

In conclusion, we demonstrate the formation of the cobalt-silicide NCs by cosputtering Co and Si<sub>0.5</sub>Ge<sub>0.5</sub> targets

simultaneously. A significant C-V hysteresis of 5.5 V is observed under  $\pm 10$  V gate voltage operation for the MOIOS structure. The obvious memory window is attributed to both the cobalt-silicide NCs and the trap-rich oxidized Ge elements. In addition, this formation method of cobalt-silicide NCs with distributed storage elements is easy and compatible with the current manufacturing technology of semiconductor industry.

This work was performed at National Nano Device Laboratory and was supported by the National Science Council of the Republic of China under Contract Nos. NSC 96-2120-M-110-001, NSC 95-2221-E-009-296-MY2, NSC 96-2221-E-009-202-MY3, and NSC 96-2112-M-110-013.

- <sup>4</sup>Y. C. King, T. J. King, and C. Hu, Tech. Dig. Int. Electron Devices Meet. **1998**, 115.

- <sup>5</sup>J. Y. Tseng, C. W. Cheng, S. Y. Wang, T. B. Wu, K. Y. Hsieh, and R. Liu, Appl. Phys. Lett. **85**, 2595 (2004).

- <sup>6</sup>Y. Zhu, D. Zhao, R. Li, and J. Liu, Appl. Phys. Lett. **88**, 103507 (2006).

<sup>7</sup>A. Chandra and B. M. Clemens, Appl. Phys. Lett. **87**, 253113 (2005).

- <sup>8</sup>W. R. Chen, T. C. Chang, P. T. Liu, P. S. Lin, C. H. Tu, and C. Y. Chang, Appl. Phys. Lett. **90**, 112108 (2007).

- <sup>9</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices **49**, 1606 (2002).

- <sup>10</sup>Y. H. Lin, C. H. Chien, C. T. Lin, C. Y. Chang, and T. F. Lei, IEEE Electron Device Lett. **26**, 154 (2005).

- <sup>11</sup>T. C. Chang, S. T. Yan, Y. H. Tai, P. T. Liu, and S. M. Sze, Appl. Phys. Lett. **84**, 2581 (2004).

- <sup>12</sup>P. T. Goeller, B. I. Boyanov, D. E. Sayers, and R. J. Nemanich, Nucl. Instrum. Methods Phys. Res. B 133, 84 (1997).

- K. Prabhakaran, K. Sumitomo, and T. Ogino, Surf. Sci. 429, 274 (1999).

M. Porti, M. Avidano, M. Nafría, X. Aymerich, J. Carreras, O. Jambois, and B. Garrido, J. Appl. Phys. 101, 064509 (2007).

- <sup>15</sup>K. Prabhakaran and T. Ogino, Appl. Surf. Sci. **121/122**, 213 (1997).

- <sup>16</sup>G. Hollinger, P. Kumurdjian, J. M. Mackowski, P. Pertosa, L. Porte, and T. M. Duc, J. Electron Spectrosc. Relat. Phenom. 5, 237 (1974).

<sup>&</sup>lt;sup>1</sup>D. Kahng and S. M. Sze, Bell Syst. Tech. J. **46**, 1288 (1967).

<sup>&</sup>lt;sup>2</sup>J. D. Blauwe, IEEE Trans. Nanotechnol. **1**, 72 (2002).

<sup>&</sup>lt;sup>3</sup>S. Tiwari, F. Rana, K. Chan, H. Hanafi, W. Chan, and D. Buchanan, Tech. Dig. - Int. Electron Devices Meet. **1995**, 521.