# 行政院國家科學委員會補助專題研究計畫成果報告

# 無鉛銲錫的電遷移研究

計畫類別:■個別型計畫 整合型計畫

計畫編號: NSC 90 - 2216 - E - 009 - 042 -

執行期間: 90年 8月 01日至 91年07月31日

計畫主持人:陳 智

本成果報告包括以下應繳交之附件:

赴國外出差或研習心得報告一份 赴大陸地區出差或研習心得報告一份 出席國際學術會議心得報告及發表之論文各一份 國際合作研究計畫國外研究報告書一份

執行單位:交通大學材料科學與工程系

中 華 民 國 90 年 10 月 29 日

# 行政院國家科學委員會專題研究計畫成果報告 無鉛銲錫的電遷移研究

A Systematic Study of Electromigration in Pb-free Solder Alloys

計畫編號: NSC 90 - 2216 - E - 009 - 042 -

執行期限:90年8月01日至91年07月31日

主持人:陳智 交通大學材料科學與工程系

計畫參與人員:邵棟樑、劉書宏、許穎超、陳義雄、林克瑾

## 一、中文摘要

在消費電子產品以及微處理器的構裝中,有兩種趨值得注意,第一個趨勢是將以無鉛銲錫取代傳統的含鉛銲錫。第二個趨勢是直接將矽晶片接在 organic 的基板上,此技術稱為 Direct Chip Attachment (DCA) 或是 Flip Chip on Organic.

含鉛銲錫的使用一直是造成鉛環境污染的一個重要原因之一。因此,美國、歐洲和日本已開始注重此問題。並將於近年內禁止鉛在電子產品的使用。同時隨著消費電子產品的小型化,電子構裝中用的銲錫即將面臨一個嚴重的可靠性(reliability)問題:即 Electromigration,電遷移。本計畫擬設計適合研究銲錫 Electromigration的結構:即矽 V 形槽(V-grove)、 Blech 和球狀三種試片,並運用 NDL 和交大半導體中心的 製 程 儀 器 及 技 術 來 製 作 銲 錫 Electromigration 試片。將使用 SnAg、SnSb、SnAgCu、以及純 Sn 等四種無鉛銲錫,進行銲錫 Electromigration的量測及研究。

本計劃將針對純錫、SnAg SnAgCu和 SnSb 種無鉛銲錫進行研究。建立 Blech structure 試片及製備球狀 Electromigration 試片及,模擬 Flip Chip 中的銲錫球。研究的重點包括以下兩項重要的課題:(1)觀察和分析銲錫的顯微結構演化和電流密度、溫度以及時間的關係。(2)量測 Electromigration 速率。將對無鉛錫銲錫的 Electromigration 特性做一個有系統的研究。。

**關鍵詞**:電子構裝、電遷移、無鉛銲錫

#### **Abstract**

In consumer electronic goods as well as in microprocessors, two current trends in electronic packaging are worth noting. The first is the replacement of Pb-Sn solder by Pb-free solder. The second is to attach the Si chip directly to an organic substrate. It is called direct chip attachment or flip chip on organic technology.

PbSn has been one of the sources for environment Pb pollution. Therefore, American, Europe, and Japan started to pay great attention to this issue, and will forbid the use of Pb-Sn solder in consumer electronics in the near future. Also, the continuous miniaturization of consumer electronics has caused a serious issue on the reliability of solder in microelectronic packaging, i.e. solder Electromigration (EM). This project proposes to design a suitable test structure for solder electromigration, including V-groove, Blech and ball samples, and to fabricate the electromigration samples in NDL and Semiconductor Center in National Chio-Tung University. Electromigration behaviors of four important Pb-free solders, SnAg, SnCu, SnAgIn and SnAgCu will be examined. In the first year, focus will be on the following three Pb-free solders: pure tin, Fundamental SnAg, and SnCu in. understanding on Electromigration will be made on the pure tin samples, and after adding few percent of Ag or Cu. In the second year, we will focus on the SnAgIn and SnAgCu solders, and start to fabricate solder ball EM samples, trying to simulate the real current flow situation in Flip Chip Technology. In the third year, then we will concentrate on the solder ball EM. The mail focus of this project includes (1) Observe and analize the microstructure evolution as a function of current density, temperature, and time. (2) Measure the volume of hillocks to calculate electromigration rate. Thus this project will make a systematic study on Pb-free solder.

Keywords: Lead-free solder, microelectronic packaging, Electromigration

## 二、緣由與目的

為了加強微處理器以及邏輯元件的性能及速度,半導體工業界一直追求較高密度的輸入/輸出接點(I/O terminal)和較小的IC 晶片[1]。因此 BGA(Ball Grid Array)製造技術已經被廣泛採用。當銲錫球的尺寸漸漸縮小,以便容納更多的I/O 接點時,銲錫球的機械強度及散熱問題都會變的更嚴重。台灣也開始重視這些問題,已經有許多學者投入銲錫球的機械強度研究。然而,由於銲錫球的尺寸縮小,同時也引起另一個新的挑戰:銲錫的電遷移

(Electromigration) [2-4]。 電遷移一種由於電場和帶電載子所造

成的質量移動。此現象通常在微電子元件中有高電流密度的導線內發生。例如在一條  $5\mu m$  寬, $0.2\mu m$  厚的鋁導線,在室溫下通入 1mA 的電流(電流密度為  $10^5$  amp/cm²),則會造成一端有 void 生成,而另一端有 extrusion 產生。嚴重時會造成電路短路。它是在 1965 年被發現會對半導體產品的可靠度會有威脅。因此,在過去三十多年中,一直有許多學者在研究此問題,並已經研究出有效的防治之道,即在鋁線中加入 2-3%的銅,而使電遷移不致於危害到電子元件。

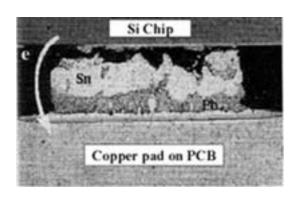

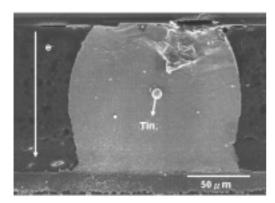

對於封裝中的銲錫接點,以前由於銲錫的尺寸較大(約  $200\mu m$ ),所以電流密度較低,電遷移對銲 錫接點並不構成威脅。然而,目前工業界使用  $150\mu m$  的銲錫球,而幾年後會降到  $75\mu m$  對於  $150\mu m$  的銲錫球,它的工作電流密度是  $10^4 amp/cm^2$ ,此電流密度造成銲錫溫度升高至 80 左右。對於  $125\mu m$  共晶錫鉛銲錫( 溶點 183 ),Elenius 在去年指出,在 150 下通入 $6-8\times10^3 A/cm^2$ 的電流密度,經過 100 小時

後, Electromigration 會破壞銲錫接點(見圖一), 所以當銲錫的尺寸漸漸地縮小時,所通入的電流密度也跟著增加,

Electromigration 對於元件的可靠性將會有 很嚴重的影響。

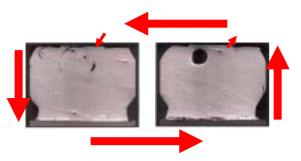

圖一: 共晶銲錫球的 EM。電子流從圖的上方流到圖的下方。在銲錫球上方造成許多大的 voids [5]。

### 三、結果與討論

1. SnAgCu 銲料之電遷移

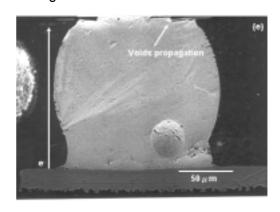

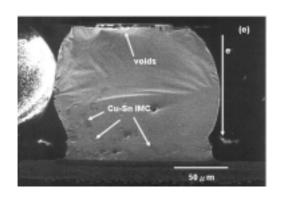

圖二、 試片在電流密度 2\*10<sup>4</sup>100 下 168 小時之 SEM 橫截面圖, 明顯發現孔洞擴大。

圖三、 試片在電流密度 2\*10⁴100 下 168 小時之 SEM 橫截面圖,與圖一相反之電子流方向,明顯發現孔洞擴大於陰極處而造成試片破壞。

圖六、 圖四之放大圖 , 明顯發現電子遷移作用下破壞發生於 UBM 與 solder 之接合處。

Cu

圖四、 EDS mapping 明顯發現銅原素在電子遷移作用下朝陽極移動而形成化合。

圖五、試片在電流密度 2\*10<sup>4</sup> 150 下 27 小時之 SEM 橫截面圖,明顯發現孔洞擴大 於陰極處而造成試片破壞,較 100 破壞速 度快約 6 倍。

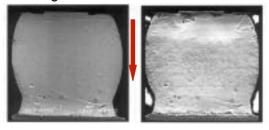

## 2. SnAg 銲料之電遷移

未通電

通電40小時

未通電

通電40小時

#### 圖八

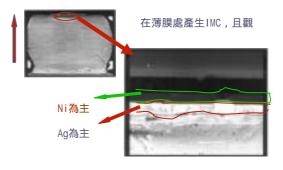

圖七和圖八:錫銀焊錫球通電 40 小時。紅 色箭頭代表電子流的方向。可以發現在錫 球陰極部分產生 void, 陽極部分 IMC 也略 有成長(圖九)。在錫球中間也有點狀的 IMC 形成,經過SEM的EDS分析其成份為Ag3Sn。

未通電

通電40小時

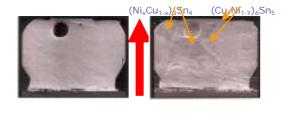

圖九:厚膜 IMC 在通電後有明顯的成長。 這是因為錫在電子流的驅動下會擴散到厚 膜的鎳凸塊層和鎳產生反應形成 IMC。

圖十:厚膜的鎳和錫球中的銀被電子流衝 到薄膜 UBM 處,並且在薄膜處形成層狀的 IMC

圖十一: 通電 40 小時後在陽極薄膜 UBM 和 錫球介面產生 crack。Crack 的形成會縮小 開口的面積,相對提高電流密度,使電遷 移的效應更強烈。加強後的電遷移又會導 致 crack 進一步變大。這樣的惡性循環會 加快錫球失效的時間, Crack 的形成是由於 錫銀 IMC 在電遷移下移動到 UMB 和錫球介 面導致介面介面機械性質劣化形成 crack。

#### 3. SnSb5 銲料之電遷移

我們使用實際的 solder bumps 來進行 銲錫的電子遷移實驗。Solder bumps 是使 用錫及銻的無鉛銲錫,其重量百分比量為 Sn:95%Sb:5%。通入的電流密度為2x 104A/cm2;通電時所處的溫度為150。 而所使用的UBM金屬曾在chip side是 Ti/Cr-Cu/Cu;在PCB上的是 electroplated Cu/Ni/Au。

圖十二:solder bumps 未通電前的情況, 紅線為電子流的方向,750X。

在通電電的過程中可發現有新的 IMCs 在 bump 中生成,且隨著通電時間的加長, IMCs 的數量也漸漸變多。而 IMCs 可分為 (NixCu1-x)3Sn4和(Cu4Ni1-y)6Sn5兩種,隨著通電時間的增長,所生成的 IMCs 會以 (NixCu1-x)3Sn4為主,可能是因為 Cu 的濃度漸漸下降所致。

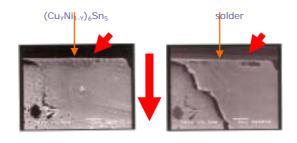

圖十三:為未通電和通電 110 小時, 150 的 SEM 圖,電子流方向為由 board side 往 chip side, 750X。

110hr

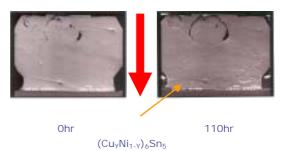

圖十四:未通電與通電 110 小時, 150 的 SEM圖,電子流方向為由 chip side 往 board side, 750X。

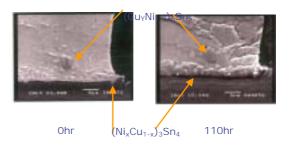

圖十五:在圖十三中的陰極,經過通電之後,可以發現 IMCs 有成長的情形出現

©hr 110hr 1

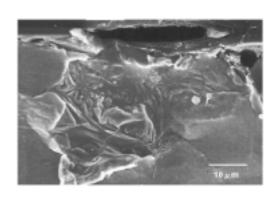

#### 4. 錫晶鬚測試部份

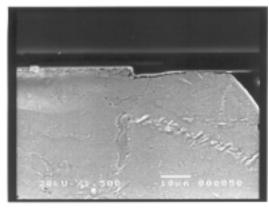

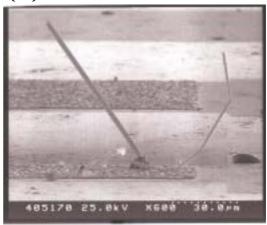

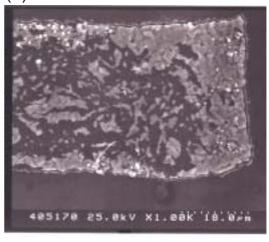

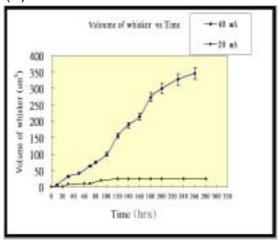

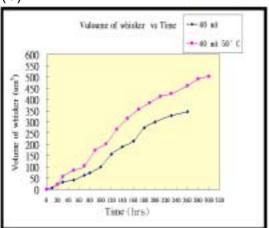

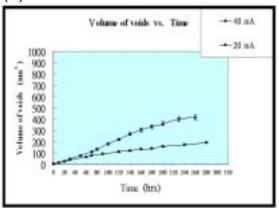

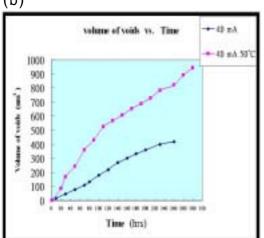

經過本年度計畫對於純錫 Blech 試片 進行電遷移的試驗,我們利用 5000A 的錫 條在 700 A 的鈦膜之上的 Blech 構造來研 究純錫的電遷移效應。所使用的電流密度 為 7.5 ×10<sup>4</sup> A/cm<sup>2</sup> 及 1.5 ×10<sup>5</sup> A/cm<sup>2</sup>。經過 通電後我們觀察到在陽極部份產生錫晶鬚 及突出物,陰極部份則產生孔洞,如圖? 所示。此外,為了研究溫度的效應,試片 在通電時分別置於室溫及 50°C 下。在室溫 下,電流密度 1.5 x10<sup>5</sup> A/cm<sup>2</sup> 時錫晶鬚的成 長速率大約為 3 A/sec, 在 50°C 下則為 7.7 A/sec。在電流密度 7.5 x10<sup>4</sup> A/cm<sup>2</sup> 室溫下 時速率為 0.4 A/sec。本論文中, 錫晶鬚成 長速率與通電的時間及電流密度及通電時 環境溫度成函數關係,如圖?及圖?所示, 在相同溫度但不同電流密度下,受到較高 電流密度的試片其錫晶鬚的成長速率較快 且陰極部分孔洞(Voids)產生及擴大的速 率也快得多。除此之外,在相同電流密度 (1.5 x10⁵ A/cm²)下,較高溫度時陽極所 產生的錫晶鬚成長速率較快,同樣地陰極 部分所產生的孔洞擴大的速率快的多。也 就是說,我們已經對此純錫的電遷移試片 做了加速的測試,模擬了在高電流密度不 同溫度下的結果。錫晶鬚的成長機制至目 前為止很多文獻所做過的推測都是針對由 機械應力所產生的錫晶鬚部分,而我們利 用電流所驅使的錫晶鬚跟由機械應力所產 生的錫晶鬚在成長機制方面主要有兩點不 同之處:第一點:在成長驅動力方面不同, 由電流所驅使的錫晶鬚其產生主要來至於 電子與金屬薄膜中錫原子的撞擊,而在未 經通電的試片長時間觀察中,並未產生錫 晶鬚。因此電子流的撞擊錫原子確實為此 錫晶鬚的產生驅動力。當電子從陰極進入 錫薄膜時並行進至陽極,電流擁擠效應 (Current crowding)產生於薄膜的角落 部分。第二點:擴散路徑不同。在文獻中, 自發性產生的錫晶鬚其錫原子的擴散是經

由短距離的擴散。而在電遷移中,錫原子 從陰極到陽極的擴散提供了一個錫原子的 流量,屬於長距離的擴散。

(a)

(b)

圖十七(a)試片通電 170 小時後陽極產生的錫晶鬚 (b)試片通電 170 小時後陰極產生的孔洞。

(a)

(b)

圖十八(a) 不同電流密度室溫下錫晶鬚成 長與時間關係圖 (b) 不同溫度相同電流密 度下錫晶鬚成長與時間關係圖。

(a)

(b)

圖十九 (a) 不同電流密度室溫下陰極孔洞產生體積與通電時間關係圖 (b) 不同溫度相同電流密度下陰極孔洞產生體積與時間關係圖。

#### 四、計畫成果自評

本計畫執行至今一年,已經將研究 EM 最困難的試片製作完成並已有十分具體結 果。

#### 五、參考文獻

- [1] The International Technology Roadmap for Semiconductors, Semiconductor Industry Association, San Jose, CA .1999.

- [2] K. N. Tu, C. C. Yeh, C. Y. Liu, and <u>C. Chen</u>, Appl. Phys. Lett., **76**, 7, 2000.

- [3] C. Y. Liu, <u>C. Chen</u>, and K. N. Tu, J. Appl. Phys. **88**, 5703, 2000.

- [4] C. Y. Liu, <u>C. Chen</u>, C. N. Liao, and K. N. Tu, Appl. Phys. Lett., **75**, 58, 1999.

- [5] S. Brandenberg and S. Yeh, Surface Mount Int. Conference and Exposition, SMI 98 Proceedings, p.337,1998.